形成用于薄膜晶体管结构的电感耦合高密度等离子体膜的方法与流程

形成用于薄膜晶体管结构的电感耦合高密度等离子体膜的方法

1.背景

2.领域

3.本公开内容的实施方式一般涉及制造薄膜晶体管(tft)的方法。更具体地,本文描述的实施方式涉及在具有高电子迁移率的薄膜晶体管中沉积层的方法。

4.现有技术描述

5.薄膜晶体管(tft)是用于集成电路和显示器中以控制像素操作的金属氧化物层半导体器件。由于tft具有高分辨率、低功耗和用于lcd和oled显示器的高速操作,因此在显示应用中引起了极大的兴趣。由于相对于彼此和相对于tft的金属氧化物层沉积层的方法,在构成tft的层中使用的当前材料通常具有有限的电子迁移率。

6.因此,本领域需要改进的tft和制造tft的方法。特别地,需要绝缘层,诸如用于具有较低氢含量、较高密度、较低湿蚀刻速率和较低等离子体损伤的tft的钝化层和蚀刻停止层。

技术实现要素:

7.在一个实施方式中,提供了一种形成薄膜晶体管的方法,包括在基板之上沉积缓冲层和在缓冲层之上形成栅极层。蚀刻栅极层的一部分以形成栅极电极并且在缓冲层和栅极电极之上沉积栅极绝缘(gi)层。在gi层之上沉积金属氧化物层。使用电感耦合等离子体(icp)的高密度等离子体化学气相沉积(hdp cvd)在金属氧化物层之上沉积钝化层。高密度等离子体包括大于1.0e11/cm3的电子或离子等离子体密度。

8.在另一个实施方式中,提供了一种制造薄膜晶体管的方法,包括在基板之上沉积缓冲层和至少部分地在缓冲层之上形成栅极层。在缓冲层和栅极层之上沉积栅极绝缘(gi)层,并且在gi层之上沉积金属氧化物层。使用电感耦合等离子体(icp)的高密度等离子体化学气相沉积(hdp cvd)沉积蚀刻停止层,并在蚀刻停止层中形成源极电极和漏极电极。使用诸如hdp cvd的基于电感耦合等离子体(icp)或基于电容耦合(ccp)的化学气相沉积工艺在上面沉积钝化层。

9.在另一个实施方式中,提供了一种方法,包括在基板上形成低温多晶硅薄膜晶体管(ltps tft)和在基板上形成金属氧化物薄膜晶体管(mo tft)。mo tft包括金属氧化物沟道层。通过使用icp的hdp cvd在mo tft的金属氧化物沟道层和ltps tft的层之上沉积氧化硅层。hdp包括大于1.0e11/cm3的电子或离子等离子体密度。

附图说明

10.为了可详细地理解本公开内容的上述特征的方式,可参考实施方式来得到以上简要地概述的本公开内容的更特别的描述,其中一些实施方式示出在附图中。然而,需注意,附图仅示出了示例性实施方式,并且因此不应视为对本公开的范围的限制,并且可允许其他等效实施方式。

11.图1是根据一实施方式的腔室的示意性截面图。

12.图2a-图2h是根据一实施方式的在制造的各个阶段的金属氧化物tft的示意性截面图。

13.图2i是根据一实施方式的具有钝化层的金属氧化物tft的示意性截面图。

14.图3是根据一实施方式的具有两个钝化层的金属氧化物tft的示意性截面图。

15.图4是根据一实施方式的具有蚀刻停止层(esl)和钝化层的金属氧化物tft的示意性截面图。

16.图5是根据一实施方式的具有两个蚀刻停止层和钝化层的金属氧化物tft的示意性截面图。

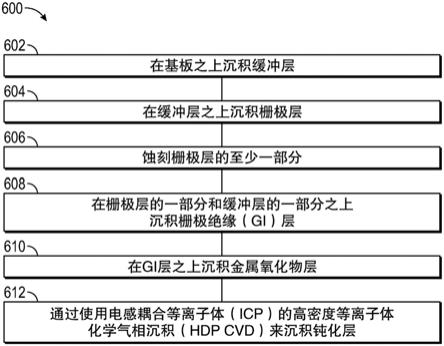

17.图6是根据一实施方式的制造mo tft结构的示例方法的流程图。

18.图7a-图7g是根据一实施方式的在制造的各个阶段的金属氧化物tft和低温多晶硅(ltps)tft的示意性截面图。

19.图7g是根据一实施方式的具有钝化层的mo tft和ltps tft的示意性截面图。

20.图8是根据一实施方式的具有钝化层和蚀刻停止层的mo tft和ltps tft的示意性截面图。

21.图9是根据一实施方式的具有钝化层的mo tft和ltps tft的示意性截面图。

22.图10是根据一实施方式的具有蚀刻停止层和钝化层的mo tft和ltps tft的示意性截面图。

23.图11是根据一实施方式的示例电感耦合等离子体(icp)高密度等离子体(hdp)工艺的流程图。

24.为了便于理解,在可能的情况下使用相同的附图标记来表示附图共有的相同元件。可以预期,一个实施方式的元素和特征可以有益地合并到其他实施方式中,而无需进一步叙述。

具体实施方式

25.本公开内容一般涉及一种制造tft的方法。tft具有包括诸如氧化铟镓锌(igzo)和/或氧化锌的金属氧化物的有源沟道。一个或多个钝化层和/或一个或多个蚀刻停止层(esl)设置在金属氧化物之上。金属氧化物与设置在金属氧化物之上的层之间的界面提供了用于在一些tft的应用中的预定tft特性。特别地,在金属氧化物之上处理和沉积层的方法影响tft特性。

26.本文提供了制造薄膜晶体管(tft)的方法,包括使用电感耦合等离子体高密度等离子体工艺在金属氧化物沟道层之上沉积一层,以提高金属氧化物沟道层和/或mo沟道层和通过使用电感耦合等离子体的高密度等离子体化学气相沉积所沉积的层的界面的电子迁移率。如本文所用,术语“高密度等离子体”是指密度大于的电子或离子等离子体,其中高密度等离子体包括大于1.0e11/cm3的电子或离子等离子体密度。沉积工艺包括用n2o气体或用n2o气体和氩气预处理金属氧化物层,激发气体形成电感耦合等离子体,然后引入sih4气体沉积包含氧化硅的界面层。界面层为蚀刻停止层,或者界面层为tft结构的钝化层。

27.图1是可用于实施本文描述的实施方式的腔室100的示意性截面图。合适的腔室可以从位于加利福尼亚州圣克拉拉市的应用材料公司获得。应该理解,下面描述的腔室是示

例性的腔室,并且包括来自其他制造商的腔室的其他腔室可以一起使用或修改以完成本公开内容的各方面。腔室100被配置为产生电感耦合高密度等离子体。

28.腔室100包括腔室主体104、盖组件106和基板支撑组件108。盖组件106设置在腔室主体104的上端。基板支撑组件108至少部分设置在腔室主体104的内部空间内。基板支撑组件108包括基板支撑件110和从基板支撑件110延伸的轴112。基板支撑件110具有用于支撑至少一个基板102的支撑表面114。在可以与本文描述的其他实施方式组合的一个实施方式中,基板102是大面积基板,诸如是具有表面积通常为约1平方米或更大的基板。然而,基板102不限于任何特定尺寸或形状。在一个方面,术语“基板”是指任何多边形、正方形、矩形、弯曲或其他非圆形工件。

29.盖组件106包括扩散器116,所述扩散器116跨腔室主体104的上端的至少一部分延伸。一个或多个气体入口118通过盖组件耦接以连通来自至少一个气源120的处理气体到扩散器116。来自气源120的一种或多种气体流过扩散器116并进入位于扩散器116与基板支撑件110之间的处理区域124。通过面对扩散器116的一侧的处理区域124中的多个孔或开口(未示出)将一种或多种气体提供给处理区域124。流量控制器122(例如质量流量控制(mfc)装置)设置在每个扩散器入口118与气源之间120以控制气体从气源120到扩散器116的流速。在可以与本文描述的其他实施方式组合的一个实施方式中,扩散器116由陶瓷材料组成,诸如是al2o3。泵126与腔室的内部空间流体连通并因此与处理区域124流体连通。泵126可与质量流量控制器122结合操作以控制处理区域124内的压力并排出来自处理区域124的气体和副产物。

30.这里,盖组件106包括至少一个凹部128,所述凹部128从所述凹部128的上外表面向内延伸,具有位于其中并支撑在至少一个介电板132之上的一个或多个电感耦合等离子体生成部件、线圈130。每个介电板132提供处理区域124与腔室100的外部之间的物理屏障,并且具有承受结构负载所需的结构强度,该结构负载在凹部128中存在大气压力并且在腔室主体104的内部空间中存在真空压力所产生。每个线圈130连接到功率源134和接地138。在可以与本文描述的其他实施方式组合的一个实施方式中,每个线圈130通过匹配盒136连接到功率源134,所述匹配盒136具有用于调整线圈130的电特性(诸如阻抗)的匹配电路,以“匹配”形成在处理区域124中的等离子体的电特性。每个线圈130被配置为在处理区域内产生电磁场,该电磁场将处理区域124中的气体激发成电感耦合高密度等离子体。控制器158耦接到腔室100并且被配置为在处理期间控制腔室100的各方面。

31.图2a-图2i是根据一实施方式的在各个制造阶段的金属氧化物(mo)tft200的示意图。如图2a所示,通过在基板102之上首先沉积缓冲层202来制造tft 200。基板102可以包括任何合适的材料,诸如是玻璃、钠钙玻璃、聚合物和用于制造平板显示器中的半导体。合适的基板102包括硅基基板、绝缘基基板、锗基基板、以及通常存在于cmos结构中的一个或多个通用层。应当理解,其他材料也被考虑在内。缓冲层202通过物理气相沉积或其他合适的沉积方法形成,诸如是原子层沉积(ald)、化学气相沉积(cvd)或等离子体增强化学气相沉积(pecvd)。在可以与本文描述的其他实施方式组合的一些实施方式中,缓冲层202使用电容耦合等离子体(ccp)或通过高密度等离子体(hdp)共形地形成,诸如腔室100中的电感耦合高密度等离子体,如参考图1所描述的。缓冲层202由一材料组成,所述材料包括p型硅(例如掺硼硅)、金属氮化物(例如氮化铝或氮化钨)、金属氧化物(例如氧化钒)或它们的组合。

在可以与本文描述的其他实施方式组合的一些实施方式中,缓冲层202包括氧化硅(sio

x

)、氮化硅(si

x

ny)和它们的组合中的至少一种。除非另有说明,否则tft的任何层可以使用工业中已知的和/或本文所述的任何合适的沉积方法来沉积。

32.如图2b所示,在缓冲层202之上沉积栅极层203。用于栅极层203的合适材料包括铬、钼、铜、铝、钨、钛和它们的组合。栅极层203可以通过物理气相沉积(pvd)或其他合适的沉积方法形成,诸如是电镀、化学镀或化学气相沉积(cvd)。如图2c所示,图案化栅极层203以形成栅极电极204。图案化包括在栅极层203之上形成光刻掩模或硬掩模(未示出)并将栅极层203暴露于本文中提及的蚀刻剂作为“蚀刻”。取决于栅极层203中使用的材料,通过将栅极层203未被掩模覆盖的部分暴露于湿蚀刻剂,或者通过将栅极层203的未被掩模覆盖的部分暴露于蚀刻等离子体来图案化栅极层203。在可以与本文描述的其他实施方式组合的一些实施方式中,通过用蚀刻等离子体蚀刻栅极层203未被掩模覆盖的部分来图案化栅极层203,所述等离子体包括六氟化硫气体、氧气、氯气、或它们的组合。所描述的蚀刻等离子体和蚀刻工艺可用于本文所述的任何层的任何图案化和蚀刻。

33.如图2d所示,栅极绝缘(gi)层206沉积在栅极电极204之上。gi层206使用本文描述的和行业中已知的任何沉积方法形成。在可以与本文描述的其他实施方式组合的一些实施方式中,gi层206使用hdp cvd或ccp cvd形成。在ccp中,提供了相对的电极,诸如平行板电极,电极中的一个耦接接地,而另一个耦接到功率源,并且在它们之间引入气体以形成实际上的电容器。通过为通电电极供电,电能电容耦合到气体中以形成所述气体的等离子体。等离子体的离子密度是传送到气体中的功率的函数。相比之下,在icp等离子体中,线圈围绕或在将要形成等离子体的气体区域之上,流过线圈的电能电磁耦合到气体中,以电离或以其他方式激发气体原子或分子。同样,等离子体离子密度是耦合到气体中的能量的函数。在ccp系统中,电极中的一个通常也是基板支撑件,因此可以耦合到气体中的功率受到该功率对基板的潜在负面影响的限制。相比之下,使用icp布置,将气体原子和分子电离的功率与固定基板的电路部件去耦合,可以使用更高的功率将更高的能量赋予给等离子体,从而在等离子体中实现更高的离子密度,而不会对基板产生不利影响。

34.如图2e所示,诸如金属氧化物(mo)层207之类的有源层设置在gi层206之上。mo层207通过诸如物理气相沉积(pvd)之类的合适沉积方法来沉积。mo层207使用本文所述的任何图案化方法来图案化,诸如通过湿蚀刻工艺。在可以与本文描述的其他实施方式组合的一个实施方式中,mo沟道层208包括氧(o)和以下的至少一种:铟(in)、锌(zn)、镓(ga)、氧(o)、锡(sn)、铝(al)和铪(hf)。mo沟道层208的示例包括但不限于ingazno、inzno、ingasno、inznsno、ingaznsno、insno、hfinzno、gazno、ino、alsnzno、zno、znsno、alzno、alznsno、hfzno、sno和alsnznino。用于mo层207的合适材料包括igzo和/或氧化锌。如图2f所示,通过蚀刻图案化mo层207以形成mo沟道层208。任何mo层和/或mo沟道层可以是1114mol%的ingazno层。

35.如图2g所示,金属层210通过物理气相沉积(pvd)或其他合适的沉积方法形成在mo沟道层208和暴露的gi层206之上,所述其他合适的沉积方法诸如是电镀、化学镀或化学气相沉积(cvd)。除非另有规定,否则pvd、电镀、化学镀或cvd的任何工艺均可用于本文所述的任何金属层。然后图案化金属层210以形成源极电极210a和漏极电极210b,以及形成在它们之间的开口211。使用本文所述的任何合适的方法图案化金属层210,诸如是背沟道蚀刻

(bce)工艺。除非另有说明,否则本文所述的源极电极、漏极电极和栅极电极中的每一个可包括导电材料,诸如是铜、钛、钽或任何导电金属。应当理解,其他材料也被考虑在内。

36.mo沟道层208之上的开口211暴露出mo沟道层208在mo沟道层208底部的一部分。如图2i所示,通过使用电感耦合等离子体的hdp cvd工艺,在mo沟道层208、暴露的gi层206以及源极电极210a和漏极电极210b之上形成钝化层212。在图2a至图2i示出和描述的工艺公开了被钝化层覆盖的栅极的实施方式的制造。在形成源极电极和漏极电极之后,但在源极电极和漏极电极上沉积钝化或蚀刻停止层之前,在使用icp进行hdp cvd工艺之前,对开口211内的mo沟道层208进行预处理。mo沟道层208的顶表面和/或mo沟道层208与将在mo沟道层208上沉积的层(例如,esl或钝化层)之间的界面被认为被化学改性以具有高电子迁移率。

37.本文参考图11描述了使用电感耦合等离子体的hdp cvd工艺的操作顺序。钝化层(例如,212)通常是tft装置的最顶层,以保护装置免受环境损害,包括化学或机械诱导的损害。钝化层还提供稳定可靠的tft性能,以抵抗长期的热和电偏置应力。由于金属氧化物层对氢和其他环境化学品的敏感性,因此提供高质量、低含氢的氧化物,诸如本文所述的硅氧化物作为钝化层212。特别是,在钝化层直接设置在栅极的金属氧化物层之上并接触栅极的金属氧化物层的实施方式中,使用电感耦合等离子体的hdp cvd工艺提供与由其他形式的沉积产生的氧化硅相比具有低氢含量的氧化硅组合物。尽管钝化层212在图2i中被描绘为单层,但是设想了多个钝化层,并且参考本文描述的图3提供一个这样的示例。

38.图3描绘了使用ccp cvd工艺在源极电极210a和漏极电极210b以及mo沟道层208的一部分之上形成的第一钝化层302,接着是使用电感耦合等离子体的hdp cvd工艺沉积的第二钝化层304,以形成底栅tft 300。这里,由于在tft的最外层或最上层上形成的第二钝化层304是使用hdp cvd工艺使用电感耦合等离子体形成的,因此它具有高质量、稳定和低氢含量组成,能够保护mo沟道层免受环境破坏并增强mo沟道中的电子迁移率。在可以与本文描述的其他实施方式组合的一些实施方式中,在使用ccp cvd沉积第一钝化层302之前,使用电容耦合等离子体预处理mo沟道层208。第一钝化层302具有小于100nm的厚度。第二钝化层304具有约10nm至约300nm的厚度。不受理论束缚,相信在第一钝化层302之上沉积第二钝化层304能够增加设置在第一钝化层302下方的mo沟道层208的电子迁移率。

39.图4描绘了具有沉积在栅极绝缘层206和栅极电极204之上的蚀刻停止层402的底栅tft 400的实施方式。蚀刻停止层402使用电感耦合等离子体通过hdp cvd工艺沉积,然后被图案化以使用本文所述的形成源极电极和漏极电极的任何方法形成源极电极410a和漏极电极410b。

40.钝化层404沉积在源极电极410a和漏极电极410b之上以及在蚀刻停止层402之上。钝化层404使用本文公开的任何沉积方法沉积,诸如ccp cvd或hdp cvd。图5描绘了底栅tft 500的实施方式,具有通过使用ccp cvd沉积工艺沉积的第一蚀刻停止层502,接着是通过使用电感耦合等离子体的hdp cvd工艺沉积的第二蚀刻停止层504。源极电极510a和漏极电极510b形成在第一蚀刻停止层502和第二蚀刻停止层504中。钝化层506使用本文公开的任何方法沉积在其上,诸如通过ccp cvd,或者通过使用电感耦合等离子体的hdp cvd工艺。

41.图6是根据一实施方式的制造mo tft结构的示例性方法的流程图。在操作602中,在基板(例如,102)之上形成缓冲层(例如,202)。在操作604中,在缓冲层之上沉积栅极层

(例如,203),并且在操作606中,蚀刻栅极层的至少一部分以形成栅极电极(例如,204)。在操作608中,在栅极电极之上沉积gi层(例如,206),并且在操作610中,在gi层之上形成图案化的金属氧化物层(例如,208)。在操作612中,使用电感耦合等离子体的hdp cvd在图案化金属氧化物层之上沉积钝化层或蚀刻停止层。

42.图7a-图7g是根据一实施方式的在制造的各个阶段的mo tft730和ltps tft 720(统称为tft 700)的示意性截面图。第一缓冲层702以与参考图2a所述类似的方式形成在基板102之上。在缓冲层702之上沉积硅层,然后使用本文所述的任何方法蚀刻以形成低温多晶硅(ltps)层704。在所述低温多晶硅层704上沉积gi层706并且使用本文描述图案化方法形成栅极708。层间介电(ild)层710沉积在gi层706和栅极708之上。用于ild层的合适材料包括氮化硅、氧化硅和氮氧化硅。此外,虽然显示为单层,但预期ild层710可包括多层,每一层可包括不同的化学成分。使用本文所述的任何方法沉积ild层,所述方法诸如是使用hdp cvd或ccp cvd。ild层710的一部分和gi层706的一部分被向下蚀刻到ltps层704以形成第一下开口711a和第二下开口711b。形成第一金属层713(如图7b所示)。如图7c所示,第一金属层713被图案化以形成ltps tft 720的下源极通孔712a、中间源极电极焊盘712c、中间漏极电极焊盘712d和下漏极通孔712b。此外,第一金属层713被图案化以形成mo tft 730的栅极电极714。

43.关于ltps tft 720,下源极通孔712a向上延伸到中间源极电极焊盘712c,并且下漏极通孔712b向上延伸到中间漏极电极焊盘712d。如图7d所示,然后在上面形成第二缓冲层716。如图7e所示,金属氧化物层717沉积在第二缓冲层716之上,并且在图7f中,金属氧化物层717的一部分被图案化以形成mo tft 730的mo沟道层718。第二缓冲层716被图案化以形成向下延伸至中间源极电极焊盘712c的第一上开口721a以及向下延伸至ltps tft 720的中间漏极电极焊盘712d的第二上开口721b。沉积并图案化第二金属层(未示出)以形成从中间源极电极焊盘712c延伸到上源极电极焊盘722c的上源极通孔722a和从中间漏极电极焊盘712d延伸到ltps tft 720的上漏极电极焊盘722d的上漏极电极通孔722b,如图7g所示。下源极通孔712a、中间源极电极焊盘712c、上源极通孔722a和上源极电极焊盘722c一起形成源极电极742a。下漏通孔712b、中间漏极电极焊盘712d、上漏极电极通孔722b和上漏极电极焊盘722d一起形成ltps tft 720的漏极电极742b。

44.mo tft源极电极732a和mo tft漏极电极732b形成在mo tft730的mo沟道层718之上。钝化层724通过使用电感耦合等离子体的hdp cvd工艺沉积以形成结构700的mo tft 730和ltps tft 720。

45.图8是根据一实施方式的包括具有钝化层804和蚀刻停止层802的mo tft830和ltps tft820的tft结构800的示意性截面图。tft结构800的层以与图7a-图7e所示类似的方式沉积。蚀刻停止层802通过使用电感耦合等离子体的hdp cvd工艺沉积在mo tft830的mo沟道层718之上。图案化蚀刻停止层802并且形成从mo沟道层718延伸到mo tft源极电极焊盘832c的mo tft源极电极通孔832a。mo tft漏极电极832b形成为从mo沟道层718延伸到mo tft830中的mo tft漏极焊盘832d。钝化层804通过ccp cvd或通过hdp cvd沉积。

46.参考图8中描绘的ltps tft820,形成从中间源极电极焊盘712c延伸到上源极电极焊盘822c的上源极电极通孔822a,并且形成从中间漏极电极焊盘712d延伸到ltps tft820的上漏极电极焊盘822d的上漏极电极通孔822b。下源极通孔712a、中间源极电极焊盘712c、

上源极通孔822a和上源极电极焊盘822c一起形成源极电极842a。下漏极通孔712b、中间漏极电极焊盘712d、上漏极电极通孔822b和上漏极电极焊盘822d一起形成ltps tft820的漏极电极842b。

47.图9是根据一实施方式的包括具有钝化层906的mo tft 930和ltps tft 920的tft结构900的示意性截面图。tft结构900的层702、706、708和710以参考图7a描述的方式形成。在与ltps栅极708相同的平面上,mo tft栅极908形成在mo tft 930中。ild层710形成在上面,并且第二缓冲层902形成在ild层710之上。源极电极922a和漏极电极922b形成在第二缓冲层902、ild层710和延伸到ltps tft920的ltps层704的gi层706中。源极电极932a和漏极电极932b形成在mo tft930中的金属氧化物层904周围。钝化层906通过使用电感耦合等离子体的hdp cvd形成在上面。已经发现,可以形成包括p型ltps tft和n型mo tft的互补结构,适用于诸如半导体基的电路的应用。常规n型mo tft结构包括具有小于30cm2/vsec,诸如约10cm2/vsec的电子迁移率的mo沟道层。相比之下,常规的p型ltps tft结构包括具有约80cm2/vsec至约100cm2/vsec的电子迁移率的层。因此,本公开内容已经发现通过使用本文描述的方法增加mo tft结构的mo沟道层中的电子迁移率来改善ltps tft结构和mo tft结构之间的电子迁移率差异。本公开内容的mo沟道层的电子迁移率大于30cm2/vsec,诸如大于50cm2/vsec,诸如约80cm2/vsec至约100cm2/vsec,或约100cm2/vsec至约400100cm2/vsec。此外,与形成包括ltps tft和mo tft的结构的常规方法相比,本文描述的方法使用更少的掩模。

48.图10是根据一实施方式的具有蚀刻停止层(esl)1006和钝化层1008的mo tft1030和ltps tft1020(统称为tft结构1000)的示意性截面图。在tft结构1000中,第二缓冲层1002形成在ild层710之上。mo沟道层1004形成在esl 1006中,并且esl 1006使用电感耦合等离子体的hdp cvd工艺形成。源极电极1022a和漏极电极1022b形成在ltps tft1020中,源极电极1032a和漏极电极1032b形成在mo tft1030中。钝化层1008通过ccp cvd或hdp cvd形成。在可以与本文描述的其他实施方式组合的一些实施方式中,mo tft的mo沟道层设置在与ltps tft的栅极相同的平面内。在可以与本文描述的其他实施方式组合的一些实施方式中,mo tft的mo沟道层设置在与ltps tft的栅极电极不同的平面中。在其一些方面,mo沟道层可以在通过使用icp的hdp cvd在mo沟道层之上沉积层之前经历预处理工艺。图11的方法1100中示出了示例预处理和沉积工艺并且总结在下面的表1中。

49.表1:通过使用icp工艺的hdp cvd预处理和沉积示例

[0050][0051]

图11的操作1102包括使用预处理气体对其膜层进行预处理的预处理工艺。在图11的操作1102中,预处理气体包括一氧化二氮气体、氩气或含氧气和氩气的组合到处理腔室的处理区域124。含氧气体为n2o气体、no气体、o2气体、o3气体中的一种或多种,诸如n2o气体。

[0052]

在操作1102之前,基板102被定位在处理区域124内以在扩散器116与基板102之间提供约100mm到约300mm的间距。引入预处理气体包括以约0.3sccm/cm2至约0.7sccm/cm2引入n2o气体和以约0sccm/cm2至约0.7sccm/cm2引入氩气。如本文所用,单位“sccm/cm

2”是指每平方厘米基板表面积的标准立方厘米体积气体流量。引入处理空间的预处理气体包括按体积计约1:0至约1:2,诸如约3:1至约1:1的n2o气与氩气之比。在可以与本文描述的其他实施方式组合的一些实施方式中,氩气不与n2o气体一起使用。

[0053]

处理空间的预处理处理压力为约10mt至约150mt,诸如约12mt至约120mt。基板的预处理处理温度为约70℃至约350℃,诸如约70℃至约250℃,且预处理处理时间为约5秒至约60秒,诸如约10秒至约40秒。在可以与本文描述的其他实施方式组合的一些实施方式中,预处理气体在被激发为等离子体之前被引入到处理空间中。

[0054]

在操作1104中,提供等离子体预处理,包括以约1mhz至约30mhz、诸如约2mhz至约15mhz的频率供应的icp线圈能量激发处理空间内的预处理气体。在可以与本文描述的其他实施方式组合的一些实施方式中,表1和操作1104中描述的等离子体处理条件用于在操作1102之后预处理mo沟道层。或者,可以使用在操作1104中提供的条件预处理mo沟道层而不使用参考操作1102提供的条件进行预处理。已经发现,低icp线圈频率减少了与激发等离子体相关的损坏,增加了均匀性,并减少了能量消耗。高等离子体能量频率、诸如用于微波化学气相沉积,在微波化学气相沉积的工艺中使用频率超过100mhz、诸如100ghz的功率。高频可用于本文所述的hdp工艺,然而,约1mhz至约30mhz、诸如约2mhz至约15mhz的icp线圈频率激发预处理气体以产生等离子体。激发预处理气体包括以约2.3w/cm2至约5.3w/cm2的功率密度提供电力。如本文所用,术语“功率密度”是指每平方厘米暴露的基板表面积提供的电功率量。基板的温度维持在约70℃至约350℃,诸如约70℃至约250℃。等离子体预处理时间

为约2秒至约32秒。在可与本文描述的其他实施方式组合的一些实施方式中,在如本文所述沉积氧化硅层之前,将预处理气体转化为原位形成的等离子体。或者,等离子体在异位形成并被引入到处理空间中。相信等离子体预处理工艺增强了金属氧化物tft在热偏置应力下的特性和性能。在形成蚀刻停止层和/或钝化层之前执行等离子体预处理。在可与本文描述的其他实施方式组合的一些实施方式中,气体流速、功率密度和频率的所述范围的组合产生低等离子体密度,这足以制备用于后续氧化硅层沉积的暴露膜表面,并提供损坏部分制造的tft结构的低电位和低离子轰击。

[0055]

在操作1106中,以约0.02sccm/cm2至约0.09sccm/cm2引入硅烷(sih4)气体以形成氧化硅界面(例如,与mo沟道层界面连接的esl或钝化层)。在可与本文描述的其他实施方式组合的一些实施方式中,在按体积计以约5:1至约40:1的n2o气流与sih4气流的比率添加sih4气体期间和之后维持操作1104中的等离子体条件。在一些实施方式中,mo沟道层不暴露于操作1102和1104中描述的预处理工艺。特别地,将如表1的“沉积”列中描述的操作1106的工艺条件应用于mo沟道层而不预处理。处理区域124的空间压力维持在约80mt至约12mt。sih4气体被引入约26秒至约260秒。氧化硅界面层(例如,钝化层或esl)形成为具有约200埃至约2000埃的厚度,诸如约500埃至约2000埃。基于原子百分比,通过使用电感耦合等离子体的hdp cvd产生的氧化硅界面层在250℃下的氢含量为约1.9%,而由ccp产生的界面层在250℃下的氢含量为约3.5%。额外的操作(例如,表1中描述的后沉积列)包括退火约5秒到约15秒,以维持约70℃到约250℃的温度。不受理论束缚,相信暴露的mo沟道层的顶表面和/或mo沟道层与通过使用icp的hdp cvd沉积在上面的层之间的界面通过操作1102、操作1104、操作1106和后沉积操作的一种或多种来化学和/或物理改性。相信通过增加mo沟道层中和/或mo沟道层与沉积在mo沟道层之上的层之间的界面处的电子载流子密度来实现高电子迁移率。mo沟道层的迁移率大于30cm/vsec,诸如大于60cm/vsec。

[0056]

例子

[0057]

示例性氧化硅沉积工艺在表2中提供并总结。

[0058]

表2:用于使用icp的hdp cvd的示例工艺条件

[0059][0060][0061]

使用表2中总结的工艺条件形成其中沉积有氧化硅层的几个tft样品。可以看出,沉积的每一层提供低于2600埃/分钟的湿蚀刻速率(wer),即使在低基板处理温度,例如80

℃和85℃。wer性能明显优于其他沉积形式的典型wer,典型wer通常高于4000,或高于6000,或高于8000埃/分钟。wer值标准化为热氧化物wer,热氧化物wer为1000a/min。发现si-o峰位在约100℃至约300℃的宽温度范围内始终处于高位,这表明在宽范围内具有高的膜质量和可控性。列“间距”由扩散器和基板之间的距离(以密耳为单位)定义。

[0062]

另外,对于使用电感耦合等离子体的hdp cvd沉积的示例膜,测量氢浓度和膜密度。特别是在低温下,氢含量比使用其他工艺通常发现的氢含量低得多。其他工艺通常具有大于5%的氢浓度,例如在低于150℃的温度下为约6%。在使用电感耦合等离子体的hdp cvd沉积的示例膜中测量的氢浓度在约120℃时为约2.7%,在约225℃时为1.8%,在约340℃时为1.7%。使用电感耦合等离子体的hdp cvd沉积的示例膜的膜密度在约250℃下具有约2.3g/cm3的膜密度,通过x射线反射率测量,高于由其他沉积所沉积的氧化硅膜的典型膜密度。这些膜在约250℃时的膜密度为2.2g/cm3或更低。

[0063]

与互补金属氧化物半导体(cmos),诸如p型多晶硅+n型多晶硅结构相比,本文所述的tft结构使用p型ltps tft和n型mo tft减少了形成具有改进的性能、稳定性和电子迁移率的tft结构所需的掩模数量。

[0064]

总之,提供了制造薄膜晶体管(tft)的方法,包括使用电感耦合等离子体高密度等离子体工艺在金属氧化物层之上沉积界面层以提高电子迁移率。沉积工艺包括用n2o气体或用n2o气体和氩气预处理金属氧化物层,激发气体形成电感耦合等离子体,然后引入sih4气体以沉积包含氧化硅的界面层。界面层为蚀刻停止层,或者界面层为tft结构的钝化层。

[0065]

虽然以上涉及本公开内容的示例,但是在不脱离其基本范围的情况下可以设计本公开内容的其他和进一步的示例,并且本公开内容的范围由随附权利要求书确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1