半导体封装、电子装置及半导体封装的制造方法与流程

半导体封装、电子装置及半导体封装的制造方法

1.关联申请的相互参照

2.本技术基于2019年7月10日提出的日本专利申请第2019-128693号和2020年6月30日提出的日本专利申请第2020-113132号,这里通过参照而引用其记载内容。

技术领域

3.本发明涉及将半导体芯片用密封部件密封的半导体封装、电子装置及半导体封装的制造方法。

背景技术:

4.以往,提出了将半导体芯片用密封部件密封的半导体封装(例如参照专利文献1)。具体而言,该半导体封装中,半导体芯片被由玻璃环氧树脂等构成的密封部件密封。

5.现有技术文献

6.专利文献

7.专利文献1:美国专利申请公开第2016/020471号说明书

技术实现要素:

8.但是,在将上述半导体封装搭载在车辆中使用的情况下,本发明者们研究确认到,有可能密封部件中导入裂纹而损坏。即,作为车载用的零件,上述半导体封装有可能耐久性较低。

9.本发明的目的在于,提供能够抑制损坏的半导体封装、电子装置及半导体封装的制造方法。

10.根据本发明的一技术方案,半导体封装具备半导体芯片、搭载半导体芯片的散热部件和将半导体芯片密封的密封部件,密封部件由液晶聚合物构成。

11.由此,密封部件由液晶聚合物构成,液晶聚合物是与玻璃环氧树脂相比材料强度高且柔软的材料。因此,能够抑制在密封部件中被导入裂纹,能够抑制半导体封装的损坏。

12.此外,根据本发明的另一技术方案,电子装置具备半导体封装、与半导体封装中的散热部件连接的冷却器、以及与半导体封装的焊盘电连接的被安装部件。

13.这样,还能够使用半导体封装构成电子装置。并且,通过配置与散热部件连接的冷却器,能够进一步实现散热性的提高。

14.此外,根据本发明的另一技术方案,半导体封装的制造方法进行以下工序:准备用切割线将多个构成散热部件的部分进行了划分的构成基板;准备半导体芯片;在构成基板的构成散热部件的部分上,经由接合部件配置半导体芯片;在构成基板上,配置收容半导体芯片的密封构成部件;在构成基板与半导体芯片的层叠方向上一边加压一边加热,从而使密封构成部件成为将半导体芯片中的与和接合部件接合的部分不同的部分密封并与散热部件接合的密封部件;沿着切割线进行分割;作为密封构成部件,使用由液晶聚合物构成的部件。

15.由此,制造出抑制了在密封部件中导入裂纹的半导体封装。

16.另外,对于各构成要素等赋予的带括号的标记表示该构成要素等与后述实施方式所记载的具体构成要素等的对应关系的一例。

附图说明

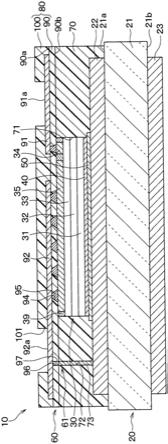

17.图1是第1实施方式的半导体封装的剖视图。

18.图2是图1所示的半导体芯片的剖视图。

19.图3是图1所示的半导体芯片的平面图。

20.图4a是将图1所示的半导体封装的散热部件从散热部件的一面侧观察的平面图。

21.图4b是将图1所示的半导体封装的半导体芯片及侧面密封部件从散热部件的一面侧观察的平面图。

22.图4c是将图1所示的半导体封装的第1密封部件从散热部件的一面侧观察的平面图。

23.图4d是将图1所示的半导体封装的第1密封部件及第2密封部件从散热部件的一面侧观察的平面图。

24.图5a是表示图1所示的半导体封装的制造工序的剖视图。

25.图5b是表示接着图5a的导体封装的制造工序的剖视图。

26.图5c是表示接着图5b的导体封装的制造工序的剖视图。

27.图5d是表示接着图5c的导体封装的制造工序的剖视图。

28.图5e是表示接着图5d的导体封装的制造工序的剖视图。

29.图5f是表示接着图5e的导体封装的制造工序的剖视图。

30.图5g是表示接着图5f的导体封装的制造工序的剖视图。

31.图6是表示构成基板的平面图。

32.图7是第2实施方式的半导体封装的剖视图。

33.图8a是表示第2实施方式的半导体封装的制造工序的剖视图。

34.图8b是表示第2实施方式的半导体封装的制造工序的剖视图。

35.图9是第3实施方式的半导体封装的剖视图。

36.图10a是将第4实施方式的半导体封装的散热部件从散热部件的一面侧观察的平面图。

37.图10b是将第4实施方式的半导体封装的半导体芯片及侧面密封部件从散热部件的一面侧观察的平面图。

38.图10c是将第4实施方式的半导体封装的第1密封部件从散热部件的一面侧观察的平面图。

39.图11是表示第4实施方式的半导体封装的连接通孔与半导体芯片的关系的示意图。

40.图12a是将第5实施方式的半导体封装的散热部件从散热部件的一面侧观察的平面图。

41.图12b是将第5实施方式的半导体封装的半导体芯片及侧面密封部件从散热部件的一面侧观察的平面图。

42.图12c是将第5实施方式的第1密封部件从散热部件的一面侧观察的平面图。

43.图13是第6实施方式的半导体封装的剖视图。

44.图14是第7实施方式的半导体封装的剖视图。

45.图15是表示将图14所示的半导体封装安装于印刷基板的状态的剖视图。

46.图16是第8实施方式的半导体封装的剖视图。

47.图17是第9实施方式的半导体封装的剖视图。

48.图18是第10实施方式的半导体封装的剖视图。

49.图19是第11实施方式的半导体封装的剖视图。

50.图20是图19中的下层板状部件中的位于半导体封装的下方的部分的平面示意图。

51.图21是第12实施方式的半导体封装的剖视图。

52.图22是图21中的下层板状部件中的位于半导体封装的下方的部分的平面示意图。

53.图23是第13实施方式的半导体封装的剖视图。

54.图24是第13实施方式的变形例的半导体封装的剖视图。

55.图25是第14实施方式的半导体封装的剖视图。

56.图26是第15实施方式的半导体封装的剖视图。

57.图27是第16实施方式的半导体封装的剖视图。

58.图28是第17实施方式的半导体封装的剖视图。

59.图29是第18实施方式的半导体封装的剖视图。

60.图30是第19实施方式的半导体封装的剖视图。

61.图31是第20实施方式的半导体封装的剖视图。

62.图32是第21实施方式的半导体封装的剖视图。

63.图33是第22实施方式的半导体封装的平面图。

64.图34是第23实施方式的半导体封装的平面图。

65.图35是第24实施方式的半导体封装的平面图。

66.图36是第24实施方式的半导体封装的平面图。

67.图37是第25实施方式的半导体封装的剖视图。

68.图38是第26实施方式的半导体封装的剖视图。

69.图39是第27实施方式的半导体封装的剖视图。

70.图40a是表示第27实施方式的半导体封装的制造工序的剖视图。

71.图40b是表示接着图40a的半导体封装的制造工序的剖视图。

72.图41是用来说明第1实施方式的制造方法的课题的图。

73.图42是表示第28实施方式的半导体封装的制造工序的构成基板的平面图。

74.图43是表示第29实施方式的半导体封装的制造工序的剖视图。

75.图44a是表示第30实施方式的板状部件构成部件的制造工序的示意图。

76.图44b是表示接着图44a的板状部件构成部件的制造工序的示意图。

77.图44c是表示接着图44b的板状部件构成部件的制造工序的示意图。

78.图45a是表示加热处理前的lcp膜构成部件的内部状态的图。

79.图45b是表示加热处理前的lcp膜构成部件的内部状态的图。

80.图46是表示第31实施方式的电子装置的剖视图。

81.图47是表示第32实施方式的电子装置的剖视图。

82.图48是表示第33实施方式的电子装置的剖视图。

83.图49是将其他实施方式的半导体封装的第1密封部件从散热部件的一面侧观察的平面图。

84.图50是其他实施方式的半导体封装的剖视图。

85.图51是其他实施方式的半导体封装的剖视图。

86.图52是其他实施方式的半导体封装的剖视图。

87.图53是其他实施方式的半导体封装的剖视图。

具体实施方式

88.以下,基于附图对本发明的实施方式进行说明。另外,在以下的各实施方式中,对于相互相同或等同的部分赋予同一标记进行说明。

89.(第1实施方式)

90.参照图1~图4d对第1实施方式的半导体封装10的结构进行说明。另外,本实施方式的半导体封装10适于搭载在车辆中来使用。

91.如图1~图4d所示,半导体封装10具备散热部件20、半导体芯片30、密封部件60等。

92.散热部件20具有由氮化硅(sin)或氮化铝(aln)等构成的绝缘基板21。并且,散热部件20在绝缘基板21的一面21a形成有一面金属膜22、并且在另一面21b形成有另一面金属膜23。在本实施方式中,一面金属膜22及另一面金属膜23由铜构成,厚度为10~100μm左右。此外,一面金属膜22及另一面金属膜23为相同的平面形状,夹着绝缘基板21对称地配置。

93.如图2及图3所示,在本实施方式中,半导体芯片30形成利用二维电子气(即2deg)的高电子迁移率晶体管而构成。另外,图2相当于沿着图3中的ii-ii线的截面。

94.具体而言,半导体芯片30具有由硅或碳化硅(以下也简称sic)等构成的支承基板31,在支承基板31上依次层叠有缓冲层32、半导体层33,半导体芯片30的外形为大致矩形。另外,半导体层33层叠有氮化镓(gan)层及氮化铝镓(algan)层等外延层而构成,在内部生成有二维电子气。

95.在半导体层33的表面,相互离开而形成有漏极电极34及源极电极35。在本实施方式中,漏极电极34及源极电极35分别形成为梳齿状并且彼此的梳齿啮合。另外,在本实施方式中,漏极电极34相当于第1电极,源极电极35相当于第2电极。

96.此外,在半导体层33的表面,在被漏极电极34和源极电极35夹着的部分形成有绝缘膜36。并且,在绝缘膜36上,在从漏极电极34及源极电极35离开了的位置形成有栅极布线37。该栅极布线37适当绕过被源极电极35和漏极电极34夹着的部分,与在半导体层33的表面的外缘部配置的栅极电极38连接。漏极电极34、源极电极35及栅极电极38例如由铜构成,但并不特别限定。栅极布线37例如由铝、铂、铜等金属、或掺杂有杂质的聚合物半导体等构成。

97.并且,在半导体层33的表面,以使漏极电极34、源极电极35、栅极电极38露出并将栅极布线37覆盖的方式形成有保护膜39。

98.在支承基板31中的与半导体层33侧相反侧的面,形成有另一面电极40。并且,另一面电极40与源极电极35电连接,具体后述。由此,源极电极35和支承基板31经由另一面电极

40电连接,电流崩塌得以抑制。

99.这样的半导体芯片30通过控制在栅极布线37上施加的栅极电压来控制经由二维电子气而在漏极电极34与源极电极35之间流动的电流的通断。即,本实施方式的半导体芯片30形成横型半导体元件。

100.以上是本实施方式的半导体芯片30的结构。这样的半导体芯片30通过采用上述结构,成为具有形成有源极电极35等的一面侧、形成有另一面电极40的另一面侧、将一面与另一面之间相连的侧面的大致矩形状。

101.并且,半导体芯片30如图1所示,以使另一面电极40与散热部件20对置的方式,经由接合部件50而配置在形成于散热部件20的一面金属膜22上。接合部件50由具有导电性的材料构成。在本实施方式中,接合部件50由以银锡(agsn)为主成分的烧结体构成。因此,另一面电极40成为经由接合部件50而与一面金属膜22电连接的状态。另外,接合部件50通过混入热传导率比银锡高的铜粉等而构成,从而热传导率进一步变高。

102.此外,在本实施方式中,在散热部件20与半导体芯片30的层叠方向(以下也简称层叠方向)上,接合部件50配置为,比半导体芯片30突出。换言之,在层叠方向上,接合部件50配置为,使得半导体芯片30位于接合部件50内。由此,例如与在层叠方向上半导体芯片30比接合部件50突出的情况相比,能够抑制应力集中于半导体芯片30与接合部件50的接合面的端部。因此,能够抑制在半导体芯片30与接合部件50的接合面中产生裂纹。

103.密封部件60配置在散热部件20上,以将半导体芯片30的与接合于接合部件50的部分不同的部分密封,并且与散热部件20接合。即,密封部件60配置在散热部件20上,以将半导体芯片30的一面侧及侧面密封。密封部件60具有将半导体芯片30的侧面密封的侧面密封部件70和将半导体芯片30的一面侧密封的一面密封部件80,分别由液晶聚合物(以下也简称lcp)构成。另外,lcp是与玻璃环氧树脂相比材料强度高且柔软的材料。即,lcp是与玻璃环氧树脂相比难以被导入裂纹的材料。

104.侧面密封部件70在本实施方式中是通过注塑成型而构成的注塑成型品,呈大致矩形。并且,侧面密封部件70配置在散热部件20上,以将半导体芯片30的侧面密封并与散热部件20接合。具体而言,侧面密封部件70如图1及图4b所示,形成有沿着层叠方向贯通的第1贯通孔71,成为在该第1贯通孔71内配置有半导体芯片30及接合部件50的状态。另外,第1贯通孔71形成为,使一面金属膜22的大致中央部露出。

105.此外,在侧面密封部件70,以使一面金属膜22的外缘部露出的方式形成有第2贯通孔72,配置有与一面金属膜22连接的下方连接通孔73。该下方连接通孔73由以银锡为主成分的烧结体构成,还与后述的上方连接通孔97连接。另外,下方连接通孔73通过混入热传导率比银锡高的铜粉等而构成,从而热传导率进一步变高。此外,在图4a中,将与一面金属膜22连接的下方连接通孔73用虚线表示。并且,在后述的同样的图中,也将与一面金属膜22连接的下方连接通孔73用虚线表示。此外,在本实施方式中,下方连接通孔73配置为圆柱状。

106.一面密封部件80如图1及图4c所示,层叠有膜状的第1密封部件90与第2密封部件100而构成。第1密封部件90由具有一面90a及另一面90b的lcp膜构成。并且,第1密封部件90在一面90a侧形成有由铜箔等构成的多个图案91~93,并且形成有使各图案91~93从另一面90b侧露出的贯通孔94、96,上方连接通孔95、97配置于贯通孔94、96。另外,上方连接通孔95、97由以银锡为主成分的烧结体构成。并且,上方连接通孔97通过混入热传导率比银锡高

的铜粉等而构成,从而热传导率进一步变高。

107.具体而言,在第1密封部件90的一面90a,在与半导体芯片30的漏极电极34对置的位置,形成有与漏极电极34对应的形状的漏极用图案91。在第1密封部件90的一面90a,在与半导体芯片30的源极电极35对置的位置,形成有与源极电极35对应的形状的源极用图案92。在第1密封部件90的一面90a,在与半导体芯片30的栅极电极38对置的位置,形成有与栅极电极38对应的形状的栅极用图案93。在本实施方式中,漏极用图案91相当于第1图案,源极用图案92相当于第2图案。

108.贯通孔94形成在漏极用图案91与漏极电极34之间、源极用图案92与源极电极35之间、栅极用图案93与栅极电极38之间。并且,在各贯通孔94中配置有上方连接通孔95。由此,经由上方连接通孔95,源极用图案92与源极用电极电连接,漏极用图案91与漏极电极34电连接,栅极用图案93与栅极电极38电连接。

109.在本实施方式中,形成有多个将漏极用图案91与漏极电极34连接的上方连接通孔95以及将源极用图案92与源极电极35连接的上方连接通孔95。由此,能够实现电感的减小,能够实现开关动作的高速化。

110.另外,各图案91~93例如由铜箔形成。该情况下,优选的是将各图案91~93设为约18μm以下的厚度,以避免图案93向厚度方向的热膨胀变大。

111.此外,贯通孔96形成在将源极用图案92与侧面密封部件70的第2贯通孔72相连的位置。并且,在该贯通孔96中,配置有与侧面密封部件70的下方连接通孔73以及源极用图案92电连接的上方连接通孔97。由此,在本实施方式中,半导体芯片30的源极电极35经由上方连接通孔95、源极用图案92、上方连接通孔97、下方连接通孔73、一面金属膜22而与另一面电极40电连接。

112.另外,在图4b及图4c中,将上方连接通孔95、97用虚线表示。此外,在后述的同样的图中也将下方连接通孔73用虚线表示。并且,在本实施方式中,上方连接通孔95形成为圆柱状。以下,将形成于侧面密封部件70的下方连接通孔73以及与该下方连接通孔73连接的上方连接通孔95一起也简称为形成于密封部件60的连接通孔61。即,在本实施方式中,形成于密封部件60的连接通孔61以将源极用图案92与一面金属膜22连接的方式配置,呈圆柱状。

113.第2密封部件100如图1及图4d所示,由lcp膜构成,配置在第1密封部件90上。并且,在第2密封部件100中,形成有使各图案91~93露出的接触孔101。由此,由漏极用图案91中的从接触孔101露出的部分构成漏极用焊盘91a。由源极用图案92中的从接触孔露出的部分构成源极用焊盘92a。由栅极用图案93中的从接触孔101露出的部分构成栅极用焊盘93a。另外,虽不特别限定,但各图案91~93例如为18μm以下。

114.另外,在本实施方式中,接触孔101在层叠方向上形成在成为与半导体芯片30不同的位置的部分。即,各焊盘91a、92a、93a在层叠方向上形成在与半导体芯片30不同的位置。换言之,各焊盘91a、92a、93a以在层叠方向上不与半导体芯片30重叠的方式形成。由此,能够减小在经由焊料等向各焊盘91a、92a、93a安装了印刷基板等时施加于半导体芯片30的应力,能够抑制半导体芯片30的损坏。另外,这样的结构在后述的各实施方式中能够适当应用。

115.此外,第2密封部件100如后述那样被加压而与第1密封部件90等一体化。因此,第2密封部件100成为还进入到形成于第1密封部件90的漏极用图案91与源极用图案92之间的

状态。由此,第2密封部件100能够发挥作为阻焊部的功能,并且还能够发挥使漏极用图案91与源极用图案92的绝缘沿面距离变长的功能。

116.以上是本实施方式的密封部件60的结构。并且,密封部件60以在层叠方向上位于散热部件20内的方式配置。即,散热部件20成为在层叠方向上使密封部件60位于散热部件20内的大小。即,绝缘基板21(即,散热部件20)的一面21a的外缘部成为从密封部件60露出的状态。由此,能够抑制应力集中于密封部件60与散热部件20的接合面的端部。因此,能够抑制在密封部件60与散热部件20的接合面中产生裂纹,能够抑制密封部件60从散热部件20剥离。

117.进而,在本实施方式中,各部件间为了提高密接性而进行活性基彼此结合的化学结合,详细地讲为共价键结合(换言之分子结合)。在本实施方式中,为了提高散热部件20与密封部件60的密接性,散热部件20在进行乙醇清洗等表面清洁之后,进行紫外线处理或大气压等离子处理。然后,散热部件20通过涂布包含硅酸盐的碱溶液而形成活性基。

118.此外,为了提高半导体芯片30的周边部、漏极电极34、源极电极35、栅极电极38等与密封部件60的密接性,在对漏极电极34等进行乙醇清洗等表面清洁之后,通过稀硫酸蚀刻等进行氧化物去除。然后,对漏极电极34等涂布具有硅烷醇基及氨基的有机化合物的水溶液而形成活性基。另外,所谓周边部,包括漏极电极34、源极电极35、栅极电极38等的周围、以及将支承基板31、缓冲层32、半导体层33层叠而构成的基板的侧面等。此外,漏极电极34、源极电极35、栅极电极38等由于成为后述的与上方连接通孔95连接的部分,所以在这些部分也可以不形成活性基。即,对于半导体芯片30,可以仅在与形成漏极电极34、源极电极35、栅极电极38的部分不同的部分形成活性基。

119.进而,为了提高侧面密封部件70与第1密封部件90、以及第1密封部件90与第2密封部件100的密接性,对于各部件70、90、100,在进行乙醇清洗等表面清洁之后,进行紫外线处理或大气压等离子处理。然后,各部件70、90、100通过被涂布具有硅烷醇基及氨基的有机化合物的水溶液而形成活性基。

120.以上是本实施方式的半导体封装10的结构。接着,参照图5a~图5g、图6对上述半导体封装10的制造方法进行说明。另外,图5a~图5g是表示制造相邻的2个半导体封装10的工序的图,实际上,如图6所示那样,在相同的工序中制造更多半导体封装10。此外,在下述工序中准备各部件时,适当执行用来形成活性基的处理。

121.首先,如图5a及图6所示,准备将上述绝缘基板21经由切割线dl而一体化的多连基板即构成基板210。并且,在构成基板210中的成为绝缘基板21的部分,形成一面金属膜22及另一面金属膜23。

122.此外,在构成基板210,在形成另一面金属膜23的一侧的面中的位于切割线dl的部分,沿着切割线dl形成槽部211。该情况下,如果设构成基板210的厚度为t,则槽部211被设为0.1t~0.5t左右的深度。此外,这里,对在构成基板210中的形成另一面金属膜23的一侧的面上形成槽部211的例子进行说明,但槽部211也可以形成在构成基板210中的形成一面金属膜22的一侧的面上,也可以形成在形成另一面金属膜23的一侧的面及形成一面金属膜22的一侧的面上。

123.并且,如图5b所示,准备将上述侧面密封部件70经由切割线dl而一体化的侧面构成部件700。接着,在侧面构成部件700中的成为侧面密封部件70的部分,形成第1贯通孔71

及第2贯通孔72。然后,例如,在第2贯通孔72中,通过压入等配置构成下方连接通孔73的烧结体73a。该情况下,也可以在第2贯通孔72中通过印刷法等配置构成下方连接通孔73的导电性膏。另外,通过压入等配置的烧结体73a例如使用以银锡为主成分的烧结体。通过印刷法配置的导电性膏使用在有机溶剂中混入了以银锡为主成分的粉末的材料。

124.同样,如图5c所示,准备将上述第1密封部件90经由切割线dl而一体化的第1构成部件900。并且,在第1构成部件900中的成为第1密封部件90的部分,形成漏极用图案91及源极用图案92。此外,在与图5c不同的截面中,在第1构成部件900中的成为第1密封部件90的部分,形成栅极用图案93。并且,在第1构成部件900中的成为第1密封部件90的部分,通过激光等形成贯通孔94、96,在贯通孔94、96中,通过压入等配置构成上方连接通孔95、97的烧结体95a、97a。该情况下,也可以在贯通孔94、96中通过印刷法等配置构成上方连接通孔95、97的导电性膏。另外,通过压入等配置的烧结体95a、97a例如使用以银锡为主成分的烧结体。通过印刷法配置的导电性膏使用在有机溶剂中混入了以银锡为主成分的粉末的材料。

125.此外,如图5d所示,准备将上述第2密封部件100经由切割线dl而一体化的第2构成部件1000。并且,在第2构成部件1000中的成为第2密封部件100的部分,形成接触孔101。

126.接着,如图5e所示,在构成基板210上,配置侧面构成部件700,并且在第1贯通孔71中经由构成接合部件50的烧结体50a配置半导体芯片30。该情况下,也可以在第1贯通孔71中通过印刷法等配置构成接合部件50的导电性膏。并且,在侧面构成部件700及半导体芯片30上,依次层叠第1构成部件900及第2构成部件1000。即,在构成基板210上,以将半导体芯片30收容的方式配置侧面构成部件700、第1构成部件900及第2构成部件1000。另外,在本实施方式中,侧面构成部件700、第1构成部件900及第2构成部件1000相当于密封构成部件。此外,烧结体50a例如使用以银锡为主成分的烧结体。通过印刷法配置的导电性膏使用在有机溶剂中混入了以银锡为主成分的粉末的材料。

127.并且,如图5f所示,一边加热一边在层叠方向上加压,从而将构成基板210、侧面构成部件700、半导体芯片30、第1构成部件900、第2构成部件1000一体化。此时,由烧结体50a、73a、95a、97a构成接合部件50、下方连接通孔73、上方连接通孔95、97。同样,在配置有导电性膏的情况下,由各导电性膏构成接合部件50、下方连接通孔73、上方连接通孔95、97。

128.然后,如图5g所示,沿着切割线dl分割为芯片单位。此时,在本实施方式中,由于在构成基板210上形成有槽部211,所以能够容易地进行切割。并且,通过激光等将密封部件60的外缘部除去,以使绝缘基板21的一面21a的外缘部从密封部件60露出。如以上这样,制造上述图1所示的半导体封装10。

129.如以上说明,在本实施方式中,密封部件60由lcp构成,lcp是与玻璃环氧树脂相比材料强度高且柔软的材料。因此,能够抑制在密封部件60中导入裂纹,能够抑制半导体封装10的损坏。

130.此外,半导体封装10在散热部件20与密封部件60的界面等处通过将活性基彼此接合的化学结合而被接合。具体而言,散热部件20与密封部件60的界面等通过共价键结合而被接合。因此,能够抑制在散热部件20与密封部件60的界面等处发生剥离。此外,半导体芯片30与密封部件60的界面等通过化学结合而被接合。因此,能够抑制在半导体芯片30与密封部件60的界面等处发生剥离。进而,由于半导体芯片30与密封部件60的界面通过化学结合而被接合,所以能够提高半导体芯片30与密封部件60的接合性。因而,能够减少半导体芯

片30与密封部件60相接合的区域。特别是,作为半导体芯片30,在将支承基板31用sic构成的情况下,与将支承基板31用硅构成的情况相比成本容易变高。因此,通过减少半导体芯片30与密封部件60相接合的区域而实现半导体芯片30的大小的减小,由此能够实现成本的降低。

131.并且,接合部件50以在层叠方向上使半导体芯片30位于接合部件50内的方式配置。因此,例如与在层叠方向上半导体芯片30比接合部件50突出的情况相比,能够抑制应力集中于半导体芯片30与接合部件50的接合面的端部。因而,能够抑制在半导体芯片30与接合部件50的接合面中产生裂纹。

132.进而,散热部件20被做成在层叠方向上使密封部件60位于散热部件20内的大小。因此,能够抑制应力集中于密封部件60与散热部件20的接合面的端部。因而,能够抑制在密封部件60与散热部件20的接合面中产生裂纹,能够抑制密封部件60从散热部件20剥离。

133.此外,侧面密封部件70由注塑成型品构成,所以能够容易地实现量产化。

134.进而,在漏极用图案91与源极用图案92之间,配置有构成第2密封部件100的lcp。因此,第2密封部件100能够在发挥作为阻焊部的功能的同时还发挥使漏极用图案91与源极用图案92的绝缘沿面距离变长的功能。

135.并且,在本实施方式中,半导体芯片30的源极电极35与另一面电极40电连接。因此,能够实现电流崩塌的减少。

136.进而,散热部件20被做成在绝缘基板21上形成有一面金属膜22及另一面金属膜23的结构。因此,能够抑制散热部件20的翘曲。该情况下,在本实施方式中,一面金属膜22及另一面金属膜23为相同形状,夹着绝缘基板21对称地形成。因而,能够进一步抑制散热部件20的翘曲。

137.此外,在制造半导体封装10时,在构成基板210上形成有槽部211。因此,能够容易地进行切割。另外,在本实施方式中,说明了在将构成基板210与侧面构成部件700等一体化之前形成槽部211的例子,但也可以在将构成基板210与侧面构成部件700等一体化之后形成槽部211。即,槽部211在沿着切割线dl分割为芯片单位之前形成于构成基板210即可。

138.(第2实施方式)

139.对第2实施方式进行说明。本实施方式相对于上述第1实施方式变更了侧面密封部件70的结构。其他与上述第1实施方式是同样的,所以这里省略说明。

140.本实施方式的半导体封装10如图7所示,侧面密封部件70通过将由多层lcp膜构成的板状部件74层叠并一体化而构成。板状部件74具有lcp膜77、形成于该lcp膜77的图案75、以及配置于贯通孔76a的连接通孔76。即,在本实施方式中,构成侧面密封部件70的各板状部件74和第1、第2密封部件90、100分别是对lcp膜77适当形成有图案75、91~93或通孔73、95、97的同样的结构。并且,下方连接通孔73通过连接形成于各板状部件74的图案75以及连接通孔76而构成。即,连接通孔61由上方连接通孔97和构成下方连接通孔73的形成于各板状部件74的图案75及连接通孔76构成。

141.此外,本实施方式的半导体芯片30形成有横型半导体元件而构成。并且,形成于各板状部件74的图案75不成为使电流通过的部分。因而,可以使形成于各板状部件74的图案75比形成于第1密封部件90的各图案91~93薄,例如为12μm以下。由此,能够实现构成图案75的材料的削减。

142.此外,在本实施方式中,在层叠方向上相邻的各板状部件74的连接通孔76经由图案75而被电连接。因此,各板状部件74的连接通孔76可以以在层叠方向上重叠的方式配置,也可以以在层叠方向上不重叠的方式配置。

143.另外,在本实施方式中,相邻的各板状部件74也优选的是通过将活性基彼此接合的化学结合而接合。该情况下,例如可以仅在图案75及导通孔76形成活性基。由此,与在各板状部件74的整体形成活性基的情况相比,还能够实现成本的降低。

144.另外,这样的侧面密封部件70通过在将板状部件74层叠后加热并加压来制造。即,在本实施方式中,在图5b的工序中,如图8a所示,准备将lcp膜77经由切割线dl而一体化的板状部件构成部件770。另外,板状部件构成部件770被准备了与用来构成侧面密封部件70的层数对应的数量。该情况下,板状部件构成部件770的数量优选设为使板状部件构成部件770的整体厚度比半导体芯片30的厚度厚的数量。由此,在后述的图5f以后的加热加压的工序中,能够实现成形后的品质的提高。此外,上述第1实施方式中的准备第1构成部件900及第2构成部件1000的工序,与关于准备将lcp膜77经由切割线dl一体化的板状部件74而准备板状部件构成部件770是同样的。

145.并且,对于板状部件构成部件770,形成相当于第1贯通孔71的贯通孔71a及贯通孔76a,在贯通孔76a中配置构成连接通孔76的构成体76b。构成体76b使用导电性膏或烧结体等。

146.并且,在图5e的工序中,如图8b所示,在构成基板210上,依次层叠板状部件构成部件770,并且依次配置半导体芯片30、第1构成部件900、第2构成部件1000。另外,在图8b中表示了构成1个半导体封装10的区域,但实际上如图5e所示,构成多个半导体封装10的部分用切割线dl相连。然后,通过进行图5f以后的工序,制造出图7所示的半导体封装10。

147.这样,即使将侧面密封部件70不是用注塑成型品构成而是将多个板状部件74层叠而构成,也能够得到与上述第1实施方式同样的效果。

148.(第3实施方式)

149.对第3实施方式进行说明。本实施方式相对于上述第1实施方式,在散热部件20上不具备一面金属膜22及另一面金属膜23。其他与上述第1实施方式是同样的,所以这里省略说明。

150.本实施方式的半导体封装10如图9所示,在散热部件20上不具备一面金属膜22及另一面金属膜23。并且,半导体芯片30隔着接合部件50而配置在散热部件20上。另外,本实施方式的接合部件50由在有机溶剂中混入了银粒子的材料等具有导电性的材料构成,为0.1nm~20μm左右的厚度。即,相对于在上述第1实施方式中说明的一面金属膜22,接合部件50充分薄。

151.此外,接合部件50沿着散热部件20的面方向延伸设置,与下方连接通孔73连接。即,接合部件50延伸设置至与下方连接通孔73连接的位置。并且,源极用图案92经由形成于密封部件60的连接通孔61而与接合部件50连接,从而与半导体芯片30的另一面电极40连接。

152.由此,由于在散热部件20上没有配置一面金属膜22及另一面金属膜23,所以能够实现部件个数的削减并且得到与上述第1实施方式同样的效果。另外,与一面金属膜22相比,接合部件50形成得充分薄。因此,即使不在绝缘基板21的另一面21b配置接合部件50,绝

缘基板21也成为难以翘曲的状态。

153.此外,通过不对散热部件20配置另一面金属膜23,在进行制造工序中的上述图5g的切割时,容易将构成基板210固定。因而,还能够实现切割的简化。

154.(第4实施方式)

155.对第4实施方式进行说明。本实施方式相对于上述第1实施方式,对密封部件60配置有多个连接通孔61。其他与上述第1实施方式是同样的,所以这里省略说明。

156.本实施方式的半导体封装10如图10a~图10c所示,形成有多个连接通孔61。具体而言,散热部件20的一面金属膜22被划分形成为与漏极用图案91连接的漏极用区域22a、与源极用图案92连接的源极用区域22b、与栅极用图案93连接的栅极用区域22c。并且,半导体芯片30经由接合部件50配置在源极用区域22b上。在本实施方式中,漏极用区域22a相当于第1区域,源极用区域22b相当于第2区域。

157.在侧面密封部件70,形成有多个与漏极用区域22a连接的下方连接通孔73。在侧面密封部件70,形成有多个与源极用区域22b连接的下方连接通孔73。在侧面密封部件70,形成有多个与栅极用区域22c连接的下方连接通孔73。

158.另外,与源极用区域22b连接的下方连接通孔73形成得比上述第1实施方式多。此外,在本实施方式中,与漏极用区域22a连接的多个下方连接通孔73以及与源极用区域连接的多个下方连接通孔73形成为,隔着半导体芯片30而位于相反侧。

159.在第1密封部件90,以与连接于漏极用区域22a的下方连接通孔73连接的方式形成有上方连接通孔97。在第1密封部件90,以与连接于源极用区域22b的下方连接通孔73连接的方式形成有上方连接通孔97。在第1密封部件90,以与连接于栅极用区域22c的下方连接通孔73连接的方式形成有上方连接通孔97。

160.即,在密封部件60,以将漏极用图案91与漏极用区域22a连接的方式形成有连接通孔61。在密封部件60,以将源极用图案92与源极用区域22b连接的方式形成有连接通孔61。在密封部件60,以将栅极用图案93与栅极用区域22c连接的方式形成有连接通孔61。

161.此外,在本实施方式中,各连接通孔61相比于将源极电极35与源极用图案92连接的上方连接通孔95以及将漏极电极34与漏极用图案91连接的上方连接通孔95而言直径小。换言之,在与层叠方向正交的截面中,各连接通孔61的截面积比将源极电极35与源极用图案92连接的上方连接通孔95以及将漏极电极34与漏极用图案91连接的上方连接通孔95小。

162.如以上说明,在本实施方式中,一面金属膜22被划分为多个区域。并且,漏极用图案91及栅极用图案93经由连接通孔61而与一面金属膜22连接。因此,成为在密封部件60中形成有许多连接通孔61的状态。因而,通过连接通孔61,能够抑制密封部件60在层叠方向上膨胀,能够在抑制对连接通孔61导入裂纹的同时得到与上述第1实施方式同样的效果。

163.此外,在本实施方式中,连接通孔61相比于将漏极电极34与漏极用图案91连接的上方连接通孔95以及将源极电极35与源极用图案92连接的上方连接通孔95而言直径小。因此,相比于连接通孔61与这些上方连接通孔95直径相同的情况,在制造工序中容易在各贯通孔72、96中通过压入而配置烧结体73a、97a。因而,能够实现制造工序的简化。另外,连接通孔61抑制密封部件60的热膨胀,并不流过电流,所以即使直径小,半导体封装10的电气特性也不会特别变化。

164.此外,虽然没有特别图示,但连接通孔61形成的数量越多,越能够抑制密封部件60

的层叠方向上的热膨胀,所以是优选的。该情况下,为了均等地抑制密封部件60的热膨胀,可以使连接通孔61沿着密封部件60的外表面形成。即,在层叠方向上,连接通孔61可以包围半导体芯片30而形成。换言之,可以是,以与半导体芯片30的各侧面对置的方式分别形成连接通孔61。例如,在图10a~图10c中,也可以在纸面左右方向上的两端部也形成将漏极用图案91与漏极用区域22a连接的连接通孔61(即,下方连接通孔73及上方连接通孔97)。即,如图11所示,可以将连接通孔61以包围半导体芯片30的方式形成。

165.(第5实施方式)

166.对第5实施方式进行说明。本实施方式相对于上述第1实施方式,配置有测试用图案。其他与上述第1实施方式是同样的,所以这里省略说明。

167.本实施方式的半导体封装10如图12a~图12c所示,在第1密封部件90的一面90a配置有被划分形成的漏极用图案91、源极用图案92、栅极用图案93和测试用图案98。另外,测试用图案98与漏极用图案91等同样,由铜箔等形成。

168.并且,在第1密封部件90,形成有与测试用图案98连接的上方连接通孔97。此外,在侧面密封部件70,以将连接于测试用图案98的上方连接通孔97与一面金属膜22连接的方式形成有下方连接通孔73。即,在密封部件60,以将测试用图案98与一面金属膜22连接的方式形成有连接通孔61。并且,源极用图案92和测试用图案98都与一面金属膜22电连接而成为相同电位。

169.由此,通过对测试用图案98与源极用图案92之间的导通电阻进行测定,能够检查半导体芯片30的源极电极35与另一面电极40的导通状态,并且能够得到与上述第1实施方式同样的效果。

170.(第6实施方式)

171.对第6实施方式进行说明。本实施方式相对于上述第1实施方式,变更了半导体芯片30及散热部件20的结构。其他与上述第1实施方式是同样的,所以这里省略说明。

172.本实施方式的半导体封装10如图13所示,依次层叠绝缘基板41、支承基板31、缓冲层32、半导体层33而构成半导体芯片30。另外,绝缘基板41由氮化硅或氮化铝等构成。此外,在本实施方式中,支承基板31相当于第1基板,半导体层33相当于第2基板。

173.并且,支承基板31及绝缘基板41的平面大小比缓冲层32及半导体层33大。即,支承基板31及绝缘基板41在绝缘基板41、支承基板31、缓冲层32、半导体层33的层叠方向上是具有比半导体层33及缓冲层32突出的部分的形状。并且,在支承基板31中的比半导体层33及缓冲层32突出的部分,形成有电极膜42。另外,在本实施方式中,半导体芯片30不配置有另一面电极40。

174.并且,半导体芯片30的绝缘基板41经由接合部件50而配置在散热部件20上。本实施方式的接合部件50可以由在有机溶剂中混入了银粒子、或银及锡的金属粒子的材料等的烧结体构成,只要能够将绝缘基板41与半导体芯片30机械连接即可,也可以由高散热的粘接剂等构成。

175.并且,在密封部件60,以将源极用图案92与电极膜42电连接的方式形成有连接通孔61。即,在本实施方式中,源极电极35经由上方连接通孔95、源极用图案92、连接通孔61、电极膜42而与支承基板31电连接。这样,即使将源极电极35与支承基板31电连接也能够实现电流崩塌的减少。

176.此外,在本实施方式中,由于如上述那样将源极电极35与支承基板31电连接,所以散热部件20由铜等的金属板24构成。因此,例如与将散热部件20用氮化硅或氮化铝等构成的情况相比,能够提高散热部件20的散热性。

177.如以上说明,在本实施方式中,由于将散热部件20用金属板24构成,所以能够提高散热部件20的散热性并且得到与上述第1实施方式同样的效果。

178.(第7实施方式)

179.对第7实施方式进行说明。本实施方式相对于上述第1实施方式,将多个半导体芯片30一体地用密封部件60密封。其他与上述第1实施方式是同样的,所以这里省略说明。

180.本实施方式的半导体封装10被做成将2个半导体芯片30一体地用密封部件60密封的所谓2in1封装。另外,2个半导体芯片30为相同结构。以下,将一个半导体芯片30设为第1半导体芯片30a,将另一个半导体芯片30设为第2半导体芯片30b而进行说明。另外,在图14中,在纸面右侧表示第1半导体芯片30a,在纸面右侧表示第2半导体芯片30b。

181.具体而言,在散热部件20,2个一面金属膜22相互分离地形成。并且,在各个一面金属膜22上,分别经由接合部件50配置有第1半导体芯片30a及第2半导体芯片30b。

182.密封部件60以将第1、第2半导体芯片30a、30b一体地密封的方式配置。具体而言,侧面密封部件70以将第1、第2半导体芯片30a、30b的侧面密封的方式配置。此外,一面密封部件80以将第1、第2半导体芯片30a、30b的一面侧密封的方式配置。

183.在第1密封部件90,形成有与第1半导体芯片30a的漏极电极34连接的漏极用图案91、与第2半导体芯片30b的源极电极35连接的源极用图案92。此外,在第1密封部件90,形成有与第1半导体芯片30a的源极电极35及第2半导体芯片30b的漏极电极34电连接的连接图案99。进而,在第1密封部件90,在与图14不同截面中,分别形成有与第1半导体芯片30a的栅极电极38连接的栅极用图案93、以及与第2半导体芯片30b的栅极电极38连接的栅极用图案93。

184.并且,在第1密封部件90,以将第1半导体芯片30a的漏极电极34与漏极用图案91连接的方式形成有上方连接通孔95。在第1密封部件90,以将第2半导体芯片30b的源极电极35与源极用图案92连接的方式形成有上方连接通孔95。在第1密封部件90,以将第1半导体芯片30a的源极电极35与连接图案99连接的方式形成有上方连接通孔95,并且以将第2半导体芯片30b的漏极电极34与连接图案99连接的方式形成有上方连接通孔95。即,第1、第2半导体芯片30a、30b成为第1半导体芯片30a的源极电极35与第2半导体芯片30b的漏极电极34电连接的状态。

185.此外,在第1密封部件90,在与图14不同的截面中,以将第1半导体芯片30a的栅极电极38与栅极用图案93连接的方式形成有上方连接通孔95。在第1密封部件90,以将第2半导体芯片30b的栅极电极38与栅极用图案93连接的方式形成有上方连接通孔95。

186.并且,在密封部件60,以将连接图案99与配置有第1半导体芯片30a的一面金属膜22连接的方式形成有连接通孔61。在密封部件60,以将源极用图案92与配置有第2半导体芯片30b的一面金属膜22连接的方式形成有连接通孔61。由此,第1、第2半导体芯片30a、30b分别将源极电极35及另一面电极40电连接。

187.第2密封部件100形成有使漏极用图案91、源极用图案92、连接图案99的一部分露出的接触孔101。并且,漏极用图案91、源极用图案92、连接图案99中的从接触孔101露出的

部分成为漏极用焊盘91a、源极用焊盘92a、连接用焊盘99a。

188.此外,在与图14不同的截面中,第2密封部件100形成有使栅极用图案93的一部分露出的接触孔101。并且,如在上述图4d等中说明的那样,栅极用图案93中的从接触孔101露出的部分成为栅极用焊盘93a。

189.这样的半导体封装10例如在dc/dc变换器电路或逆变器电路中以第1半导体芯片30a构成上臂并且第2半导体芯片30b构成下臂的方式被使用。该情况下,漏极用焊盘91a成为高电压侧焊盘,源极用焊盘92a成为低电压侧焊盘,连接用焊盘99a成为输出焊盘。并且,上述半导体封装10如图15所示,与作为被安装部件的印刷基板110及冷却器140等一起构成电子装置1而使用。

190.印刷基板110具有一面110a以及与一面110a相反侧的另一面110b。并且,印刷基板110在一面110a形成有一面布线图案111并且在另一面110b形成有另一面布线图案112,以将一面布线图案111与另一面布线图案112电连接的方式形成有贯通孔电极113。此外,在印刷基板110,在一面布线图案111上,经由作为连接部件的焊料115等配置有陶瓷电容器等电子部件114。

191.并且,半导体封装10中,漏极用焊盘91a、源极用焊盘92a、连接用焊盘99a经由作为连接部件的焊料120而与印刷基板110的另一面布线图案112分别连接。此外,在与图15不同的截面中,半导体封装10的栅极用焊盘93a经由焊料120而与印刷基板110的另一面布线图案112连接。另外,优选的是,焊料120不是以膏状配置而是由焊料凸块构成,以使得能够通过确保高度来提高可靠性。

192.进而,在印刷基板110与半导体封装10之间,为了确保焊料120的可靠性、漏极用焊盘91a、源极用焊盘92a、栅极用焊盘93a、连接用焊盘99a之间的绝缘性,配置有底部填充件130。

193.并且,在半导体封装10的另一面金属膜23,经由散热润滑脂等连接部件141,配置由金属等构成的冷却器140。

194.如以上说明,将多个半导体芯片30用密封部件60一体地密封的半导体封装10也能够得到与上述第1实施方式同样的效果。

195.(第7实施方式的变形例)

196.对第7实施方式的变形例进行说明。在第7实施方式中,对2个半导体芯片30被密封部件60密封的半导体封装10进行了说明,但也可以做成以下这样的半导体封装10。例如,半导体封装10可以是将4个半导体芯片30用密封部件60密封的所谓4in1封装。此外,半导体封装10也可以是将6个半导体芯片30用密封部件60密封的所谓6in1封装。

197.(第8实施方式)

198.对第8实施方式进行说明。本实施方式相对于上述第1实施方式,在半导体芯片30中形成了纵型半导体元件。其他与上述第1实施方式是同样的,所以这里省略说明。

199.本实施方式的半导体封装10如图16所示,在半导体芯片30中形成纵型的半导体元件而构成。例如,本实施方式的半导体芯片30具有由硅或sic等构成的半导体基板43。并且,半导体芯片30的详细结构虽没有图示,但在散热部件20侧形成有漏极电极34,在与散热部件20相反侧形成有源极电极35等。此外,在与图16不同的截面中,半导体芯片30在与散热部件20相反侧形成有栅极布线37、栅极电极38等。并且,半导体芯片30的漏极电极34经由具有

导电性的接合部件50而与一面金属膜22连接。另外,在本实施方式中,漏极电极34相当于第1电极及另一面电极。

200.在第1密封部件90,形成有源极用图案92及漏极用图案91。此外,在第1密封部件90,在与图16不同的截面中,形成有栅极用图案93。

201.并且,在第1密封部件90,在贯通孔94内配置有实心图案95b,以将源极用图案92与源极电极35连接。另外,在本实施方式中,为了能够降低电阻而配置有实心图案95b,但源极用图案92和源极电极35也可以与第1实施方式等同样地用上方连接通孔95连接。此外,在与图16不同的截面中,以将栅极用图案93与栅极电极38连接的方式配置有上方连接通孔95。

202.进而,在密封部件60,以将漏极用图案91与一面金属膜22电连接的方式形成有连接通孔61。由此,漏极用图案91经由连接通孔61及一面金属膜22而与漏极电极34连接。另外,优选的是,该连接通孔61为了发挥使电流流过的功能而形成多个以能够减小电感。

203.如以上说明,即使在半导体芯片30中形成纵型半导体元件,也能够得到与上述第1实施方式同样的效果。

204.(第9实施方式)

205.对第9实施方式进行说明。本实施方式相对于上述第2实施方式,在半导体芯片30与散热部件20之间也配置了板状部件74。其他与上述第2实施方式是同样的,所以这里省略说明。

206.本实施方式的半导体封装10如图17所示,在半导体芯片30的另一面电极40与散热部件20之间也配置有板状部件74。在本实施方式中,将配置在半导体芯片30的另一面电极40与散热部件20之间的板状部件74也称作下层板状部件740,将配置在下层板状部件740上的板状部件74也称作中层板状部件840。并且,下层板状部件740在lcp膜77中适当形成有下层连接通孔760,以将一面金属膜22覆盖的方式配置。中层板状部件840被做成在lcp膜中适当形成有中层图案850、中层连接通孔860的同样的结构,配置在下层板状部件740上。

207.并且,半导体芯片30的另一面电极40与一面金属膜22经由形成于下层板状部件740的下层连接通孔760而被连接。此外,在本实施方式中,一面金属膜22延伸设置至形成于中层板状部件840的中层连接通孔860的下方。并且,中层连接通孔860经由下层连接通孔760而与一面金属膜22连接。由此,在本实施方式中,半导体芯片30的另一面电极40与源极电极35电连接。另外,在本实施方式中,一面金属膜22的厚度形成得比上述第1实施方式的一面金属膜22薄,以使下层板状部件740能够覆盖一面金属膜22。并且,在绝缘基板21的另一面21b不具备另一面金属膜23。但是也可以做成在绝缘基板21的另一面21b具备另一面金属膜23的结构。

208.此外,在本实施方式中,散热部件20的一面21a的外缘部也被密封部件60密封。即,密封部件60在层叠方向上以外缘端部与散热部件20的外缘端部一致的方式配置。另外,这样的半导体封装10在上述的图5g的工序中沿着切割线dl分割为芯片单位后不将密封部件60的外缘部除去即可。此外,在上述各实施方式及后述的各实施方式中,对应于各实施方式的形态,既可以散热部件20的一面21a的外缘部被密封部件60密封,也可以散热部件20的一面21a的外缘部从密封部件60露出。

209.如以上说明,也可以是,配置下层板状部件740,半导体芯片30的另一面电极40经由形成于下层板状部件740的下层连接通孔760而与源极电极35连接。

210.(第10实施方式)

211.对第10实施方式进行说明。本实施方式相对于上述第9实施方式,规定了下层连接通孔760的配置场所。其他与上述第9实施方式是同样的,所以这里省略说明。

212.如图18所示,本实施方式的半导体封装10配置为,下层连接通孔760与半导体芯片30的内缘部分连接,不配置成使下层连接通孔760与半导体芯片30的外缘部分连接。在本实施方式中,下层连接通孔760配置在从半导体芯片30的外缘端部离开了作为半导体芯片30的厚度的距离l的位置。

213.在这样的半导体封装10中,能够抑制下层连接通孔760的损坏,能够实现可靠性的提高。即,半导体芯片30越是外缘部分越容易弯曲,越容易产生较大的应力。因此,通过将下层连接通孔760配置在半导体芯片30中的与应力变大的部分不同的部分,能够抑制下层连接通孔760的损坏。

214.(第11实施方式)

215.对第11实施方式进行说明。本实施方式相对于上述第9实施方式,变更了下层板状部件740的结构。其他与上述第9实施方式是同样的,所以这里省略说明。

216.本实施方式的半导体封装10如图19及图20所示,形成于下层板状部件740的下层连接通孔760的直径根据配置的场所而不同。具体而言,下层连接通孔760的与半导体芯片30的内缘部分连接的部分的直径大于与半导体芯片30的外缘部分连接的部分的直径。换言之,下层连接通孔760的与半导体芯片30的内缘部分连接的部分的连接面积大于与半导体芯片30的外缘部分连接的部分的连接面积。更详细地讲,从与半导体芯片30的内缘部分连接的部分朝向与外缘部分连接的部分,下层连接通孔760的直径逐渐变小。

217.在这样的半导体封装10中,半导体芯片30的内缘部分与外缘部分相比容易成为高温。因此,通过在半导体芯片30中的成为高温的部分配置直径较大的下层连接通孔760,能够提高散热性。此外,半导体芯片30如也在上述第10实施方式中记载的那样,越是外缘部分越容易弯曲,越容易产生较大的应力。因此,通过在半导体芯片30中的应力容易变大的部分配置直径较小的下层连接通孔760,能够抑制下层连接通孔760的损坏。即,根据本实施方式的半导体封装10,能够在提高散热性的同时抑制下层连接通孔760的损坏。

218.(第12实施方式)

219.对第12实施方式进行说明。本实施方式相对于上述第9实施方式,变更了下层板状部件740的结构。其他与上述第9实施方式是同样的,所以这里省略说明。

220.在本实施方式中,如图21所示,从散热部件20侧依次层叠第1下层板状部件741和第2下层板状部件742而构成下层板状部件740。并且,在第1下层板状部件741,形成有作为下层连接通孔760的第1下层连接通孔761。在第2下层板状部件742,形成有下层图案752及作为下层连接通孔760的第2下层连接通孔762。

221.具体而言,在第2下层板状部件742,以与半导体芯片30的另一面电极40连接的方式形成有多个第2下层连接通孔762,并且以与形成于中层板状部件840的中层连接通孔860连接的方式形成有第2下层连接通孔762。并且,在第2下层板状部件742,以将各第2下层连接通孔762相互连接的方式形成有下层图案752。即,下层图案752从位于半导体芯片30的下方的部分延伸设置至位于中层连接通孔860的下方的部分。

222.在第1下层板状部件741,以将形成于第2下层板状部件742的下层图案752与一面

金属膜22连接的方式形成有多个第1下层连接通孔761。另外,本实施方式的一面金属膜22为与下层图案752大致相同的大小,以与下层图案752对置的方式形成。即,一面金属膜22与下层图案752同样,从位于半导体芯片30的下方的部分延伸设置至位于中层连接通孔860的下方的部分。并且,第1下层连接通孔761在层叠方向上在成为半导体芯片30的外侧的部分也与下层图案752连接。

223.此外,在本实施方式中,如图21及图22所示,形成于第1下层板状部件741的第1下层连接通孔761相比于形成于第2下层板状部件742的第2下层连接通孔762而言直径较大。进而,形成于第1下层板状部件741的第1下层连接通孔761和形成于第2下层板状部件742的第2下层连接通孔762以在层叠方向上成为不同的位置的方式形成。换言之,形成于第1下层板状部件741的第1下层连接通孔761和形成于第2下层板状部件742的第2下层连接通孔762以在层叠方向上不重叠的方式配置。在本实施方式中,形成于第1下层板状部件741的第1下层连接通孔761和形成于第2下层板状部件742的第2下层连接通孔762形成为,在从层叠方向观察时呈相互错开的交错状。另外,在图22中,为了容易理解,对第1下层连接通孔761施以了阴影。

224.如以上说明,可以将第1下层板状部件741及第2下层板状部件742层叠而构成下层板状部件740。并且,在这样的半导体封装10中,第2下层板状部件742与第1下层板状部件741相比容易成为高温。因此,通过使形成于第2下层板状部件742的第2下层连接通孔762比形成于第1下层板状部件741的第1下层连接通孔761小,能够抑制第2下层连接通孔762的损坏,能够实现可靠性的提高。

225.此外,一面金属膜22以及形成于第2下层板状部件742的下层图案752在层叠方向上延伸设置至半导体芯片30的外侧。并且,形成于第1下层板状部件741的第1下层连接通孔761在层叠方向上在半导体芯片30的外侧也与形成于第2下层板状部件742的下层图案752连接。因此,当在半导体芯片30中产生的热从第2下层连接通孔762向下层图案752传递时,热一边在下层图案752中在平面方向上扩散一边经由第1下层连接通孔761、一面金属膜22向绝缘基板21传递。因而,与在层叠方向上形成于第1下层板状部件741的第1下层连接通孔761仅在半导体芯片30的内侧与形成于第2下层板状部件742的下层图案752连接的情况相比,能够提高散热性。该情况下,虽然没有特别图示,但通过使第1下层连接通孔761的数量比第2下层连接通孔762多,能够更容易向散热部件20散热。

226.进而,第1下层连接通孔761和第2下层连接通孔762形成为,在层叠方向上为不同的位置。因此,与第1下层连接通孔761和第2下层连接通孔762在层叠方向上重叠的情况相比,能够减小在第1下层连接通孔761及第2下层连接通孔762中可能产生的应力,能够进一步实现可靠性的提高。

227.(第13实施方式)

228.对第13实施方式进行说明。本实施方式相对于上述第9实施方式,在绝缘基板21形成有粗化部。其他与上述第9实施方式是同样的,所以这里省略说明。

229.本实施方式的半导体封装10如图23所示,在绝缘基板21,在与密封部件60接合的部分形成有粗化部25。在本实施方式中,粗化部25形成为将绝缘基板21中的形成有一面金属膜22的部分包围的框状。这样的粗化部25例如通过将绝缘基板21进行激光处理或喷砂处理等而形成。

230.由此,在绝缘基板21形成有粗化部25,所以在形成有粗化部25的部分,能够提高下层板状部件740与绝缘基板21的密接力。因此,能够抑制下层板状部件740与绝缘基板21剥离的情况。

231.(第13实施方式的变形例)

232.对第13实施方式的变形例进行说明。在上述第13实施方式中,在绝缘基板21,如图24所示,也可以代替粗化部25而形成槽部26。由此,在形成有槽部26的部分,能够提高构成下层板状部件740的lcp膜77与绝缘基板21的密接力,所以能够得到与上述第12实施方式同样的效果。此外,通过形成槽部26,在假设剥离从下层板状部件740与绝缘基板21的界面发展的情况下,剥离的发展方向由于槽部26而变化。因此还能够抑制剥离的发展。

233.(第14实施方式)

234.对第14实施方式进行说明。本实施方式相对于上述第1实施方式,在绝缘基板21形成有凹部。其他与上述第1实施方式是同样的,所以这里省略说明。

235.本实施方式的半导体封装10如图25所示,在绝缘基板21的一面21a侧形成有凹部27。凹部27的底面比半导体芯片30的平面大小大,凹部27的深度比半导体芯片30的厚度浅。

236.一面金属膜22从凹部27的底面延伸设置至形成有凹部27的部分的周围。并且,一面金属膜22在与形成有凹部27的部分不同的部分与下方连接通孔73连接。

237.半导体芯片30配置为,另一面电极40侧收容在凹部27中。但是,半导体芯片30以漏极电极34、源极电极35侧的一部分从凹部27突出的方式收容在凹部27中。

238.在这样的半导体封装10中,由于半导体芯片30配置在形成于绝缘基板21的凹部27内,所以能够减少将半导体芯片30密封的密封部件60的树脂量。因此,能够减少容易比绝缘基板21昂贵的lcp的使用量,进而能够实现成本的削减。

239.(第15实施方式)

240.对第15实施方式进行说明。本实施方式相对于上述第9实施方式,从中层板状部件840去除了中层图案850。其他与上述第9实施方式是同样的,所以这里省略说明。

241.本实施方式的半导体封装10如图26所示,在中层板状部件840,没有形成中层图案850。并且,各中层板状部件840的中层连接通孔860相互被直接连接。

242.这样的半导体封装10例如如以下这样制造。即,在准备在上述第2实施方式中说明的图8a的板状部件构成部件770时,不对构成中层板状部件840的板状部件构成部件770形成贯通孔76a,也不配置构成体76b。并且,将构成中层板状部件840的板状部件构成部件770及构成下层板状部件740的板状部件构成部件770层叠,进行暂时加压等而预先一体化。接着,通过激光、钻削、冲孔等,对于构成中层板状部件840的板状部件构成部件770及构成下层板状部件740的板状部件构成部件770一起形成贯通孔76a。接着,在贯通孔76a中配置导电性膏等构成体76b。由此,即使在中层板状部件840中不形成中层图案850,也容易连接形成于各中层板状部件840的中层连接通孔860。

243.由此,能够削减中层板状部件840的中层图案850,所以能够实现部件的削减。

244.另外,本实施方式能够应用于上述各实施方式及后述的各实施方式。并且,例如在将本实施方式也对第12实施方式应用的情况下,也可以将配置在形成于第2下层板状部件742的第2下层连接通孔762和形成于第1下层板状部件741的第1下层连接通孔761之间的下层图案752去除。该情况下,下层图案752能够做成仅具有位于半导体芯片30下方的部分的

结构。即,在本实施方式中,能够得到在层叠方向上相邻的板状部件74中适当将图案75去除了的半导体封装10。

245.(第16实施方式)

246.对第16实施方式进行说明。本实施方式相对于上述第9实施方式,在半导体芯片30中形成有纵型的半导体元件。即,对上述第9实施方式组合了第8实施方式。其他与上述第9实施方式是同样的,所以这里省略说明。

247.本实施方式的半导体封装10如图27所示,半导体芯片30形成有与第8实施方式同样的纵型的半导体元件。具体而言,半导体芯片30在散热部件20侧形成有漏极电极34,在与散热部件20相反侧形成有源极电极35。此外,在与图27不同的截面中,半导体芯片30在与散热部件20相反侧形成有栅极布线37、栅极电极38等。

248.并且,半导体芯片30的漏极电极34经由下层连接通孔760而与一面金属膜22连接。另外,在本实施方式中,漏极电极34相当于第1电极及另一面电极。

249.这样,可以将密封部件60用多个板状部件74构成、并且在半导体芯片30中形成纵型半导体元件。

250.(第17实施方式)

251.对第17实施方式进行说明。本实施方式相对于上述第16实施方式,在密封部件60中还配置有电容器。其他与上述第16实施方式是同样的,所以这里省略说明。

252.在本实施方式中,如图28所示,在密封部件60中,还配置有具有一对电极150a、150b的电容器150。具体而言,电容器150配置在半导体芯片30的附近且半导体芯片30的侧方。此外,电容器150以一方的电极150a位于第1密封部件90侧、另一方的电极150b位于下层板状部件740侧的方式配置。另外,本实施方式的电容器150由硅等构成,与半导体芯片30的厚度大致相等。

253.形成于第1密封部件90的源极用图案92延伸设置至与电容器150对置的部分。形成于绝缘基板21的一面金属膜22延伸设置至与电容器150对置的部分。

254.并且,电容器150的电极150a经由上方连接通孔95而与源极用图案92连接,并且经由下层连接通孔760而与连接于半导体芯片30的漏极电极34的一面金属膜22连接。

255.另外,在本实施方式中,源极用图案92、上方连接通孔95、一面金属膜22、下层连接通孔760相当于布线层。此外,这样的半导体封装10与半导体芯片30同样,通过将电容器150配置在板状部件构成部件770内而制造。

256.本实施方式的半导体封装10由于将电容器150配置在密封部件60内,所以能够将半导体芯片30和电容器150接近而配置,能够缩短将半导体芯片30与电容器150连接的布线层。因此,能够实现寄生电感的降低。

257.此外,本实施方式的半导体封装10通过将电容器150与半导体芯片30同样地配置在密封部件60内而构成。因此,与将电容器150配置在其他场所并与半导体芯片30连接的情况相比,能够实现构造的简化,并且能够实现制造工序的简化。

258.另外,在上述中,对电容器150是与半导体芯片30相同厚度的例子进行了说明,但电容器150例如也可以形成得比半导体芯片30薄。该情况下,例如,通过在配置于电容器150的电极150a与源极用图案92之间的中层板状部件840中适当形成中层图案850及中层连接通孔860,将电容器150的电极150a与源极用图案92连接即可。

259.(第18实施方式)

260.对第18实施方式进行说明。本实施方式相对于第9实施方式,在半导体封装10的第2密封部件100上追加了散热部件。其他与上述第9实施方式是同样的,所以这里省略说明。

261.本实施方式的半导体封装10如图29所示,在第2密封部件100上也配置有散热部件160。在本实施方式中,散热部件160与半导体芯片30对置,并且配置在第2密封部件100中的与形成接触孔101的部分不同的部分。

262.并且,在第2密封部件100,以将散热部件160与源极用图案92连接的方式,在贯通第2密封部件100的贯通孔102中形成有上方连接通孔103。由此,散热部件160与源极用图案92被热连接。

263.由此,还能够从散热部件160将由半导体芯片30产生的热散热,所以能够进一步实现散热性的提高。

264.(第19实施方式)

265.对第19实施方式进行说明。本实施方式相对于第9实施方式,在半导体封装10的散热部件20侧追加了高散热部件。其他与上述第9实施方式是同样的,所以这里省略说明。

266.本实施方式的半导体封装10如图30所示,在构成散热部件20的绝缘基板21的另一面21b,配置有由热传导率比绝缘基板21高的材料构成的高散热部件170。并且,本实施方式的高散热部件170的平面方向的大小比散热部件20大。另外,这样的高散热部件170例如由铜或铝等金属材料构成。

267.并且,绝缘基板21和高散热部件170被用以银锡为主成分的烧结体等接合部件171连接。另外,绝缘基板21和高散热部件170也可以通过将活性基彼此接合的共价键结合而被连接。

268.由此,能够从散热部件20经由高散热部件170散热,所以能够进一步提高散热性。此外,在本实施方式中,由于高散热部件170的平面方向的大小比绝缘基板21大,所以与高散热部件170的平面方向的大小为绝缘基板21以下的大小的情况相比,能够进一步提高散热性。并且,本实施方式的半导体封装10在如上述第7实施方式那样被安装于冷却器140时,高散热部件170经由散热润滑脂等连接部件141而安装于冷却器140。因此,通过增大高散热部件170的平面方向的大小,能够增大高散热部件170与连接部件141的接触面积,能够进一步提高散热性。

269.(第19实施方式的变形例)

270.对上述第19实施方式的变形例进行说明。在上述第19实施方式中,作为散热部件20,也可以代替使用绝缘基板21而将高散热部件170直接配置在半导体芯片30的另一面电极40侧。该情况下,高散热部件170在由金属构成的情况下具有导电性。因此,在将散热部件20用高散热部件170构成的情况下,在高散热部件170与一面金属膜22之间配置lcp膜等即可。

271.此外,在上述第19实施方式中,也可以如上述第1实施方式那样通过在绝缘基板21的另一面21b配置另一面金属膜23并使该另一面金属膜23的厚度较厚,从而使另一面金属膜23作为高散热部件170发挥功能。

272.进而,在上述第19实施方式中,高散热部件170的平面方向的大小也可以比绝缘基板21小。

273.(第20实施方式)

274.对第20实施方式进行说明。本实施方式相对于上述第16实施方式,具备形成有纵型半导体元件的2个半导体芯片30。其他与上述第16实施方式是同样的,所以这里省略说明。

275.本实施方式的半导体封装10如图31所示,与上述第7实施方式同样,是将2个半导体芯片30一体地用密封部件60密封的所谓2in1封装。另外,2个半导体芯片30分别为与上述第16实施方式同样的结构。即,在另一面侧形成漏极电极34、在一面侧形成源极电极35及栅极电极38等而构成各半导体芯片30。以下,设一个半导体芯片30为第1半导体芯片30a,设另一个半导体芯片30为第2半导体芯片30b而进行说明。另外,在图31中,在纸面右侧表示第1半导体芯片30a,在纸面右侧表示第2半导体芯片30b。并且,第1半导体芯片30a及第2半导体芯片30b配置为,漏极电极34位于与散热部件20相反侧,源极电极35及栅极电极38等位于散热部件20侧。另外,栅极电极38形成在与图31不同的截面中。

276.第1密封部件90及第2密封部件100为与上述第7实施方式同样的结构。即,在第1密封部件90,形成有与第1半导体芯片30a的漏极电极34连接的漏极用图案91。在第1密封部件90,形成有将第1半导体芯片30a的源极电极35与第2半导体芯片30b的漏极电极34连接的连接图案99。在第1密封部件90,形成有与第2半导体芯片30b的源极电极35连接的源极用图案92。

277.此外,在第1密封部件90,分别形成有与漏极用图案91、源极用图案92、连接图案99连接的上方连接通孔95。在第1密封部件90,在与图31不同的截面中,形成有与第1半导体芯片30a的栅极电极38连接的栅极用图案93、以及与栅极用图案93连接的上方连接通孔95。在第1密封部件90,在与图31不同的截面中,形成有与第2半导体芯片30b的栅极电极38连接的栅极用图案93、以及与栅极用图案93连接的上方连接通孔95。

278.第2密封部件100形成有使漏极用图案91、源极用图案92、连接图案99的一部分露出的接触孔101。并且,漏极用图案91、源极用图案92、连接图案99中的从接触孔101露出的部分成为漏极用焊盘91a、源极用焊盘92a、连接用焊盘99a。此外,第2密封部件100在与图31不同的截面中形成有使栅极用图案93的一部分露出的接触孔101。并且,栅极用图案93中的从接触孔101露出的部分成为栅极用焊盘93a。

279.一面金属膜22形成在与第1半导体芯片30a对置的部分以及与第2半导体芯片30b对置的部分。另外,一面金属膜22的与第1半导体芯片30a对置的部分和与第2半导体芯片30b对置的部分分离而形成。此外,与第1半导体芯片30a对置的一面金属膜22具有与源极电极35对置的部分及与栅极电极38对置的部分,它们分离而形成。与第2半导体芯片30b对置的一面金属膜22具有与源极电极35对置的部分及与栅极电极38对置的部分,它们分离而形成。

280.并且,第1半导体芯片30a的源极电极35经由下层连接通孔760而与对置于该源极电极35的一面金属膜22连接。第2半导体芯片30b的源极电极35经由下层连接通孔760而与对置于该源极电极35的一面金属膜22连接。此外,第1半导体芯片30a的栅极电极38在与图31不同的截面中经由下层连接通孔760而与对置于该栅极电极38的一面金属膜22连接。第2半导体芯片30b的栅极电极38在与图31不同的截面中经由下层连接通孔760而与对置于该栅极电极38的一面金属膜22连接。

281.此外,与第1半导体芯片30a对置的一面金属膜220在层叠方向上延伸设置至第1半导体芯片30a的外侧。同样,与第2半导体芯片30b对置的一面金属膜22在层叠方向上延伸设置至第2半导体芯片30b的外侧。

282.并且,在密封部件60,形成有将连接图案99与连接于第1半导体芯片30a的源极电极35的一面金属膜22连接的连接通孔61。在密封部件60,形成有将源极用图案92与连接于第2半导体芯片30b的源极电极35的一面金属膜22连接的连接通孔61。进而,在密封部件60,在与图31不同的截面中,形成有将连接于第1半导体芯片30a的栅极电极38的一面金属膜22与栅极用焊盘93a连接的连接通孔61。此外,在密封部件60,在与图31不同的截面中,形成有将连接于第2半导体芯片30b的栅极电极38的一面金属膜22与栅极用焊盘93a连接的连接通孔61。

283.这样的半导体封装10例如在dc/dc变换器电路及逆变器电路中以第1半导体芯片30a构成上臂并且第2半导体芯片30b构成下臂的方式被使用。该情况下,漏极用焊盘91a成为高电压侧焊盘,源极用焊盘92a成为低电压侧焊盘,连接用焊盘99a成为输出焊盘。

284.如以上说明,还能够做成将形成有纵型的半导体元件的2个半导体芯片30用密封部件60一体地密封的半导体封装10。此外,在该半导体封装10中,由于能够将第1半导体芯片30a与第2半导体芯片30b接近而配置,所以能够缩短将第1半导体芯片30a与第2半导体芯片30b连接的布线层。因而,能够实现寄生电感的降低。

285.另外,在本实施方式中,说明了第1半导体芯片30a及第2半导体芯片30b以漏极电极34位于与散热部件20相反侧、源极电极35及栅极电极38等位于散热部件20侧的方式配置的例子。但是,第1半导体芯片30a及第2半导体芯片30b也可以配置为,源极电极35及栅极电极38等位于与散热部件20相反侧,漏极电极34位于散热部件20侧。并且,在这样的结构的情况下,适当调整一面金属膜22、下层连接通孔760及形成于密封部件60的连接通孔61的连接关系、以使各焊盘91a、92a、93a、99a与第1半导体芯片30a及第2半导体芯片30b的连接关系成为上述关系即可。

286.(第21实施方式)

287.对第21实施方式进行说明。本实施方式相对于上述第20实施方式,变更了第1半导体芯片30a及第2半导体芯片30b的配置的方式。其他与上述第20实施方式是同样的,所以这里省略说明。

288.在本实施方式的半导体封装10中,如图32所示,第1半导体芯片30a配置为,漏极电极34位于与散热部件20相反侧,源极电极35及栅极电极38等位于散热部件20侧。另一方面,第2半导体芯片30b配置为,漏极电极34位于散热部件20侧,源极电极35及栅极电极38等位于与散热部件20相反侧。即,第1半导体芯片30a和第2半导体芯片30b反向配置。

289.此外,形成于绝缘基板21的一面金属膜22具有与第1半导体芯片30a的源极电极35对置的部分以及与第2半导体芯片30b的漏极电极34对置的部分,它们相连而形成。并且,第1半导体芯片30a的源极电极35及第2半导体芯片30b的漏极电极34分别经由下层连接通孔760而与共通的一面金属膜22连接。

290.第1半导体芯片30a的漏极电极34经由上方连接通孔95而与形成于第1密封部件90的漏极用图案91连接。第2半导体芯片30b的源极电极35经由上方连接通孔95而与形成于第1密封部件90的源极用图案92连接。第2半导体芯片30b的栅极电极38在与图32不同的截面

中经由上方连接通孔95而与形成于第1密封部件90的栅极用图案93连接。

291.并且,在密封部件60,形成有将连接图案99与连接于第1半导体芯片30a的源极电极35及第2半导体芯片30b的漏极电极34的一面金属膜22连接的连接通孔61。

292.如以上说明,可以将第1半导体芯片30a和第2半导体芯片30b反向配置。并且,在这样的半导体封装10中,第1半导体芯片30a的源极电极35和第2半导体芯片30b的漏极电极34仅经由一面金属膜22及下层连接通孔760连接,所以能够实现构造的简化。

293.(第22实施方式)

294.对第22实施方式进行说明。本实施方式相对于第9实施方式,变更了半导体封装10的各焊盘91a、92a、93a的配置的方式。其他与上述第9实施方式是同样的,所以这里省略说明。

295.本实施方式的半导体封装10当从层叠方向观察时呈具有两组相对的第1~第4边10a~10d的大致平面矩形状。并且,半导体封装10具有作为栅极用焊盘93a的第1栅极用焊盘931a及第2栅极用焊盘932a,第1栅极用焊盘931a及第2栅极用焊盘932a配置在半导体封装10的外缘部分。

296.具体而言,第1栅极用焊盘931a配置在将第2边10b与第3边10c连结的角部附近,第2栅极用焊盘932a配置在将第3边10c与第4边10d连结的角部附近。即,第1栅极用焊盘931a及第2栅极用焊盘932a分别配置在外缘部分中的相对的部分。更详细地讲,源极用焊盘92a一直配置到第3边10c的附近,第1栅极用焊盘931a及第2栅极用焊盘932a以夹着源极用焊盘92a的方式配置。并且,半导体芯片30的栅极电极38与第1栅极用焊盘931a及第2栅极用焊盘932a连接。

297.在这样的半导体封装10中,半导体封装10的第1栅极用焊盘931a及第2栅极用焊盘932a分别配置在外缘部分中的相对的部分。因此,在将半导体封装10与印刷基板110连接时,将某一方的栅极用焊盘931a、932a与印刷基板110连接即可,所以能够提高印刷基板110侧的布线自由度。该情况下,例如,在将第1栅极用焊盘931a与印刷基板110连接的情况下,通过使得将第1栅极用焊盘931a与向该第1栅极用焊盘931a施加规定电压的驱动电路进行连接的布线层的长度变短,能够实现驱动电压的偏差的减小。进而,在将半导体封装10与印刷基板110连接时,将某一方的栅极用焊盘931a、932a与印刷基板110连接即可,所以印刷基板110侧的布线的引绕变得容易,例如能够做成不将印刷基板110的布线在多层中引绕的结构。由此,能够抑制产生多余磁通的影响。

298.(第23实施方式)

299.对第23实施方式进行说明。本实施方式对于第22实施方式组合了第20实施方式,变更了半导体封装10的各焊盘91a、92a、93a、99a的配置的方式。其他与上述第22实施方式是同样的,所以这里省略说明。

300.本实施方式的半导体封装10与第22实施方式同样,具有第1半导体芯片30a及第2半导体芯片30b。并且,半导体封装10如图34所示,当从层叠方向观察时,各焊盘911a、931a、991a、932a、921a、912a、932a、992a、934a、922a沿着外缘排列配置。

301.具体而言,半导体封装10沿着第2边10b依次排列配置有第1漏极用焊盘911a、第1栅极用焊盘931a、第1连接用焊盘991a、第2栅极用焊盘932a、第1源极用焊盘921a。此外,沿着第4边10d排列配置有第2漏极用焊盘912a、第3栅极用焊盘933a、第2连接用焊盘992a、第4

栅极用焊盘934a、第2源极用焊盘922a。即,各焊盘911a、931a、991a、932a、921a、912a、933a、992a、934a、922a配置在半导体封装10的外缘部分中的相对的部分。

302.另外,虽然没有特别图示,但第1半导体芯片30a的漏极电极34与第1漏极用焊盘911a及第2漏极用焊盘912a连接。第2半导体芯片30b的源极电极35与第1源极用焊盘921a及第2源极用焊盘922a连接。第1半导体芯片30a的源极电极35及第2半导体芯片30b的漏极电极34与第1连接用焊盘991a及第2连接用焊盘992a连接。第1半导体芯片30a的栅极电极38与第1栅极用焊盘931a及第3栅极用焊盘933a连接。第2半导体芯片30b的栅极电极38与第2栅极用焊盘932a及第3栅极用焊盘933a连接。

303.根据以上说明的本实施方式,半导体封装10的各焊盘911a、931a、991a、932a、921a、912a、933a、992a、934a、922a分别配置在外缘部分中的相对的部分。并且,第1半导体芯片30a的各电极34、35、38与沿着第2边10b排列配置的各焊盘911a、931a、991a电连接,并且与沿着第4边10d排列配置的各焊盘912a、933a、992a电连接。同样,第2半导体芯片30b的各电极34、35、38与沿着第2边10b排列配置的各焊盘991a、932a、921a电连接,并且与沿着第4边10d排列配置的各焊盘992a、934a、922a电连接。

304.因此,本实施方式的半导体封装10通过将沿着第2边10b排列配置的各焊盘911a、931a、991a、932a、921a或沿着第4边10d排列配置的各焊盘912a、933a、992a、934a、922a的一方与印刷基板110连接,能够构成dc/dc变换器电路或逆变器电路。因而,能够提高印刷基板110侧的布线自由度,能够得到与第22实施方式同样的效果。

305.另外,这样的半导体封装10例如在构成4in1封装或6in1封装时也能够应用。

306.(第24实施方式)

307.对第24实施方式进行说明。本实施方式相对于上述第22实施方式,变更了栅极用焊盘93a的配置。其他与上述第22实施方式是同样的,所以这里省略说明。

308.本实施方式的半导体封装10如图35所示,在从层叠方向观察时,在大致中央部配置有半导体芯片30。并且,半导体封装10相对于经过半导体芯片30的中心且在一个方向上延伸的假想线k,对称地配置有漏极用焊盘91a和源极用焊盘92a。在图35中,漏极用焊盘91a沿着第4边10d配置,源极用焊盘92a沿着第2边10b配置。并且,栅极用焊盘93a配置在第3边10c侧,并且以与假想线k交叉的方式配置。即,本实施方式的半导体封装10中,栅极用焊盘93a为1个。

309.根据以上说明的本实施方式,在如上述第7实施方式那样与印刷基板110等一起构成电子装置1时,能够提高印刷基板110侧的布线自由度。即,在构成电子装置1的情况下,与图35的半导体封装10一起,还准备图36所示那样的半导体封装10。图36的半导体封装10相对于图35的半导体封装10而言,使漏极用焊盘91a和源极用焊盘92a的配置相反。即,漏极用焊盘91a沿着第2边10b配置,源极用焊盘92a沿着第4边10d配置。但是,在图36的半导体封装10中,栅极用焊盘93a也为1个。

310.并且,在构成电子装置1的情况下,根据印刷基板110侧的制约而使用图35的半导体封装10或图36的半导体封装10的一方。因此,能够提高印刷基板110侧的布线自由度。换言之,能够实现半导体封装10的通用性的提高。并且,在本实施方式中,即使这样在半导体封装10中仅具备1个栅极用焊盘93a,也能够提高印刷基板110侧的布线自由度。因而,与在半导体封装10中配置2个栅极用焊盘93a的情况相比,能够还实现半导体封装10的小型化,

并且提高印刷基板110侧的布线自由度。

311.另外,虽然没有特别图示,但在半导体芯片30中,在形成纵型的半导体元件的情况下,也能够通过将栅极电极38设为1个而增大能够配置源极电极35的部分。因此,在这样的半导体芯片30中,容易扩大能够流过电流的有效区域,能够实现低导通电阻化。换言之,在构成相同导通电阻的半导体芯片30的情况下,能够实现半导体芯片30的小型化。

312.(第25实施方式)

313.对第25实施方式进行说明。本实施方式相对于上述第20实施方式,配置有2个电容器。其他与上述第20实施方式是同样的所以这里省略说明。

314.在本实施方式中,如图37所示,与第1半导体芯片30a及第2半导体芯片30b一起,在密封部件60内配置有具有一对电极151a、151b的第1电容器151以及具有一对电极152a、152b的第2电容器152。另外,图37是与在上述第20实施方式中说明的图32不同的截面,第1半导体芯片30a及第2半导体芯片30b配置在与图37不同的截面中。此外,本实施方式的第1电容器151及第2电容器152由硅等构成,与半导体芯片30的厚度大致相等。

315.第1电容器151及第2电容器152与第1半导体芯片30a及第2半导体芯片30b同样,配置在下层板状部件740上。具体而言,第1电容器151及第2电容器152以一方的电极151b、152b位于下层板状部件740侧、另一方的电极151a、152a位于第1密封部件90侧的方式配置在下层板状部件740上。

316.并且,第1电容器151的电极151a经由上方连接通孔95而与形成于第1密封部件90的漏极用图案91连接。第2电容器152的电极152a经由上方连接通孔95而与形成于第1密封部件90的源极用图案92连接。此外,第1电容器151的电极151b及第2电容器152的电极152b经由下层连接通孔760而与一面金属膜22连接。即,在本实施方式中,成为对于第1半导体芯片30a及第2半导体芯片30b的串联构造并联连接第1电容器151及第2电容器152的串联构造的状态。另外,在本实施方式中,漏极用图案91、源极用图案92、上方连接通孔95、一面金属膜22、下层连接通孔760相当于布线层。

317.由此,与第1半导体芯片30a及第2半导体芯片30b一起配置有第1电容器151及第2电容器152。因此,能够将第1半导体芯片30a及第2半导体芯片30b和第1电容器151及第2电容器152接近而配置,能够缩短将它们连接的布线层。因而,能够实现寄生电感的降低。此外,相对于后述的第25实施方式,能够抑制半导体封装10在厚度方向上大型化。

318.另外,在上述中,说明了第1电容器151及第2电容器152的串联构造相对于第1半导体芯片30a及第2半导体芯片30b的串联构造并联连接的状态的例子。但是,第1电容器151及第2电容器152也可以相对于第1半导体芯片30a及第2半导体芯片30b的串联构造分别并联地连接。

319.此外,第1电容器151及第2电容器152也可以与上述第17实施方式同样,形成得比第1半导体芯片30a及第2半导体芯片30b薄。

320.(第26实施方式)

321.对第26实施方式进行说明。本实施方式相对于上述第25实施方式,变更了第1电容器151及第2电容器152的配置的方式。其他与上述第25实施方式是同样的,所以这里省略说明。

322.在本实施方式中,如图38所示,在第1半导体芯片30a上配置有第1电容器151,在第

2半导体芯片30b上配置有第2电容器152。在本实施方式中,第1电容器151及第2电容器152配置为,沿着半导体封装10的平面方向而使一对电极151a、151b、152a、152b位于第2密封部件100上。

323.密封部件60形成为,将第1电容器151及第2电容器152也密封。在本实施方式中,密封部件60具备配置在第2密封部件100上的上层密封部件180。另外,上层密封部件180层叠与中层板状部件840等同样结构的上层板状部件940而构成,适当形成有上层图案950及上层连接通孔960。

324.此外,上层密封部件180在位于与绝缘基板21侧最相反侧的部分形成有使与漏极用图案91、源极用图案92、连接图案99连接的上层图案950露出的接触孔181。并且,上层图案950的从接触孔181露出的部分成为漏极用焊盘91a、源极用焊盘92a、连接用焊盘99a。另外,在与图38不同的截面中,上层图案950还构成栅极用焊盘93a。

325.并且,第1半导体芯片30a的漏极电极34经由上方连接通孔97、漏极用图案91、上层连接通孔960等而与漏极用焊盘91a连接。第2半导体芯片30b的源极电极35经由上方连接通孔97、源极用图案92、上层连接通孔960等而与源极用焊盘92a连接。连接图案99经由上方连接通孔97及上层连接通孔960等而与连接用焊盘99a连接。第1半导体芯片30a的栅极电极38及第2半导体芯片30b的栅极电极38在与图38不同的截面中经由上方连接通孔95、栅极用图案93、上层连接通孔960等而与栅极用焊盘93a连接。

326.第1电容器151的一方的电极151a经由形成于上层密封部件180的上层连接通孔960而与构成漏极用焊盘91a的上层图案950连接。第2电容器152的另一方的电极151b经由形成于上层密封部件180的上层连接通孔960而与构成源极用焊盘92a的上层图案950连接。第1电容器151的另一方的电极151b及第2电容器152的一方的电极152a在与图38不同的截面中经由形成于上层密封部件180的上层图案950及上层连接通孔960而被连接。

327.这样,即使将第1电容器151及第2电容器152相对于第1半导体芯片30a及第2半导体芯片30b层叠配置,也能够得到与上述第24实施方式同样的效果。此外,在这样的半导体封装10中,相对于上述第24实施方式,能够抑制平面方向的大小的增大。

328.(第27实施方式)

329.对第27实施方式进行说明。本实施方式相对于上述第1实施方式,对半导体封装10配置有连接用凸块。其他与上述第1实施方式是同样的,所以这里省略说明。

330.在本实施方式的半导体封装10中,如图39所示,在漏极用焊盘91a及源极用焊盘92a上配置有连接用凸块190。另外,在与图39不同的截面中,在栅极用焊盘93a上也配置有连接用凸块190。连接用凸块190例如由以银锡为主成分的烧结体构成。

331.以上是本实施方式的半导体封装10的结构。接着,参照图40a、图40b对上述半导体封装10的制造方法进行说明。

332.首先,如图40a所示,准备具有lcp膜191和设于lcp膜191的由特氟龙(注册商标)膜等构成的剥离部件192的凸块构成体1900。接着,在凸块构成体1900中形成贯通孔193,在贯通孔193中配置构成凸块的凸块构成部件190a。贯通孔193以与接触孔101对应的位置及大小形成。凸块构成部件190a通过用印刷法等配置导电性膏而构成。导电性膏例如使用在有机溶剂中混入了以银锡为主成分的粉末的材料。该情况下,根据需要而进行临时烧结等使有机溶剂蒸发,以免导电性膏从贯通孔193溢出。

333.另外,凸块构成体1900的平面方向的大小与第1构成部件900等相同。并且,在图40a、图40b中,图示了1个半导体封装10的制造方法,但实际上如上述第1实施方式那样将多个半导体封装10一起制造。

334.接着,如图40b所示,对于进行到相当于图5f的工序的结构的加工对象,以使凸块构成部件190a位于接触孔101上的方式配置凸块构成体1900。并且,一边加热一边在层叠方向上加压,从而由凸块构成体1900构成连接用凸块190,并且使连接用凸块190与各焊盘91a、92a、99a连接。然后,使连接用凸块190残留在各焊盘91a、92a、99a上,并且通过剥离部件192将凸块构成体1900从第2构成部件1000上除去。由此,连接用凸块190被配置于各焊盘91a、92a、99a。

335.然后,虽然没有特别图示,但通过沿着切割线dl分割为芯片单位,制造图39所示的半导体封装10。

336.由此,在如上述第7实施方式那样将半导体封装10经由焊料120向印刷基板110安装时,容易确保半导体封装10与印刷基板110的间隔,容易确保焊料120的厚度。因此,能够抑制焊料120的高度偏差。此外,由于容易确保半导体封装10与印刷基板110的间隔,所以还能够实现底部填充件130的注入性的提高。

337.(第28实施方式)

338.对第28实施方式进行说明。本实施方式相对于上述第1实施方式,变更了半导体封装10的制造方法。其他与上述第1实施方式是同样的,所以这里省略说明。

339.首先,在上述第1实施方式中,准备作为多连基板的构成基板210来制造半导体封装10。该情况下,例如如图41所示,将构成基板210的内缘部分作为构成区域210a并将构成基板210的外缘部分作为辅助区域210b,一边在辅助区域210b中形成定位孔部等一边由构成区域210a制造半导体封装10。

340.另外,在图41中,配置有一面金属膜22的区域为构成区域210a。并且,辅助区域210b以包围构成区域210a的方式配置。在这样的构成基板210中,辅助区域210b容易成为浪费的区域。

341.因此,在本实施方式中,如图42所示,将构成基板210的外缘部分也作为用来构成半导体封装10的构成区域210a。并且,将构成基板210的外缘部分的一部分作为辅助区域210b。即,构成基板210的外缘部分成为构成区域210a和辅助区域210b混合存在的状态。

342.在本实施方式中,在将构成基板210做成平面矩形状的情况下,将成为角部的部分作为辅助区域210b。另外,在图42中,没有形成一面金属膜22的区域成为辅助区域210b。该情况下,辅助区域210b如图42所示,优选的是以相对于构成基板210的中心为非对称的方式配置。由此,容易掌握构成基板210的位置关系,能够容易进行定位。

343.由此,不需要在构成基板210的外缘部的整体中配置辅助区域210b,所以能够有效地利用构成基板210。另外,这里,以上述第1实施方式的制造方法为例进行了说明,但在制造上述第2实施方式及上述第9实施方式的半导体封装10的情况下也是同样的。

344.(第29实施方式)

345.对第29实施方式进行说明。本实施方式相对于上述第1实施方式,在侧面构成部件700、第1构成部件900、第2构成部件1000中形成有槽部。其他与上述第1实施方式是同样的,所以这里省略说明。

346.在本实施方式中,如图43所示,在图5e的工序中,在侧面构成部件700、第1构成部件900及第2构成部件1000中的成为切割线dl的部分分别层叠形成有槽部701、901、1001的部件。

347.另外,槽部701、901、1001在通过图5b~图5d的工序来准备侧面构成部件700、第1构成部件900及第2构成部件1000时分别形成。此外,槽部701、901、1001例如通过激光等形成。并且,在本实施方式中,在构成基板210中不形成槽部211,但也可以在构成基板210中形成槽部211。然后,通过如图5f那样一边加热一边加压,将它们一体化。

348.这样,即使在侧面构成部件700、第1构成部件900、第2构成部件1000中形成槽部701、901、1001,也能够容易进行切割。此外,通过在侧面构成部件700、第1构成部件900、第2构成部件1000中形成槽部701、901、1001,在图5f的工序中进行了一体化之后,能够通过槽部701、901、1001降低构成各部件700、900、1000的lcp膜的热收缩的影响。

349.另外,在本实施方式中,说明了在将侧面构成部件700、第1构成部件900、第2构成部件1000一体化之前形成槽部701、901、1001的例子。但是,例如也可以在将侧面构成部件700、第1构成部件900、第2构成部件1000一体化之后在第2构成部件1000中形成槽部1001。

350.(第30实施方式)

351.对第30实施方式进行说明。本实施方式相对于上述第9实施方式,规定了板状部件74的制造方法。其他与上述第9实施方式是同样的,所以这里省略说明。

352.在本实施方式中,如以下这样制造构成密封部件60的板状部件74。即,首先,如图44a所示,准备lcp膜构成部件7400。此时,lcp膜构成部件7400如图45a所示,内部状态成为非晶形状态。

353.接着,对lcp膜构成部件7400进行加热处理,如图45b所示那样使其结晶化。另外,加热处理在比lcp膜构成部件7400的熔点温度小的温度即300℃左右下进行几十分钟~几小时。该情况下,优选的是,从270℃左右到300℃左右使温度阶段性地上升。由此,能够抑制lcp膜构成部件7400熔融。

354.此外,在与图44a不同的工序中,如图44b所示,准备由铜等构成的金属片构成部件7500。然后,如图44c所示,通过将lcp膜构成部件7400和金属片构成部件7500层压加工而一体化,从而形成板状部件构成部件770。另外,层压加工通过一边加热一边加压来进行。但是,lcp膜构成部件7400和金属片构成部件7500的层压加工中的加热时间相对于对上述lcp膜构成部件7400进行加热处理使其结晶化的工序而言是很短的时间。因此,仅通过该层压加工中的加热,lcp膜构成部件7400不会结晶化。

355.然后,虽然没有特别图示,但在根据需要适当进行了切断等之后,进行蚀刻等而成为所希望的形状的图案75并且配置构成连接通孔76的烧结体或导电性膏,从而构成板状部件74。

356.另外,这里以板状部件构成部件770为例进行了说明,但第1构成部件900及第2构成部件1000也同样地形成。

357.由此,lcp膜构成部件7400结晶化,所以在一边加热一边加压而将各板状部件构成部件770(即板状部件74)和半导体芯片30等一体化时,能够抑制图案75及连接通孔76的偏移。因此,能够抑制没有实现层叠方向上的相邻的板状部件74的电连接的情况。

358.(第31实施方式)

359.对第31实施方式进行说明。本实施方式相对于上述第9实施方式,将半导体封装10安装于印刷基板110而构成电子装置1。其他与上述第9实施方式是同样的,所以这里省略说明。

360.在本实施方式中,如图46所示,构成了具有半导体封装10、印刷基板110、冷却器140、推压部件300的电子装置1。

361.印刷基板110形成有在厚度方向上贯通的孔部116。此外,在印刷基板110,形成有从孔部116露出的多个端子部117。另外,在图46中,将印刷基板110的结构简化而表示,但印刷基板110与图15的印刷基板110同样,适当形成有一面布线图案111、贯通孔电极113等。

362.并且,半导体封装10通过使漏极用焊盘91a、源极用焊盘92a经由焊料120而与端子部117连接,从而被与印刷基板110连接。在与图46不同的截面中,半导体封装10通过使栅极用焊盘93a经由焊料120而与端子部117连接,从而被与印刷基板110连接。

363.此外,半导体封装10的散热部件20经由润滑脂等连接部件141而与冷却器140连接。

364.推压部件300由壳体等构成,具有向一方向突出的推压部301。推压部301由橡胶等弹性体构成,具备与和半导体封装10连接的端子部117的数量相同的数量。在本实施方式中,端子部117与漏极用焊盘91a、源极用焊盘92a、栅极用焊盘93a连接,所以具备3个推压部301。

365.并且,推压部件300配置为,印刷基板110的端子部117中的与各焊盘91a、92a、93a连接的部分被推压部301向半导体封装10侧推压。

366.这样,可以使用半导体封装10构成电子装置1。并且,在本实施方式的电子装置1中,由于端子部117中的与各焊盘91a、92a、93a连接的部分被推压,所以能够抑制半导体封装10与冷却器140的间隔偏差,并且通过使该间隔容易缩窄而能够提高散热性。

367.(第32实施方式)

368.对第32实施方式进行说明。本实施方式相对于上述第30实施方式,变更了电子装置1的结构。其他与上述第30实施方式是同样的,所以这里省略说明。

369.本实施方式的电子装置1的印刷基板110如图47所示,在印刷基板110中没有形成孔部116,是与第7实施方式同样的结构。并且,印刷基板110被螺钉等紧连部件118固定于冷却器140。另外,在图47中将印刷基板110的结构简化而表示,但印刷基板110与图15的印刷基板110同样,形成有一面布线图案111、贯通孔电极113等。

370.半导体封装10的漏极用焊盘91a及源极用焊盘92a经由焊料120而与印刷基板110的另一面布线图案112分别连接。此外,在与图13不同的截面中,半导体封装10的栅极用焊盘93a经由焊料120而与印刷基板110的另一面布线图案112连接。并且,在印刷基板110与半导体封装10之间配置有底部填充件130。

371.推压部件300的推压部301能够将印刷基板110整体向冷却器140侧推压。并且,推压部件300通过将印刷基板110向冷却器140侧推压,将半导体封装10向冷却器140侧推压。

372.即使这样经由印刷基板110将半导体封装10推压,也能够得到与上述第30实施方式同样的效果。此外,通过将印刷基板110直接推压,能够通过推压部301容易地吸收印刷基板110向半导体封装10的相反侧的翘曲及印刷基板110的厚度的偏差。

373.(第33实施方式)

374.对第33实施方式进行说明。本实施方式相对于上述第9实施方式,构成电子装置1。其他与上述第9实施方式是同样的,所以这里省略说明。

375.本实施方式的电子装置1如图48所示,在冷却器140上形成有凹部142。并且,半导体封装10经由o形圈等密封部件143而配置,以将凹部142的开口端堵塞。凹部142与未图示的冷却管等连接,冷却介质经由冷却管流动。即,凹部142形成为,构成流动冷却介质的冷却通路142a。另外,冷却介质例如使用水或通常的防冻液等。

376.此外,在本实施方式中,绝缘基板21的另一面21b形成有凹凸构造21c。另外,在图48中虽然省略,但与上述第31实施方式等同样,半导体封装10的各焊盘91a、92a、93a与印刷基板110电连接。

377.在这样的电子装置1中,冷却介质在凹部142中流动,从而能够进一步实现散热性的提高。此外,在本实施方式的电子装置中,在绝缘基板21的另一面21b侧构成有凹凸构造21c,能够使散热部件20与冷却介质的接触面积增加。因而,能够进一步实现散热性的提高。

378.(其他实施方式)

379.将本发明依据实施方式进行了记述,但应理解的是本发明并不限定于该实施方式及构造。本发明也包含各种各样的变形例及等价范围内的变形。除此以外,各种各样的组合及形态,进而在它们中仅包含一要素、其以上或其以下的其他组合及形态也落入在本发明的范畴及思想范围中。

380.在上述各实施方式中,各部件的接合也可以不是化学结合而是通过机械性接合使密接性提高。例如,在上述第1实施方式中,关于散热部件20和密封部件60,也可以对散热部件20进行等离子照射等而进行粗化处理,通过锚定效应使密接性提高。

381.此外,在上述第1实施方式等中,另一面金属膜23也可以不与一面金属膜22对称地形成,也可以不配置。此外,接合部件50也可以在层叠方向上配置在半导体芯片30内。进而,散热部件20也可以在层叠方向上配置在密封部件60内。即使做成这样的结构,通过将密封部件60用lcp构成,也能够得到与上述第1实施方式同样的效果。另外,在上述其他实施方式中,也可以在具有一面金属膜22及另一面金属膜23的情况下适当变更为这些结构。

382.进而,在上述第1实施方式中,例如,也可以不是在侧面构成部件700的第2贯通孔72中配置烧结体73a,而是在第2贯通孔72中通过cvd法等配置金属膜(即下方连接通孔73)。这样的结构对于第1构成部件900也是同样的。此外,这些结构在其他实施方式中也能够适当应用。

383.并且,在上述各实施方式中,半导体芯片30也可以形成有超结mosfet或igbt。此外,半导体芯片30也可以不是使用由硅或sic构成的支承基板31而是使用由氧化镓、氮化镓等构成的支承基板31而构成。

384.此外,在上述第1实施方式中,在制造半导体封装10时,在图5e及图5f的工序中也可以如以下这样。即,在图5e的工序中,也可以在将侧面构成部件700配置到构成基板210上并且在第1贯通孔71中经由烧结体50a配置了半导体芯片30之后,在低温下将它们临时接合。然后,可以在侧面构成部件700及半导体芯片30上依次层叠第1构成部件900及第2构成部件1000,进行图5f的工序而一体化。同样,在上述第2实施方式中,也可以在将构成侧面密封部件70的板状部件构成部件770与半导体芯片30等临时接合之后,将第1构成部件900及第2构成部件1000层叠而一体化。并且,这些制造方法在上述各实施方式中能够适当应用。

385.进而,在上述各实施方式中,如图49所示,也可以在形成于第1密封部件90的各图案91~93中分别形成狭缝91b~93b。具体而言,在各图案91~93中,形成有将与连接于上方连接通孔95、97的部分不同的部分除去了的狭缝91b~93b。由此,能够由狭缝91b~93b将应力释放,所以能够缓和从各图案91~93向上方连接通孔95、97施加的应力。该情况下,例如,如与源极用图案92连接的上方连接通孔97那样,通过在层叠方向上以将上方连接通孔97大致包围的方式形成狭缝92b,能够进一步缓和施加于上方连接通孔97的应力。另外,狭缝91b~93b也可以不是分别形成于各图案91~93,而是形成于某1个或2个图案。

386.此外,在上述第9实施方式中,也可以将下层连接通孔760如图50所示那样做成圆筒状。另外,这样的下层连接通孔760能够应用于具有下层连接通孔760的各实施方式。

387.进而,在上述第9实施方式中,各焊盘91a、92a、93a也可以如图51所示那样在层叠方向上形成在与连接通孔61不同的位置。换言之,各焊盘91a、92a、93a也可以在层叠方向上形成在不与连接通孔61重叠的位置。由此,当将印刷基板110经由焊料120等安装到各焊盘91a、92a、93a时,能够减小施加于连接通孔61的应力,能够抑制连接通孔61的损坏。该情况下,可以将源极用焊盘92a在层叠方向上如图51所示那样配置到连接通孔61与半导体芯片30之间,也可以如图52所示那样隔着连接通孔61而配置在与半导体芯片30相反侧。

388.进而,如图53所示,也可以是,连接通孔61在层叠方向上在与各焊盘91a、92a、93a不同的位置以各焊盘91a、92a、93a为中心在周向上配置多个。该情况下,多个连接通孔61优选的是在周向上以等间隔配置。由此,当将印刷基板110经由焊料120等安装于各焊盘91a、92a、93a时,应力容易被分散施加于各连接通孔61,能够抑制较大的应力被施加于半导体芯片30。另外,这些图51~图53那样的结构也能够适当应用于上述各实施方式。

389.此外,还能够将上述各实施方式适当组合。例如,也可以将上述第2实施方式适当与其他实施方式组合,将侧面密封部件70用多个板状部件74构成。此外,也可以将上述第3实施方式适当与其他实施方式组合,将接合部件50与连接通孔61接合并且不具备一面金属膜22及另一面金属膜23。进而,也可以将上述第4实施方式适当与其他实施方式组合,形成将漏极用图案91与漏极用区域22a连接的连接通孔61等,具备多个连接通孔61。并且,也可以将上述第5实施方式适当与其他实施方式组合,具备测试用图案98。进而,也可以将上述第6实施方式适当与其他实施方式组合,做成半导体芯片30具有绝缘基板41的结构,并且散热部件20由金属板24构成。并且,也可以将上述第7实施方式适当与其他实施方式组合,将多个半导体芯片30一体地用密封部件60密封。并且,在上述第8~上述第32实施方式中也能够分别适当应用。此外,也可以将组合了上述各实施方式的形态彼此进一步组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1