用于制造光电子半导体芯片的方法和光电子半导体芯片与流程

1.提出一种用于制造光电子半导体芯片的方法。此外,提出一种光电子半导体芯片。

技术实现要素:

2.要实现的目的在于,提出一种用于制造具有高的效率的相对小的光电子半导体芯片的方法。

3.所述目的尤其通过具有权利要求1的特征的方法来实现。优选的改进方案是其余权利要求的主题。

4.根据至少一个实施方式,方法用于制造光电子半导体芯片。制成的半导体芯片尤其是发光二极管芯片,简称led芯片。替选地,可以制造激光二极管芯片,例如表面发射的激光二极管芯片或还有边缘发射的激光二极管芯片。还可行的是,光电子半导体芯片是探测器芯片,尤其是光电二极管。

5.根据至少一个实施方式,所述方法包括步骤:生长半导体层序列。尤其,在生长衬底上沿着生长方向生长半导体层序列。生长衬底尤其是gaas衬底。

6.半导体层序列优选基于iii-v族化合物半导体材料。特别优选地,半导体层序列基于磷化物材料体系alingaasp。在此,半导体层序列不仅包括al而且包括in、ga和p。as形成半导体层序列的可选的组成部分。在此,半导体层序列可以具有掺杂材料以及附加的组成部分。然而,为了简单性,仅说明半导体层序列的晶格的主要组成部分,即al、as、ga、in或p,即使所述主要组成部分也可以部分地由少量其他材料替代和/或补充也如此。

7.对于alingaasp或alingap替选地,半导体层序列也可以基于alingan或alingaas。alingaasp或alingap的下面的实施方案可以相应地适用于alingan或alingaas,其中于是n或as分别取代p。

8.根据至少一个实施方式,半导体层序列包括有源区。有源区优选设立为用于产生辐射,替选地然而可以构成用于探测辐射。有源区尤其是多量子阱结构,英语:multi quantum well structure或简称mqw。在有源区中,量子阱层和势垒层彼此交替地设置。尤其,有源区由交替设置的量子阱层和势垒层构成。

9.根据至少一个实施方式,所述方法包括步骤:产生结构化的掩模层。掩模层可以是半导体层序列的一部分从而在制成的半导体芯片中仍可以存在。替选地,掩模层是特别针对所述目的制造的层,例如是软质掩模,如光刻胶层,或是硬质掩模,如氧化物层。

10.根据至少一个实施方式,所述方法包括步骤:将量子阱层和势垒层局部地混匀。混匀借助于施加混匀辅助材料执行。混匀辅助材料,尤其是锌穿过掩模层的开口引入到有源区中,使得混匀辅助材料位于至少一个混匀区域中。通过混匀辅助材料引起半导体层序列的晶体组分,尤其是al、ga和/或in的混匀。在混匀时,优选施加明显高于室温还有制成的半导体芯片的随后的常规运行温度的温度。

11.混匀可以均匀地在所有量子阱层之上进行。替选地,混匀不均匀地进行。混匀区域优选完全地穿过有源区伸展直至n型掺杂的区域中。更确切地,优选地,在每有源区或在有

源区的每个侧边仅存在唯一的混匀区域,然而在每有源区或在每侧边也可以存在多个混匀区域,所述混匀区域可以沿着生长方向由未混匀的区域中断。

12.根据至少一个实施方式,所述方法包括步骤:将半导体层序列分割为用于半导体芯片的子区域。分割例如借助于刻蚀进行,替选地然而也可以借助于锯割或刻刮和折断进行。

13.根据至少一个实施方式,生长由[(al

x

ga

1-x

)yin

1-y

]zp

1-z

构成的势垒层。在此优选适用x≥0.5或x≥0.6或x≥0.7或x≥0.8或x≥0.9。可行的是,适用x=1,从而势垒层,如生长那样,不具有或基本上不具有ga。

[0014]

在至少一个实施方式中,所述方法用于制造光电子半导体芯片并且具有以下步骤,特别优选地以给定的顺序:

[0015]

a)在生长衬底上沿着生长方向生长alingaasp半导体层序列,其中半导体层序列包括用于产生辐射的有源区,并且有源区由多个、彼此交替的量子阱层和势垒层组成;

[0016]

b)产生结构化的掩模层;

[0017]

c)在至少一个混匀区域中借助于将混匀辅助材料穿过掩模层的开口施加到有源区中来局部地混匀量子阱层和势垒层;并且

[0018]

d)将半导体层序列分割成用于半导体芯片的子区域,其中势垒层在步骤a)中由[(al

x

ga

1-x

)yin

1-y

]zp

1-z

生长,其中x≥0.5,或者优选x≥0.6。

[0019]

借助在此所描述的方法可行的是,特别是在半导体层序列的侧面处具有小的边长的led芯片中尤其减少或消除不进行辐射的载流子复合,从而减少或消除损耗通道。由此,可产生具有小的横向尺寸和高的效率的半导体芯片。

[0020]

杂质的局部扩散和量子阱的随后的混匀,也称为quantum well intermixing(量子阱混杂),是一种专门改善光电子半导体芯片的小电流性能的可行的方法。这尤其适用于具有小尺寸的发光二极管芯片,也称为μled,特别是具有在红色光谱范围中的发射。在此,应维持足够长的扩散时间,尤其是在movpe反应器中,以便在具有密集封装的μled的晶片上实现显著程度的混匀。

[0021]

然而,混匀的程度不仅取决于扩散时间,而且也取决于μled的封装因数。在此,当封装因数升高时,混匀的程度趋于降低。借助在此所描述的方法可行的是,减少在制造期间的时间耗费,尤其是扩散时间,和/或在晶片上密集封装的、尤其发红光的μled的情况下实现在有源区中的提高的混匀程度。

[0022]

将杂质、如锌的局部扩散与量子阱和势垒层的由杂质引起的混匀组合,以改善基于alingaasp材料体系的μled中的效率。在此,在常规的led结构中,势垒层具有大约50%的铝份额,通过[(al

x

ga

1-x

)yin

1-y

]zp

1-z

中的变量x表达。这种相对低的铝含量的原因是,启动电压随着较高的铝含量通常升高,特别是在具有数10个势垒层和量子阱层的有源区中。而在此处描述的方法中,生长具有至少60%、优选至少80%的明显更高的铝份额的势垒层。

[0023]

在基于algainp的μled中,有源区中的量子阱层和势垒层的数量通常限制为最高50。尽管如此,到有源区中的电流注入在量子阱层之上均匀地进行。如果使用混匀步骤,则应仔细地选择有源区中的层的设计。为了避免对于载流子在μled的侧壁处的不进行辐射的复合的复合中心从而同样为了避免效率降低,对于具有为50%的铝份额x的势垒,典型的阻挡势垒约为65mev。对于铝份额x为85%的势垒层,该值为140mev。

[0024]

这适用于相同的工艺时间。也就是说,由于更高的铝份额,相同的工艺时间导致增强的混匀从而制成的半导体芯片的改进的效率。此外,在μled的制造工艺中,混匀通常是困难的,使得在这种μled中的混匀通常可以借助在此所描述的方法来改进。此外,借助具有高的铝份额x的势垒产生的混匀区域具有带有间接跃迁的带隙。也就是说,可以显著地减少在混匀区域中与混匀辅助材料的进行辐射的复合和不进行辐射的复合,由此制成的发光二极管的效率提高。

[0025]

此外,借助在此所描述的方法可行的是,尤其是在μled的情况下,通过势垒层的在有源区之上沿着生长方向变化的构型来影响到量子阱层中的电流注入的均匀性。

[0026]

根据至少一个实施方式,掩模层由半导体层序列的接触层、尤其是p型接触层形成。替选地,使用单独的掩模层,例如呈相应结构化的永久的钝化层的形式或呈诸如光刻胶层的临时层的形式。

[0027]

根据至少一个实施方式,接触层,特别是p型接触层在步骤b)中完全地由开口穿透。也就是说,局部地将接触层完全地去除。

[0028]

在此,接触层优选地包括alvga

1-v

as或者由其构成。尤其适用v≤0.35或v≤0.1。替选地或附加地,适用v≥0,尤其v≥0.01或v≥0.05。接触层也可以是由gaas层和由这种algaas层形成的组合。

[0029]

根据至少一个实施方式,步骤c)中的混匀沿着生长方向完全穿过有源区进行。也就是说,混匀区域朝向生长衬底完全穿透有源区。替选地,虽然混匀区域伸展穿过有源区,但是不伸展至或仅局部地伸展至生长衬底。

[0030]

根据至少一个实施方式,步骤d)中的分割仅在至少一个混匀区域中进行。这尤其适用于在半导体层序列的俯视图中、尤其是在接触层的俯视图中观察。半导体层序列的在分割时产生的侧面因此至少部分地或也完全地由至少一个混匀区域形成。

[0031]

根据至少一个实施方式,量子阱层在步骤a)中由[(alaga

1-a

)bin

1-b

]cp

1-c

生长。在此,尤其适用0《a≤0.3或0.05≤a≤0.2。经由量子阱层中的铝份额,尤其可以设定有源区的最大强度的发射波长。可行的是,所有量子阱层名义上相同地生长,即在关于其材料组成以及关于其厚度的制造公差的范围中彼此没有差异。替选地可行的是,生长不同地构造的量子阱层,使得例如在有源区中沿着生长方向实现量子阱层的厚度变化曲线或铝含量的变化曲线。这种具有变化的特性的量子阱层也称为啁啾(chirped)mqw。

[0032]

根据至少一个实施方式,0.47≤y≤0.53以及0.47≤z≤0.53和/或0.47≤b≤0.53以及0.47≤c≤0.53或者还有0.48≤y≤0.52和0.48≤z≤0.52和/或0.48≤b≤0.52以及0.48≤c≤0.52适用于由[(alaga

1-a

)bin

1-b

]cp

1-c

构成的量子阱层和适用于由[(al

x

ga

1-x

)yin

1-y

]zp

1-z

构成的势垒层。此外,优选适用c《0.5以及z《0.5和/或b》0.5以及y》0.5。

[0033]

b、c、y和z的上述值尤其在半导体层序列在gaas生长衬底上的晶格匹配的或准晶格匹配的生长的情况中适用。替选地,可以有针对性地张紧地生长有源区,使得有针对性地考虑与上述区域不同的y、z和/或b、c的值。

[0034]

根据至少一个实施方式,步骤c)包括半导体层序列的热处理。

[0035]

例如,在至少0.2小时或0.5小时和/或最多10小时或2小时的时长中存在升高的温度。升高的温度例如至少为400℃或500℃和/或最多700℃或600℃。尤其,该温度在500℃和540℃之间、其中包含边界值。

[0036]

根据至少一个实施方式,有源区位于第一半导体区域和第二半导体区域之间。第一和/或第二半导体区域可以分别由一个或多个子层组成。尤其,第二半导体区域包括多个子层。例如,第一半导体区域是n型掺杂的,而第二半导体区域是p型掺杂的。在这种情况下,p型接触层可以是第二半导体区域在步骤a)之后距离有源区最远的子层。

[0037]

根据至少一个实施方式,开口朝有源区的方向穿过接触层伸展进入其余的第二半导体区域至少50nm或至少100nm。在此,这些开口距有源区一定间距地终止。距有源区的间距优选至少为150nm或250nm或300nm。第二半导体区域的总厚度尤其至少为0.3μm或0.4μm。替选地或附加地,总厚度例如可以最多为10μm或1μm或0.6μm。在此,p型接触层优选仅具有相对小的厚度,例如最多50nm或20nm和/或至少4nm或8nm的厚度。

[0038]

根据至少一个实施方式,用于半导体芯片的半导体层序列的在步骤d)中产生的子区域在俯视图中观察分别具有最多150μm或100μm或70μm或30μm或10μm的平均边长。因此,制成的半导体芯片是μled。如果在俯视图中观察子区域不是正方形的或矩形的,则可以使用子区域的平均直径来代替平均边长。

[0039]

根据至少一个实施方式,在步骤d)之后,至少一个混匀区域沿垂直于生长方向的方向伸展进入有源区至少0.1μm或0.2μm。替选地或附加地,该值最多为1.5μm或1μm或0.5μm或0.3μm。也就是说,在俯视图中观察,仅相对小份额的有源区被混匀。也就是说,在俯视图中观察,混匀区域相对于有源区是相对小的,并且又在俯视图中观察,尤其最多为有源区的面积的3%或1%或0.2%。

[0040]

根据至少一个实施方式,至少一个混匀区域沿平行于生长方向的方向伸展完全穿过半导体层序列。也就是说,混匀区域可以伸展至生长衬底或也伸展进入生长衬底。

[0041]

根据至少一个实施方式,有源区在步骤a)之后包括至少2个或3个或4个量子阱层。替选地或附加地,量子阱层的数量为最多50个或30个或20个或10个或5个。

[0042]

根据至少一个实施方式,量子阱层分别具有至少2nm或4nm的厚度。替选地或附加地,量子阱层的厚度分别最多为15nm或10nm或7nm或4nm。

[0043]

根据至少一个实施方式,势垒层分别具有至少2nm或3nm或5nm的厚度。替选地或附加地,势垒层的厚度分别最多为353nm或25nm或15nm或10nm。尤其,势垒层的厚度为7nm,例如具有最多1nm或2nm的公差。

[0044]

根据至少一个实施方式,有源区设立为用于产生至少560nm或590nm或610nm或620nm的最大强度的发射波长。替选地或附加地,最大强度的发射波长最多为670nm或655nm或635nm。也就是说,制成的半导体芯片尤其设立为用于产生红光。

[0045]

根据至少一个实施方式,势垒层生长为,使得一些或所有势垒层在步骤a)之后并且至少还在步骤c)之前具有不同的铝份额。直接彼此跟随的势垒层的块名义上可以相同地生长。可行的是,势垒层成对地具有彼此不同的铝份额。

[0046]

根据至少一个实施方式,在步骤a)之后和在步骤c)之前,所涉及的铝份额在相应的势垒层内是恒定的。也就是说,各个势垒层随后,分别在所涉及的势垒层内观察,在铝份额中没有梯度地生长。替选地,可以早已在步骤a)中使各个势垒层以一定的铝梯度过度生长。

[0047]

根据至少一个实施方式,在步骤a)之后和直至至少在步骤c)之前,有源区中的势垒层的最小和最大铝份额相差至少1.05倍或1.1倍或1.2倍。替选地或附加地,该份额相差

最多为1.7或1.6或1.5或1.4倍。

[0048]

根据至少一个实施方式,一些或所有的势垒层具有彼此不同的厚度。在此,可以将相同厚度的势垒层以块的方式组合或所有势垒层成对地具有彼此不同的厚度。

[0049]

根据至少一个实施方式,有源区中的势垒层的最小和最大厚度相差至少1.2倍或1.5倍或2倍或2.5倍。替选地或附加地,所述厚度相差至多为8或6或4或3倍。

[0050]

根据至少一个实施方式,有源区中的势垒层至少在步骤a)之后直到步骤c)之前关于厚度变化和/或铝份额变化不对称地设置。也就是说,在势垒层的设计的方面,在有源区中不存在垂直于生长方向定向的对称平面。替选地,势垒层对称地分布,使得在有源区中关于势垒层存在这样的对称平面。

[0051]

根据至少一个实施方式,混匀辅助材料是锌。在步骤c)中,锌尤其借助于气相沉积施加,例如以二乙基锌的形式,简称dezn,或作为二甲基锌,简称dmzn。对于锌替选地或附加地,可以使用镁,例如借助于双(环戊二烯基)镁,简称cp2mg施加镁。

[0052]

根据至少一个实施方式,在步骤d)之后,在步骤e)中,将至少一个钝化层施加到切开的混匀区域上,即施加到半导体层序列的在分割中产生的侧面上。钝化层例如由诸如二氧化硅的氧化物或诸如氮化硅的氮化物构成。钝化层的厚度优选是相对小的并且例如至少为50nm和/或至多为250nm。

[0053]

根据至少一个实施方式,在步骤c)之后,直接在步骤c)之后或者也在另外的中间步骤之后才去除生长衬底。尤其,可以在去除生长衬底之前将替代载体安置在半导体层序列处。这种替代载体优选在步骤d)中的分割之前安置。分割,即步骤d),可以在去除生长衬底之前或之后执行,这取决于何时安置可选的替代载体。

[0054]

此外,提出一种光电子半导体芯片。优选借助结合一个或多个上述实施方式所描述的方法来制造半导体芯片。因此,半导体芯片的特征也对该方法公开,并且反之亦然。

[0055]

在至少一个实施方式中,光电子半导体芯片包括alingaasp半导体层序列,其中所述半导体层序列包括用于产生辐射的有源区并且该有源区由多个彼此交替的量子阱层和势垒层组成。半导体层序列包括结构化的掩模层,尤其是p型接触层。量子阱层和势垒层在有源区中在混匀区域中局部地混匀,并且在混匀区域中存在混匀辅助材料,尤其是锌。在俯视图中观察,混匀区域优选在闭合轨迹中在四周围绕半导体层序列延伸。势垒层在混匀区域之外由[(al

x

ga

1-x

)yin

1-y

]zp

1-z

构成,其中x≥0.5或x≥0.8或x≥0.9或x=1。

[0056]

根据至少一个实施方式,半导体芯片是平均边长最多为50μm的发红光的发光二极管芯片。沿垂直于半导体层序列的生长方向的方向,混匀区域伸展进入有源区中至少0.1μm和/或最多0.5μm。

附图说明

[0057]

下面,根据实施例参照附图详细阐述在此所描述的方法和在此所描述的光电子半导体芯片。在此,相同的附图标记说明在各个附图中相同的元件。在此然而没有示出符合比例的关系,更确切地说为了更好的理解,个别元件可以夸大地示出。

[0058]

附图示出:

[0059]

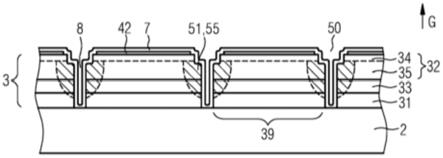

图1至5示出用于在此所描述的光电子半导体芯片的在此所描述的制造方法的一个实施例的方法步骤的示意剖面图;

[0060]

图6和7示出用于在此所描述的光电子半导体芯片的在此所描述的制造方法的一个实施例的方法步骤的示意剖面图;

[0061]

图8示出用于在此所描述的光电子半导体芯片的制造方法的一个实施例的方法步骤的示意剖面图;

[0062]

图9示出用于在此所描述的光电子半导体芯片的制造方法的一个实施例的方法步骤的示意俯视图;

[0063]

图10示出在半导体芯片的变型中的铝份额的变化曲线的示意图;以及

[0064]

图11至14示出在此所描述的光电子半导体芯片的实施例的铝变化曲线的示意图。

具体实施方式

[0065]

在图1至5中图解说明用于光电子半导体芯片1的制造方法的实施例。根据图1,在生长衬底2处沿着生长方向g外延生长半导体层序列3。

[0066]

半导体层序列3直接在生长衬底2处包括第一半导体区域31,例如n型掺杂区域。在图中,第一半导体区域31分布仅作为层示出。与此不同,第一半导体区域31可以由多个子层组成。尤其,朝向生长衬底2的第一半导体区域31具有未示出的缓冲层和/或未示出的n型接触层。

[0067]

在远离生长衬底2的方向上,第一半导体区域31跟随有用于产生辐射的有源区33。有源区33包括交替设置的多个量子阱层61和势垒层62。尤其,在制成的半导体芯片1运行时,在有源区33中产生橙色的或红色的光。

[0068]

沿着生长方向g,有源区33跟随有第二半导体区域32。例如,第二半导体区域32是p型掺杂的。第二半导体区域32包括p型接触层34,作为距生长衬底2最远的最上层。因此,在p型接触层34和有源区33之间存在其余的第二半导体区域35。

[0069]

半导体层序列3基于材料体系algainasp。在此,量子阱层优选由[(alaga

1-a

)bin

1-b

]cp

1-c

构成,其中0.1≤a≤0.3,取决于要产生的波长。势垒层由[(al

x

ga

1-x

)yin

1-y

]zp

1-z

构成,其中x≥0.6,尤其x≥0.8。由此,势垒层具有相对高的铝份额x。p型接触层34尤其由alvga

1-v

as构成,其中v≤0.2。对于参数b、c、y和z,尤其适用的是,这些参数在0.5左右,特别是0.51或0.49。例如,有源区33包括在5个和15个之间、其中包含边界值的量子阱层62。

[0070]

在图2的方法步骤中示出,穿过p型接触层34产生多个开口50。开口50伸展到其余的第二半导体区域35中。开口50的深度例如处于50nm和200nm之间、其中包含边界值。开口50与有源区33之间的间距优选至少为300nm。其余的第二半导体区域35例如具有在300nm至600nm之间、其中包含边界值的厚度。p型接触层34的厚度例如处于5nm和20nm之间、其中包含边界值。

[0071]

因此,p型接触层34同时用作为用于后续工艺步骤的掩模层5,参见图3。可选地,在图2和3的步骤中,在p型接触层34上在开口旁边安置未示出的另外的掩模层,例如光刻胶层。然而这种另外的掩模层也可以在图3的方法步骤之前已经去除,借助所述另外的掩模层在p型接触层34中产生开口50。

[0072]

在图3中图解说明,将气态的前驱体56引向半导体层序列3。前驱体56例如是dmzn或dezn。因此经由前驱体56提供锌作为混匀辅助材料55。对于从气相提供的替代方案,也可以沉积用于混匀辅助材料55的固体层,例如几纳米厚的锌层。

[0073]

混匀辅助材料55优选在例如大约550℃的提高的温度扩散到半导体层序列3中。在此,algaas-p型接触层34对混匀辅助材料55而言是不可穿透的。

[0074]

因此,在开口50处分别形成混匀区域51,在所述混匀区域中存在混匀辅助材料55。在混匀区域51中进行势垒层62的材料和量子阱层61的材料的混匀。这在更下文中结合图11至14示出。

[0075]

例如,混匀区域51伸展到p型接触层34下方至少0.2μm或0.5μm。相应内容也可以适用于所有其他实施例。

[0076]

在图4的方法步骤中图解说明,半导体层序列3在开口50的区域中分割成用于半导体芯片1的子区域39。这种分割例如借助于刻蚀进行。因此,在子区域39之间形成分割槽8。与图4中的示图不同,分割槽8也可以伸展至生长衬底2中。在俯视图中观察,子区域39的边长在此优选是小的并且小于100μm或50μm。

[0077]

分割槽8分别位于混匀区域51的区域中。由分割槽8产生半导体层序列3的侧壁,所述侧壁根据图4分别仅部分地由混匀区域51形成。在朝向生长衬底2的方向上,混匀区域51在p型接触层34的朝向有源区33的一侧开始。混匀区域51优选延伸到p型接触层34下方,如图所示。

[0078]

此外,在图4中图解说明,将多个第二电极42施加到p型接触层34上以及产生钝化层7。未示出用于产生第二电极42和/或用于产生钝化层7的掩模层。

[0079]

在图5中还作为选项示出,从子区域去除生长衬底。在第一半导体区域31处安置第一电极41。钝化层7尽可能从第二电极42去除。由此,半导体芯片1优选是用于产生红光的发光二极管芯片。

[0080]

电极41、42在图5中仅示意地表明。包括至少一种金属和/或透明导电氧化物的电极41、42例如设计为如在图3和在文献us 2012/0248494 a1的第59至62段中描述的那样。该文献的公开内容,尤其图3和第59至62段,通过参引结合于此。

[0081]

在图6和7中示出另一制造方法,其中仅图解说明几个方法步骤。其余的方法步骤可以类似于图1至图5进行。

[0082]

根据图6,穿过开口50施加混匀辅助材料55并且产生混匀区域51。在此,使用单独的掩模层5,其不是半导体层序列3的子层。例如,掩模层5为硬质掩模,例如由氮化硅或二氧化硅构成。由此,混匀区域51可以伸展至掩模层5。

[0083]

在图6中还示出,混匀区域51完全穿透半导体层序列3从而伸展至生长衬底2。在图1至5的方法中,混匀区域51的相应构型也是可能的。

[0084]

根据图7,产生分割槽8,所述分割槽至少伸展至生长衬底2。因此,半导体层序列3的侧壁从而分割槽8的侧壁可以在掩模层5下方的区域中完全由混匀区域51形成。

[0085]

可行的是,掩模层5也可以用作为用于产生分割槽8的掩模。也就是说,在俯视图中,分割槽8和开口50可以彼此全等地伸展,与图1至5中的示图不同。相应的分割槽8也可以替选地在该方法中考虑,如结合图1至5图解说明的。

[0086]

在图8的方法中图解说明,p型接触层34又用作为掩模层5。在此,在所述情况中,在俯视图中观察,分割槽8和开口50也全等地设置。然而不强制要求,分割有关的混匀区域51在分割之后还仍然伸展至生长衬底2。例如,混匀区域51仅伸展到直至生长衬底2的区域中,随后通过分割将其去除。在图1至5以及图6和7的方法中,相应的设置也是可行的。

[0087]

在图9中示意地示出在分割之后的半导体层序列3的俯视图,尤其如在图6和7的方法中以及在图8的方法中所示的那样。也就是说,分割槽8和开口50全等地伸展。同样可以使用具有比开口50更窄的分割槽8的相应的结构。

[0088]

混匀区域51分别在四周以闭合的轨迹环绕半导体层序列3的子区域39。用于半导体芯片1的子区域39分别近似正方形地或者也矩形地构成。子区域39的边长小于100μm。相邻的子区域39之间的间距从而开口50和分割槽8的宽度优选是相对小的,并且例如最多为子区域39的平均边长的最高10%或5%或2%。尤其,开口50和/或分割槽8的宽度最高为5μm或3μm或1μm和/或至少为0.5μm或1μm。也就是说,子区域39在生长衬底2上以密集封装的方式设置,使得对混匀辅助材料55的扩散留有相对小的空间。

[0089]

在图10中示出半导体芯片的一个变型10。在此,关于生长方向g以百分比说明的方式绘制铝份额与铝份额和镓份额的总和的比值。左边的图部分涉及有源区33的未混匀的区域52,而右侧的图部分涉及有源区33的混匀区域51。在图11至14中也使用相同的示图。

[0090]

势垒层62具有相对低的铝份额。由此在混匀之后在混匀区域51中出现铝份额的相对平坦的变化曲线,从而与量子阱层61相比带隙的相对小的提高。由此,在子区域39从而半导体芯片1的侧壁处的载流子的复合损失只能相对差地减少。在传统的led中,这种边缘效应几乎没有意义,因为相对于有源区的总面积,边缘线仅有次要意义。而在此处所描述的μled的情况下,由于子区域39的小的边长,侧壁处的相应的效应是潜在的显著的损耗通道。

[0091]

在图11中示出半导体芯片1的实施例的铝份额的变化曲线。势垒层62与在图10中相比具有大约85%的明显更高的铝份额。在混匀区域51中,由此得出在未混匀的区域52中的量子阱层61与混匀区域51中的混匀结构之间的明显更高的带隙。

[0092]

根据图11,所有的量子阱层51和势垒层62都相同地生长,从而在未混匀的区域52中沿着生长方向g保持不变。相反,根据图12至14的势垒层62在厚度和/或材料成分方面分别具有至少一个梯度。

[0093]

因此,根据图12,势垒层62构造为沿着生长方向g具有减少的铝份额。根据图13,势垒层62的铝份额沿着生长方向g保持不变,但势垒层62的厚度减小。图14是图12和13中的构型的组合,使得沿着生长方向g,铝份额减小并且势垒层的厚度变小。

[0094]

在图11至14中,分别仅为了简化示图而示出五个量子阱层61。在有源区33中可以存在分别多于或少于所示的量子阱层。

[0095]

图12至14的势垒层62不对称地设置在有源区33中,使得有源区33不具有势垒层62关于其镜像对称地构造的对称平面。替选地,势垒层62的对称次序也是可行的,使得例如类似于图12,势垒层62的铝含量沿着生长方向g首先升高并且然后以相同程度下降。相应内容适用于根据图13和14的实施方式。

[0096]

与图12至14的示图不同地同样分别可行的是,生长方向g并非从左到右伸展,而是从右到左伸展。此外,由增多和下降的铝含量以及升高和下降的层厚度构成的不对称的组合以及它们的相应的组合分别是可能的。也就是说,沿着生长方向g观察,可以存在铝含量首先升高并且然后下降或者铝含量首先下降并且然后升高的不对称分布的势垒层62。相应内容在厚度方面适用,参见图13,或适用于厚度变化和铝含量变化的组合,参见图14。

[0097]

除非另有说明,否则在附图中所示的组件优选以给定的顺序分别直接彼此跟随。在图中未接触的层优选彼此间隔开。如果线彼此平行地绘制,则相应的面优选同样彼此平

行地定向。同样,除非另有说明,否则在图中正确地再现示出的组件彼此间的相对位置。

[0098]

在此所描述的发明不限于根据实施例的描述。更确切地说,本发明包括任意新特征和特征的任意组合,这尤其包括权利要求中的特征的任意组合,即使所述特征或者所述组合本身没有明确地在专利权利要求或实施例中说明也如此。

[0099]

本技术要求德国专利申请102019126506.1的优先权,其公开内容通过引用结合于此。

[0100]

附图标记列表

[0101]1ꢀꢀꢀ

光电子半导体芯片

[0102]2ꢀꢀꢀ

生长衬底

[0103]3ꢀꢀꢀ

半导体层序列

[0104]

31

ꢀꢀ

第一半导体区域(n型区域)

[0105]

32

ꢀꢀ

第二半导体区域(p型区域)

[0106]

33

ꢀꢀ

有源区

[0107]

34

ꢀꢀ

p型接触层,尤其是alvga

1-v

as

[0108]

35

ꢀꢀ

其余的第二半导体区域

[0109]

39

ꢀꢀ

半导体层序列的子区域

[0110]

41

ꢀꢀ

第一电极

[0111]

42

ꢀꢀ

第二电极

[0112]5ꢀꢀꢀ

掩模层

[0113]

50

ꢀꢀ

开口

[0114]

51

ꢀꢀ

半导体层序列的混匀区域

[0115]

52

ꢀꢀ

半导体层序列的未混匀的区域

[0116]

55

ꢀꢀ

混匀辅助材料

[0117]

56

ꢀꢀ

用于混匀辅助材料的前驱体

[0118]

61

ꢀꢀ

量子阱层,尤其是[(alaga

1-a

)bin

1-b

]cp

1-c

[0119]

62

ꢀꢀ

势垒层,尤其是[(al

x

ga

1-x

)yin

1-y

]zp

1-z

[0120]7ꢀꢀꢀ

钝化层

[0121]8ꢀꢀꢀ

分割槽

[0122]

10

ꢀꢀ

半导体芯片的变型

[0123]gꢀꢀꢀ

半导体层序列的生长方向

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1