用于处理基板的方法和设备与流程

用于处理基板的方法和设备

领域

1.本公开内容的实施例总体涉及用于处理基板的方法和设备,且更具体地涉及使用被配置成在基板上执行pvd和预清洁工艺的物理气相沉积(pvd)腔室的方法和设备。

背景技术:

2.已知将工艺腔室配置成执行预清洁工艺。例如,在凸块下金属化(under bump metallization;ubm)中,此类腔室被配置成在用于在基板上沉积一个或多个阻挡层(例如,钛(ti)、铜(cu)、钨(w)等等)的pvd之前,去除基板的金属接触垫上的原生氧化物和其他材料。预清洁腔室通常使用(由rf等离子体引发的)离子轰击以去除金属接触垫上的原生氧化物。例如,预清洁工艺可从金属接触垫蚀刻掉原生氧化物。预清洁工艺被配置成降低基板上的金属接点之间的接触电阻,以改善基板上的集成电路(ic)的性能和功耗。

3.在预清洁基板之后,将基板从预清洁腔室移动至一个或多个其他工艺腔室以用于进一步处理。例如,如上文所述,可将基板从预清洁腔室移动至pvd腔室,使得可在基板上形成一个或多个附加的阻挡层。但是,不幸的是,当将基板从预清洁腔室移动至pvd腔室时,基板暴露于大气可导致金属接点上形成额外的原生氧化物,这进而可对基板上的集成电路(ic)的性能和功耗产生负面影响。

4.因此,发明人已经提供了使用被配置成在基板上执行pvd和预清洁工艺两者的pvd腔室的方法和设备。

技术实现要素:

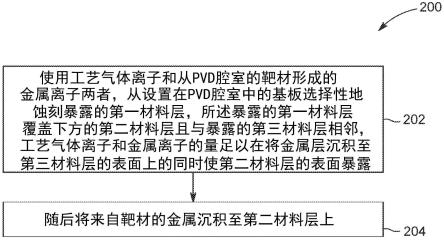

5.本文提供用于处理基板的方法和设备。在一些实施例中,例如,用于在物理气相沉积(pvd)腔室中处理基板的方法可包括:使用工艺气体离子和从pvd腔室的靶材形成的金属离子两者,从设置在pvd腔室中的基板选择性地蚀刻暴露的第一材料层,所述暴露的第一材料层覆盖下方的第二材料层且与暴露的第三材料层相邻,工艺气体离子和金属离子的量足以在将金属层沉积至第三材料层上的同时使第二材料层暴露;以及随后将来自靶材的金属沉积至第二材料层上。

6.根据至少一些实施例,用于处理基板的物理气相沉积(pvd)腔室包括:dc功率源和rf功率源;靶材,所述靶材用于形成金属离子,所述金属离子被溅射至设置在pvd腔室的处理容积内的基板的表面上;气体源,所述气体源用于将至少一种工艺气体提供至pvd腔室的处理容积内;以及控制器,所述控制器耦接至dc功率源和rf功率源,并被配置成:使用工艺气体离子和金属离子两者,从基板选择性地蚀刻暴露的第一材料层,所述暴露的第一材料层覆盖下方的第二材料层且与暴露的第三材料层相邻,工艺气体离子和金属离子的量足以在将金属层沉积至第三材料层上的同时使第二材料层暴露;以及随后将来自靶材的金属沉积至第二材料层上。

7.根据至少一些实施例,一种非瞬时计算机可读存储介质,所述非瞬时计算机可读存储介质具有存储于其上的指令,所述指令在由处理器执行时,执行用于处理物理气相沉

积(pvd)腔室中的基板的方法。所述方法包括:使用工艺气体离子和从pvd腔室的靶材形成的金属离子两者,从设置在pvd腔室中的基板选择性地蚀刻暴露的第一材料层,所述暴露的第一材料层覆盖下方的第二材料层且与暴露的第三材料层相邻,工艺气体离子和金属离子的量足以在将金属层沉积至第三材料层上的同时使第二材料层暴露;以及随后将来自靶材的金属沉积至第二材料层上。

8.本公开内容的其他和进一步实施例描述于下文。

附图说明

9.通过参照在附图中描绘的本公开内容的说明性实施例,可以理解上面简要概述并在下文更详细地讨论的本公开内容的实施例。然而,附图仅示出了本公开内容的典型实施例,因此不应视为对范围的限制,因为本公开内容可以允许其他等效实施例。

10.图1为根据本公开内容的至少一些实施例的工艺腔室的示意性剖面图。

11.图2为根据本公开内容的至少一些实施例的用于处理基板的方法的流程图。

12.图3a至图3c为根据本公开内容的至少一些实施例的示出使用图2的方法处理的基板的多个阶段的示意图。

13.为了便于理解,尽可能使用相同的附图标记来表示图中共有的相同要素。附图未按比例绘制,并且为清楚起见可以简化。一个实施例的要素和特征可以有益地并入其他实施例中,而无需进一步叙述。

具体实施方式

14.本文描述了使用被配置成在基板上执行pvd和预清洁(或蚀刻)工艺的pvd腔室的方法和设备的实施例。本文描述的pvd腔室克服了与用来执行pvd和预清洁工艺的常规方法和设备相关联的缺点。例如,由于在相同的腔室中执行pvd和预清洁工艺两者,因此从预清洁工艺至pvd工艺之间没有排队时间(例如,基板暴露于大气),所以排除了基板的金属垫再次氧化的可能性。此外,由于在相同的腔室中执行pvd和预清洁工艺两者,因此将提升基板的处理产量。而且,(例如,在基板上执行预清洁工艺之前)有时可能存在于基板上的聚合物不会因为通常在将基板移出预清洁腔室之前在基板上执行的除气工艺而被无意中去除(聚合物分解)。更具体地,根据本公开内容,由于在预清洁工艺中使用金属离子和气体离子的组合,因此在预清洁工艺期间,可能存在于基板上的任何聚合物被金属离子钝化(例如,被金属离子覆盖)。因此,在将气体离子从pvd腔室移除的除气工艺期间可保护聚合物免受聚合物分解。

15.图1为根据本公开内容的至少一些实施例的用于处理基板104(或晶片)的系统的示意性剖面图。系统包括可在工艺腔室100中实施的设备。在至少一些实施例中,例如,可配置为用于与所述系统一起使用的pvd工艺腔室可为独立pvd设备的plus和sip pvd系列,两者均可商购自加利福尼亚州圣克拉拉市的应用材料公司。工艺腔室100可被组合在群集工具(例如,)上。例如,群集工具可被配置成执行ald、cvd、外延、蚀刻、光掩模制造、pvd、等离子体掺杂、等离子体氮化和rtp,以及整合的多步骤工艺,诸如高介电常数晶体管栅极堆叠制造。

16.工艺腔室100被配置成在设置在工艺腔室100中的基板104上执行材料的pvd。此外,如上所述,工艺腔室100被配置成执行一个或多个额外的工艺。例如,如将在下文更详细描述的,工艺腔室100可被配置成执行预清洁工艺,用以从基板104去除(例如,蚀刻)一种或多种材料。

17.继续参照图1,工艺腔室100含有基板支撑底座102和溅射源,基板支撑底座102用于在其上接收基板104,溅射源诸如源材料的靶材106(靶材106)。基板支撑底座102可位于接地的封闭腔室壁108内,封闭腔室壁108可为腔室壁(如图所示)或接地屏蔽件。在图1中,接地屏蔽件140被示出为覆盖靶材106上方的工艺腔室100的至少一些部分。在一些实施例中,接地屏蔽件140可在靶材下方延伸以也包围底座102。

18.工艺腔室包括馈送结构110,馈送结构110用于将rf和dc能量耦接至靶材106。例如,如下文所述,馈送结构是用于将rf能量和dc能量耦接至靶材106或耦接至含有靶材的组件的设备。在一些实施例中,馈送结构110可为管状。馈送结构110包括主体112,主体112具有第一端114和与第一端114相对的第二端116。在一些实施例中,主体112进一步包括中央开口115,中央开口115设置为从第一端114至第二端116穿过主体112。

19.馈送结构110的第一端114可耦接至rf功率源118和dc功率源120,所述rf功率源118和dc功率源120可分别用于将rf和dc能量提供至靶材106。例如,如将在下文更详细地描述的,在第一处理状态下,可使用rf功率源118和dc功率源120两者在基板104上执行预清洁工艺,且在第二处理状态下,可使用dc功率源120在基板104上执行pvd工艺。在一些实施例中,dc功率源120可用于将负电压或偏压施加至靶材106。在一些实施例中,由rf功率源118供应的rf能量可在从约2mhz至约60mhz的频率范围内,或者,例如,可使用诸如2mhz、13.56mhz、27.12mhz或60mhz的非限制性频率。在一些实施例中,可提供多个rf功率源(即,两个或更多个rf功率源),以提供多个上述频率的rf能量。可由合适的导电材料制成馈送结构110,以传导来自rf功率源118和dc功率源120的rf和dc能量。dc功率源120可替代地耦接至靶材106,而不经过馈送结构110。

20.可同步使用dc功率源120和rf功率源118,以在工艺腔室100的处理容积148内产生第一处理状态(例如,以用于蚀刻基板104)。例如,第一处理状态可包含等离子体119,所述等离子体119包括气体离子和金属离子两者,且可用于预清洁基板104,以从基板104去除一种或多种材料(例如,原生氧化物)。dc功率源可用于产生第二处理状态(例如,以用于在基板104上执行pvd)。例如,如将在下文更详细描述的,第二处理状态可仅包含金属原子和/或离子,且可用于在基板104上执行pvd,以在基板104上沉积一种或多种金属。

21.此外,可将rf偏压功率源162耦接至基板支撑底座102,以便在基板104上引起负dc偏压。此外,在一些实施例中,可在处理期间在基板104上形成负dc自偏压。例如,由rf偏压功率源162供应的rf功率可在从约2mhz至约60mhz的频率范围内,例如,可使用如2mhz、13.56mhz或60mhz的非限制性频率。在其他应用中,基板支撑底座102可接地或保持电浮动(electrically floating)。例如,电容调谐器164可耦接至基板支撑底座,以用于在可能不想要rf偏压功率的应用中调节基板104上的电压。

22.馈送结构110可具有适合长度,所述适合长度促进相应的rf和dc能量在馈送结构110周边的基本上均匀分布。例如,在一些实施例中,馈送结构110可具有约0.75英寸至约12英寸,或约3.26英寸的长度。

23.在一些实施例中,主体112可具有至少约1:1的长度对内径比。在一些实施例中,主体可具有至少约0.5:1(例如,约0.6:1)的长度对外径比。

24.可在仍允许磁控管轴延伸通过的同时使馈送结构110的内径(即,中央开口115的直径)尽可能小,例如,从约1英寸至约11英寸,或约3.9英寸。在一些实施例中,在不存在磁控管轴的情况下(例如,在不使用磁控管的情况下,或其中磁控管不是经由居中设置在靶材的背侧上方的轴所控制),馈送结构110的内径可小至零英寸(例如,可提供没有中央开口115的主体112)。在此类实施例中,馈送结构110的内径(如果有的话)可为例如,从约0英寸至约11英寸。

25.可在为了机构完整性而维持足够的馈送结构110的壁厚度的同时使馈送结构110的外径尽可能小,例如从约1.5英寸至约12英寸,或约5.8英寸。在一些实施例中,在不存在磁控管轴的情况下,馈送结构110的外径250可小至约0.5英寸。在此类实施例中,馈送结构110的外径可为,例如,从约0.5英寸至约12英寸。

26.提供较小的内径(和较小的外径)有助于在不增加馈送结构110的长度的情况下提高长度对id比(和长度对od比)。尽管上文描述为用于将rf和dc能量两者都耦接至靶材106,但馈送结构110也可用于仅将rf能量耦接至靶材,其中dc能量从不同的位置耦接至靶材。在此类实施例中,尽管dc能量可能不如经由馈送结构110提供的那样均匀,rf能量仍然更均匀地提供至靶材以促进更均匀的等离子体处理。例如,当执行蚀刻工艺以从基板104去除材料时。

27.主体112的第二端116耦接至电源分配板(source distribution plate)122。电源分配板包括被设置成穿过电源分配板122并与主体112的中央开口115对齐的孔洞124。可由合适的导电材料制成电源分配板122,以从馈送结构110传导rf和dc能量。

28.电源分配板122可以经由导电构件125耦接至靶材106。导电构件125可以是具有第一端126的管状构件,第一端126耦接至电源分配板122的面向靶材的表面128邻近电源分配板122的周向边缘。导电构件125进一步包括第二端130,第二端130耦接至靶材106的面向电源分配板的表面132(或耦接至靶材106的背板146)邻近靶材106的周向边缘。

29.空腔134可以由导电构件125的面向内的壁、电源分配板122的面向靶材的表面128和靶材106的面向电源分配板的表面132限定。空腔134经由电源分配板122的孔洞124流体耦接至主体112的中央开口115。如图1所示并且下文进一步描述的,可利用空腔134和主体112的中央开口115来至少部分地容纳可旋转磁控管组件136的一个或多个部分。在一些实施例中,可以用冷却流体(诸如水(h2o)等)来至少部分地填充空腔。

30.可以设置接地屏蔽件140来覆盖工艺腔室100的盖的外侧表面。接地屏蔽件140可例如经由腔室主体的接地连接耦接到接地。接地屏蔽件140具有中央开口,以允许馈送结构110通过接地屏蔽件140而耦接至电源分配板122。接地屏蔽件140可包含任何合适的导电材料,诸如铝、铜等等。在接地屏蔽件140与电源分配板122、导电构件125和靶材106(和/或背板146)的外表面之间提供绝缘间隙139,以防止rf和dc能量被直接导引到接地。可用空气或一些其他合适的介电材料(诸如陶瓷、塑料等等)填充绝缘间隙。

31.在一些实施例中,接地套环(ground collar)141可围绕主体112和馈送结构110的下部设置。接地套环141耦接至接地屏蔽件140且可为接地屏蔽件140的一体部件,或可为耦接至接地屏蔽件的独立部件,以提供馈送结构110的接地。接地套环141可由合适的导电材

料(诸如铝或铜)制成。在一些实施例中,可将设置在接地套环141的内径与馈送结构110的主体112的外径之间的间隙保持在最小,并恰好足以提供电气隔离。间隙可填充有诸如塑料或陶瓷等隔离材料或可为气隙。接地套环141防止rf馈送与主体112之间的串扰,从而改善等离子体和处理的均匀性。

32.可将绝缘体板(isolator plate)138设置在电源分配板122与接地屏蔽件140之间,以防止rf和dc能量被直接导引到接地。绝缘体板138具有中央开口,以允许馈送结构110通过绝缘体板138而耦接至电源分配板122。绝缘体板138可包含合适的介电材料,诸如陶瓷、塑料等等。替代地,可提供气隙来取代绝缘体板138。在提供气隙取代绝缘体板的实施例中,接地屏蔽件140在结构上足够可靠,以支撑安置在接地屏蔽件140上的任何部件。

33.返回图1,可通过介电绝缘体144使靶材106被支撑在接地的导电铝适配器142上。大体而言,靶材106可为通常在经由pvd的薄膜制造中使用的任何材料,诸如金属或金属氧化物。例如,在一些实施例中,靶材106可为适于在基板104上沉积ti或ti氮化物(tin)、钨(w)、铜(cu)等等的金属,诸如钛(ti)等等。根据本文提供的教示,也可适当地使用其他材料。

34.靶材106大体上是细长的,并且可以是,例如,圆柱形或矩形。靶材106的尺寸可根据基板104的尺寸和/或工艺腔室100的配置而变化。例如,为了处理300mm直径的半导体晶片,靶材106的宽度或直径可介于约100mm至约200mm之间,且可具有约400mm至约600mm的长度。靶材106可为静止的或可移动的,包括可沿着靶材106的延长轴旋转。

35.在一些实施例中,背板146可耦接至靶材106的面向电源分配板的表面132。背板146可包含导电材料,诸如铜-锌、铜-铬、或与靶材相同的材料,使得rf和dc功率可经由背板146耦接至靶材106。替代地,背板146可不导电且可包括诸如电馈通件等导电构件(未示出),以用于将靶材106的面向电源分配板的表面132耦接至导电构件125的第二端130。可包括背板146以,例如,改善靶材106的结构稳定性。

36.基板支撑底座102具有面向靶材106的主表面的材料接收表面,并且在与靶材106的主表面相对的平面位置中支撑待溅射涂布的基板104。基板支撑底座102可在工艺腔室100的处理容积148中支撑基板104。处理容积148被定义为处理期间在基板支撑底座102上方的区域(例如,介于靶材106与处于处理位置的基板支撑底座102之间)。

37.在一些实施例中,可垂直地移动基板支撑底座102通过连接到底部腔室壁152的伸缩囊150,以允许经由工艺腔室100的下部中的装载锁定阀(未示出)将基板104传送到基板支撑底座102上,然后将基板104升高至沉积或处理位置,诸如预清洁处理位置。

38.可从气体源154通过质流控制器156将一种或多种工艺气体供应至工艺腔室100的下部。工艺气体可为任何合适的工艺气体,诸如惰性气体(例如,氩)或氮(n2),用以在从靶材106溅射材料107时在处理容积148内形成等离子体。如将在下文更详细地描述的,工艺气体也可用于在基板104上执行预清洁工艺。排放口158可被提供并经由阀门160耦接至泵(未示出),用以从工艺腔室100的内部排放或除气用过的工艺气体和/或有助于在工艺腔室100内部维持期望的压力。

39.可旋转磁控管组件136可定位在邻近靶材106的后表面(例如,面向电源分配板的表面132)。可旋转磁控管组件136包括由底板168支撑的多个磁铁166。底板168连接到旋转轴170,旋转轴170与工艺腔室100和基板104的中心轴重合。可将电机172耦接到旋转轴170

的上端,以驱动可旋转磁控管组件136的旋转。磁铁166在工艺腔室100内产生磁场,所述磁场通常平行于且靠近靶材106的表面,以捕获电子并增加局部等离子体密度,这进而(例如,在pvd期间)增加溅射速率。磁铁166在工艺腔室100的顶部周围产生电磁场,并旋转磁铁166以旋转电磁场,所述电磁场影响工艺的等离子体密度以更均匀地溅射靶材106。例如,旋转轴杆170每分钟可旋转约0至约150转。

40.在一些实施例中,工艺腔室100可进一步包括接地的底部屏蔽件174,底部屏蔽件174连接至适配器142的突出部176。暗空间屏蔽件(dark space shield)178可被支撑在底部屏蔽件174上,且可通过螺钉或其他合适的方式紧固至底部屏蔽件174。底部屏蔽件174与暗空间屏蔽件178之间的金属螺纹连接允许底部屏蔽件174和暗空间屏蔽件178接地至适配器142。适配器142进而被密封并接地至腔室壁108。底部屏蔽件174和暗空间屏蔽件178两者通常由硬的非磁性不锈钢制成。

41.底部屏蔽件174向下延伸并可包括大体上管状部分180,所述大体上管状部分180具有大体上恒定的直径。底部屏蔽件174沿着适配器142的壁和腔室壁108往下延伸至基板支撑底座302的顶表面下方,并往上返回直到到达基板支撑底座102的顶表面为止(例如,从而在底部形成u形部分184)。当基板支撑底座102位于盖环186的较低的装载位置时,盖环186安置在底部屏蔽件174的往上延伸的内侧部分188的顶端上,但当盖环186位于盖环186的较高的沉积位置时,盖环186安置在基板支撑底座102的外周边上,以保护基板支撑底座102免受溅射沉积。可使用额外的沉积环(未示出)来屏蔽基板104的周边免受沉积。

42.在一些实施例中,可在工艺腔室100周围设置磁铁190,以用于选择性地在基板支撑底座102与靶材106间提供磁场。例如,如图1所示,当位于处理位置时,可将磁铁190在基板支撑底座102正上方的区域中设置在腔室壁108外部周围。在一些实施例中,可附加地或替代地将磁铁190设置在其他位置,诸如毗邻适配器142。磁铁190可以是电磁铁,并且可耦接至功率源(未示出)以控制所述电磁铁所产生的磁场强度。

43.包括处理器123的控制器121被配置(或编程)成控制工艺腔室100的整体操作。例如,在处理器123的控制下,控制器121可接收输入到处理器123的存储器127内的配方。例如,存储器127可为具有指令的非瞬时计算机可读存储介质,所述指令在由处理器123(或控制器121)执行时,执行本文描述的方法。配方可包括与用于处理基板104的前述部件中的一者或多者相关联的一个或多个参数有关的信息。例如,控制器121可使用配方中的信息来控制rf功率源18和dc功率源120,用以控制操作期间所使用的电量;用以调节rf功率源18和dc功率源120,例如,以选择rf功率源18和dc功率源120中的一者或两者以产生惰性气体离子、金属离子和/或气体离子和金属离子的组合;用以控制基板支撑底座102的高度(诸如当基板104被装载至工艺腔室100中时,或被处理时);控制气体源154以用于控制将被供应至工艺腔室100中的工艺气体的量;控制多个磁铁166以用于控制磁铁的位置或多个磁铁166旋转的速度等。

44.图2为用于处理基板的方法200的流程图,且图3a至图3c为根据本公开内容的至少一些实施例的示出使用图2的方法200处理的基板的多个阶段的示意图。

45.最初,基板(例如,基板104)可使用一个或多个工艺腔室(例如,cvd腔室、ald腔室等等)形成,并且可由用于形成本文所述的基板的任何合适材料制成,所述材料包括但不限于硅或锗。例如,在至少一些实施例中,基板可为具有由硅制成的基底层302的基板300(图

3a)。基底层302的顶部上可沉积有一个或多个额外的材料层,包括但不限于,氧化物(诸如热氧化物)、一种或多种类型的金属、一种或多种类型的聚合物等等。例如,在至少一些实施例中,基底层302可具有沉积于其上的热氧化物层304;至少部分地覆盖热氧化物层304的传导层,诸如金属层,例如,铝层306(例如,第二材料层);以及至少部分地覆盖热氧化物层304和铝层306的聚合物层308(例如,第三材料层),因而形成暴露出铝层306的至少一部分的沟槽(或通孔)310(例如,参见图3a)。在至少一些实施例中,热氧化物可为氧化硅(sio2)(或其他合适的热氧化物),并且聚合物可包括但不限于,聚酰亚胺(pi)、聚苯并恶唑(pbo)等等。此外,热氧化物层304可具有约至约的厚度。

46.在形成图3a的基板300后,可能需要在基板300上执行一个或多个附加工艺。为了说明的目的,假设附加工艺是pvd,以用于在基板300上沉积一个或多个附加金属层。然而,如上文所述,当将基板从一个工艺腔室转移至另一个工艺腔室时,在基板上的金属接触垫(例如,铝层306)上有时可形成原生氧化物(例如,第一材料层,诸如金属氧化物层)。因此,为了说明的目的,将氧化铝层312示出于铝层306的顶部(图3a)。

47.可以以上文描述的适当方式将基板300(例如,通过装载锁定、狭缝阀等等)装载到工艺腔室中。一旦经装载,在至少一些实施例中,控制器(例如,控制器121)可选择dc功率源120和rf功率源118中的一者或两者来产生一种或多种工艺状态,以执行一个或多个对应工艺(在202处)。例如,在202处,控制器可产生第一工艺状态,所述第一工艺状态可用于在基板上执行预清洁工艺(例如,选择性地蚀刻)。

48.例如,发明人已发现到,可通过选择dc功率源120和rf功率源118两者来产生第一工艺状态,并根据工艺腔室的内部容积内提供的靶材和工艺气体而可在工艺腔室内产生等离子体(例如,等离子体119),所述等离子体包括一种或多种靶材离子(例如,靶材106离子)和气体离子。包括一种或多种靶材离子和气体离子的等离子体可用于执行预清洁工艺,以从基板去除(例如,选择性地蚀刻)原生氧化物(例如,从基板300去除诸如氧化铝层312之类的金属氧化物),和/或在基板上的一个或多个层(例如,聚合物层308)的顶部沉积靶材材料的薄膜层。

49.因此,在至少一些实施例中,靶材可包括金属(例如,钛、钨、铜等等)且工艺气体可包括惰性气体(例如,氩、氮或其他惰性气体,诸如一种或多种惰性气体)。因此,当控制器选择dc功率源120和rf功率源118两者时,产生包含等离子体(由图3b中的箭头314所描绘)的第一处理状态,所述等离子体包括金属离子和惰性气体离子两者,以执行预清洁工艺来去除(例如,选择性地蚀刻)原生氧化物和/或沉积金属薄膜层。

50.例如,在基板300的蚀刻期间,在202处,金属离子和惰性气体离子轰击基板300,以从第二材料层(例如,铝层306)去除第一层或材料(例如,原生氧化物)。此外,在202处蚀刻基板300期间(或在蚀刻后在204处),还将金属薄膜层316沉积于第三材料层(例如,聚合物层308)的顶部上。聚合物层308顶部的金属薄膜层316可在用来从工艺腔室的内部容积去除用过的工艺气体的脱气或除气程序期间保护聚合物层308。控制器还可被配置成调节一个或多个参数(例如,从rf功率源118和dc功率源120供应的电量、压力、温度、磁铁旋转、气流、偏压等等),以控制沉积于聚合物层308的顶部上的金属薄层316的厚度,和/或在工艺腔室的内部容积内产生的金属离子和/或惰性气体离子的量。

51.另外,在204处(例如,在完成蚀刻工艺之后),控制器可在基板上沉积一种或多种

材料。例如,控制器可仅选择dc功率源120来产生第二处理状态,所述第二处理状态仅包含金属离子(由图3c中的箭头318所描绘),以执行pvd以在经蚀刻的铝层306的顶部上沉积金属层320,和/或在聚合物层308的顶部上沉积附加的金属层。在至少一些实施例中,用于执行蚀刻工艺的金属可与用于执行pvd的金属相同或相异。在一些实施例中,也可在基板的pvd期间使用一种或多种工艺气体。再次,控制器还可被配置成调节一个或多个参数(例如,从rf功率源118和dc功率源120供应的电量、压力、温度、磁铁旋转、气流、偏压等等),以控制沉积在铝层306的顶部上(和/或沉积在聚合物层308的顶部上)的金属薄层320的厚度,和/或在工艺腔室的内部容积内产生的金属离子的量。

52.虽然前述内容针对本公开内容的实施例,但可在不脱离本公开内容基本范围的情况下设计出本公开内容的其他和进一步实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1