半导体装置及其制造方法与流程

1.本发明涉及半导体装置及其制造方法。

背景技术:

2.以往,作为存储装置,已知有dram(dynamic random access memory,动态随机存取存储器)等易失性存储器(ram)。对于dram要求大容量化,以能够承受运算装置(以下称为逻辑芯片)的高性能化和数据量的增大。因此,通过存储器(存储单元阵列、存储芯片)的微细化以及单元的平面增设来实现大容量化。另一方面,由于微细化导致对噪声的脆弱性、管芯(die)面积的增加等,这种大容量化达到了极限。

3.因此,最近开发了层叠多个平面式存储器来进行三维化(3d化)从而实现大容量化的技术。而且,曾提出了将层叠的多个模块电连接的半导体模块(例如,参照专利文献1和2)。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2016-46447号公报;

7.专利文献2:日本特开2012-227328号公报。

技术实现要素:

8.发明要解决的问题

9.在专利文献1的半导体模块的形成方法中,形成从最上层的电极贯穿到最下层的电极表面的通孔。在专利文献1中,在通过蚀刻形成通孔时,使最上层和中间层的电极作为硬掩模发挥功能。因此,越是上层的电极,暴露于蚀刻的时间越长。由此,上层的电极受到损伤而变薄。特别地,存在当层叠片数变多时电极的损伤变大的问题。此外,层叠片数越多,最上层的开口直径越大。因此,贯穿电极区域的面积增加。

10.此外,专利文献2所公开的半导体模块是在支承衬底上层叠三片模块而构成的。贯穿电极是按邻接的两片模块来配置的。通过多个贯穿电极将模块彼此电连接,从而将三张模块的布线层彼此连接。在多个贯穿电极的形成工序中,多个贯穿电极分别依次排他地形成。因此,贯穿电极的形成工序变长,制造成本增加。此外,在专利文献2中,使用在不同的层具有不同的开口的贯穿电极,因此层叠片数越多,开口部位越多,贯穿电极区域的面积越增加。

11.本发明的目的在于,提供一种能够抑制贯穿电极区域的面积的增加的半导体装置及其制造方法。

12.用于解决问题的方案

13.本发明涉及一种半导体装置,其层叠有多个电路模块,所述电路模块具有电路层和衬底主体,所述半导体装置具有:基准单元,其以使所述电路层邻接的方式层叠有至少两个所述电路模块;附加单元,其以使所述电路层邻接的方式层叠有其他的至少两个所述电

路模块,所述附加单元层叠在所述基准单元;以及过孔,其跨越所述基准单元和所述附加单元来配置,且在层叠方向上延伸,所述过孔具有:基准过孔,其配置在所述基准单元;以及附加过孔,其配置在所述附加单元,所述附加过孔在与所述基准过孔接触的位置具有比所述基准过孔的直径小的直径。

14.此外,优选地,所述附加过孔具有:附加过孔主体,其在层叠方向上贯穿所述附加单元;以及附加侧阻挡金属,其与所述附加过孔主体的外周面接触,并且与所述基准过孔接触。

15.此外,优选地,所述基准过孔从所述基准单元的与所述附加单元层叠的一侧的面起沿着层叠方向缩径并延伸。

16.此外,优选地,所述基准过孔的顶端部延伸至与所述附加单元所接触的另一个所述电路模块不同的所述电路模块的所述电路层。

17.此外,优选地,所述附加单元相对于所述基准单元层叠有多个。

18.此外,优选地,各所述电路模块的所述衬底主体具有围绕所述基准过孔或所述附加过孔并且沿着层叠方向延伸的电介质膜。

19.此外,本发明涉及一种半导体装置的制造方法,所述半导体装置层叠有多个电路模块,所述电路模块具有电路层和衬底主体,所述半导体装置的制造方法包括:基准单元形成工序,通过以使所述电路层邻接的方式层叠至少两个所述电路模块,从而形成基准单元;基准过孔形成工序,在所述基准单元的内部形成基准过孔,所述基准过孔在所述基准单元的层叠方向上延伸;附加单元形成工序,通过以将其他的至少两个所述电路模块的所述电路层邻接的方式进行层叠,从而形成附加单元;层叠工序,在所述基准单元层叠所述附加单元;以及附加过孔形成工序,形成贯穿所述附加单元并与所述基准过孔接触的附加过孔,所述附加过孔在所述附加单元的层叠方向上延伸。

20.此外,优选地,半导体装置的制造方法还包括:第一电介质膜形成工序,在基准单元形成工序时,在所述基准单元的所述电路模块的所述衬底主体形成电介质膜,所述电介质膜形成在如下位置,该位置围绕形成所述基准过孔的位置;以及第二电介质膜形成工序,在附加单元形成工序时,在所述附加单元的所述电路模块的所述衬底主体形成所述电介质膜,所述电介质膜形成在如下位置,该位置围绕形成所述附加过孔的位置。

21.发明效果

22.根据本发明,能够提供一种能够抑制贯穿电极区域的面积的增加的半导体装置及其制造方法。

附图说明

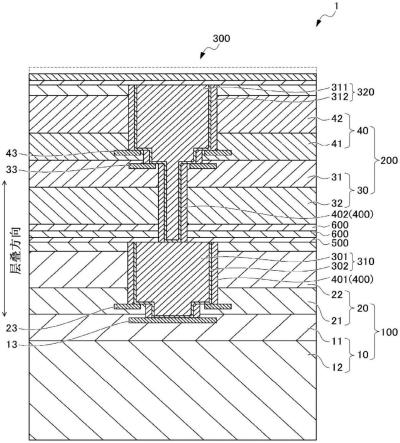

23.图1是表示本发明的第一实施方式的半导体装置的剖视图。

24.图2是表示第一实施方式的半导体装置的制造过程的剖视图。

25.图3是表示第一实施方式的半导体装置的制造过程的剖视图。

26.图4是表示第一实施方式的半导体装置的制造过程的剖视图。

27.图5是表示第一实施方式的半导体装置的制造过程的剖视图。

28.图6是表示第一实施方式的半导体装置的制造过程的剖视图。

29.图7是表示第一实施方式的半导体装置的制造过程的剖视图。

30.图8是表示第一实施方式的半导体装置的制造过程的剖视图。

31.图9是表示第一实施方式的半导体装置的制造过程的剖视图。

32.图10是表示第一实施方式的半导体装置的制造过程的剖视图。

33.图11是表示本发明的第二实施方式的半导体装置的剖视图。

34.图12是表示第二实施方式的半导体装置的制造过程的剖视图。

35.图13是表示第二实施方式的半导体装置的制造过程的剖视图。

36.图14是表示第二实施方式的半导体装置的制造过程的剖视图。

37.图15是表示第二实施方式的半导体装置的制造过程的剖视图。

38.图16是表示第二实施方式的半导体装置的制造过程的剖视图。

具体实施方式

39.以下,参照图1至图16,对本发明的各实施方式的半导体装置1及其制造方法进行说明。

40.各实施方式的半导体装置1例如是存储器模块,其构成为将多个电路模块10、20、30、40(ram)层叠在接口模块(例如,active interposer(aip):有源中介层)上。接口模块也是电路模块的一例。不使用接口模块的结构也是存储器模块的一例。此外,在各实施方式的半导体装置1中,多个电路模块10、20、30、40通过贯穿电极(过孔(via))进行电连接。此外,电路模块10、20、30、40具有电路层11、21、31、41和衬底主体12、22、32、42。

41.电路层11、21、31、41例如是二氧化硅(sio2)层。电路层11、21、31、41在内部具有电极。电路层11、21、31、41具有例如与贯穿电极接触的电极13、23、33、43。

42.电极13、23、33、43例如是在与电路层11、21、31、41的层叠方向交叉的方向上延伸的板状体。电极13、23、33、43配合贯穿电极的位置来配置。具体而言,电极13、23、33、43配置在与贯穿电极的外周面接触的位置。在以下的实施方式中,配置在层叠方向一端的电极13、23、33、43例如构成为没有通孔的板状体。此外,配置在层叠方向一端以外的电极13、23、33、43构成为例如具有规定的大小的通孔的板状体。特别地,在以下的实施方式中,配置在邻接的电路层11、21、31、41的电极13、23、33、43之中的配置在层叠方向一端侧的电极13、23、33、43具有直径比配置在另一端侧的电极13、23、33、43小的通孔。

43.衬底主体12、22、32、42例如是硅(si)层。衬底主体12、22、32、42与电路层11、21、31、41的一面侧邻接地配置。在以下的实施方式中,层叠方向一端的电路模块10、20、30、40的衬底主体12、22、32、42构成为比其他的电路模块10、20、30、40的衬底主体厚。

44.以下的各实施方式的半导体装置1是通过将贯穿电极的直径设为规定值以下就能够削减贯穿电极在电路模块10、20、30、40的表面中占有的面积的半导体装置。具体而言,半导体装置1是通过在层叠方向上配置剖面为凸状的多个贯穿电极从而使贯穿电极的直径为规定值以下的半导体装置。

45.[第一实施方式]

[0046]

接下来,参照图1至图10,对本发明的第一实施方式的半导体模块及其制造方法进行说明。

[0047]

本实施方式的半导体装置1具有层叠有多个电路模块10、20、30、40的结构,所述电路模块10、20、30、40具有电路层11、21、31、41和衬底主体12、22、32、42。半导体装置1具有例

如层叠有四个电路模块10、20、30、40的结构。半导体装置1具有基准单元100、附加单元200、过孔300、以及绝缘膜400。另外,在图1中,将从附加单元200朝向基准单元100的方向作为层叠方向的一端侧进行说明。此外,将相反侧作为另一端侧进行说明。

[0048]

基准单元100具有以使电路层11、21邻接的方式层叠有多个电路模块10、20的结构。在本实施方式中,基准单元100例如具有将两个电路模块10、20的电路层11、21以使电极13、23的位置相匹配的方式进行接合的结构。此外,基准单元100构成为层叠方向一端侧的电路模块10的电极13的外径比另一个电路模块20的电极23的通孔大。更详细地说,基准单元100配置成在层叠方向上在层叠方向一端侧的电路模块10的电极13的外周部重叠另一个电路模块20的电极23。此外,基准单元100构成为层叠方向一端侧的电路模块10的衬底主体12比另一个电路模块20的衬底主体22厚。

[0049]

附加单元200是以使电路层31、41邻接的方式层叠有其他的两个电路模块30、40的附加单元200,其层叠在基准单元100上。附加单元200例如与基准单元100同样地具有将两个电路模块30、40的电路层31、41以使电极33、43的位置相匹配的方式进行接合的结构。附加单元200层叠在基准单元100的层叠方向另一端侧的电路模块20上。此外,附加单元200构成为层叠方向一端侧的电路模块30的电极33的外径比另一个电路模块40的电极43的通孔大。更详细地说,附加单元200配置成在层叠方向上在层叠方向一端侧的电路模块30的电极33的外周部重叠另一个电路模块40的电极43。此外,附加单元200在层叠方向一端侧的电路模块30的电极33中具有比另一个电路模块40的电极43的通孔小的通孔。

[0050]

过孔300跨越基准单元100和附加单元200而配置,在层叠方向延伸。在本实施方式中,过孔300构成为沿着层叠方向大径部分和小径部分交替地重复。过孔300具有基准过孔310和附加过孔320。

[0051]

基准过孔310配置在基准单元100。基准过孔310例如沿着层叠方向从层叠方向另一端侧的电路模块20的端面延伸至与一端侧的电路模块10的电极13接触的位置。基准过孔310从基准单元100的与附加单元200层叠的一侧的面起沿着层叠方向缩径并延伸。基准过孔310的顶端部延伸至与附加单元200所接触的另一个电路模块20不同的电路模块10的电极13。基准过孔310具有基准过孔主体301和基准阻挡金属302。

[0052]

基准过孔主体301例如由铜(cu)构成。在本实施方式中,基准过孔主体301构成为朝向层叠方向一端剖面为凸状。基准过孔主体301在大径部与层叠方向另一端侧的电路模块20的电极23的另一端侧表面相向。此外,基准过孔主体301以大径部贯穿层叠方向另一端侧的电路模块20的电极23。而且,基准过孔主体301在小径部与层叠方向一端侧的电路模块10的电极13的另一端侧表面相向。

[0053]

基准阻挡金属302例如由氮化钽(tan)、钽(ta)或它们的层叠膜构成。基准阻挡金属302配置在基准过孔主体301与基准单元100之间。基准阻挡金属302与基准过孔主体301的外周面中的层叠方向另一端侧的面以外的面接触地配置。

[0054]

附加过孔320配置在附加单元200。附加过孔320例如沿着层叠方向从层叠方向另一端侧的电路模块40的端面贯穿至一端侧的电路模块30的端面。此外,附加过孔320在层叠方向一端处与基准过孔310的另一端接触。附加过孔320在与基准过孔310的接触位置具有比基准过孔310的直径小的直径。附加过孔320具有附加过孔主体311和附加侧阻挡金属312。

[0055]

附加过孔主体311例如由铜(cu)构成。附加过孔主体311在层叠方向上贯穿附加单元200。在本实施方式中,附加过孔主体311构成为朝向层叠方向一端剖面为凸状。附加过孔主体311在大径部与层叠方向另一端侧的电路模块40的电极43的另一端侧表面相向。此外,附加过孔主体311以第一小径部贯穿层叠方向另一端侧的电路模块40的电极43。此外,附加过孔主体311在第一小径部与层叠方向一端侧的电路模块30的电极33的另一端侧表面相向。此外,附加过孔主体311以与第一小径部相比进行了缩径的第二小径部贯穿层叠方向一端侧的电路模块30的电极33。

[0056]

附加侧阻挡金属312例如由氮化钽(tan)、钽(ta)或它们的层叠膜构成。附加侧阻挡金属312与附加过孔主体311的外周面接触,并且与基准过孔310接触。附加侧阻挡金属312例如配置在附加过孔主体311与附加单元200之间。附加侧阻挡金属312与附加过孔主体311的外周面中的层叠方向另一端侧的面以外的面接触地配置。即,附加侧阻挡金属312被夹在基准过孔主体301与附加过孔主体311之间来配置。

[0057]

绝缘膜400配置在基准过孔310与基准单元100之间。此外,绝缘膜400配置在附加过孔320与附加单元200之间。绝缘膜400具有基准侧绝缘膜401和附加侧绝缘膜402。

[0058]

基准侧绝缘膜401例如由二氧化硅(sio2)构成。基准侧绝缘膜401与基准阻挡金属302中的与层叠方向交叉的方向的面接触地配置。

[0059]

附加侧绝缘膜402例如由二氧化硅(sio2)构成。附加侧绝缘膜402与附加侧阻挡金属312中的与层叠方向交叉的方向的面接触地配置。

[0060]

接下来,参照图2至图10,对第一实施方式的半导体装置1的制造方法进行说明。

[0061]

半导体装置1的制造方法包括:基准单元形成工序、基准过孔形成工序、附加单元形成工序、层叠工序、以及附加过孔形成工序。

[0062]

在基准单元形成工序中,如图2所示,通过以使电路层11、21邻接的方式层叠两个电路模块10、20,从而形成基准单元100。在基准单元形成工序中,层叠方向另一端侧的电路模块20的衬底主体22在层叠之后被研磨,在被研磨的表面配置保护膜900。保护膜900例如由二氧化硅(sio2)构成。

[0063]

接下来,执行基准过孔形成工序。在基准过孔形成工序中,在基准单元100的内部形成基准过孔310,所述基准导通孔310在基准单元100的层叠方向延伸。在基准过孔形成工序中,首先,如图3所示,通过使用抗蚀剂r实施各向异性蚀刻,从而与层叠方向另一端侧的电路模块20的电极23的位置一致地形成导通孔。接下来,在基准过孔形成工序中,如图4所示,与层叠方向另一端侧的电路模块20的电极23的通孔的位置一致地形成导通孔。接下来,在基准过孔形成工序中,如图5所示,在导通孔的位置形成基准侧绝缘膜401、基准阻挡金属302、以及基准过孔主体301。

[0064]

接下来,执行附加单元形成工序。在附加单元形成工序中,通过以将其他的两个电路模块30、40的电路层31、41邻接的方式进行层叠,从而形成附加单元200。在附加单元形成工序中,层叠于基准单元100的一侧的电路模块30的衬底主体32在层叠方向上被研磨,在被研磨的表面形成用于粘接的交联层600。

[0065]

接下来,执行层叠工序。在层叠工序中,在基准单元100上层叠附加单元200。在层叠工序中,如图6所示,与基准单元100的各电极13、23的位置相配合地层叠附加单元200。此外,在层叠工序中,在附加单元200相对于基准单元100进行层叠之后,附加单元200的层叠

方向另一端侧的衬底主体42在层叠方向被研磨,在被研磨的表面配置保护膜900。另外,在本实施方式中,在层叠工序中,在层叠前在基准单元100的与附加单元200相向的面形成蚀刻停止层500和用于粘接的交联层600。

[0066]

接下来,执行附加过孔形成工序。在附加过孔形成工序中,形成贯穿附加单元200并与基准过孔310接触的附加过孔320,附加过孔320在附加单元200的层叠方向上延伸。在附加过孔形成工序中,首先,如图7所示,与层叠方向另一端侧的电路模块40的电极43的位置一致地形成导通孔。接下来,在附加过孔形成工序中,如图8所示,与层叠方向另一端侧的电路模块40的电极43的通孔的位置一致地形成导通孔。接下来,在附加过孔形成工序中,如图9所示,与层叠方向一端侧的电路模块30的电极33的通孔的位置一致地形成导通孔。接下来,在附加过孔形成工序中,如图10所示,在导通孔的位置形成附加侧绝缘膜402、附加侧阻挡金属312、以及附加过孔主体311。

[0067]

根据如以上这样的第一实施方式的半导体装置1,获得以下的效果。

[0068]

(1)一种半导体装置1,其层叠有多个电路模块10、20、30、40,所述电路模块10、20、30、40具有电路层11、21、31、41和衬底主体12、22、32、42,所述半导体装置具有:基准单元100,其以使电路层11、21邻接的方式层叠有至少两个电路模块10、20;附加单元200,其以使电路层31、41邻接的方式层叠有其他的至少两个电路模块30、40,所述附加单元200层叠在基准单元100;以及过孔300,其跨越基准单元100和附加单元200来配置,且在层叠方向上延伸,过孔300具有:基准过孔310,其配置在基准单元100;和附加过孔320,其配置在附加单元200,附加过孔320在与基准过孔310接触的位置具有比基准过孔310的直径小的直径。由此,能够抑制层叠方向另一端侧(层叠方向中的附加单元200的一侧)的附加过孔320的直径相对于基准过孔310进行扩径的情况。因此,在与层叠方向交叉的方向上,能够抑制附加过孔320的区域相对于附加单元200的电路模块10、20、30、40的面积变大。

[0069]

(2)附加过孔320具有:附加过孔主体311,其在层叠方向上贯穿附加单元200;和附加过孔320侧阻挡金属,其与附加过孔主体311的外周面接触,并且与基准过孔310接触。由此,能够改善基准过孔310和附加过孔320的电接触,能够形成良好的过孔。

[0070]

(3)基准过孔310从基准单元100的与附加单元200层叠的一侧的面起沿着层叠方向缩径并延伸。由此,能够容易地使基准过孔310与构成基准单元100的电路模块10、20的电极13、23接触。

[0071]

(4)基准过孔310的顶端部延伸至与附加单元200所接触的另一个电路模块20不同的电路模块10的电路层11。由此,不需要使基准过孔310贯穿基准单元100,因此能够容易地构成基准过孔310。

[0072]

(5)一种半导体装置1的制造方法,所述半导体装置1层叠有多个电路模块10、20、30、40,所述电路模块10、20、30、40具有电路层11、21、31、41和衬底主体12、22、32、42,该半导体装置1的制造方法包括:基准单元形成工序,通过以使电路层11、21邻接的方式层叠两个电路模块10、20,从而形成基准单元100;基准过孔形成工序,在基准单元100的内部形成有基准过孔310,基准过孔310在基准单元100的层叠方向上延伸;附加单元形成工序,通过以将其他的两个电路模块30、40的电路层31、41邻接的方式进行层叠,从而形成附加单元200;层叠工序,在基准单元100层叠附加单元200;以及附加过孔形成工序,形成贯穿附加单元200并与基准过孔310接触的附加过孔320,该附加过孔320在附加单元200的层叠方向上

延伸。由此,能够容易地构成半导体装置1。此外,能够抑制电路模块30、40中的附加过孔320的区域变大。

[0073]

[第二实施方式]

[0074]

接下来,参照图11至图16,对本发明的第二实施方式的半导体装置1及其制造方法进行说明。在第二实施方式中,对同一结构标注同一标记,简化或省略说明。

[0075]

如图11所示,第二实施方式的半导体装置1与第一实施方式的不同之处在于,基准过孔310和附加过孔320为锥形。此外,第二实施方式的半导体装置1与第一实施方式的不同之处在于,各电路模块20、30、40、50、60的衬底主体22、32、42、52、62具有围绕基准过孔310或附加过孔320并且沿着层叠方向延伸的电介质膜800。另外,在第二实施方式中,基准过孔310和附加过孔320贯穿在电路层11、21、31、41、51、61配置的贯穿孔701、触点702、栅电极703、以及金属布线704之中的没有通孔的金属布线704,并与层叠方向一端侧的电路层11的金属布线704的层叠方向另一端侧的面接触。此时,配置成通过基准过孔310和附加过孔320的侧面在贯穿金属布线704的部位与金属布线704电连接,从而将金属布线704彼此电连接。此外,在第二实施方式中,基准过孔310跨越四个电路模块10、20、30、40来配置。此外,在第二实施方式中,附加过孔320跨越两个电路模块50、60来配置。在第二实施方式中,基准单元100由四个电路模块10、20、30、40构成。此外,在第二实施方式中,附加单元200由两个电路模块50、60构成。此外,在第二实施方式中,基准过孔310和附加过孔320分别配置有两个,但不限于此。

[0076]

电介质膜800例如由二氧化硅(sio2)构成。电介质膜800在层叠方向上贯穿衬底主体22、32、42、52、62直至配置在衬底主体22、32、42、52、62的场氧化膜700。

[0077]

接下来,参照图11至图16,对第二实施方式的半导体装置1的制造方法进行说明。

[0078]

第二实施方式的半导体装置1的制造方法与第一实施方式的不同之处在于,还包括第一电介质膜形成工序,在基准单元形成工序时,在基准单元100的电路模块20、30、40的衬底主体22、32、42形成电介质膜800,所述电介质膜800形成在如下位置,该位置围绕形成基准过孔310的位置。此外,第二实施方式的半导体装置1的制造方法与第一实施方式的不同之处在于,还包括第二电介质膜形成工序,在附加单元形成工序时,在附加单元200的电路模块50、60的衬底主体52、62形成电介质膜800,所述电介质膜800形成在如下位置,该位置围绕形成附加过孔320的位置。此外,第二实施方式的半导体装置1的制造方法与第一实施方式的不同之处在于,在层叠工序中,在层叠方向上使电介质膜800的位置一致地层叠基准单元100和附加单元200。

[0079]

首先,如图12所示,层叠两个电路模块10、20。接下来,如图13所示,执行第一电介质膜形成工序。在第一电介质膜形成工序中,在衬底主体22中的如下位置形成电介质膜800,该位置围绕形成基准过孔310的位置。接下来,如图14所示,针对图13所示那样层叠了的两个电路模块10、20准备另一组(电路模块30、40)。在层叠方向上使电介质膜800的位置一致地层叠两个电路模块10、20与其他的两个电路模块30、40。接下来,如图15所示,执行基准过孔形成工序,并执行基准单元形成工序。接下来,如图16所示,执行附加单元形成工序、和形成电介质膜800的第二电介质膜形成工序、以及层叠工序。然后,如图11所示,执行附加过孔形成工序。

[0080]

根据如以上这样的第二实施方式的半导体装置1及其制造方法,获得以下的效果。

[0081]

(8)各电路模块20、30、40、50、60的衬底主体22、32、42、52、62具有围绕基准过孔310或附加过孔320并且沿着层叠方向延伸的电介质膜800。由此,能够抑制基准过孔310或附加过孔320与衬底主体22、32、42、52、62电连接。此外,仅在衬底主体22、32、42、52、62形成电介质膜800。因此,能够仅在衬底主体22、32、42、52、62形成花费加工时间的电介质膜800,能够通过缩短工艺时间来削减成本。

[0082]

(9)半导体装置1的制造方法还包括:第一电介质膜形成工序,在基准单元形成工序时,在基准单元100的电路模块20、30、40的衬底主体22、32、42形成电介质膜800,所述电介质膜800形成在如下位置,该位置围绕形成基准过孔310的位置;和第二电介质膜形成工序,在附加单元形成工序时,在附加单元200的电路模块50、60的衬底主体52、62形成电介质膜800,所述电介质膜800形成在如下位置,该位置围绕形成附加过孔320的位置。由此,能够不与衬底主体22、32、42、52、62电连接,通过贯穿金属布线704来一次分别形成基准过孔310和附加过孔320。因此,能够削减形成基准过孔310和附加过孔320的成本。

[0083]

以上,对本发明的半导体装置1及其制造方法的优选的各实施方式进行了说明,但本发明不限于上述实施方式,能够酌情地变更。

[0084]

例如,在上述实施方式中,附加单元200可以相对于基准单元100层叠有多个。例如,可以通过使附加单元200相对于基准单元100层叠有两个,从而构成层叠有六个电路模块的半导体装置1。此外,例如,也可以通过使附加单元200相对于基准单元100层叠有三个,从而构成层叠有八个电路模块的半导体装置1。此外,基准单元100和附加单元200包含的电路模块不限于两个、四个,也可以是其以上的偶数个。此外,例如,也可以包括半导体装置1,在其层叠方向一端侧、另一端侧进一步层叠一个以上的电路模块。

[0085]

附图标记说明

[0086]

1:半导体装置

[0087]

10、20、30、40、50、60:电路模块

[0088]

11、21、31、41、51、61:电路层

[0089]

12、22、32、42、52、62:衬底主体

[0090]

13、23、33、43:电极

[0091]

100:基准单元

[0092]

200:附加单元

[0093]

300:过孔

[0094]

310:基准过孔

[0095]

320:附加过孔

[0096]

301:基准过孔主体

[0097]

302:基准阻挡金属

[0098]

311:附加过孔主体

[0099]

312:附加侧阻挡金属

[0100]

400:绝缘膜

[0101]

500:蚀刻停止层

[0102]

600:交联层

[0103]

700:场氧化膜

[0104]

704:金属布线

[0105]

800:电介质膜

[0106]

900:保护膜

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1