存储器三维封装方法及结构与流程

1.本发明涉及集成电路封装技术领域,特别涉及一种存储器三维封装方法及结构。

背景技术:

2.随着超大规模集成电路的发展趋势,集成电路特征尺寸持续减小,人们对集成电路的封装技术的要求相应也不断提高。传统dram(dynamic random access memory,动态随机存取存储器)封装结构常采用pop(package on package,pop)封装结构或是多芯片三维堆叠打线封装技术,现有的(package on package,pop)由于结构设计不合理,容易出现散热效果差的问题,降低了装置的工作效率和工作性能。多芯片三维堆叠打线封装技术采用多层芯片堆叠,通过焊线实现芯片与sip基板互联,此封装技术会导致封装面积尺寸较大,封装厚度较厚,与电子封装产品小型化的发展趋势相悖。

技术实现要素:

3.本发明的目的在于提供一种存储器三维封装方法及结构,以解决现有的存储器封装结构结构设计不适合小型化发展趋势的问题。

4.为解决上述技术问题,本发明提供一种存储器三维封装方法,包括:

5.在载片上形成第一重新布线层;

6.在所述第一重新布线层上附连第一存储芯片;

7.在所述第一存储芯片上附连第二存储芯片;

8.形成覆盖所述载片、所述第一存储芯片及所述第二存储芯片的塑封层;

9.在所述塑封层上形成第二重新布线层;

10.在所述第二重新布线层上附连第三存储芯片;

11.去掉所述载片,在所述第一重新布线层上附连第四存储芯片。

12.可选的,在所述的存储器三维封装方法中,还包括:

13.在所述第一重新布线层上形成第一电镀铜柱,所述第一电镀铜柱与所述第一重新布线层电连接;

14.所述第一电镀铜柱能够通过所述第一重新布线层与所述第一存储芯片和第四存储芯片进行电连接;

15.所述第一电镀铜柱能够通过所述第二重新布线层与所述第二存储芯片和第三存储芯片进行电连接。

16.可选的,在所述的存储器三维封装方法中,还包括:

17.在所述第一存储芯片上形成粘胶层,所述第二存储芯片通过粘胶层与所述第一存储芯片粘接在一起;

18.所述第一存储芯片与所述第二存储芯片背靠背的布置。

19.可选的,在所述的存储器三维封装方法中,还包括:

20.在所述第二存储芯片上形成第二电镀铜柱,所述第二电镀铜柱的长度小于所述第

一电镀铜柱的长度;

21.所述第二电镀铜柱为第二存储芯片本体上的焊点,或形成在第二存储芯片本体焊点上的焊柱;

22.所述第二存储芯片能够通过所述第二电镀铜柱与所述第二重新布线层、所述第三存储芯片、所述第一电镀铜柱、所述第一重新布线层、所述第一存储芯片和所述第四存储芯片中的一个或多个进行电连接。

23.可选的,在所述的存储器三维封装方法中,还包括:

24.形成所述塑封层后,对所述塑封层进行减薄,以使所述第一电镀铜柱及所述第二电镀铜柱由所述塑封层中暴露出;

25.在所述第一电镀铜柱上形成所述第二重新布线层,以使所述第二重新布线层能够与所述第一电镀铜柱电连接;和/或

26.在所述第二电镀铜柱上形成所述第二重新布线层,以使所述第二重新布线层能够与所述第二电镀铜柱电连接。

27.可选的,在所述的存储器三维封装方法中,还包括:所述第三存储芯片与所述第二重新布线层电连接,并能够通过所述第二重新布线层与第一电镀铜柱、第二电镀铜柱、第一重新布线层、第一存储芯片、第二存储芯片中的一个或多个电连接;

28.在第三存储芯片与所述第二重新布线层之间形成第一底填层。

29.可选的,在所述的存储器三维封装方法中,还包括:所述第四存储芯片与所述第一重新布线层电连接,并能够通过所述第一重新布线层与第一电镀铜柱、第二电镀铜柱、第二重新布线层、第一存储芯片、第二存储芯片中的一个或多个电连接;

30.在第四存储芯片与所述第一重新布线层之间形成第二底填层。

31.本发明还提供一种存储器三维封装结构,包括:

32.第一重新布线层,被配置为正反两面分别附连第一存储芯片和第四存储芯片;

33.第二重新布线层,被配置为正反两面分别附连第二存储芯片和第三存储芯片;

34.其中,所述第一存储芯片和所述第二存储芯片附连在一起,并由塑封层包裹形成一个整体结构。

35.可选的,在所述的存储器三维封装结构中,还包括:

36.所述第一存储芯片的有源面面向所述第一重新布线层的第一面;

37.所述第二存储芯片的有源面面向所述第二重新布线层的第一面;

38.所述第三存储芯片的有源面面向所述第二重新布线层的第二面;

39.所述第四存储芯片的有源面面向所述第一重新布线层的第二面。

40.可选的,在所述的存储器三维封装结构中,还包括:

41.所述第一存储芯片、所述第二存储芯片、所述第三存储芯片及所述第四存储芯片占用的面积相同,且堆叠在不同布线层的同一位置;

42.所述第一重新布线层的面积大于所述第一存储芯片及所述第四存储芯片占用的面积;

43.所述第二重新布线层的面积大于所述第二存储芯片及所述第三存储芯片占用的面积。

44.发明人通过研究发现,在现有的存储器封装结构中,多芯片三维堆叠打线封装技

术采用多层芯片堆叠,通过焊线实现芯片与sip基板互联,此封装技术会导致封装面积尺寸较大,封装厚度较厚,与电子封装产品小型化的发展趋势相悖,或者如图1所示,采用两个芯片封装在一个封装模块中,多个封装模块堆叠,可以通过该封装模块顶端的重新布线层将电性引出,因此,四个存储芯片就需要两个封装模块叠加,且两个封装模块的重新布线层需要更多的布线面积,使得整个封装结构体积大、面积大、散热效果差、且需要两次进行封装模块在制作,工艺复杂。

45.基于上述洞察,本发明提供了一种存储器三维封装方法及结构,通过在第一重新布线层上依次附连第一存储芯片及第二存储芯片、形成塑封层、形成第二重新布线层、附连第三存储芯片、附连第四存储芯片,形成了第一重新布线层正反两面分别附连第一存储芯片和第四存储芯片,第二重新布线层正反两面分别附连第二存储芯片和第三存储芯片,第一存储芯片和第二存储芯片附连且由塑封层包裹形成一个整体的结构,不仅将所有的存储芯片集成在同一封装模块中,减小的封装体积,且第一重新布线层和第二重新布线层分布在该封装模块的正反两面,分别引出附连其上的两个芯片的电性,不需要较大的布线面积,进一步减小了封装体积和面积;进一步的,第三存储芯片和第四存储芯片暴露在整个封装结构的外侧,散热效果好,无需布置复杂的散热模块,且容易和其他封装体对接,同时整个工艺一次成型,仅需要一次键合和拆键合,工艺简单;存储芯片之间垂直互连,有效缩短了传输路径,提高传输速率。

46.由于存储芯片之间大多数情况下型号、外观和尺寸相同,因此,第一存储芯片、第二存储芯片、第三存储芯片及第四存储芯片占用的面积相同,本发明通过将四个芯片堆叠在不同布线层的同一位置,将本封装结构的占用面积降至最小。

附图说明

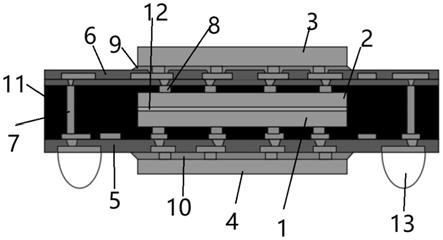

47.图1是现有的存储器三维封装结构示意图;

48.图2是本发明一实施例存储器三维封装结构示意图;

49.图3是本发明一实施例存储器三维封装方法形成第一重新布线层示意图;

50.图4是本发明一实施例存储器三维封装方法附连第一存储芯片示意图;

51.图5是本发明一实施例存储器三维封装方法附连第二存储芯片示意图;

52.图6是本发明一实施例存储器三维封装方法形成塑封层示意图;

53.图7是本发明一实施例存储器三维封装方法附连第三存储芯片示意图;

54.图8是本发明一实施例存储器三维封装方法附连第四存储芯片示意图;

55.图中所示:1

‑

第一存储芯片;2

‑

第二存储芯片;3

‑

第三存储芯片;4

‑

第四存储芯片;5

‑

第一重新布线层;6

‑

第二重新布线层;7

‑

第一电镀铜柱;8

‑

第二电镀铜柱;9

‑

第一底填层;10

‑

第二底填层;11

‑

塑封层;12

‑

粘胶层;13

‑

焊球;14

‑

载片。

具体实施方式

56.以下结合附图和具体实施例对本发明提出的存储器三维封装方法及结构作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

57.另外,除非另行说明,本发明的不同实施例中的特征可以相互组合。例如,可以用第二实施例中的某特征替换第一实施例中相对应或功能相同或相似的特征,所得到的实施例同样落入本申请的公开范围或记载范围。

58.本发明的核心思想在于提供一种存储器三维封装方法及结构,以解决现有的存储器封装结构结构设计不适合小型化发展趋势的问题。

59.为实现上述思想,本发明提供了一种存储器三维封装方法及结构,包括:在载片上形成第一重新布线层;在所述第一重新布线层上附连第一存储芯片;在所述第一存储芯片上附连第二存储芯片;形成覆盖所述载片、所述第一存储芯片及所述第二存储芯片的塑封层;在所述塑封层上形成第二重新布线层;在所述第二重新布线层上附连第三存储芯片;去掉所述载片,在所述第一重新布线层上附连第四存储芯片。

60.本实施例提供一种存储器三维封装方法,包括:如图3~8所示,在载片14上形成第一重新布线层5;在所述第一重新布线层5上附连第一存储芯片1;在所述第一存储芯片1上附连第二存储芯片2;形成覆盖所述载片14、所述第一存储芯片1及所述第二存储芯片2的塑封层11;在所述塑封层11上形成第二重新布线层6;在所述第二重新布线层6上附连第三存储芯片3;去掉所述载片14,在所述第一重新布线层5上附连第四存储芯片4。

61.在本发明的一个实施例中,在所述的存储器三维封装方法中,如图3所示,还包括:在形成第一重新布线层5之后,附连第一存储芯片之前,在所述第一重新布线层5上形成第一电镀铜柱7,所述第一电镀铜柱7与所述第一重新布线层5电连接;如图4所示,附连第一存储芯片1时,第一存储芯片的有源面面向第一重新布线层,且两者电连接;并进一步的所述第一电镀铜柱7能够通过所述第一重新布线层5与所述第一存储芯片1进行电连接。

62.在本发明的一个实施例中,在所述的存储器三维封装方法中,如图5所示,还包括:在所述第一存储芯片1上形成粘胶层12,所述第二存储芯片2通过粘胶层12与所述第一存储芯片1粘接在一起;所述第一存储芯片1与所述第二存储芯片2背靠背的布置。

63.在本发明的一个实施例中,在所述的存储器三维封装方法中,如图5所示,还包括:在所述第二存储芯片2上形成第二电镀铜柱8,所述第二电镀铜柱8的长度小于所述第一电镀铜柱7的长度;所述第二电镀铜柱8为第二存储芯片2本体上的焊点,或形成在第二存储芯片2本体焊点上的焊柱;所述第二存储芯片2能够通过所述第二电镀铜柱8与所述第二重新布线层6、所述第三存储芯片3、所述第一电镀铜柱7、所述第一重新布线层5、所述第一存储芯片1和所述第四存储芯片4中的一个或多个进行电连接。

64.在本发明的一个实施例中,在所述的存储器三维封装方法中,如图6所示,形成塑封层;还包括:形成所述塑封层11后,对所述塑封层11进行减薄,以使所述第一电镀铜柱7及所述第二电镀铜柱8由所述塑封层11中暴露出;在所述第一电镀铜柱7上形成所述第二重新布线层6,以使所述第二重新布线层6能够与所述第一电镀铜柱7电连接(所述第一电镀铜柱7能够通过所述第二重新布线层6与所述第二存储芯片2电连接);和/或在所述第二电镀铜柱8上形成所述第二重新布线层6,以使所述第二重新布线层6能够与所述第二电镀铜柱8电连接。

65.在本发明的一个实施例中,在所述的存储器三维封装方法中,如图7所示,形成第二重新布线层;还包括:所述第三存储芯片3与所述第二重新布线层6电连接,并能够通过所述第二重新布线层6与第一电镀铜柱7、第二电镀铜柱8、第一重新布线层5、第一存储芯片1、

第二存储芯片2中的一个或多个电连接;在第三存储芯片3与所述第二重新布线层6之间形成第一底填层9。

66.在本发明的一个实施例中,在所述的存储器三维封装方法中,如图8所示,去掉载片后附连第四存储芯片;还包括:所述第四存储芯片4与所述第一重新布线层5电连接,并能够通过所述第一重新布线层5与第一电镀铜柱7、第二电镀铜柱8、第二重新布线层6、第一存储芯片1、第二存储芯片2中的一个或多个电连接;在第四存储芯片4与所述第一重新布线层5之间形成第二底填层10。第四存储芯片4能够通过所述第一重新布线层5与所述第一电镀铜柱7进行电连接。之后,还可以在第一重新布线层5和/或第二重新布线层6上形成焊球13。

67.本实施例还提供一种存储器三维封装结构,如图2所示,包括:第一重新布线层5,被配置为正反两面分别附连第一存储芯片1和第四存储芯片4;第二重新布线层6,被配置为正反两面分别附连第二存储芯片2和第三存储芯片3;其中,所述第一存储芯片1和所述第二存储芯片2附连在一起,并由塑封层11包裹形成一个整体结构。

68.在本发明的一个实施例中,在所述的存储器三维封装结构中,还包括:所述第一存储芯片1的有源面面向所述第一重新布线层5的第一面;所述第二存储芯片2的有源面面向所述第二重新布线层6的第一面;所述第三存储芯片3的有源面面向所述第二重新布线层6的第二面;所述第四存储芯片4的有源面面向所述第一重新布线层5的第二面。

69.在本发明的一个实施例中,在所述的存储器三维封装结构中,还包括:所述第一存储芯片1、所述第二存储芯片2、所述第三存储芯片3及所述第四存储芯片4占用的面积相同,且堆叠在不同布线层的同一位置;所述第一重新布线层5的面积大于所述第一存储芯片1及所述第四存储芯片4占用的面积;所述第二重新布线层6的面积大于所述第二存储芯片2及所述第三存储芯片3占用的面积。

70.综上所述,本发明提供了一种存储器三维封装方法及结构,通过在第一重新布线层5上依次附连第一存储芯片1及第二存储芯片2、形成塑封层11、形成第二重新布线层6、附连第三存储芯片3、附连第四存储芯片4,形成了第一重新布线层5正反两面分别附连第一存储芯片1和第四存储芯片4,第二重新布线层6正反两面分别附连第二存储芯片2和第三存储芯片3,第一存储芯片1和第二存储芯片2附连且由塑封层11包裹形成一个整体的结构,不仅将所有的存储芯片集成在同一封装模块中,减小的封装体积,且第一重新布线层5和第二重新布线层6分布在该封装模块的正反两面,分别引出附连其上的两个芯片的电性,不需要较大的布线面积,进一步减小了封装体积和面积;进一步的,第三存储芯片和第四存储芯片暴露在整个封装结构的外侧,散热效果好,无需布置复杂的散热模块,且容易和其他封装体对接,同时整个工艺一次成型,仅需要一次键合和拆键合,工艺简单;存储芯片之间垂直互连,有效缩短了传输路径,提高传输速率。

71.由于存储芯片之间大多数情况下型号、外观和尺寸相同,因此,第一存储芯片1、第二存储芯片2、第三存储芯片3及第四存储芯片4占用的面积相同,本发明通过将四个芯片堆叠在不同布线层的同一位置,将本封装结构的占用面积降至最小。

72.综上,上述实施例对存储器三维封装方法及结构的不同构型进行了详细说明,当然,本发明包括但不局限于上述实施中所列举的构型,任何在上述实施例提供的构型基础上进行变换的内容,均属于本发明所保护的范围。本领域技术人员可以根据上述实施例的内容举一反三。

73.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

74.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1