一种具有电荷平衡结构的沟槽MOSFET及其制作方法与流程

一种具有电荷平衡结构的沟槽mosfet及其制作方法

技术领域

1.本发明涉及具有电荷平衡结构的沟槽mosfet及其制作方法技术领域,具体涉及一种具有电荷平衡结构的沟槽mosfet及其制作方法。

背景技术:

2.普通沟型mosfet产品主要依靠漂移区承受耐压,一般通过提高外延电阻率和厚度来增加漂移区宽度的方式,提高击穿电压(bvdss),相应地,器件的导通电阻(rdson)也会急速增加,rdson和bvdss存在2.5倍的制约关系。

3.虽然沟槽型mosfet在漂移区内引入横向电场,可改善rdson和bvdss的制约关系。但由于栅氧化层和输入电容(ciss)的限制,结合工艺难度,沟槽深度不能无限增加。随着bvdss的增加,沟槽的作用逐渐降低。

技术实现要素:

4.本发明的目的是针对现有技术存在的不足,提供一种具有电荷平衡结构的沟槽mosfet及其制作方法。

5.为实现上述目的,本发明提供了一种具有电荷平衡结构的沟槽mosfet,包括第一导电类型的衬底,所述衬底上侧制作有外延,所述外延中部刻蚀形成第一沟槽,所述第一沟槽的表面生长有第一导电类型的连接层,所述连接层内侧的第一沟槽内经外延生长形成第二导电类型的柱区,所述第一沟槽两侧的外延内刻蚀形成第二沟槽,所述第二沟槽的表面长有氧化层,所述氧化层的上表面长有高k介质层,所述高k介质层外侧的第二沟槽内设有掺杂的多晶,所述外延的上侧制作有第二导电类型的体区,所述体区的上侧制作有第一导电类型的掺杂区,所述掺杂区、第一沟槽和第二沟槽的上侧沉积有介质层,所述介质层、掺杂区和体区上刻蚀形成连接孔,所述连接孔的下端深入至第一沟槽上方的体区内,所述介质层的上侧和连接孔内设置有金属。

6.进一步的,所述第一沟槽的和第二沟槽的宽度均为0.2

‑

1.2μm,所述第二沟槽的深度为0.6

‑

2μm,所述第一沟槽的深度大于第二沟槽深度0.5μm以上。

7.进一步的,所述第一沟槽和第二沟槽的宽度均从上端至底端逐渐减小,所述第一沟槽的侧壁的倾斜角度为88

°‑

89

°

,所述第二沟槽的侧壁的倾斜角度为89

°

。

8.进一步的,所述外延的电阻率为0.1

‑

3ω.cm,所述连接层的电阻率比外延的电阻率低60%

‑

80%,所述柱区的电阻率比外延的电阻率低40%

‑

60%。

9.进一步的,所述连接层的厚度为第一沟槽的宽度的八分之一至十二分之一。

10.在第二方面,本发明提供了一种如上述的具有电荷平衡结构的沟槽mosfet的制作方法,包括:

11.提供第一导电类型的衬底,并在所述衬底上侧制作外延;

12.在所述外延上侧沉积一层掩膜,并在外延的中部刻蚀形成第一沟槽;

13.在所述第一沟槽的表面长一层第一导电类型的连接层;

14.在所述连接层内侧的第一沟槽内生长第二导电类型的外延,以形成柱区,

15.并将露出第一沟槽上端的柱区去除;

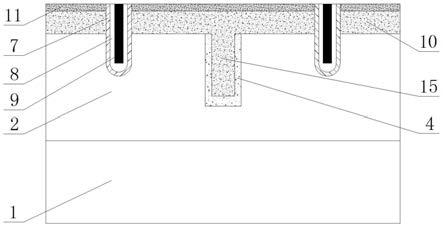

16.在所述外延的上侧长掩蔽层,并在所述第一沟槽的两侧的外延内刻蚀形成第二沟槽;

17.在所述第二沟槽的表面长氧化层,并在所述氧化层的上表面长高k介质层;

18.在所述高k介质层外侧的第二沟槽内沉积多晶,并对多晶进行掺杂;

19.在所述外延的上侧制作第二导电类型的体区,并在所述体区的上侧制作第一导电类型的掺杂区;

20.在所述掺杂区、第一沟槽和第二沟槽的上侧沉积介质层,在所述介质层、掺杂区和体区上刻蚀形成连接孔,所述连接孔的下端深入至第一沟槽上方的体区内;

21.在所述介质层的上侧和连接孔内设置金属。

22.进一步的,所述第一沟槽的和第二沟槽的宽度均为0.2

‑

1.2μm,所述第二沟槽的深度为0.6

‑

2μm,所述第一沟槽的深度大于第二沟槽深度0.5μm以上。

23.进一步的,所述第一沟槽和第二沟槽的宽度均从上端至底端逐渐减小,所述第一沟槽的侧壁的倾斜角度88

°‑

89

°

,所述第二沟槽的侧壁的倾斜角度89

°

。

24.进一步的,所述外延的电阻率为0.1

‑

3ω.cm,所述连接层的电阻率比外延的电阻率低60%

‑

80%,所述柱区的电阻率比外延的电阻率低40%

‑

60%。

25.进一步的,所述连接层的厚度为第一沟槽的宽度的八分之一至十二分之一。

26.有益效果:本发明具有以下优点:

27.1、在第一沟槽内形成电荷平衡结构,引入平行电场,改变漂移区电场分布,提高器件耐压,降低rsp(单位面积电阻率),从而降低导通损耗。

28.2、第二沟槽内采用高k介质材料,可优化第二深槽对bvdss的制约作用,进一步优化器件性能。

29.3、与现有工艺平台兼容,工艺实现简单且工艺窗口足够。

附图说明

30.图1是在外延上刻蚀出第一沟槽后的结构示意图;

31.图2是在第一沟槽内制作出连接层和柱区后的结构示意图;

32.图3是在外延上刻蚀出第二沟槽后的结构示意图;

33.图4是在第二沟槽内制作出氧化层和高k介质层后的结构示意图;

34.图5是在第二沟槽内沉积多晶后的结构示意图;

35.图6是在外延上制作出体区和第一导电类型的掺杂区后的结构示意图;

36.图7是在介质层上刻蚀出连接孔的结构示意图;

37.图8是在介质层及连接孔内设置金属后的结构示意图;

38.图9是具有电荷平衡结构的沟槽型mosfet的局部电场分布三维图;

39.图10是本申请与现有的常规结构在与柱区平行方向电场分布对比图;

40.图11是本申请与现有的常规结构在与柱区垂直方向电场分布对比图;

41.图12是柱区的电阻率与bvdss的关系图;

42.图13是柱区的电阻率与vth的关系图;

43.图14是柱区的电阻率与rsp的关系图;

44.图15是柱区的电阻率与ciss的关系图;

45.图16是柱区的电阻率与coss的关系图;

46.图17是柱区的电阻率与crss的关系图;

47.图18是柱区的深度与bvdss的关系图;

48.图19是柱区的深度与rsp的关系图;

49.图20是柱区的宽度与bvdss的关系图。

具体实施方式

50.下面结合附图和具体实施例,进一步阐明本发明,本实施例在以本发明技术方案为前提下进行实施,应理解这些实施例仅用于说明本发明而不用于限制本发明的范围。

51.如图8所示,本发明实施例提供了一种具有电荷平衡结构的沟槽mosfet,包括第一导电类型的衬底1,在衬底1上侧制作有外延2,衬底1为重掺杂,外延2为第一导电类型轻掺杂。在外延2中部刻蚀形成第一沟槽3,第一沟槽3的表面长有第一导电类型的连接层4,连接层4内侧的第一沟槽3内生长有第二导电类型的外延,形成第二导电类型的柱区。在第一沟槽3两侧的外延2内刻蚀形成第二沟槽6,第二沟槽6的深度低于第一沟槽3的深度,第二沟槽6的表面长有氧化层7,氧化层7的厚度优选为100

‑

200埃。在氧化层7的上表面长有高k介质层8,高k介质层8的厚度优选为50

‑

500埃,高k介质层8可以是氮化硅(si3n4)等。在高k介质层8外侧的第二沟槽6内设有掺杂的多晶9,掺杂的多晶9在芯片的边缘引出,作为栅极。掺杂的多晶9的厚度为0.8

‑

1.2μm,在外延2的上侧制作有第二导电类型的体区10,在体区10的上侧制作有第一导电类型的掺杂区11,在掺杂区11、第一沟槽3和第二沟槽6的上侧沉积有介质层12,在介质层12、掺杂区11和体区10上刻蚀形成连接孔13,连接孔13的下端深入至第一沟槽3上方的体区10内,在介质层12上侧和连接孔13内设置有金属14。为了降低接触电阻,可对连接孔执行注入和退火操作,注入元素为bf2/b,剂量:2e14

‑

5e14,能量:30

‑

40kev,快速退火:950℃30s。金属14优选包括先在连接孔13内淀积的ti/tin层,然后在连接孔13内填充钨金属,形成欧姆接触孔。最后再沉积厚度为4μm金属铝,铝中可掺杂一定比例的sicu,防止铝硅互溶,然后光刻腐蚀铝。

52.本发明实施例的第一沟槽3的和第二沟槽6的宽度均优选为0.2

‑

1.2μm,第二沟槽6的深度优选为0.6

‑

2μm,第一沟槽3的深度优选大于第二沟槽6深度0.5μm以上。

53.本发明实施例的外延2的电阻率为0.1

‑

3ω.cm,其厚度通常为3

‑

15μm,连接层4的电阻率优选比外延2的电阻率低60%

‑

80%,柱区15的电阻率比外延2低40%

‑

60%。连接层4的厚度为第一沟槽3的宽度的八分之一至十二分之一,优选为十分之一。

54.还可以在金属14的上侧沉积钝化层,钝化层可以是氮化硅层,钝化层的厚度优选为7000

‑

12000埃,然后光刻腐蚀,形成gate和source的开口区,可降低芯片表面可动离子引起的器件漏电。

55.还可在衬底1的下侧设置背金层,在设置背金层前,先从衬底1的下侧减薄至剩余厚度为150μm左右,然后在衬底1的下侧依次蒸发ti

‑

ni

‑

ag(钛

‑

镍

‑

银)。

56.基于以上实施例,本领域技术人员可以理解,本发明还提供了一种上述具有电荷平衡结构的沟槽mosfet的制作方法,包括:

57.如图1所示,提供第一导电类型的衬底1,并在衬底1上侧制作外延2。以下以第一导电类型为n型、第二导电类型为p型为例具体说明,衬底1可以采用n型(100)晶向,通过砷元素或磷元素掺杂,衬底1的电阻率通常在0.001

‑

0.05ω.cm。外延2的电阻率和厚度,由不同的器件耐压决定。通常外延2的厚度为3

‑

15μm,外延电阻率为0.1

‑

3ω.cm,器件耐压可以达到20v

‑

200v。

58.在外延2上侧沉积一层掩膜101,并在外延2的中部刻蚀形成第一沟槽3。掩膜101可以是一层sio2+si3n4膜,厚度优选为8000埃,可根据第一沟槽3的刻蚀形貌做微调。第一沟槽3的深度依工作电压而定,第一沟槽3的宽度优选为0.2

‑

1.2μm。需要说明的是,在刻蚀完成第一沟槽3后,需要将掩膜101刻蚀掉。

59.如图2所示,在第一沟槽3的表面长一层第一导电类型的连接层4。连接层4可以视为不同于外延2的外延层,连接层4的电阻率优选比外延2的电阻率低60%

‑

80%,连接层4的厚度为第一沟槽3的宽度的八分之一至十二分之一,优选为十分之一。

60.在连接层4内侧的第一沟槽3内生长第二导电类型的外延,以形成柱区15,并将露出第一沟槽3上端柱区15去除。可通过化学机械研磨(cmp)工艺去除露出第一沟槽3上端的柱区15。柱区15的电阻率优选比外延2低40%

‑

60%。

61.如图3所示,在外延2的上侧长掩蔽层102,并在第一沟槽3两侧的外延2内刻蚀形成第二沟槽6。掩蔽层102的厚度优选为4000埃,掩蔽层102的厚度可根据第二沟槽6的形貌做微调,第二沟槽6的宽度优选为0.2

‑

1.2μm,深度优选为0.6

‑

2μm。第一沟槽的深度大于第二沟槽深度0.5μm以上。需要说明的是,在刻蚀完成第二沟槽6后,需要将掩蔽层102刻蚀掉。

62.如图4所示,在第二沟槽6的表面长氧化层7,并在氧化层7的上表面长高k介质层8。氧化层7的厚度优选为100

‑

200埃,生长温度950℃

‑

1050℃。高k介质层8的厚度优选50

‑

500埃,高k介质层8可以是如氮化硅(si3n4)等。在生长氧化层7前,可以在第二沟槽6内先通过干法氧化形成一层厚度500

‑

2000埃的牺牲氧化层,氧化温度1000

‑

1100℃,湿法漂洗去除所有牺牲氧化层,修复第二沟槽6内的刻蚀损伤,并使第二沟槽6的底部圆滑。

63.如图5所示,在高k介质层8外侧的第二沟槽6内沉积多晶,并对多晶进行掺杂。从而形成掺杂的多晶9,沉积多晶的厚度优选为0.8

‑

1.2μm,多晶掺杂浓度1e19

‑

6e19,掺杂元素:磷。

64.如图6所示,在外延2的上侧制作第二导电类型的体区10,并在体区10的上侧制作第一导电类型的掺杂区11。其中体区10通过注入b元素和退火形成,注入能量60kev

‑

120kev,剂量根据vth参数的需求调整,通常在5e12

‑

3e13左右,退火条件:1100℃/60min,也可以采用双注入提高p阱掺杂浓度的均匀性。第一导电类型的掺杂区11的注入元素:as元素,能量60kev,退火条件:950℃/60min。

65.如图7所示,在掺杂区11、第一沟槽3和第二沟槽6的上侧沉积介质层12,在介质层12、掺杂区11和体区10上刻蚀形成连接孔13,连接孔13的下端深入至第一沟槽3上方的体区10内。介质层12的厚度优选为8000

‑

12000埃,可向介质层12掺入一定比例的b元素和p元素,吸收可动na、k离子,提高器件可靠性。连接孔13的深度一般为0.3

‑

0.45μm。

66.如图8所示,在介质层12的上侧和连接孔13内设置金属14。为了降低接触电阻,可对连接孔执行注入和退火操作,注入元素为bf2/b,剂量:2e14

‑

5e14,能量:30

‑

40kev,快速退火:950℃,30s。金属14优选包括先在连接孔13内淀积的ti/tin层,然后在连接孔13内填

充钨金属,形成欧姆接触孔。最后在沉积厚度为4um金属铝,铝中可掺杂一定比例的sicu,防止铝硅互溶,然后光刻腐蚀铝。

67.还可以在金属14的上侧沉积钝化层,钝化层可以是氮化硅层,钝化层的厚度优选为7000

‑

12000埃,然后光刻腐蚀,形成gate和source的开口区,可降低芯片表面可动离子引起的器件漏电。

68.还可在衬底1的下侧设置背金层,在设置背金层前,先从衬底1的下侧减薄至剩余厚度为150μm左右,然后在衬底1的下侧依次蒸发ti

‑

ni

‑

ag(钛

‑

镍

‑

银)。

69.本发明实施例的第一沟槽3和第二沟槽6的宽度均优选从上端至底端逐渐减小,其中,第一沟槽3的侧壁的倾斜角度优选为88

°‑

89

°

,以便于后续制作连接层4。第二沟槽6的侧壁的倾斜角度为89

°

,以便于后续制作氧化层7和高k介质层8。

70.参见图9和10,本申请的沟槽mosfet电场强度分布更加平坦,如图11所示,横向电场强度增加10%左右,从而提高耐压效率。参见图12至14,其分别示意了不同的柱区电阻率与bvdss(雪崩电压)、rsp(单位面积电阻)和vth(阈值电压)对应关系,bvdss随柱区电阻率的增加,呈抛物线分布,属于典型的电荷平衡效应。柱区电阻率增加,其对外延2的影响逐渐减小,rsp相应减小,选择合适的柱区电阻率,与常规结构相比,对于100v产品,rsp可降低15%左右,器件耐压越高,rsp的降低越明显。柱区电阻率对vth影响很小。参见图15至17,其分别示意了不同柱区电阻率与ciss(输入电容)、coss(输出电容)和crss(米勒电容)对应关系。ciss与rsp变化趋势一致。coss呈v型分布,对应柱区电阻率转折点在bvdss抛物线分度顶点附近。crss在该点附近也存在突变。参见图18和19,其分别示意了不同柱区深度与bvdss和rsp对应关系图,柱区靠近体区10的底部时,柱区深度对bvdss影响较小;当深度逐渐增加,bvdss呈线性增加;柱区靠近外延2的底部时,深度几乎不影响bvdss。柱区深度对rsp的影响与bvdss一致。参见图20,为不同柱区宽度与bvdss对应关系图,当元胞尺寸不变时,随着柱区宽度增加,其对外延2的影响会越来越大,bvdss呈线性增加,相应的,rsp也会呈线性增加。

71.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,其它未具体描述的部分,属于现有技术或公知常识。在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1