半导体衬底配置结构的制作方法

1.本公开涉及一种半导体衬底配置结构、特别涉及一种之上布置有金属层的半导体衬底配置结构。

背景技术:

2.功率半导体模块配置结构通常包括布置在壳体中的至少一个半导体衬底。包括多个半导体本体(例如,半桥配置中的两个igbt)的半导体配置结构布置在至少一个衬底中的每个上。每个衬底通常包括衬底层(例如,陶瓷层)、沉积在衬底层的第一侧上的第一金属化层和沉积在衬底层的第二侧上的第二金属化层。例如,半导体本体安装在第一金属化层上。第二金属化层可以可选地附接到基板。可控半导体器件通常通过焊接或烧结技术安装到半导体衬底上。金属层可以布置在半导体本体与第一金属化层之间,例如,金属层形成将半导体本体机械地和电地耦接到半导体衬底的连接层。通常,薄的金属涂层布置在这种金属连接层与第一金属化层之间。当将金属涂层形成在半导体衬底上时,通常在紧邻金属涂层的第一金属化层中出现不希望的空腔。在形成金属涂层的过程已经完成之后,污染物可能会残留在不希望的空腔中。例如,这些污染物可以在将半导体本体安装在衬底上的随后的烧结过程期间以及在诸如清洁步骤的随后的工艺步骤期间释放出来,并且可能在生产线末端处导致半导体衬底的金属化层的不希望的氧化。这可能导致产量损失。

3.需要一种减少了生产线末端的产量损失的半导体衬底。

技术实现要素:

4.一种半导体衬底配置结构包括:半导体衬底,所述半导体衬底包括介电绝缘层和附接到所述介电绝缘层的第一金属化层,其中,所述第一金属化层在垂直方向上布置在所述介电绝缘层上。所述半导体衬底配置结构还包括在垂直方向上布置在所述第一金属化层上的导电涂层,使得第一金属化层布置在所述导电涂层与所述介电绝缘层之间。在距导电涂层的外周的第一距离内的水平面中,第一金属化层不包括任何空腔或沟槽,或者仅包括在水平方向上具有小于10μm的最大宽度和在垂直方向上具有小于3μm的最大深度的空腔或沟槽。

5.参考以下附图和描述可以更好地理解本发明。附图中的构件不一定按比例绘制,而是将重点放在说明本发明的原理上。此外,在附图中,相似或相同的附图标记在不同的视图中指代对应的部分。

附图说明

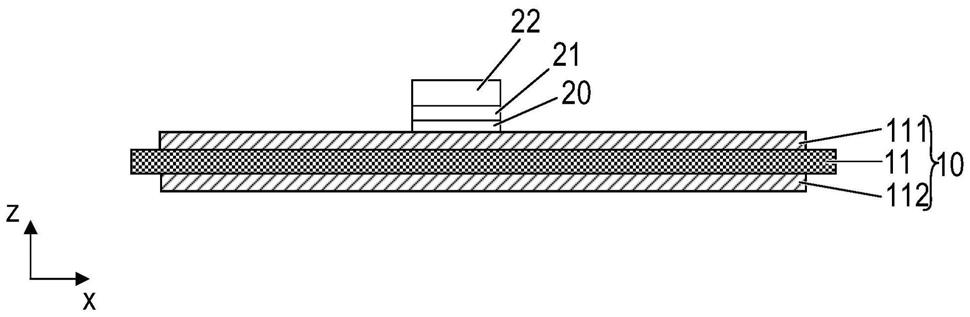

6.图1是半导体衬底配置结构的剖视图。

7.图2a

‑

2c示意性地示出了用于形成半导体模块配置结构的常规工艺。

8.图3a

‑

3d示意性地示出了用于形成半导体衬底配置结构的示例性方法。

9.图4a和4b示出了当使用常规镀覆工艺时在形成金属涂层之前和之后的半导体衬

底配置结构的俯视图。

10.图5a和5b示出了当使用示例性镀覆工艺时在形成金属涂层之前和之后的半导体衬底配置结构的俯视图。

具体实施方式

11.在下面的详细描述中,参考了附图。附图示出了可以实践本发明的具体示例。应当理解的是,除非另外特别指出,否则结合各个示例描述的各个特征和原理可以彼此组合。在说明书以及权利要求书中,某些元件命名为“第一元件”、“第二元件”、“第三元件”等不应被理解为枚举。相反,此类命名仅仅用于称呼不同的“元件”。也就是说,例如,“第三元件”的存在不需要“第一元件”和“第二元件”必须存在。本文所述的半导体本体可以由(掺杂的)半导体材料制成,并且可以是半导体芯片或被包括在半导体芯片中。半导体本体具有电连接焊盘并且包括电极。

12.参考图1,示意性地示出了半导体衬底配置结构的剖视图。半导体衬底配置结构包括半导体衬底10。半导体衬底10包括介电绝缘层11、附接到介电绝缘层11的第一金属化层111和附接到介电绝缘层11的第二金属化层112。介电绝缘层11设置在第一与第二金属化层111、112之间。然而,半导体衬底10也可以仅包括第一金属化层111,而省略第二金属化层112。

13.第一和第二金属化层111、112中的每一个可以由以下材料中的一种组成或包括以下材料中的一种:铜;铜合金;铝;铝合金;在半导体衬底配置结构的操作期间保持固体的任何其它金属或合金。半导体衬底10可以是陶瓷衬底,即,介电绝缘层11是陶瓷、例如薄陶瓷层的衬底。陶瓷可以由以下材料中的一种组成或包括以下材料中的一种:氧化铝;氮化铝;氧化锆;氮化硅;氮化硼;或任何其它介电陶瓷。例如,介电绝缘层11可以由以下材料中的一种组成或包括以下材料中的一种:al2o3、aln、sic、beo或si3n4。例如,衬底10可以是例如直接铜结合(dcb:direct copper bonding)衬底、直接铝结合(dab:direct aluminum bonding)衬底或活性金属钎焊(amb:active metal brazing)衬底。此外,衬底10可以是绝缘金属衬底(ims:insulated metal substrate)。例如,绝缘金属衬底通常包括这样的介电绝缘层11:所述介电绝缘层11包括(填充的)材料,例如环氧树脂或聚酰亚胺。例如,介电绝缘层11的材料可以填充有陶瓷颗粒。这样的颗粒可以包括例如si2o、al2o3、aln或bn,并且可以具有在大约1μm至大约50μm之间的直径。衬底10也可以是具有非陶瓷介电绝缘层11的常规印刷电路板(pcb:printed circuit board)。例如,非陶瓷介电绝缘层11可以由固化树脂组成或包括固化树脂。

14.通常,一个或多个半导体本体22可以布置在半导体衬底10上。布置在半导体衬底10上的半导体本体中的每个可以包括igbt(绝缘栅双极晶体管:insulated

‑

gate bipolar transistor)、mosfet(金属氧化物半导体场效应晶体管:metal

‑

oxide

‑

semiconductor field

‑

effect transistor)、jfet(结场效应晶体管:junction field

‑

effect transistor)、hemt(高电子迁移率晶体管)和/或任何其它合适的半导体元件。一个或多个半导体本体22可以在半导体衬底10上形成半导体配置结构。在图1所示的示例中,仅示意性地示出了一个半导体本体22。

15.图1中的半导体衬底10的第一金属化层111和第二金属化层112是连续层。然而,在

图1所示的配置结构中,第一金属化层111和/或第二金属化层112也可以是结构化层。“结构化层”是指第一或第二金属化层111、112不是连续层,而是在层的不同区段之间包括凹部。例如,不同的半导体本体22可以被安装到第一金属化层111的相同或不同的区段。第一金属化层111的不同的区段可以不具有电连接,或者可以使用电连接结构(未具体示出)、例如接合导线或接合带电连接到一个或多个其它区段。例如,电连接结构还可以包括连接板或导体轨,在此仅举这几个示例。

16.半导体本体22可以借助于导电连接层21电和机械地连接到半导体衬底10。例如,这样的导电连接层21可以是焊料层、导电粘合剂层或烧结金属粉层、例如烧结银粉层。通常,在第一金属化层111与导电连接层21之间布置有附加的导电涂层20。导电涂层20通常是在垂直方向z上具有数(百)纳米厚度的层。导电涂层20通常是薄金属层。例如,导电涂层20可以包括诸如银的金属材料。例如,导电涂层20还可以包括其它导电材料,例如镍或金。导电涂层20也可以包括银、镍和金中的两种或更多种的组合。在施加导电涂层20之后,在第一金属化层111与导电涂层20之间发生离子交换。例如,如果第一金属化层111是铜层并且导电涂层20是薄银层,则铜原子可以扩散到导电涂层20中,而银离子可以扩散到第一金属化层111中。这使得金属化层111与导电涂层20之间的边界模糊。换言之,在第一金属化层111与导电涂层20之间不再有清晰的边界。形成了包含两种材料的离子的过渡区。

17.一旦已经形成导电涂层20,就可以在导电涂层20上形成导电连接层21,使得导电涂层20布置在导电连接层21与第一金属化层111之间。导电连接层21通常在垂直方向z上具有比导电涂层20更大的厚度。在进一步的步骤中,可以在导电连接层21上布置半导体本体22,并且例如可以执行烧结工艺,以便将半导体本体22机械地和电地耦合到半导体衬底10。然后,导电连接层21提供半导体本体22与半导体衬底10之间的永久连接。

18.现在参考图2a

‑

2c,示意性地示出了用于形成包括之上布置有导电涂层20的半导体衬底10的半导体衬底配置结构的传统方法。在第一步骤中,提供半导体衬底10。半导体衬底10包括至少第一金属化层111。如上面结合图1所述的,该第一金属化层111布置在介电绝缘层11上。掩模30布置在第一金属化层111上。该掩模30通常在垂直方向z上具有变化的厚度。垂直方向z是垂直于半导体衬底10的顶表面的方向。例如,第一金属化层111在垂直方向z上布置在介电绝缘层11上。掩模30布置在第一金属化层111上,使得第一金属化层111布置在掩模30与介电绝缘层11之间。掩模30具有至少一个开口。换言之,并不是所有的第一金属化层111都被掩模30覆盖。开口具有对应于待形成在半导体衬底10上的导电涂层20的横截面的横截面。例如,横截面可以是方形横截面或矩形横截面(图2a

‑

2c的剖视图中不可见所述横截面)。

19.如果要在半导体衬底10上形成多于一个的导电涂层20,则掩模30包括多于一个的开口。掩模30中的开口的数量对应于待形成在半导体衬底10上的导电涂层20的数量。

20.掩模30覆盖半导体衬底10的未被导电涂层20覆盖的所有部分。如上所述,当将掩模30施加到半导体衬底10时,掩模30在垂直方向z上的厚度通常是不均匀的。通常,与开口相邻的掩模30的厚度小于远离开口的掩模30的厚度。换言之,半导体衬底10的顶表面与掩模30的边缘之间所形成的角度α例如在130

°

至170

°

之间。如图2b中示意性地示出的,这通常使得在与导电涂层20相邻的第一金属化层111中形成不希望的空腔或沟槽40。导电涂层20可以通过任何合适的工艺来施加,例如丝网印刷、镀覆工艺或蒸发沉积。在图2b中借助于箭

头表示在施加导电涂层20的步骤期间第一金属化层111的不希望的材料去除和空腔或沟槽40的形成。

21.一旦在半导体衬底10上已形成导电涂层20,就可以去除掩模30。这在图2c中示意性地示出。例如,为了去除掩模30,可使用蚀刻工艺。掩模30在垂直方向z上的厚度减小由图2c中的虚线表示。由于掩模30具有变化的厚度,因此某些部分(例如,与导电涂层20相邻)的厚度比其它部分更早地减小到零。因此,用于去除掩模30的化学物质可以在掩模30较早已被去除的那些部分中蚀刻到第一金属化层111中。这可以使得已经存在的空腔或沟槽40扩大以及新的空腔或沟槽40形成。因此,一旦掩模30从半导体衬底10上完全去除,空腔或沟槽40通常会在水平方向上具有大于10μm的最大宽度w40,在垂直方向z上具有大于3μm的最大深度d40。空腔或沟槽40通常布置在距导电涂层20 2mm的距离内。

22.在去除掩模30之后,不同种类的污染物可能会残留在空腔或沟槽40中。例如,用于去除掩模30的化学物质的残留物可以残留在空腔或沟槽40中,例如碱离子或其它蚀刻材料。当半导体本体22随后被安装到半导体衬底10而使得导电涂层20和导电连接层21布置在半导体本体22与半导体衬底10之间时,污染物会与半导体衬底10的不同部件的材料反应,例如与导电涂层20的材料反应。例如,这可能使得第一金属化层111发生不希望的快速氧化,这可能会大大缩短半导体衬底配置结构的寿命。

23.为了减少或甚至防止不希望的空腔或沟槽40的形成,将掩模30均匀地施加到半导体衬底10。根据另一个示例,掩模的靠近其边缘的厚度甚至大于其远离边缘的厚度。在图3a中示意性地示出了具有均匀厚度的掩模30。换言之,掩模30在垂直方向z上具有基本上均匀的厚度。特别地,掩模30的靠近其边缘的厚度d30可以与掩模30的在更远离其边缘的区域中的厚度d32相同。根据另一个示例,掩模30靠近其边缘的厚度d30可以甚至大于掩模30在更远离其边缘的区域中的厚度d32。掩模30的边缘区域可以是布置在距掩模30的边缘例如2mm或4mm内的区域。换言之,边缘区域在水平方向(例如,第一水平方向x)上的宽度w30可以是至少2mm或至少4mm。例如,半导体衬底10的顶表面与掩模30的边缘之间所形成的角度α可以在90

°

至130

°

之间。图3b和3c中的形成导电涂层20和去除掩模30的后续步骤与上面结合图2b和2c所描述的步骤相似。所得的导电涂层20可以在垂直方向z上具有至少300nm至1000nm的厚度d1。由于掩模30的厚度d30、d32是均匀的,因此在剥离过程期间掩模30被均匀地去除。因此,邻近导电涂层20不会形成空腔或沟槽。这同样适用于d30>d32的情况。在那些情况下,邻近导电涂层20也不会形成空腔或沟槽。

24.在图3d中示意性地示出了所得的半导体衬底配置结构。可以看出,在距导电涂层20的外周的第一距离x1内没有空腔或沟槽。例如,第一距离x1可以是2mm。然而,由于工艺不规则或异常,仍然可能在第一距离x1内形成小的空腔或沟槽40(在图3d中未具体示出)。然而,这样的小的沟槽或空腔40比上面结合图2a

‑

2c描述的空腔或沟槽40小得多。特别地,在距导电涂层20的外周的第一距离x1内的任何空腔或沟槽40在水平方向x、y或水平平面上的最大宽度w40小于10μm,在垂直方向z上的最大深度d40小于3μm。这样的小的空腔或沟槽40可以存储更少或甚至没有污染物。因此,大大降低了在随后的过程期间快速氧化的风险。

25.如果掩模30的外边缘没有均匀地形成,也可能出现问题。这在图4a

‑

4b的俯视图中示例性地示出。在图4a中,示意性地示出了布置在半导体衬底10上、特别是在第一金属化层111上的掩模30。通过掩模30中的开口,第一金属化层111是可见的。然而,掩模30的边缘是

不均匀的。换言之,掩模的边缘未形成直线。当形成导电涂层20并去除掩模30时,这也会导致不希望的空腔或沟槽40。图4b示出了半导体衬底配置结构的最终状态。导电涂层20布置在半导体衬底10上,并且掩模30已经从半导体衬底10上去除。换言之,第一金属化层111在图4a中被掩模30覆盖的那些区域在图4b中的最终状态中是可见的,这类似于图3a和3d的配置结构。在第一金属化层111中存在多个空腔或沟槽40。

26.另一方面,如果掩模30的边缘均匀地形成,如图5a中示意性地所示,则如图5b中所示,在第一金属化层111中不会形成空腔或沟槽40或仅形成小的空腔或沟槽40。小的空腔或沟槽40也是指距导电涂层20的外周的第一距离x1内的空腔或沟槽40在水平方向x、y或水平平面上具有小于10μm的最大宽度w40,在垂直方向z上具有小于3μm的最大深度d40。如果掩模30的边缘均匀地形成,则可以防止掩模30的潜在的欠蚀刻。如果例如在图4a

‑

4b的示例中发生这种欠蚀刻,则第一金属化层111可能在欠蚀刻的区域中被破坏,这会导致不希望的空腔和沟槽40。

27.如果在将掩模30施加到半导体衬底10上时形成掩模的材料的粘度被选择为足够高以防止材料的不希望的污迹或玷污,则掩模30可以形成为具有均匀的厚度。粘度与掩模30的材料和在将其施加到半导体衬底10上时的材料的温度有关。在将材料施加到半导体衬底10之后,可以通过去除液体的至少一部分来使其硬化到一定程度,以便掩模30在形成导电涂层20的同时保持固体。掩模30的材料也可以选择为具有改进的粘附特性,以便防止在形成导电涂层20的过程期间掩模30的不希望的剥离。更进一步地,掩模30的材料可以被选择为具有与掩模30的剥离工艺(掩模的去除)有关的改进的性能。换言之,掩模可能易于去除。此外,可以改进形成掩模30的工艺的工艺参数,以便保证掩模30的厚度均匀且边缘均匀。换言之,可以针对用于形成掩模30的材料来优化诸如工艺温度的工艺参数。

28.一种用于形成半导体衬底配置结构的方法可以包括将掩模30形成在半导体衬底10上,所述半导体衬底10包括介电绝缘层11和布置在介电绝缘层11上的第一金属化层111。掩膜30包括至少一个开口。换言之,形成掩模30包括仅在第一金属化层111的一些区域上形成掩模30,而第一金属化层111的至少一个区域保持没有掩模30。第一金属化层111布置在掩模30与介电绝缘层之间。形成掩模30包括将基本上均匀的材料层施加在第一金属化层111上。替代性地,掩模30的材料可以被施加到第一金属化层111,使得与掩模30的边缘相邻的厚度d30大于掩模30的更远离边缘的厚度d32。可选地,然后可以在随后的步骤中使材料硬化(例如,通过执行干燥或加热过程从材料中去除液体)。然后在第一金属化层111上形成至少一个导电涂层20。在第一金属化层111的未被掩模30覆盖的那些区域上形成至少一个导电涂层20。一旦形成了至少一个导电涂层20,掩模30就在随后的步骤中从半导体衬底10上去除。这获得了包括半导体衬底10的半导体衬底配置结构,所述半导体衬底10包括介电绝缘层11和附接到介电绝缘层11的第一金属化层111,其中,第一金属化层111在垂直方向z上布置在介电绝缘层11上。所得的半导体衬底配置结构还包括在垂直方向z上布置在第一金属化层111上的导电涂层20,使得第一金属化层111布置在导电涂层20与介电绝缘层11之间。在距导电涂层20的外周2mm的距离内的水平平面x

‑

y中,第一金属化层111不包括任何空腔或沟槽40,或者仅包括在水平方向x、y上具有小于10μm的宽度w40和在垂直方向z上具有小于3μm的深度d40的空腔或沟槽40。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1