封装结构及其制作方法与流程

1.本发明涉及一种半导体结构及其制作方法,尤其涉及一种封装结构及其制作方法。

背景技术:

2.近年来,高性能计算(high-performance computing;hpc)变得更加流行,且广泛用于先进网路和伺服器应用,特别是用于需要高数据速率、逐渐增加的频宽以及逐渐降低的时延的人工智慧(artificial intelligence;ai)相关的产品。其中,人们对于包含高性能计算(hpc)的封装结构所采用的高密度(high density,hd)封装载板的期待及要求也越来越多,例如是对金属层的线宽和线距要求要在次微米至10微米之间,而重配置线路层的介电层厚度要在1微米至5微米之间。然而,目前的增层封装基板(build-up package substrate)无法满足上述的要求。

技术实现要素:

3.本发明是针对一种封装结构及其制作方法,其可解决前先技术的问题。

4.根据本发明的实施例,封装结构包括至少一第一重配置线路层、至少一第二重配置线路层、芯片接垫、焊球接垫、芯片、焊球以及封装胶体。第一重配置线路层包括第一介电层以及第一重配置线路。第一介电层包括彼此连通的第一开口与第二开口。第二开口的孔径大于第一开口的孔径,而第一重配置线路填满第一开口与第二开口。第一介电层的第一上表面切齐于第一重配置线路的第一表面。第二重配置线路层配置于第一重配置线路层上。第二重配置线路层包括第二介电层、第三介电层以及第二重配置线路。第二介电层包括第三开口,而第二重配置线路配置于第二介电层上、延伸至第三开口内且与第一重配置线路层电性连接。第三介电层覆盖第二介电层与第二重配置线路且填满第三开口。第三介电层的第二上表面切齐于第二重配置线路的第二表面。芯片接垫配置于第一介电层相对于第一上表面的第一下表面上,且芯片接垫电性连接第一重配置线路。焊球接垫配置于第三介电层的第二上表面上,且焊球接垫电性连接第二重配置线路。芯片配置于芯片接垫上且电性连接芯片接垫。焊球配置于焊球接垫上且电性连接焊球接垫。封装胶体配置于第一介电层的第一下表面上,且至少覆盖芯片与芯片接垫。

5.在根据本发明的实施例的封装结构中,上述的第一介电层的材质包括二氧化硅。

6.在根据本发明的实施例的封装结构中,上述的第二介电层的材质包括光敏介电材料。

7.在根据本发明的实施例的封装结构中,上述的第一重配置线路具有次微米(submicron)的金属线宽与线距。

8.在根据本发明的实施例的封装结构中,上述的第二重配置线路具有大于等于1微米且小于等于10微米的金属线宽与线距。

9.在根据本发明的实施例的封装结构中,上述的第一重配置线路与第二重配置线路

分别包括种子层以及配置于种子层上的金属层。

10.在根据本发明的实施例的封装结构中,上述的芯片接垫与焊球接垫分别包括种子层以及配置于种子层上的金属层。

11.在根据本发明的实施例的封装结构中,上述的第一重配置线路层的厚度小于第二重配置线路层的厚度。

12.在根据本发明的实施例的封装结构中,上述的封装结构还包括保护层,配置于第三介电层的第二上表面上。保护层的第三表面切齐于焊球接垫的第四表面。

13.在根据本发明的实施例的封装结构中,上述的封装结构还包括铜柱以及焊料。铜柱配置于芯片上,而焊料配置于铜柱上。芯片通过铜柱上的焊料而与芯片接垫电性连接。

14.根据本发明的实施例,封装结构的制作方法包括以下步骤。形成至少一第一重配置线路层于第一载板上。第一重配置线路层包括第一介电层以及第一重配置线路。第一介电层包括彼此连通的第一开口与第二开口。第二开口的孔径大于第一开口的孔径,而第一重配置线路填满第一开口与第二开口。第一介电层的第一上表面切齐于第一重配置线路的第一表面。形成至少一第二重配置线路层于第一重配置线路层上。第二重配置线路层包括第二介电层、第三介电层以及第二重配置线路。第二介电层包括第三开口,而第二重配置线路配置于第二介电层上、延伸至第三开口内且与第一重配置线路层电性连接。第三介电层覆盖第二介电层与第二重配置线路且填满第三开口。第三介电层的第二上表面切齐于第二重配置线路的第二表面。形成焊球接垫于第三介电层的第二上表面上,且焊球接垫电性连接第二重配置线路。提供第二载板于焊球接垫上,且移除第一载板而暴露出第一介电层相对于第一上表面的第一下表面。形成芯片接垫于第一介电层的第一下表面上,且芯片接垫电性连接第一重配置线路。配置芯片于芯片接垫上且电性连接芯片接垫。形成封装胶体于第一介电层的第一下表面上。封装胶体至少覆盖芯片与芯片接垫。移除第二载板,以暴露出焊球接垫。形成焊球于焊球接垫上且电性连接焊球接垫。

15.在根据本发明的实施例的封装结构的制作方法中,上述形成第一重配置线路层于第一载板上的步骤,包括:以电浆化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)程序形成第一介电层于第一载板上。对第一介电层进行反应性离子蚀刻(reactive ion etching,rie)程序,以形成彼此连通的第一开口与第二开口。形成种子材料于第一介电层的第一上表面、第一开口的内壁与第二开口的内壁。形成金属材料于种子材料上。金属材料覆盖种子材料且填满第一开口与第二开口。对金属材料及种子材料进行研磨程序,以暴露出第一介电层的第一上表面,且形成位于第一开口与第二开口内的金属层及种子层。金属层与种子层定义出第一重配置线路。

16.在根据本发明的实施例的封装结构的制作方法中,上述形成第二重配置线路层于第一重配置线路层上的步骤,包括:形成第二介电层于第一重配置线路层上。第二介电层覆盖第一介电层的第一上表面,且包括暴露出第一重配置线路的部分第一表面的第三开口。形成种子材料于第二介电层及第三开口的内壁上。形成图案化光致抗蚀剂层于种子材料上,其中图案化光致抗蚀剂层暴露出部分种子材料。以图案化光致抗蚀剂层为电镀罩幕,电化学沉积(electro-chemical deposition,ecd)金属材料于图案化光致抗蚀剂层所暴露出的种子材料上。移除图案化光致抗蚀剂层及其下方的种子材料,以形成金属层及其下方的种子层而定义出第二重配置线路。形成第三介电层于第二介电层上且覆盖第二重配置线

路。

17.在根据本发明的实施例的封装结构的制作方法中,上述形成焊球接垫于第三介电层的第二上表面上的步骤,包括:形成第四介电层于第二重配置线路层上。第四介电层覆盖第三介电层的第二上表面,且包括暴露出第二重配置线路的部分第二表面的第四开口。形成种子材料于第四介电层及第四开口的内壁上。形成图案化光致抗蚀剂层于种子材料上,其中图案化光致抗蚀剂层暴露出部分种子材料。以图案化光致抗蚀剂层为电镀罩幕,电镀金属材料于图案化光致抗蚀剂层所暴露出的种子材料上。移除图案化光致抗蚀剂层及其下方的种子材料,以形成金属层及其下方的种子层而定义出焊球接垫。

18.在根据本发明的实施例的封装结构的制作方法中,上述的封装结构的制作方法还包括:形成保护层于第四介电层上,其中保护层的第三表面切齐于焊球接垫的第四表面。

19.在根据本发明的实施例的封装结构的制作方法中,上述的形成芯片接垫于第一介电层的第一下表面上的步骤,包括:对第一介电层进行反应性离子蚀刻程序,以形成暴露出部分第一重配置线路的开口。形成种子材料于第一介电层及开口的内壁上。形成图案化光致抗蚀剂层于种子材料上,其中图案化光致抗蚀剂层暴露出部分种子材料。以图案化光致抗蚀剂层为电镀罩幕,电镀金属材料于图案化光致抗蚀剂层所暴露出的种子材料上。移除图案化光致抗蚀剂层及其下方的种子材料,以形成金属层及其下方的种子层而定义出芯片接垫。

20.在根据本发明的实施例的封装结构的制作方法中,上述的封装结构的制作方法还包括:于配置芯片于芯片接垫上之前,形成铜柱于芯片上;以及形成焊料于铜柱上。芯片通过铜柱上的焊料而与芯片接垫电性连接。

21.在根据本发明的实施例的封装结构的制作方法中,上述的第一介电层的材质包括二氧化硅,而第二介电层的材质包括光敏介电材料。

22.在根据本发明的实施例的封装结构的制作方法中,上述的第一重配置线路具有次微米的金属线宽与线距。

23.在根据本发明的实施例的封装结构的制作方法中,上述的第二重配置线路具有大于等于1微米且小于等于10微米的金属线宽与线距。

24.基于上述,在本发明的封装结构及其制作方法中,是形成二种结构型态完全不同的第一重配置线路层及第二重配置线路层,接着,再配置芯片及进行封装程序,之后才移除第二载板且进行焊球的设置。其中,第一重配置线路层的第一重配置线路是填满第一介电层彼此连通且不同孔径的第一开口与第二开口,而第一介电层的第一上表面切齐于第一重配置线路的第一表面。第二重配置线路层的第二重配置线路是配置于第二介电层上、延伸至第二介电层的第三开口内且与第一重配置线路层电性连接。第三介电层覆盖第二介电层与第二重配置线路且填满第三开口,其中第三介电层的第二上表面切齐于第二重配置线路的第二表面。相较于现有的增层封装基板的制作,本发明的封装结构可形成具有二种不同结构型态的重配置线路层,可满足人们对于高密度封装结构的期待及要求。

附图说明

25.图1a至图1z是依照本发明的一实施例的一种封装结构的制作方法的剖面示意图;

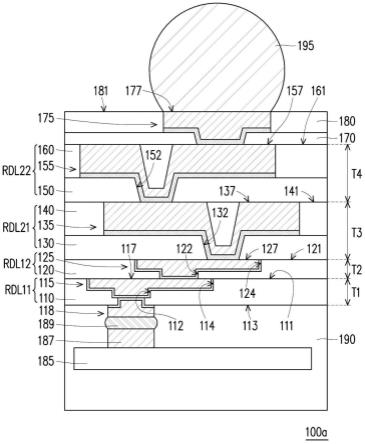

26.图2是依照本发明的另一实施例的一种封装结构的剖面示意图。

27.附图标记说明

28.10:第一载板;

29.12、22:基材;

30.14、24:牺牲层;

31.20:第二载板;

32.100a、100b:封装结构;

33.110、120:第一介电层;

34.111、121:第一上表面;

35.112、122:第一开口;

36.113:第一下表面;

37.114、124:第二开口;

38.115、125:第一重配置线路;

39.116:开口;

40.118:芯片接垫;

41.117、127:第一表面;

42.130、150:第二介电层;

43.132、152:第三开口;

44.135、155:第二重配置线路;

45.137、157:第二表面;

46.140、160:第三介电层;

47.141、161:第二上表面;

48.170:第四介电层;

49.171:表面;

50.172:第四开口;

51.175:焊球接垫;

52.177:第四表面;

53.180:保护层;

54.181:第三表面;

55.185:芯片;

56.187:铜柱;

57.189:焊料;

58.190:封装胶体;

59.195:焊球;

60.c1:凹槽;

61.m1、m2:金属材料;

62.m11、m22、m33、m44:金属层;

63.o11、o12:开口;

64.p1:光致抗蚀剂层;

65.p2、p3、p4:图案化光致抗蚀剂层;

66.rdl11、rdl12:第一重配置线路层;

67.rdl21、rdl22:第二重配置线路层;

68.s1、s2、s3、s4:种子材料;

69.s11、s22、s33、s44:种子层;

70.t1、t2、t3、t4:厚度。

具体实施方式

71.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

72.图1a至图1z是依照本发明的一实施例的一种封装结构的制作方法的剖面示意图。关于本实施例的封装结构的制作方法,首先,请先参考图1a,提供第一载板10,其中第一载板10包括基材12以及配置于基材12上的牺牲层14。此处,基材12例如是没有线路的暂时玻璃晶圆或面板,而牺牲层14例如是适合于激光解板(laser debond)或热解板(thermal debond)的材质。

73.接着,请参考图1b,以电浆化学气相沉积(pecvd)程序形成第一介电层110于第一载板10上的牺牲层14。此处,第一介电层110的材质例如是二氧化硅,且第一介电层110的厚度例如是1微米。

74.接着,请参考图1c,形成光致抗蚀剂层p1于第一介电层110上,其中光致抗蚀剂层p1完全覆盖第一介电层110的第一上表面111。

75.接着,请参考图1d,对光致抗蚀剂层p1进行第一次黄光微影程序,而形成开口o11,其中开口o11暴露出第一介电层110的第一上表面111。

76.接着,请参考图1e,对第一介电层110进行第一次反应性离子蚀刻(rie)程序,以形成第一开口112。此处,第一开口112没有贯穿第一介电层110,且第一开口112的孔径等于开口o11的孔径。

77.接着,请参考图1f,对光致抗蚀剂层p1进行第二次黄光微影程序,而形成开口o12,其中开口o12暴露出第一开口112,且开口o12的孔径大于第一开口112的孔径。

78.紧接着,请再参考图1f,对第一介电层110进行第二次反应性离子蚀刻(rie)程序,以形成连通第一开口112的第二开口114。此处,第一开口112与第二开口114彼此连通,且第二开口114的孔径大于第一开口112的孔径。第一开口112位于第二开口114与第一载板10之间,且第一开口112与第二开口114形成阶梯状结构。

79.接着,请同时参考图1f与图1g,移除光致抗蚀剂层p1,而暴露出第一介电层110的第一上表面111。

80.接着,请参考图1g,形成种子材料s1于第一介电层110的第一上表面111、第一开口112的内壁与第二开口114的内壁。此处,种子材料s1的材质例如是钛铜,但不以此为限。

81.接着,请参考图1h,形成金属材料m1于种子材料s1上,其中金属材料m1覆盖种子材料s1且填满第一开口112与第二开口114。此处,金属材料m1例如是铜,但不以此为限。

82.接着,请同时参考图1h与图1i,对金属材料m1及种子材料s1进行研磨程序,以暴露出第一介电层110的第一上表面111,且形成位于第一开口112与第二开口114内的金属层m11及种子层s11。此处,金属层m11与种子层s11定义出第一重配置线路115。至此,已形成第

一重配置线路层rdl11于第一载板10上。

83.详细来说,本实施例的第一重配置线路层rdl11包括第一介电层110以及第一重配置线路115。第一介电层110包括彼此连通的第一开口112与第二开口114,其中第二开口114的孔径大于第一开口112的孔径。第一重配置线路115填满第一开口112与第二开口114,且第一介电层110的第一上表面111切齐于第一重配置线路115的第一表面117。此处,是通过铜大马士革(cu damascene)制作流程加上研磨程序来形成第一重配置线路115,其中第一重配置线路115为阶梯状结构,且第一重配置线路115具有次微米的金属线宽与线距。

84.接着,请参考图1j,可选择性地,重复图1b至图1i的步骤,形成第一重配置线路层rdl12于第一重配线路层rdl11上。此处,第一重配置线路层rdl12包括第一介电层120以及第一重配置线路125,其中第一介电层120的材质为二氧化硅,而第一重配置线路125具有次微米的金属线宽与线距,且第一重配置线路125与第一重配置线路115电性连接。

85.接着,请参考图1k,以涂布方式形成第二介电层130于第一重配置线路层rdl12上。第二介电层130覆盖第一介电层120的第一上表面121,且包括暴露出第一重配置线路125的部分第一表面127的第三开口132。此处,第二介电层130的材质例如是光敏介电材料,其中第二介电层130的厚度例如是5微米。

86.接着,请参考图1l,形成种子材料s2于第二介电层130及第三开口132的内壁上,其中种子材料s2直接接触第三开口132所暴露出的第一重配置线路125的第一表面127。此处,形成重子材料层s2的方式例如是物理气相沉积法(physical vapor deposition,pvd)。

87.接着,请参考图1m,形成图案化光致抗蚀剂层p2于种子材料s2上,其中图案化光致抗蚀剂层p2暴露出部分种子材料s2。

88.接着,请参考图1n,以图案化光致抗蚀剂层p2为电镀罩幕,电化学沉积(ecd)金属材料m2于图案化光致抗蚀剂层p2所暴露出的种子材料s2上。此处,金属材料m2未填满第三开口132而具有凹槽c1。

89.接着,请同时参考图1n与图1o,移除图案化光致抗蚀剂层p2及其下方的种子材料s2,以形成金属层m22及其下方的种子层s22而定义出第二重配置线路135。此处,第二重配置线路135是以物理气相沉积法(pvd)及电化学沉积(ecd)来制作,其中第二重配置线路具有大于等于1微米且小于等于10微米的金属线宽与线距。

90.接着,请参考图1p,形成第三介电层140于第二介电层130上且覆盖第二重配置线路135。此处,第三介电层140的材质例如是光敏介电材料,其中第三介电层140的厚度例如是5微米。至此,已形成第二重配置线路层rdl21于第一重配置线路层rdl12上。

91.详细来说,在本实施例中,第二重配置线路层rdl21包括第二介电层130、第三介电层140以及第二重配置线路135。第二介电层130包括第三开口132,而第二重配置线路135配置于第二介电层130上、延伸至第三开口132内且与第一重配置线路层125电性连接。第三介电层140覆盖第二介电层130与第二重配置线路135且填满第三开口132及凹槽c1。第三介电层140的第二上表面141切齐于第二重配置线路135的第二表面137。

92.接着,请再参考图1p,可选择性地,重复图1b至图1p的步骤,形成第二重配置线路层rdl22于第二重配线路层rdl21上。此处,第二重配置线路层rdl22包括第二介电层150、第三介电层160以及第二重配置线路155,其中第二介电层150的材质与第三介电层160的材质皆分别例如是光敏介电材料,而第二重配置线路155具有大于等于1微米且小于等于10微米

的金属线宽与线距,且第二重配置线路135与第二重配置线路155电性连接。

93.接着,请参考图1q,形成第四介电层170于第二重配置线路层rdl22上。第四介电层170覆盖第三介电层160的第二上表面161,且包括暴露出第二重配置线路155的部分第二表面157的第四开口172。

94.接着,请参考图1r,形成种子材料s3于第四介电层170及第四开口172的内壁上,其中种子材料s3直接接触被第四介电层170所暴露出的第二重配置线路155的第二表面157。紧接着,形成图案化光致抗蚀剂层p3于种子材料s3上,其中图案化光致抗蚀剂层p3暴露出部分种子材料s3。

95.接着,请同时参考图1r与图1s,以图案化光致抗蚀剂层p3为电镀罩幕,电镀金属材料于图案化光致抗蚀剂层p3所暴露出的种子材料s3上。紧接着,移除图案化光致抗蚀剂层p3及其下方的种子材料s3,以形成金属层m33及其下方的种子层s33而定义出焊球接垫175。至此,已形成焊球接垫175于第三介电层160的第二上表面161上,且焊球接垫175电性连接第二重配置线路155。

96.接着,请参考图1t,形成保护层180于第四介电层170上,其中保护层180的第三表面181切齐于焊球接垫175的第四表面177。

97.接着,请同时参考图1t与图1u,提供第二载板20于焊球接垫175上,且移除第一载板10而暴露出第一介电层110相对于第一上表面111的第一下表面113。此处,第二载板20包括基材22以及配置于基材22上的牺牲层24,其中牺牲层24直接接触焊球接垫175以及保护层180。此处,基材22例如是没有线路的暂时玻璃晶圆或面板,牺牲层24例如是适合于激光解板(laser debond)或热解板(thermal debond)的材质。

98.接着,请再参考图1u,对第一介电层110的第一下表面113进行反应性离子蚀刻程序,以形成暴露出部分第一重配置线路115的开口116。紧接着,形成种子材料s4于第一介电层110及开口116的内壁上。

99.接着,请参考图1v,形成图案化光致抗蚀剂层p4于种子材料s4上,其中图案化光致抗蚀剂层p4暴露出部分种子材料s4。

100.接着,请同时参考图1v与图1w,以图案化光致抗蚀剂层p4为电镀罩幕,电镀金属材料于图案化光致抗蚀剂层p4所暴露出的种子材料s4上。紧接着,移除图案化光致抗蚀剂层p4及其下方的种子材料s4,以形成金属层m44及其下方的种子层s44而定义出芯片接垫118。至此,已形成芯片接垫118于第一介电层110的第一下表面113上,且芯片接垫118电性连接第一重配置线路115。

101.接着,请参考图1x,提供芯片185,并于芯片185上形成铜柱187。紧接着,形成焊料189于铜柱187上,其中芯片185通过铜柱187上的焊料189而与芯片接垫118电性连接。

102.接着,请参考图1y,形成封装胶体190于第一介电层110的第一下表面113上。封装胶体190覆盖芯片185、铜柱187、焊料189及芯片接垫118。

103.之后,请同时参考图1y以及图1z,移除第二载板20,以暴露出焊球接垫175。最后,请参考图1z,形成焊球195于焊球接垫175上且电性连接焊球接垫175。至此,已完成封装结构100a的制作。

104.在结构上,请再参考图1z,在本实施例中,封装结构100a包括至少一第一重配置线路层(示意地示出两个第一重配置线路层rdl11、rdl12)、至少一第二重配置线路层(示意地

示出两个第二重配置线路层rdl21、rdl22)、芯片接垫118、焊球接垫175、芯片185、焊球195以及封装胶体190。第一重配置线路层rdl11、rdl12包括第一介电层110、120以及第一重配置线路115、125。第一介电层110、120包括彼此连通的第一开口112、122与第二开口114、124。第二开口114、124的孔径大于第一开口112、122的孔径,而第一重配置线路115、125填满第一开口112、122与第二开口114、124。第一介电层110、120的第一上表面111、121切齐于第一重配置线路115、125的第一表面117、127。

105.再者,本实施例的第二重配置线路层rdl21、rdl22依序配置于第一重配置线路层rdl12上。第二重配置线路层rdl21、rdl22包括第二介电层130、150、第三介电层140、160以及第二重配置线路135、155。第二介电层130、150包括第三开口132、152,而第二重配置线路135、155配置于第二介电层130、50上且延伸至第三开口132、152内。第二重配置线路135与第一重配置线路层rdl12的第一重配置线路125电性连接。第三介电层140、160覆盖第二介电层130、150与第二重配置线路135、155且填满第三开口132、152。第三介电层140、160的第二上表面141、161切齐于第二重配置线路135、155的第二表面137、157。

106.请再参考图1z,本实施例的芯片接垫118配置于第一介电层110相对于第一上表面111的第一下表面113上,且芯片接垫118电性连接第一重配置线路115。焊球接垫175配置于第三介电层160的第二上表面161上,且焊球接垫175电性连接第二重配置线路155。芯片185配置于芯片接垫118上且电性连接芯片接垫118。焊球195配置于焊球接垫175上且电性连接焊球接垫175。封装胶体190配置于第一介电层110的第一下表面113上,且至少覆盖芯片185与芯片接垫118。此处,第一重配置线路层rld11、rdl12的厚度t1、t2小于第二重配置线路层rdl21、rdl22的厚度t3、t4。

107.再者,本实施例的封装结构100还包括第四介电层170及位于其上的保护层180。第四介电层170覆盖第三介电层160的第二上表面161与第二重配置线路155的第二表面157,而焊球接垫175位于第四介电层170上。保护层180配置于第三介电层160的第二上表面161上,其中第四介电层170位于保护层180与第三介电层160之间。保护层180的第三表面181切齐于焊球接垫175的第四表面177。

108.此外,本实施例的封装结构100还包括铜柱187以及焊料189。铜柱187配置于芯片185上,而焊料189配置于铜柱187上,其中芯片185通过铜柱187上的焊料189而与芯片接垫118电性连接。封装胶体190覆盖芯片185、铜柱187、焊料189及芯片接垫118,而芯片185通过铜柱187及焊料189与芯片接垫118电性连接。

109.在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

110.图2是依照本发明的另一实施例的一种封装结构的剖面示意图。请同时参考图1z与图2,本实施例的封装结构100b与上述的封装结构100a相似,两者的差异在于:在本实施例中,无设置保护层180。意即,焊球接垫175为突出于第四介电层170的表面171的结构。

111.综上所述,在本发明的封装结构及其制作方法中,是形成二种结构型态完全不同的第一重配置线路层及第二重配置线路层。其中,第一重配置线路层的第一重配置线路是通过铜大马士革(cu damascene)制作流程加上研磨程序而形成,而第一介电层是采用二氧化硅。第二重配置线路层的第二重配置线路是采用物理气相沉积法(pvd)及电化学沉积

(ecd)来制作,而第二介电层及第三介电层则是采用光敏介电材料。借此,第一重配置线路层的第一重配置线路的金属线宽与线距可为次微米,而第二第二重配置线路层的第二重配置线路的金属线宽与线距可大于等于1微米且小于等于10微米。相较于现有的增层封装基板的制作,本发明的封装结构可形成具有二种不同结构型态的重配置线路层,可满足人们对于高密度封装结构的期待及要求。

112.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1