半导体器件的制造方法与流程

1.本发明涉及一种集成电路器件的制造方法,尤其涉及一种半导体器件的制造方法。

背景技术:

2.半导体器件在制造的过程中通常会经过多道的刻蚀工艺。然而,若是所采用的刻蚀剂对于层与层之间的刻蚀选择比不足,常常造成刻蚀损坏,而造成器件的电性问题。

技术实现要素:

3.本发明是针对一种半导体器件的制造方法可以减少或避免在进行刻蚀的过程中对器件有源区造成的损坏。

4.根据本发明的实施例,一种半导体器件的制造方法,包括:提供衬底,所述衬底包括单元区与周边区,所述周边区包括第一区与第二区;在所述单元区与所述周边区形成穿隧氧化层以及浮置导体层以及硬掩模堆叠层;以硬掩模堆叠层为掩模,移除所述第一区与所述第二区的所述浮置导体层与所述穿隧氧化层;在所述周边区的所述第一区与所述第二区的所述衬底上形成第一栅介电层,并在所述单元区与所述周边区的所述第一区与所述第二区形成第一导体层以及第一硬掩模层;移除所述第一区以外的所述第一硬掩模层;以所述第一硬掩模层为掩模,移除所述第一区以外的所述第一导体层以及所述第一栅介电层;移除所述第一硬掩模层与所述第一导体层;以及于所述第一区形成第一栅极导体层。

5.根据本发明的实施例,一种半导体器件的制造方法,包括:提供衬底,所述衬底包括单元区与周边区,所述周边区包括第一区与第二区;在所述周边区的所述第一区与所述第二区的所述衬底上形成第一栅介电层,并在所述单元区与所述周边区的所述第一区与所述第二区形成第一导体层以及第一硬掩模层;在所述第一区的所述第一硬掩模层上形成第一掩模层;以所述第一掩模层为掩模,移除所述第一区以外的所述第一硬掩模层;移除所述第一掩模层;以所述第一硬掩模层为掩模,进行湿式刻蚀工艺,以移除所述第一区以外的所述第一导体层以及所述第一栅介电层;移除所述第一硬掩模层与所述第一导体层;于所述第二区形成第一栅介电层;以及于所述第一区形成第一栅极导体层,并于所述第二区形成第二栅极导体层。

6.基于上述,在本发明实施例中,先在周边电路区的各区形成阀值电压较小的晶体管的薄的栅介电层,再移除阀值电压较大的晶体管的区域上的薄的栅介电层。由于阀值电压较小的晶体管的栅介电层的厚度较薄,因此在移除薄的栅介电层的湿式刻蚀工艺的时间较短,较不易造成器件的电性问题。此外,在本发明实施例中,在阀值电压较大的晶体管的区域上的导体层是通过湿式刻蚀工艺移除,因此可以避免器件有源区遭受到刻蚀的破坏。

附图说明

7.图1a至图1n是依照本发明的实施例的一种半导体器件的制造方法的剖面示意图;

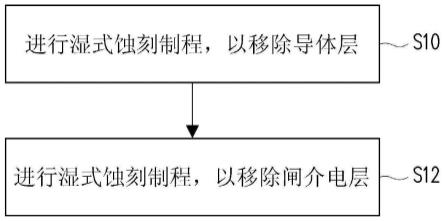

8.图2依照本发明的实施例的一种半导体器件的制造方法的中间流程图。

具体实施方式

9.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

10.请参照图1a,提供衬底100。衬底100可以是半导体或是半导体化合物,例如n型或p型的硅衬底、三五族半导体衬底或是硅化锗。衬底100也可以是绝缘层上覆硅(silicon on insulator,soi)。衬底100包括单元区r1与周边区r2。周边区r2包括区域a1、a2与a3,用以形成具有不同阀值电压的晶体管。区域a2的晶体管的阀值电压高于区域a1的晶体管的阀值电压,且低于区域a3的晶体管的阀值电压。举例来说,区域a2的晶体管具有低阀值电压;区域a1的晶体管具有超低阀值电压;区域a3的晶体管具有高阀值电压。在一些实施例中,区域a1的晶体管的阀值电压小于或等于1.8伏特;区域a2的晶体管的阀值电压约为3伏特;区域a3的晶体管的阀值电压约为5伏特至vpp。

11.在衬底100上形成穿隧氧化层102与导体层104。穿隧氧化层102的材料例如是氧化硅。导体层104后续作为浮置栅极,因此又可称为浮置导体层。导体层104的材料例如是掺杂多晶硅。穿隧氧化层102的厚度例如是8nm至11nm。导体层114的厚度例如是50nm至90nm。

12.接着,在衬底100中形成隔离结构101,以在单元区r1以及周边区r2的区域a1、a2与a3界定出多个有源区。隔离结构101可以例如是包括旋涂式玻璃层101a与高密度等离子体氧化硅层101b。

13.请参照图1b,在衬底100上形成硬掩模层106,以覆盖在单元区r1的导体层104以及隔离结构101上。在一实施例中,硬掩模层106包括氧化硅层108与氮化硅层110,因此可称为硬掩模堆叠层。硬掩模层106可以通过沉积与光刻刻蚀的工艺形成。

14.请参照图1c,以硬掩模层106为掩模,移除周边区r2的导体层104以及氧化硅层102,以裸露出区域a1、a2以及a3的衬底100的表面。导体层104可以采用反应性离子刻蚀工艺来移除。氧化硅层102可以通过湿式刻蚀工艺(例如是以稀释的氢氟酸作为刻蚀剂)来移除。在一些实施例中,周边区r2的隔离结构101的高密度等离子体氧化硅层101b也在移除氧化硅层108的过程中被移除。

15.请参照图1d,在周边区r2的衬底100上形成栅介电层112,再于单元区r1的硬掩模层106上以及周边区r2的栅介电层112上形成导体层114与硬掩模层116。栅介电层112的材料例如是氧化硅,形成的方法例如是热氧化工艺。通过热氧化工艺可以使得周边区r2所裸露的衬底100氧化而形成氧化硅,而单元区r1的氮化硅层110则无法被氧化,因此在氮化硅层110上并未形成氧化硅层。导体层114的材料例如是掺杂多晶硅。硬掩模层116的材料例如是氮化硅。导体层114与硬掩模层116的形成方法例如是化学气相沉积法。栅介电层112的厚度例如是小于穿隧氧化层102的厚度。栅介电层112的厚度例如是1nm至3nm。导体层114的厚度例如是10nm至20nm。硬掩模层116的厚度例如是10nm至20nm。

16.之后,通过光刻工艺,在衬底100上形成掩模层(例如是图案化的光刻胶层)120,以覆盖周边区r2的区域a1的硬掩模层116。

17.请参照图1e,以周边区r2的区域a1的掩模层120为掩模,进行刻蚀工艺(例如是反应性离子刻蚀工艺),以移除周边区r2的区域a1以外的硬掩模层116。

18.请参照图1f,移除掩模层120。之后,以周边区r2的区域a1的硬掩模层116作为掩模,进行刻蚀工艺,以移除周边区r2的区域a1以外的导体层114以及栅介电层112,裸露出单元区r1的硬掩模层106以及周边区r2的区域a2以及区域a3的衬底100的表面。

19.请参照图1f与图2,移除导体层114的方法例如是以具有高刻蚀选择比的刻蚀剂进行湿式刻蚀工艺(步骤s10)。刻蚀剂可以是含有四甲基氢氧化铵(tetra-methyl ammonium hydroxide,tmah)的溶液,例如是由mallinckrodt baker股份有限公司的j.t.baker制造的商业清洗配方rezi38。栅介电层112可以采用湿式刻蚀工艺(例如是稀释的氢氟酸溶液,步骤s12)来移除。由于栅介电层112的厚度非常薄,须移除的栅介电层112的量很少,所需的湿式刻蚀工艺短且刻蚀剂有高刻蚀选择比,因此可以避免器件有源区被刻蚀破坏。

20.请参照图1g,在周边区r2的区域a2与a3的衬底100上形成栅介电层122,再于单元区r1的硬掩模层106上、周边区r2的区域a1上的硬掩模层116上、以及周边区r2的区域a2与区域a3上的栅介电层122上形成导体层124与硬掩模层126。栅介电层122的材料例如是氧化硅,形成的方法例如是热氧化工艺。通过热氧化工艺可以使得周边区r2的区域a2与a3所裸露的衬底100氧化而形成氧化硅,而单元区r1的氮化硅层110以及周边区r2的区域a1的硬掩模层116则无法被氧化,因此在氮化硅层110以及硬掩模层116上并未形成氧化硅层。导体层124的材料例如是掺杂多晶硅。硬掩模层126的材料例如是氮化硅。导体层124与硬掩模层126的形成方法例如是化学气相沉积法。栅介电层122的厚度例如是5纳米(nm)至7nm。导体层124的厚度例如是10nm至20nm。硬掩模层126的厚度例如是10nm至20nm。

21.之后,在衬底100上形成掩模层(例如是图案化的光刻胶层)130,以覆盖周边区r2的区域a2的硬掩模层126。

22.请参照图1h,以周边区r2的区域a2的掩模层130为掩模,进行刻蚀工艺(例如是反应性离子刻蚀工艺),以移除周边区r2的区域a2以外的硬掩模层126。

23.请参照图1i与图2,移除掩模层130。之后,以区域a2的硬掩模层126作为掩模,进行刻蚀工艺(步骤s10与s12),以移除周边区r2的区域a2以外的导体层124以及栅介电层122,裸露出单元区r1的硬掩模层106以及周边区r2的区域a1的硬掩模层116以及区域a3的衬底100的表面。

24.移除导体层124的方法例如是以具有高刻蚀选择比的刻蚀剂进行湿式刻蚀工艺。刻蚀剂可以是含有四甲基氢氧化铵的溶液,例如是由mallinckrodt baker股份有限公司的j.t.baker制造的商业清洗配方rezi38。栅介电层122可以采用湿式刻蚀工艺(例如是稀释的氢氟酸溶液)来移除。由于栅介电层122的厚度非常薄,须移除的栅介电层122的量很少,所需的湿式刻蚀工艺短且刻蚀剂有高刻蚀选择比,因此可以避免器件有源区被刻蚀破坏。

25.请参照图1j,在周边区r2的区域a3的衬底100上形成栅介电层132,再于单元区r1的硬掩模层106上、周边区r2的区域a1上的硬掩模层116上、周边区r2的区域a2上的硬掩模层126上以及周边区r2的区域a3上的栅介电层132上形成导体层134与硬掩模层136。栅介电层132的材料例如是氧化硅,形成的方法例如是热氧化工艺。通过热氧化工艺可以使得周边区r2的区域a3所裸露的衬底100氧化而形成氧化硅,而单元区r1的氮化硅层110以及周边区r2的区域a1的硬掩模层116以及区域a2的硬掩模层126则无法被氧化,因此在氮化硅层110以及硬掩模层116、126上并未形成氧化硅层。导体层134的材料例如是掺杂多晶硅。硬掩模层136的材料例如是氮化硅。导体层134与硬掩模层136的形成方法例如是化学气相沉积法。

栅介电层132的厚度例如是13nm至17nm。导体层134的厚度例如是10nm至20nm。硬掩模层136的厚度例如是10nm至20nm。

26.之后,在衬底100上形成掩模层(例如是图案化的光刻胶层)140,以覆盖单元区r1以及周边区r2的区域a3的硬掩模层136。

27.请参照图1k,以单元区r1以及周边区r2的区域a3的掩模层140为掩模,进行刻蚀工艺(例如是反应性离子刻蚀工艺),以移除单元区r1以及周边区r2的区域a3以外的硬掩模层136与导体层134。其后,移除掩模层140。

28.请参照图1l,进行刻蚀工艺,例如是反应性离子刻蚀工艺,以移除硬掩模层116、126、136,以裸露出单元区r1的硬掩模层106以及周边区r2的导体层114、124、134。

29.请参照图1m,接着,于衬底100上形成导体层144,以覆盖单元区r1的硬掩模层106以及周边区r2的栅介电层112、122、132。导体层144的材料例如是掺杂多晶硅。导体层144作为栅极,因此又可称为栅极导体层。

30.请参照图1n,移除单元区r1的导体层144与硬掩模层106。然后,移除在单元区r1中的部分的隔离结构101b,使留下的隔离结构101b的顶面低于导体层104的顶面。之后,在单元区r1中形成栅间介电层152。栅间介电层152例如是氧化硅、氮化硅或其组合。在一实施例中,栅间介电层152包括氧化硅/氮化硅/氧化硅堆叠层。之后,再于栅间介电层152上形成导体层154。导体层154作为控制栅,其材料例如是多晶硅。导体层154的形成方法例如是在衬底100的单元区r1与周边区r2形成导体材料层,然后通过光刻与刻蚀工艺,将导体材料层图案化来形成。

31.综上所述,在本发明实施例中,可以形成厚度均匀的栅介电层,避免进隔离结构的有源区的转角处的栅介电层厚度变薄的问题,因此可以避免漏电流以及电流双驼峰(current double hump)等问题。此外,本发明实施例先在周边电路区的各区形成阀值电压较小的晶体管的薄的栅介电层,再移除阀值电压较大的晶体管的区域上的薄的栅介电层。由于阀值电压较小的晶体管的栅介电层的厚度较薄,因此在移除薄的栅介电层的湿式刻蚀工艺的时间较短,较不易造成上述漏电流以及电流双驼峰等问题。此外,在本发明实施例中,在阀值电压较大的晶体管的区域上的导体层是通过具有高刻蚀选择比的湿式刻蚀工艺移除,因此可以避免器件有源区遭受到刻蚀的破坏。

32.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1