高压元件及其制造方法与流程

1.本发明涉及一种高压元件及其制造方法,特别涉及一种能在切换式电源供应电路中,抑制寄生硅控整流器(silicon controlled rectifier,scr)导通的高压元件及其制造方法。

现有技术

2.图1显示一种典型的切换式电源供应电路的电路示意图。切换式电源供应电路10包含控制电路1与功率级电路2。如图1所示,功率级电路2包括用以作为上桥开关的高压元件11与用以作为下桥开关的高压元件12,分别根据上桥信号ug与下桥信号lg而操作,以将输入电压vin转换为输出电压vout;并于功率级电路2的电感13上,产生电感电流il。

3.高压元件12操作时,当负载电路3为轻载,在特定情况下,电感电流il转为负电流,且由相位节点ph流经高压元件11,如图1中粗虚线箭头所示意,使得高压元件11与12之间的寄生硅控整流器(silicon controlled rectifier,scr)导通,造成高压元件11与12错误操作与电路损坏。因此,限制了切换式电源供应电路的安全操作区域(safe operation area,soa)与应用范围,其中安全操作区域的定义,为本领域技术人员所熟知,在此不予赘述。

4.有鉴于此,本发明提出一种能够抑制寄生scr导通,并提高安全操作区域,进而提高应用范围的高压元件及其制造方法。

技术实现要素:

5.就其中一观点言,本发明提供了一种高压元件,用于一切换式电源供应电路的一功率级中,用以作为一下桥开关,包含:至少一横向扩散金属氧化物半导体(lateral diffused metal oxide semiconductor,ldmos)元件,其包括:一阱区,具有一第一导电型,形成于一半导体层中;一本体区,具有一第二导电型,形成于该阱区中;一栅极,形成于该本体区上方并连接于该本体区;以及一源极与一漏极,具有该第一导电型,该源极与该漏极分别位于该栅极的外部不同侧下方的该本体区中与该阱区中;一第一隔绝区,具有该第二导电型,于该半导体层中,环绕该横向扩散金属氧化物半导体元件;一第二隔绝区,具有该第一导电型,于该半导体层中,环绕该第一隔绝区;一第三隔绝区,具有该第二导电型,于该半导体层中,环绕该第二隔绝区;以及一限流元件,电连接于该第二隔绝区,用以抑制一寄生硅控整流器(silicon controlled rectifier,scr)导通;其中,该源极与该本体区一边界间的该栅极正下方的部分该本体区定义一反转区,用以作为该横向扩散金属氧化物半导体元件在一导通操作中的一反转电流通道;其中,该本体区与该漏极之间的部分该阱区定义一漂移区,用以作为该横向扩散金属氧化物半导体元件在该导通操作中的一漂移电流通道。

6.就另一观点言,本发明提供了一种高压元件制造方法,其中该高压元件用于一切换式电源供应电路的一功率级中,用以作为一下桥开关,该高压元件制造方法包含:形成至少一横向扩散金属氧化物半导体(lateral diffused metal oxide semiconductor,

ldmos)元件,形成该横向扩散金属氧化物半导体的步骤包括:形成一阱区于一半导体层中,该阱区具有一第一导电型;形成一本体区于该阱区中,该本体区具有一第二导电型;形成一栅极于该本体区上方并连接于该本体区;以及形成一源极与一漏极分别位于该栅极的外部不同侧下方的该本体区中与该阱区中,该源极与该漏极具有该第一导电型;形成一第一隔绝区于该半导体层中,该第一隔绝区具有该第二导电型,环绕该横向扩散金属氧化物半导体元件;形成一第二隔绝区于该半导体层中,该第二隔绝区具有该第一导电型,环绕该第一隔绝区;形成一第三隔绝区于该半导体层中,该第三隔绝区具有该第二导电型,环绕该第二隔绝区;以及形成一限流元件,电连接于该第二隔绝区,用以抑制一寄生硅控整流器(silicon controlled rectifier,scr)导通;其中,该源极与该本体区一边界间的该栅极正下方的部分该本体区定义一反转区,用以作为该横向扩散金属氧化物半导体元件在一导通操作中的一反转电流通道;其中,该本体区与该漏极之间的部分该阱区定义一漂移区,用以作为该横向扩散金属氧化物半导体元件在该导通操作中的一漂移电流通道。

7.在一种较佳的实施型态中,该限流元件包括一肖特基势垒二极管(schottky barrier diode,sbd)、一电阻元件或一pn二极管。

8.在一种较佳的实施型态中,当该限流元件包括一肖特基势垒二极管(schottky barrier diode,sbd),该肖特基势垒二极管包括:一肖特基金属单元,形成于该第二隔绝区上;以及一肖特基半导体单元,形成于该第二隔绝区中,其中该肖特基半导体单元与该肖特基金属单元形成肖特基接触,且部分该第二隔绝区用以作为该肖特基半导体单元。

9.在一种较佳的实施型态中,该第二隔绝区从俯视图视之为一环型区域,且该环型区域中最靠近该功率级中的一上桥开关的一部分区域,用以作为该肖特基半导体单元。

10.在一种较佳的实施型态中,该部分区域为该环型区域的至少四分之一。

11.本发明的一优点为本发明可抑制寄生scr导通,并提高安全操作区域,进而提高应用范围。

12.以下通过具体实施例详加说明,当更容易了解本发明的目的、技术内容、特点及其所实现的功效。

附图说明

13.图1显示一种典型的切换式电源供应电路的电路示意图。

14.图2a是根据本发明的一实施例显示用于切换式电源供应电路的功率级中,用以作为下桥开关的高压元件的俯视示意图。

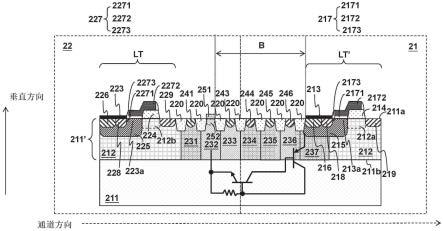

15.图2b是根据本发明的一实施例显示用于切换式电源供应电路的功率级中,用以作为下桥开关的高压元件的剖视示意图。

16.图3是根据本发明的另一实施例显示用于切换式电源供应电路的功率级中,用以作为下桥开关的高压元件的剖视示意图。

17.图4是根据本发明的一实施例显示高压元件制造方法的步骤流程图。

18.图中符号说明

19.1:控制电路

20.2:功率级电路

21.3:负载电路

22.10:切换式电源供应电路

23.11,12:高压元件

24.13:电感

25.21,22,31,32:高压元件

26.40:高压元件的制造方法

27.211,311:基板

28.211’,311’:半导体层

29.211a,311a:上表面

30.211b,311b:下表面

31.212,312:阱区

32.212a,212b:漂移区

33.213,223,313,323:硅化金属层

34.213a,223a,313a,323a:反转区

35.214,224,314,324:漂移氧化区

36.215,225,315,325:本体区

37.216,226,316,326:本体极

38.217,227,317,327:栅极

39.2171,2271,3171,3271:介电层

40.2172,2272,3172,3272:导电层

41.2173,2273,3173,3273:间隔层

42.218,228,318,328:源极

43.219,229,319,329:漏极

44.220,320:绝缘结构

45.231,331:第一隔绝区

46.232,332:第二隔绝区

47.233,333:第三隔绝区

48.234,334:第四隔绝区

49.235,335:第五隔绝区

50.236,336:第六隔绝区

51.237,337:高压阱区

52.241,341:第一隔绝区接点

53.242,342:第二隔绝区接点

54.243,343:第三隔绝区接点

55.244,344:第四隔绝区接点

56.245,345:第五隔绝区接点

57.246,346:第六隔绝区接点

58.251,351:限流元件

59.252:肖特基半导体单元

60.401,4011,4012,4013,4014,402,403,404,405:步骤

61.b:距离

62.gnd:接地

63.il:电感电流

64.lt,lt’:横向扩散金属氧化物半导体(ldmos)元件

65.lg:下桥信号

66.or3,or4:操作区域

67.ph:相位节点

68.ug:上桥信号

69.vin:输入电压

70.vout:输出电压

具体实施方式

71.涉及本发明的前述及其他技术内容、特点与功效,在以下配合参考附图的较佳实施例的详细说明中,将可清楚地呈现。本发明中的附图均属示意,主要意在表示工艺步骤以及各层之间的上下次序关系,至于形状、厚度与宽度则并未依照比例绘制。

72.请参考图2a与图2b,其显示本发明的第一个实施例。图2a显示用于切换式电源供应电路的功率级中,用以作为上桥开关的高压元件21及用以作为下桥开关的高压元件22的俯视示意图。图2b显示用于切换式电源供应电路的功率级中,用以作为上桥开关的高压元件21及用以作为下桥开关的高压元件22的剖视示意图。图2b是图2a的操作区域or3至操作区域or4沿着a-a’线所取得的剖视示意图。如图2a及图2b所示,用以作为下桥开关的高压元件22包括:横向扩散金属氧化物半导体(lateral diffused metal oxide semiconductor,ldmos)元件lt、肖特基势垒二极管(schottky barrier diode,sbd)251、第一隔绝区231、第二隔绝区232及第三隔绝区233。用以作为上桥开关的高压元件21包括:横向扩散金属氧化物半导体(ldmos)元件lt’以及第四隔绝区234、第五隔绝区235及第六隔绝区236。ldmos元件lt包括:阱区212、漂移氧化区224、本体区225、本体极226、栅极227、源极228以及漏极229。ldmos元件lt’包括:阱区212、漂移氧化区214、本体区215、本体极216、栅极217、源极218、漏极219以及高压阱区237。

73.半导体层211’形成于基板211上,半导体层211’于垂直方向(如图2b中的实线箭头方向所示意,下同)上,具有相对的上表面211a与下表面211b。基板211例如但不限于为一p型或n型的半导体基板。半导体层211’例如以外延的工艺步骤,形成于基板211上,或是以部分基板211作为半导体层211’。形成半导体层211’的方式,为本领域技术人员所熟知,在此不予赘述。

74.请继续参阅图2b,漂移氧化区224及214分别形成于该上表面211a上并分别连接于上表面211a,且分别位于对应的部分漂移区212b及212a(如图2b中ldmos元件lt及lt’中的虚线框所示意)的正上方,并分别连接于对应的漂移区212b及212a。漂移氧化区224及214例如但不限于如图所示的区域氧化(local oxidation of silicon,locos)结构,也可为浅沟槽绝缘(shallow trench isolation,sti)结构。

75.阱区212具有第一导电型,形成于半导体层211’中,且于垂直方向上,阱区212位于上表面211a下并连接于上表面211a。阱区212例如由至少一离子注入工艺步骤所形成。本体

rectifier,scr)导通,由此提高安全操作区域,进而提高应用范围。如图2b所示,通过设置限流元件251,可使寄生npn晶体管不会导通,进而使scr无法被触发,而抑制scr导通。于一实施例中,限流元件251可包括一肖特基势垒二极管(schottky barrier diode,sbd)、一电阻元件或一pn二极管。如图2b所示,自限流元件251的边缘至高压元件21的本体极216的边缘的距离定义为距离b。于一实施例中,距离b较佳为66微米(μm)。

83.于一实施例中,当限流元件251为肖特基势垒二极管(sbd)时,肖特基势垒二极管包括一肖特基金属单元以及一肖特基半导体单元252。肖特基金属单元形成于第二隔绝区232上,而肖特基半导体单元252形成于第二隔绝区232中。肖特基半导体单元252与肖特基金属单元形成肖特基接触。于一实施例中,部分第二隔绝区232用以作为肖特基半导体单元252。于一实施例中,如图2a所示,第二隔绝区232从俯视图视之为一环型区域,且环型区域中最靠近功率级中的一上桥开关的一部分区域,用以作为肖特基半导体单元252,且该部分区域的第二隔绝区232上的第二隔绝区接点242予以替换成限流元件251例如但不限于肖特基金属单元,除了该部分区域以外的第二隔绝区232的上表面下仍然设置第二隔绝区接点242。于一实施例中,前述部份区域可为环型区域的全部。于另一实施例中,前述部分区域为环型区域的至少四分之一。于一较佳实施例中,前述部分区域为环型区域的至少二分之一。

84.于一实施例中,肖特基金属单元与一偏置电压电连接。于一较佳实施例中,肖特基金属单元与功率级电路的一电流流出端电连接。于一较佳实施例中,肖特基金属单元与功率级电路的输出端电连接。

85.第一隔绝区231及第三隔绝区233分别具有对应的第一隔绝区接点241及第三隔绝区接点243。于垂直方向上,第一隔绝区接点241形成于第一隔绝区231的上表面下且电连接于第一隔绝区231,而第三隔绝区接点243形成于第三隔绝区233的上表面下且电连接于第三隔绝区233。于垂直方向上,漏极229与第一隔绝区接点241之间、第一隔绝区接点241与限流元件251之间以及限流元件251与第三隔绝区接点243之间分别形成有对应的绝缘结构220,其形成于上表面211a下并连接于上表面211a。

86.同理,第六隔绝区236具有第一导电型,于半导体层211’中,环绕ldmos元件lt’的高压阱区237,而第五隔绝区235具有第二导电型,于半导体层211’中,环绕第六隔绝区236。第四隔绝区234具有第一导电型,于半导体层211’中,环绕第五隔绝区235且邻近第三隔绝区233。第四隔绝区234、第五隔绝区235及第六隔绝区236分别具有对应的第四隔绝区接点244、第五隔绝区接点245及第六隔绝区接点246。于垂直方向上,第四隔绝区接点244形成于第四隔绝区234的上表面下且电连接于第四隔绝区234,而第五隔绝区接点245形成于第五隔绝区235的上表面下且电连接于第五隔绝区235。第六隔绝区接点246形成于第六隔绝区236的上表面下且电连接于第六隔绝区236。

87.于垂直方向上,本体极216与第六隔绝区接点246之间、第六隔绝区接点246与第五隔绝区接点245之间、第五隔绝区接点245与第四隔绝区接点244之间以及第四隔绝区接点244与第三隔绝区接点243之间分别形成有对应的绝缘结构220,其形成于上表面211a下并连接于上表面211a。高压元件21及22可更包含一基板211,具有第二导电型,包覆阱区212、第一隔绝区231、第二隔绝区232、第三隔绝区233、第四隔绝区234、第五隔绝区235、第六隔绝区236及高压阱区237的底面。在一实施例中,ldmos元件lt及lt’中,源极228及218与本体极226及216分别以如图2b所示的硅化金属层223及213电连接。

88.值得注意的是,本发明优于现有技术的其中一个技术特征,在于:根据本发明,以图2b所示的实施例为例,高压元件22包括限流元件251,其设置于第二隔绝区232上,可抑制寄生scr导通,并提高安全操作区域,进而提高应用范围。

89.图3是根据本发明的另一实施例显示用于切换式电源供应电路的功率级中,用以作为上桥开关的高压元件31及用以作为下桥开关的高压元件32的剖视示意图。本实施例与图2b的实施例的不同之处在于,本实施例的限流元件351从外部耦接至第二隔绝区接点342。本实施例的ldmos元件lt及lt’、第一隔绝区331、第二隔绝区332、第三隔绝区333、第四隔绝区334、第五隔绝区335、第六隔绝区336、第一隔绝区接点341、第二隔绝区接点342、第三隔绝区接点343、第四隔绝区接点344、第五隔绝区接点345、第六隔绝区接点346及绝缘结构320类似于图2b的ldmos元件lt及lt’、第一隔绝区231、第二隔绝区232、第三隔绝区233、第四隔绝区234、第五隔绝区235、第六隔绝区236、第一隔绝区接点241、第二隔绝区接点242、第三隔绝区接点243、第四隔绝区接点244、第五隔绝区接点245、第六隔绝区接点246及绝缘结构220,故不赘述。于一实施例中,限流元件351可包括一肖特基势垒二极管(schottky barrier diode,sbd)、一电阻元件或一pn二极管。

90.图4是根据本发明的一实施例显示高压元件制造方法的步骤流程图。如图4所示,本发明的用于切换式电源供应电路的功率级中,用以作为下桥开关的高压元件的制造方法40包含于步骤401,形成至少一横向扩散金属氧化物半导体(ldmos)元件。步骤401包括于步骤4011、步骤4012、步骤4013以及步骤4014。于步骤4011中,形成一阱区于一半导体层中,阱区具有第一导电型。接着,于步骤4012中,形成一本体区于阱区中,本体区具有一第二导电型。之后,于步骤4013中,形成一栅极于本体区上方并连接于本体区。接续,于步骤4014中,形成一源极与一漏极分别位于栅极的外部不同侧下方的本体区中与阱区中,源极与漏极具有第一导电型。之后,于步骤402中,形成一第一隔绝区于半导体层中,第一隔绝区具有第二导电型,环绕横向扩散金属氧化物半导体元件。接着,于步骤403中,形成一第二隔绝区于半导体层中,第二隔绝区具有第一导电型,环绕第一隔绝区。之后,于步骤404中,形成一第三隔绝区于半导体层中,第三隔绝区具有第二导电型,环绕第二隔绝区。接续,于步骤405中,形成一限流元件,电连接于第二隔绝区,用以抑制一寄生硅控整流器(scr)导通。

91.以上已针对较佳实施例来说明本发明,但以上所述,仅为使本领域技术人员易于了解本发明的内容,并非用来限定本发明的权利范围。在本发明的相同精神下,本领域技术人员可以想到各种等效变化。此外,所说明的各个实施例,并不限于单独应用,也可以组合应用。因此,本发明的范围应涵盖上述及其他所有等效变化。此外,本发明的任一实施型态不必须实现所有的目的或优点,因此,权利要求的任一项也不应以此为限。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1