功率半导体器件和功率半导体芯片的制作方法

功率半导体器件和功率半导体芯片

1.相关申请的交叉引用

2.本技术要求于2020年5月15日向韩国知识产权局提交的韩国专利申请no.10

‑

2020

‑

0058261的优先权的利益,该专利申请的全部内容通过引用结合于此。

技术领域

3.本公开涉及半导体器件,更具体地,涉及用于切换功率传输的功率半导体器件和功率半导体芯片。

背景技术:

4.功率半导体器件是在高电压和大电流环境下工作的半导体器件。功率半导体器件用于需要高功率切换的领域,例如逆变器器件。例如,功率半导体器件可以包括绝缘栅双极晶体管(igbt)、功率mosfet等。功率半导体器件需要基本上对高电压的击穿特性,并且近来还需要高速切换操作。

5.当从沟道注入的电子和从集电极注入的空穴流动时,半导体器件工作。然而,在沟槽栅型功率半导体器件中,当空穴在沟槽栅极中过度累积时,发生负栅极充电(ngc)现象,并且在栅极方向上产生位移电流。沟槽栅型功率半导体器件具有大的栅极至集电极电容(cgc),其受到负栅极充电(ngc)的极大影响,从而导致切换稳定性的问题。

6.现有技术文献

7.专利文献

8.专利文献1:韩国专利申请公开第20140057630号(2014年5月13日公开)

技术实现要素:

9.提供本概述以便以简化形式介绍将在以下具体实施方式中进一步描述的一些概念。本概述不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在用作确定所要求保护的主题的范围的辅助。

10.在一个总体方面,一种功率半导体器件包括:半导体层;梯形沟槽,该沟槽从该半导体层的表面向该半导体层内凹陷特定深度并且包括具有第一深度的一对线以及连接在该对线之间并且具有比该第一深度浅的第二深度的多个连接件;阱区,被限定在半导体层中、在该对线之间并且在该沟槽的多个连接件之间;浮动区,被限定在该半导体层中、在沟槽的一对线的外部;栅极绝缘层,布置在沟槽的内壁上;以及栅极电极层,布置在栅极绝缘层上以填充沟槽,并且包括填充一对线的第一部分和填充多个连接件的第二部分。栅极电极层的第二部分的深度比栅极电极层的第一部分的深度浅。

11.连接件中的每一个的宽度可以大于一对线中的每条线的宽度,并且栅极电极层的第二部分的宽度可以大于栅极电极层的第一部分的宽度。

12.浮动区可在该对线下方延伸以包围栅极电极层的第一部分的底表面,并且栅极电极层的第二部分的底表面可以相对于浮动区露出。

13.栅极电极层的第二部分的深度可以比阱区域的深度深。

14.功率半导体器件可以包括源极区或发射极区,源极区或发射极区在阱区中与栅极电极层的第二部分相邻并且在栅极电极层的第一部分的延伸方向上彼此间隔开。

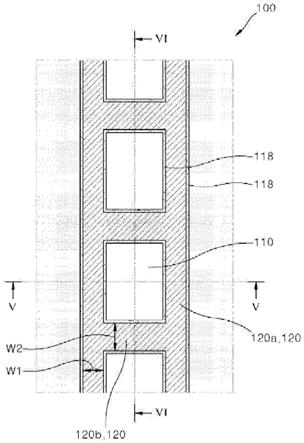

15.功率半导体器件可以包括被限定在半导体层中、位于阱区下方的漂移区。

16.漂移区、以及源区或发射区可以掺杂有第一导电类型的杂质,并且阱区和浮动区可以掺杂有与第一导电类型相反的第二导电类型的杂质。

17.在另一总体方面,一种功率半导体芯片包括:半导体层,其包括主单元区域和传感器区域;功率半导体晶体管,布置在主单元区域中并且包括功率半导体器件;电流传感器晶体管,布置在传感器区域中以监测功率半导体晶体管的电流;发射极端子,连接到功率半导体晶体管的发射电极;电流传感器端子,连接到电流传感器晶体管的发射电极;以及栅极端子,连接到功率半导体晶体管的栅极电极和电流传感器晶体管的栅极电极。

18.其他特征和方面将从以下详细说明、附图以及权利要求中变得清楚。

附图说明

19.根据结合附图的以下详细描述,本公开的上述和其它目的、特征以及优点将更加明显:

20.图1是示出根据本公开的实施例的功率半导体芯片的示意性平面图;

21.图2是示出根据本公开的实施例的功率半导体芯片的电路图;

22.图3是示出图2的功率半导体芯片的一部分的电路图;

23.图4是示出根据本公开的实施例的功率半导体器件的平面图;

24.图5是沿着图4的功率半导体器件的线v

‑

v截取的剖面图;以及

25.图6是沿着图4的功率半导体器件的线vi

‑

vi截取的剖面图。

具体实施方式

26.在下文中,将参照附图详细描述本公开的实施例。然而,本公开不限于以下公开的实施例,而是可以以各种不同形式实现。以下示例被用于完成本公开的公开,并且充分告知本公开的范围中的普通技术人员。此外,为了便于描述,在附图中至少一些构成元件的尺寸可以被夸大或减小。在附图中,相同的附图标记表示相同的元件。

27.除非另有定义,本文中使用的所有术语具有与本领域普通技术人员通常理解的相同的含义。在附图中,为了解释而夸大了层和区域的尺寸,并且因此被提供来解释本公开的一般结构。

28.相同的附图标记表示相同的元件。当将诸如层、区域或衬底的配置称为在另一配置上时,将理解它在另一配置的正上部沟槽中,或者在两者之间还可以存在其他的中间配置。另一方面,当一个配置被称为“直接在”另一配置上时,应理解不存在介入配置。

29.图1是示出根据本公开的实施例的功率半导体芯片50的示意性平面图,图2是示出根据本公开的实施例的功率半导体芯片50的电路图,以及图3是示出图2的功率半导体芯片的一部分的电路图。

30.参照图1,可以使用包括主单元区域mc和传感器区域sa的半导体层105来形成功率半导体芯片50。功率半导体芯片50可以包括晶片管芯或封装结构。

31.多个功率半导体晶体管(图3的pt)可以形成在主单元区域mc中。多个电流传感器晶体管(图3的st)可以形成在传感器区域sa中以监测功率半导体晶体管pt的电流。

32.例如,功率半导体晶体管pt和电流传感器晶体管st可以包括绝缘栅双极晶体管(igbt)或功率mosfet结构。igbt可以包括栅极电极、发射电极和集电极。在图2至图3中,将作为示例描述功率半导体晶体管pt和电流传感器晶体管st是igbt的情况。

33.参照图1至图3,功率半导体芯片50可以包括用于与外部连接的多个端子。

34.例如,功率半导体芯片50可以包括:发射极端子69,发射极端子69连接到功率半导体晶体管pt的发射电极;开尔文(kelvin)发射极端子66,与功率半导体晶体管pt的开尔文发射电极连接;电流传感器端子64,与电流传感器晶体管st的发射电极连接以用于监测电流;栅极端子62,与功率半导体晶体管pt的栅极电极和电流传感器晶体管st的栅极电极连接;温度传感器端子67和68,与温度传感器tc连接以用于监测温度;和/或集电极端子61,与功率半导体晶体管pt的集电极以及电流传感器晶体管st的集电极连接。

35.在图2中,集电极端子61可以形成在图1的半导体层105的后表面上,并且图2中的发射极端子69可以形成在图1的主单元区域mc上。

36.温度传感器tc可以包括连接到温度传感器端子67和68的结二极管。结二极管可以包括在至少一个n型杂质区和至少一个p型杂质区之间的结结构,例如p

‑

n结结构、p

‑

n

‑

p结结构、n

‑

p

‑

n结结构等。

37.这种结构示例性地描述了在功率半导体芯片50中嵌入温度传感器tc的结构,但是在本实施例的变形例中可以省略温度传感器tc。

38.功率半导体晶体管pt连接在发射极端子69和集电极端子61之间,并且电流传感器晶体管st部分地与功率半导体晶体管pt并联连接在电流传感器端子64和集电极端子61之间。电流传感器晶体管st的栅极电极和功率半导体晶体管pt的栅极电极通过特定电阻共同连接到栅极端子62。

39.电流传感器晶体管st可以以与功率半导体晶体管pt基本相同的结构形成,但可以减小到特定的比率。因此,可以通过监测电流传感器晶体管st的输出电流来间接监测功率半导体晶体管pt的输出电流。

40.例如,功率半导体晶体管pt和/或电流传感器晶体管st可以包括图4至图6的功率半导体器件100的结构。在一些实施例中,功率半导体晶体管pt和功率半导体器件100可以互换使用。

41.图4是示出根据本公开的实施例的功率半导体器件100的平面图,图5是沿着图4的功率半导体器件v

‑

v的线截取的剖面图,以及图6是沿着图4的功率半导体器件vi

‑

vi的线截取的剖面图。

42.参照图4至图6,半导体层105可以指一个或多个半导体材料层,例如可以指半导体衬底的一部分和/或一个或多个外延层。

43.至少一个沟槽116可以从半导体层105的表面向半导体层105内凹陷待形成的特定深度。沟槽116的数量可以根据功率半导体器件100的性能适当地选择,并且不限制本实施例的范围。

44.沟槽116可以具有梯形,沟槽116包括一对线116a和连接在该对线116a之间的多个连接件116b。连接件116b可以形成为在线116a之间以规则间隔隔开。

45.例如,在沟槽116中,线116a可以具有第一深度d1,并且连接件116b可以具有第二深度d2。第二深度d2可以小于第一深度d1,并且因此,连接件116b的深度可以比各线116a的深度浅。此外,沟槽116的每个连接件116b的宽度w2可以大于每条线116a的宽度w1。这种结构可以减轻连接件116b附近的电场应力。

46.此外,沟槽116可以具有圆形边缘,例如沟槽116的底部边缘,用于抑制电场的集中。

47.例如,半导体层105可以包括漂移区107和阱区110。此外,半导体层105还可以包括在阱区110中的发射极区112。这里,发射极区112可以被称为源极区,并且在下文中,发射极区112可以表示源极区。此外,半导体层105还可以包括浮动区125。

48.更具体地,阱区110可以被限定在半导体层105中,位于沟槽116的线116a之间且在沟槽116的连接件116b之间。即,阱区110可以是由梯形沟槽116包围的矩形半导体层105的区域。

49.浮动区125可以被限定在半导体层105中、位于沟槽116的线116a的外部。例如,浮动区125可以形成在梯形沟槽116外部的半导体层105中。

50.浮动区125还可以延伸到线116a的下方,以包围沟槽116的线116a的底表面用来减轻电场。然而,浮动区125可以不延伸到连接件116b的下方。因此,如图6所示,沿着图4的vi

‑

vi的线在阱区110和连接件116b下方可以不存在浮动区125。

51.在图4中,阱区110可以在线116a的延伸方向上(即沿着vi

‑

vi的线)被连接件116b隔开。浮动区125和阱区110可以沿着v

‑

v线交替地布置,其中,线116a位于浮动区125和阱区110之间。

52.例如,阱区110和浮动区125可以用相同类型的掺杂剂掺杂。

53.发射极区112可以在阱区110内的特定深度处邻近沟槽116形成。例如,发射极区112可以不形成在阱区110中与线116a相邻的部分中,而是可以形成在阱区110中与连接件116b相邻的部分中。因此,发射极区112可以在阱区110中沿线116a的延伸方向(即沿着线vi

‑

vi)邻近于连接件116b而形成。

54.例如,发射极区112和阱区110可以用相反类型的掺杂剂掺杂。

55.漂移区107可以被限定在半导体层105中,位于阱区110下方。例如,漂移区107可以被限定在沟槽116之间、与阱区110接触,并且可以在浮动区125的下方延伸至半导体层105的下表面。

56.例如,漂移区107和发射极区112可以具有第一导电类型,并且阱区110和浮动区125可以具有第二导电类型。第一导电类型和第二导电类型可以具有相反的导电类型,但可以分别是n型和p型中的任一种。例如,当第一导电类型可以是n型时,第二导电类型可以是p型,反之亦然。

57.在一些实施例中,漂移区107可以提供为第一导电类型的外延层,并且阱区110可以用第二导电类型的杂质掺杂到外延层,或者可以用第二导电类型的外延层形成。发射极区112可以通过在阱区110中掺杂第一导电类型的杂质或通过额外形成第一导电类型的外延层来形成。

58.此外,当功率半导体器件100是igbt时,集电极区域(未示出)可以设置在漂移区107下方,并且集电极(未示出)可以设置在集电极区域下方以连接到集电极区域。例如,集

电极区域可以设置在漂移区107的下方,作为具有与漂移区107的导电类型不同的第二导电类型的外延层。

59.作为另一示例,当功率半导体器件100是功率mosfet时,漏极电极可以在漂移区107的下方连接。

60.栅极绝缘层118可以形成在至少一个沟槽116的内壁上。例如,栅极绝缘层118可以形成为在沟槽116的内壁上具有均匀的厚度。

61.栅极电极层120可以形成在栅极绝缘层118上以填充至少一个沟槽116。例如,栅极电极层120可以形成为凹陷到半导体层105中,并且在这种情况下,栅极电极层120可以理解为具有凹陷型或沟槽型。

62.例如,栅极电极层120可以包括通过填充线116a而形成的第一部分120a和通过填充连接件116b而形成的第二部分120b。

63.沟槽116中的栅极电极层120的形状可对应于沟槽116的结构。因此,由于沟槽116的连接件116b的第二深度d2小于线116a的第一深度d1,因此栅极电极层120的第二部分120b的深度可以比第一部分120a的深度浅。栅极电极层120的第二部分120b的深度可以大于阱区110的深度。此外,栅极电极层120的第二部分120b的宽度可以大于第一部分120a的宽度。

64.栅极电极层120在平面上的布置可以跟随沟槽116的布置,并且因此栅极电极层120可以在图4中以梯形布置。与沟槽116一样,栅极电极层120的数量可以根据功率半导体器件100的操作规格来适当地选择,并且本实施例的范围不受限制。

65.此外,发射电极(未示出)可以形成在发射极区112上。发射电极可以共同连接到发射极区112和阱区110。绝缘层130可以插入在半导体层105和发射电极之间。

66.根据上述结构,浮动区125可以在沟槽116的线116a的下方延伸以包围栅极电极层120的第一部分120a的底表面。然而,栅极电极层120的第二部分120b的底表面可以从浮动区125露出,而不被浮动区125包围。

67.此外,发射极区112可以与阱区110中的栅极电极层120的第二部分120b相邻,并且可以在栅极电极层120的第一部分120a的延伸方向上彼此间隔开。

68.沟槽116的下部分可以通过梯形条部分(即,通过沟槽116的线116a和栅极电极层120的第一部分120a的结构以及浮动区125的结构)而受保护,因此,功率半导体器件100可以在关断期间保持高的内部击穿电压。

69.此外,发射极区112可以布置在与沟槽116的连接件116b和栅极电极层120的第二部分120b相邻的部分中,并且可以不布置在与沟槽116的线116a和栅极电极层120的第一部分120a相邻的部分中,因此,当功率半导体器件100工作时,可以通过改变空穴的移动路径来减小栅极

‑

集电极电容cgc的值。因此,可以减少负栅极充电(ngc)现象,并且可以改善切换稳定性。

70.此外,可以降低栅极电极层120的第二部分120b的深度,并且可以增加栅极电极层120的第二部分120b的宽度,从而减小栅极电极层120的第二部分120b下方的电场和栅极

‑

集电极电容(cgc)的值。

71.此外,当栅极电极层120的各第一部分120a之间的距离变窄时,电荷共享现象的影响增大,并且因此,随着相邻的第一部分120a下方的等电位表面连接起来,在栅极电极层

120下方的电场应力可以进一步减轻。

72.以上已经描述了对于功率半导体器件是igbt的情况,但是同样适用于其是功率mosfet的情况。

73.在图1至图3中,功率半导体芯片50可以使用图4至图6所示的功率半导体器件100作为功率半导体晶体管pt和/或电流传感器晶体管st,因此可以将上述功率半导体器件100的特性原样应用于功率半导体芯片50。

74.因此,可以提供梯形沟槽116和栅极电极层120的形状变化,并且因此,上述功率半导体器件100和使用功率半导体器件100的功率半导体芯片50可以将击穿电压维持在高电压、抑制负栅极充电现象、并且提高切换稳定性。

75.根据如上所述做出的根据本公开的实施例的功率半导体器件和功率半导体芯片,通过抑制负栅极充电(ngc)现象,同时保持对高电压的击穿特性,可以提高切换稳定性。

76.效果是说明性的,并且本公开的范围不因此而受到限制。

77.在上文中,尽管已经参照示例性实施例和附图描述了本公开,但本公开并不限于此,而是可以由本公开所属领域的技术人员进行各种修改和改变,而不脱离在所附权利要求中要求的本公开的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1