非挥发性存储器元件及其制造方法与流程

1.本发明涉及一种半导体元件及其制造方法,且特别是涉及一种非挥发性存储器元件及其制造方法。

背景技术:

2.在一般的磁阻式随机存取存储器(magnetoresistive random access memory,mram)的制作工艺中,在形成存储器单元(memory cell)的图案化过程中,光学效应会对位于存储器区域的边缘处的存储器单元的图案轮廓造成影响,使得位于存储器区域的边缘处的存储器单元的尺寸小于其他的存储器单元的尺寸。

3.为了避免上述现象,目前会在存储器区域的周围设置虚设区域,且在虚设区域中设置虚设存储器单元。如此一来,上述的光学效应仅会对存储器区域周围的虚设存储器单元造成影响,使得存储器区域中的存储器单元能够具有相同的尺寸。

4.此外,为了避免虚设区域中的虚设存储器单元与其他线路电连接而影响元件效能,因此虚设存储器单元的下方并未设置导电通孔(conductive via)。此时,位于存储器区域的边缘处的用以将存储器单元电连接至线路图案的导电通孔的图案轮廓会受到上述光学效应的影响而具有较小的孔径,因而对元件效能造成影响。举例来说,较小孔径的导电通孔会具有较大的电阻,导致磁阻式随机存取存储器的隧穿式磁阻(tunneling magnetoresistance,tmr)大幅降低。

技术实现要素:

5.本发明提供一种非挥发性存储器元件,其中存储器区域的周围设置有虚设通孔。

6.本发明提供一种非挥发性存储器元件的制造方法,其中虚设通孔形成在存储器区域的周围。

7.本发明的非挥发性存储器元件包括基底、内连线结构、多个存储器单元、多个导电通孔以及多个虚设通孔。所述基底具有存储器区域以及虚设区域,其中所述虚设区域围绕所述存储器区域。所述内连线结构设置于所述基底上,且位于所述存储器区域中。所述多个存储器单元设置于所述内连线结构上,且自俯视方向来看以阵列方式排列,其中所述多个存储器单元包括位于所述存储器区域中的多个第一存储器单元以及位于所述虚设区域中的多个第二存储器单元。所述多个导电通孔设置于所述存储器区域中,且位于所述多个第一存储器单元与所述内连线结构之间,以分别电连接所述第一存储器单元中的每一个与所述内连线结构。所述多个虚设通孔设置于所述虚设区域中,且围绕所述存储器区域。

8.在本发明的非挥发性存储器元件的一实施例中,自俯视方向来看,相邻两行中的所述导电通孔彼此对准,且相邻两列中的所述导电通孔彼此对准。

9.在本发明的非挥发性存储器元件的一实施例中,自俯视方向来看,所述多个虚设通孔在行方向上与所述多个导电通孔不对准,且所述多个虚设通孔在列方向上与所述多个导电通孔不对准。

10.在本发明的非挥发性存储器元件的一实施例中,相邻两行中的所述导电通孔之间的距离以及相邻两列中的所述导电通孔之间的距离小于相邻的所述虚设通孔与所述导电通孔之间的距离。

11.在本发明的非挥发性存储器元件的一实施例中,自俯视方向来看,相邻两行中的所述导电通孔彼此不对准,且相邻两列中的所述导电通孔彼此不对准。

12.在本发明的非挥发性存储器元件的一实施例中,相邻两行中的所述导电通孔之间以及相邻两列中的所述导电通孔之间的距离大于相邻的所述虚设通孔与所述导电通孔之间的距离。

13.在本发明的非挥发性存储器元件的一实施例中,所述内连线结构包括位于所述虚设区域中的虚设部分,且所述多个第二存储器单元不与所述虚设部分电连接。

14.在本发明的非挥发性存储器元件的一实施例中,所述多个虚设通孔不与所述虚设部分连接。

15.在本发明的非挥发性存储器元件的一实施例中,所述多个虚设通孔与所述虚设部分连接。

16.在本发明的非挥发性存储器元件的一实施例中,所述虚设通孔的孔径小于与所述导电通孔的孔径。

17.本发明的非挥发性存储器元件的制造方法包括以下步骤。提供具有存储器区域以及虚设区域的基底,其中所述虚设区域围绕所述存储器区域。在所述基底上形成内连线结构,其中所述内连线结构位于所述存储器区域中。在所述内连线结构上形成多个存储器单元,其中自俯视方向来看,所述多个存储器单元以阵列方式排列,且所述多个存储器单元包括位于所述存储器区域中的多个第一存储器单元以及位于所述虚设区域中的多个第二存储器单元。在所述存储器区域中形成多个导电通孔,其中所述多个导电通孔位于所述多个第一存储器单元与所述内连线结构之间,以分别电连接所述第一存储器单元中的每一个与所述内连线结构。在所述虚设区域中形成多个虚设通孔,其中所述多个虚设通孔围绕所述存储器区域。

18.在本发明的非挥发性存储器元件的制造方法的一实施例中,自俯视方向来看,相邻两行中的所述导电通孔彼此对准,且相邻两列中的所述导电通孔彼此对准。

19.在本发明的非挥发性存储器元件的制造方法的一实施例中,自俯视方向来看,所述多个虚设通孔在行方向上与所述多个导电通孔不对准,且所述多个虚设通孔在列方向上与所述多个导电通孔不对准。

20.在本发明的非挥发性存储器元件的制造方法的一实施例中,相邻两行中的所述导电通孔之间的距离以及相邻两列中的所述导电通孔之间的距离小于相邻的所述虚设通孔与所述导电通孔之间的距离。

21.在本发明的非挥发性存储器元件的制造方法的一实施例中,自俯视方向来看,相邻两行中的所述导电通孔彼此不对准,且相邻两列中的所述导电通孔彼此不对准。

22.在本发明的非挥发性存储器元件的制造方法的一实施例中,相邻两行中的所述导电通孔之间以及相邻两列中的所述导电通孔之间的距离大于相邻的所述虚设通孔与所述导电通孔之间的距离。

23.在本发明的非挥发性存储器元件的制造方法的一实施例中,所述内连线结构包括

位于所述虚设区域中的虚设部分,且所述多个第二存储器单元不与所述虚设部分电连接。

24.在本发明的非挥发性存储器元件的制造方法的一实施例中,所述多个虚设通孔不与所述虚设部分连接。

25.在本发明的非挥发性存储器元件的制造方法的一实施例中,所述多个虚设通孔与所述虚设部分连接。

26.在本发明的非挥发性存储器元件的制造方法的一实施例中,所述虚设通孔的孔径小于与所述导电通孔的孔径。

27.基于上述,在本发明中,虚设通孔设置于存储器区域的周围。因此,在以光刻制作工艺定义与存储器单元连接的导电通孔的位置以及虚设通孔的位置时,可避免用来定义被虚设通孔围绕的导电通孔的位置的光致抗蚀剂图案的轮廓受到光学效应而导致孔径缩小,进而能够确保存储器元件的效能。

28.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

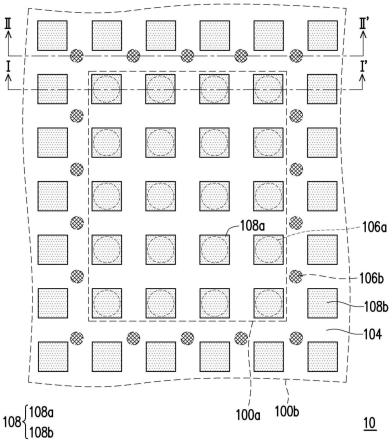

29.图1a至图1c为本发明实施例所绘示的非挥发性存储器元件的制造流程俯视示意图;

30.图2a至图2c为图1a至图1c中的i-i’剖线的制造流程剖面示意图;

31.图3a至图3c为图1a至图1c中的ii-ii’剖线的制造流程剖面示意图;

32.图4为本发明另一实施例所绘示的非挥发性存储器元件的俯视示意图;

33.图5为本发明另一实施例所绘示的非挥发性存储器元件的俯视示意图。

具体实施方式

34.下文列举实施例并配合附图来进行详细地说明,但所提供的实施例并非用以限制本发明所涵盖的范围。此外,附图仅以说明为目的,并未依照原尺寸作图。为了方便理解,在下述说明中相同的元件将以相同的符号标示来说明。

35.关于本文中所提到「包含」、「包括」、「具有」等的用语均为开放性的用语,也就是指「包含但不限于」。

36.当以「第一」、「第二」等的用语来说明元件时,仅用于将这些元件彼此区分,并不限制这些元件的顺序或重要性。因此,在一些情况下,第一元件也可称作第二元件,第二元件也可称作第一元件,且此不偏离本发明的范畴。

37.图1a至图1c为依照本发明实施例所绘示的非挥发性存储器元件的制造流程俯视示意图。图2a至图2c为依照图1a至图1c中的i-i’剖线的制造流程剖面示意图。图3a至图3c为依照图1a至图1c中的ii-ii’剖线的制造流程剖面示意图。

38.首先,同时参照图1a、图2a与图3a,提供基底100。基底100具有存储器区域100a以及围绕存储器区域100a的虚设区域100b。存储器区域100a为用以设置存储器单元的区域。存储器单元可以是磁阻式随机存取存储器的存储器单元或是其他类型存储器的存储器单元,本发明不对此进行限定。虚设区域100b为用以设置不与存储器单元电连接的虚设元件的区域。在本实施例中,基底100为其上已形成有各种半导体元件的硅基底。举例来说,基底

100可包括硅基底、形成于硅基底的表面上的晶体管以及覆盖晶体管的介电层,但本发明不限于此。然后,在介电层中形成内连线结构102。在本实施例中,为使附图清晰以及便于说明,并未绘示出上述的各种半导体元件,且仅绘示出内连线结构102中最上层的线路层。所述线路层可视实际需求而位于介电层中或位于介电层的表面上。内连线结构102与硅基底上的各种半导体元件电连接。然后,在基底100上形成介电层104,以覆盖内连线结构102。上述各种半导体元件以及内连线结构102的形成方法为本领域技术人员所熟知,于此不再赘述。

39.在本实施例中,内连线结构102包括位于存储器区域100a中作为电连接构件的主要部分102a以及位于虚设区域100b中不作为电连接构件的虚设部分102b,但本发明不限于此。在其他实施例中,视实际的布局需求,内连线结构102可仅包括位于存储器区域100a中的主要部分102a。

40.然后,同时参照图1b、图2b与图3b,在介电层104中形成多个通孔(via)。通孔的形成方法为本领域技术人员所熟知,在此不再赘述。详细地说,在本实施例中,在存储器区域100a中的介电层104中形成导电通孔106a,以及在虚设区域100b中的介电层104中形成虚设通孔106b。虚设通孔106b围绕存储器区域100a中的导电通孔106a。在本实施例中,导电通孔106a与内连线结构102的主要部分102a连接,而虚设通孔106b与内连线结构102的虚设部分102b连接。如此一来,导电通孔106a可作为电连接构件,而虚设通孔106b则不会作为电连接构件。在其他实施例中,虚设通孔106b可不与内连线结构102的虚设部分102b连接。

41.在本实施例中,自俯视方向来看,导电通孔106a以阵列方式排列。在所述阵列中,相邻两行中的导电通孔106a彼此对准,且相邻两列中的导电通孔106a彼此对准。也就是说,在本实施例中,存储器区域100a中的导电通孔106a以矩形阵列的方式排列,而虚设通孔106b围绕以矩形阵列方式排列的导电通孔106a。此外,自俯视方向来看,虚设通孔106b在行方向上与导电通孔106a不对准,且在列方向上与导电通孔106a不对准。另外,相邻两行中的导电通孔106a之间的距离d1小于相邻的虚设通孔106b与导电通孔106a之间的距离d3,且相邻两列中的导电通孔106a之间的距离d2也小于距离d3。

42.基于上述的布局方式,在形成导电通孔106a与虚设通孔106b的过程中,在以光刻制作工艺定义导电通孔106a与虚设通孔106b的位置时,仅有用来定义虚设通孔106b的位置的光致抗蚀剂图案的轮廓会受到光学效应的影响而使得虚设通孔106b具有较小的孔径,而用来定义被虚设通孔106b围绕的导电通孔106a的位置的光致抗蚀剂图案的轮廓则不会受到光学效应的影响。因此,存储器区域100a中的所有导电通孔106a可具有相同的孔径,以确保存储器元件的效能不受影响。此外,由于虚设通孔106b不作为电连接构件,因此即使虚设通孔106b具有不均一的孔径及/或被缩小的孔径,存储器元件的效能也不会受到影响。举例来说,当所欲形成的存储器元件为磁阻式随机存取存储器时,由于存储器区域100a中的所有导电通孔106a可具有相同且未被缩小的孔径,因此可避免导电通孔106a的电阻过大且不均一,进而可避免磁阻式随机存取存储器的隧穿式磁阻大幅降低。

43.之后,同时参照图1c、图2c与图3c,在介电层104上形成存储器单元108,以形成本实施例的非挥发性存储器元件10。存储器单元108可以是磁阻式随机存取存储器的存储器单元或是其他类型存储器的存储器单元,本发明不对此进行限定。存储器单元108的形成方法为本领域技术人员所熟知,在此不再赘述。基于导电通孔106a的设置,自俯视方向来看,

存储器单元108以阵列方式排列。详细地说,存储器单元108包括位于存储器区域100a中的第一存储器单元108a以及位于虚设区域100b中的第二存储器单元108b。每一个第一存储器单元108a形成于对应的导电通孔106a上方,且与对应的导电通孔106a连接。换句话说,导电通孔106a位于对应的第一存储器单元100a与内连线结构102之间,以电连接对应的第一存储器单元100a与内连线结构102。第二存储器单元108b形成于虚设区域100b中的介电层104上,且不与虚设通孔106b连接。因此,第二存储器单元108b可视为虚设存储器单元。

44.由于第二存储器单元108b被形成为围绕第一存储器单元108a,因此在形成第一存储器单元108a与第二存储器单元108b的过程中,在以光刻制作工艺定义第一存储器单元108a与第二存储器单元108b的位置时,仅有用来定义第二存储器单元108b的位置的光致抗蚀剂图案的轮廓会受到光学效应的影响而使得第二存储器单元108b具有较小的尺寸,而用来定义被第二存储器单元108b围绕的第一存储器单元108a的位置的光致抗蚀剂图案的轮廓则不会受到光学效应的影响。因此,存储器区域100a中的所有第一存储器单元108a可具有相同的尺寸,以确保存储器元件的效能不受影响。此外,由于第二存储器单元108b为虚设存储器单元,因此即使第二存储器单元108b具有不均一的尺寸及/或被缩小的尺寸,存储器元件的效能也不会受到影响。

45.此外,在虚设区域100b中,由于第二存储器单元108b不与虚设通孔106b连接,因此第二存储器单元108b不会与内连线结构102电连接,且因此不会对100a存储器区域中的第一存储器单元108a的操作造成影响。

46.在本实施例中,自俯视方向来看,如图1c所示,一圈的第二存储器单元108b围绕存储器区域100a,且虚设通孔106b位于第二存储器单元108b与第一存储器单元108a之间,以围绕第一存储器单元108a,但本发明不限于此。在其他实施例中,自俯视方向来看,在存储器区域100a的周围可设置多圈的第二存储器单元108b,且虚设通孔106b除了位于第二存储器单元108b与第一存储器单元108a之间之外,还可位于相邻的两圈第二存储器单元108b之间,如图4所示。

47.图5为依照本发明另一实施例所绘示的非挥发性存储器元件的俯视示意图。在本实施例中,与图1c中的元件相同的元件将以相同的符号表示,且不再对其进行说明。此外,本实施例的非挥发性存储器元件的制造流程与图1a至图1c所述的制造流程相同,因此也不再对其进行说明。

48.参照图5,在本实施例中,自俯视方向来看,在存储器区域100a中,相邻两行中的导电通孔106a彼此不对准,且相邻两列中的导电通孔106a彼此不对准。也就是说,在本实施例中,存储器区域100a中的导电通孔106a以近似于八边形阵列的方式排列,而虚设通孔106b围绕以近似于八边形阵列方式排列的导电通孔106a。此外,相邻两行中以及相邻两列中的导电通孔106a之间的距离d5大于相邻的虚设通孔106b与导电通孔106a之间的距离d6。

49.基于上述的布局方式,在形成导电通孔106a与虚设通孔106b的过程中,在以光刻制作工艺定义导电通孔106a与虚设通孔106b的位置时,仅有用来定义虚设通孔106b的位置的光致抗蚀剂图案的轮廓会受到光学效应的影响而使得虚设通孔106b具有较小的孔径,而用来定义被虚设通孔106b围绕的导电通孔106a的位置的光致抗蚀剂图案的轮廓则不会受到光学效应的影响。因此,存储器区域100a中的所有导电通孔106a可具有相同的孔径,以确保存储器元件的效能不受影响。此外,由于虚设通孔106b不作为电连接构件,因此即使虚设

通孔106b具有不均一的孔径及/或被缩小的孔径,存储器元件的效能也不会受到影响。举例来说,当所形成的存储器元件为磁阻式随机存取存储器时,由于存储器区域100a中的所有导电通孔106a可具有相同且为缩小的孔径,因此可避免导电通孔106a的电阻过大且不均一,进而可避免磁阻式随机存取存储器的隧穿式磁阻大幅降低。

50.此外,由于第二存储器单元108b被形成为围绕第一存储器单元108a,因此在形成第一存储器单元108a与第二存储器单元108b的过程中,在以光刻制作工艺定义第一存储器单元108a与第二存储器单元108b的位置时,仅有用来定义第二存储器单元108b的位置的光致抗蚀剂图案的轮廓会受到光学效应的影响而使得第二存储器单元108b具有较小的尺寸,而用来定义被第二存储器单元108b围绕的第一存储器单元108a的位置的光致抗蚀剂图案的轮廓则不会受到光学效应的影响。因此,存储器区域100a中的所有第一存储器单元108a可具有相同的尺寸,以确保存储器元件的效能不受影响。此外,由于第二存储器单元108b为虚设存储器单元,因此即使第二存储器单元108b具有不均一的尺寸及/或被缩小的尺寸,存储器元件的效能也不会受到影响。

51.另外,如同前述,在其他实施例中,自俯视方向来看,在存储器区域100a的周围可设置多圈的第二存储器单元108b,且虚设通孔106b除了位于第二存储器单元108b与第一存储器单元108a之间之外,还可位于相邻的两圈第二存储器单元108b之间。

52.虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1