钝化层蚀刻的改进方法与流程

1.本发明涉及半导体制造领域,特别是涉及一种钝化层蚀刻的改进方法。

背景技术:

2.钝化层蚀刻是半导体生产制造过程中的一个干法蚀刻过程,在顶铝图形形成后再使用cvd的方法覆盖二氧化硅和氮化硅介质,然后用光刻技术形成图形,再干法蚀刻将图形转移至晶圆上。钝化层蚀刻具体可以利用等离子体技术结合物理轰击和化学反应来移除掉特定材料。在量产过程中,偶发性发生wat(wafer acceptance test,晶圆验收测试)测试vt(开启电压)参数异常,其表现为vt片内均匀性偏大。

3.wat vt参数异常超出规范时会导致芯片不能够被正常使用,产生报废或良率损失。

技术实现要素:

4.为了解决器件开启电压异常的问题,有必要提供一种钝化层蚀刻的改进方法。

5.一种钝化层蚀刻的改进方法,包括:步骤a,获取晶圆结构;所述晶圆结构包括衬底、衬底上的金属结构以及覆盖所述金属结构的钝化层;步骤b,光刻形成蚀刻窗口;步骤c,通过所述蚀刻窗口以第一射频功率干法蚀刻所述钝化层,在蚀刻至所述金属结构前停止;步骤d,通过所述蚀刻窗口以第二射频功率继续向下进行干法蚀刻,直至蚀刻至所述金属结构;所述第二射频功率小于所述第一射频功率。

6.上述钝化层蚀刻的改进方法,在钝化层蚀刻至所述金属结构前,降低干法蚀刻的射频功率,从而能够降低干法蚀刻的等离子体开始接触到金属结构时的等离子体电荷密度,改善等离子体损伤,避免等离子体损伤导致器件开启电压异常。

7.在其中一个实施例中,所述第二射频功率是所述步骤c的干法蚀刻产生的等离子体不会对所述金属结构造成等离子体损伤的功率。

8.在其中一个实施例中,所述第二射频功率为400w至600w。

9.在其中一个实施例中,所述金属结构包括导电主体和导电主体上的辅助层,所述步骤d是在蚀刻至所述辅助层后停止,所述步骤d之后还包括:步骤e,通过所述蚀刻窗口以第三射频功率继续向下进行干法蚀刻至所述导电主体,所述第三射频功率大于所述第二射频功率。

10.在其中一个实施例中,所述第一射频功率和第三射频功率相等。

11.在其中一个实施例中,所述第一射频功率和第三射频功率为800w至1500w。

12.在其中一个实施例中,所述导电主体包括铝铜,所述辅助层包括钛层和所述钛层上的氮化钛层。

13.在其中一个实施例中,所述步骤d是在蚀刻至所述氮化钛层后停止。

14.在其中一个实施例中,所述钝化层包括硅氧化物层和硅氧化物层上的硅氮化物层。

15.在其中一个实施例中,所述硅氧化物层包括二氧化硅层,所述硅氮化物层包括氮化硅层。

16.在其中一个实施例中,所述步骤a获取的晶圆结构还包括设于所述金属结构和硅氧化物层之间的蚀刻停止层,所述蚀刻停止层为绝缘介质且材质与所述硅氧化物层不同;所述步骤c是蚀刻至所述蚀刻停止层。

17.在其中一个实施例中,还包括侦测所述步骤c和步骤d的蚀刻生成物的光谱波长的步骤;所述步骤c中在侦测到所述蚀刻停止层的蚀刻生成物的特征光谱波长浓度上升时停止蚀刻,并执行步骤d;所述步骤d在侦测到所述蚀刻停止层的蚀刻生成物的特征光谱波长浓度下降时停止蚀刻,并执行步骤e。

18.在其中一个实施例中,所述蚀刻停止层的材质包括氮化硅;所述步骤c中在侦测到光谱波长的浓度上升时停止蚀刻,并执行步骤d;所述步骤d在侦测到光谱波长的浓度下降时停止蚀刻,并执行步骤e。

19.在其中一个实施例中,所述步骤c和步骤d在相同的设备中进行干法蚀刻。

20.在其中一个实施例中,所述步骤c、步骤d及步骤e在相同的设备中进行干法蚀刻。

21.在其中一个实施例中,所述步骤c和步骤d的蚀刻气体包括cf4、chf3、ar、sf6及n2。

22.在其中一个实施例中,所述步骤b是光刻形成接触孔的蚀刻窗口。

23.在其中一个实施例中,所述金属结构为顶层金属,所述步骤a中获取的晶圆结构还包括顶层金属之前的层次。本技术还提供另一种钝化层蚀刻的改进方法,包括:获取晶圆结构;所述晶圆结构包括衬底、衬底上的金属结构以及覆盖所述金属结构的钝化层;光刻形成蚀刻窗口;通过所述蚀刻窗口以第一射频功率干法蚀刻所述钝化层,在蚀刻至所述金属结构前停止;将等离子体的电荷密度降低至不会对所述金属结构造成等离子体损伤后,继续通过所述蚀刻窗口向下进行干法蚀刻,直至蚀刻至所述金属结构。

24.在其中一个实施例中,所述第二射频功率为400w至600w。

25.在其中一个实施例中,所述金属结构包括导电主体和导电主体上的辅助层,所述步骤d是在蚀刻至所述辅助层后停止,所述步骤d之后还包括:步骤e,通过所述蚀刻窗口以第三射频功率继续向下进行干法蚀刻至所述导电主体,所述第三射频功率大于所述第二射频功率。

26.在其中一个实施例中,所述第一射频功率和第三射频功率相等。

27.在其中一个实施例中,所述第一射频功率和第三射频功率为800w至1500w。

28.在其中一个实施例中,所述导电主体包括铝铜,所述辅助层包括钛层和所述钛层上的氮化钛层。

29.在其中一个实施例中,所述步骤d是在蚀刻至所述氮化钛层后停止。

30.在其中一个实施例中,所述钝化层包括硅氧化物层和硅氧化物层上的硅氮化物层。

31.在其中一个实施例中,所述硅氧化物层包括二氧化硅层,所述硅氮化物层包括氮化硅层。

32.在其中一个实施例中,所述步骤a获取的晶圆结构还包括设于所述金属结构和硅氧化物层之间的蚀刻停止层,所述蚀刻停止层为绝缘介质且材质与所述硅氧化物层不同;所述步骤c是蚀刻至所述蚀刻停止层。

33.在其中一个实施例中,还包括侦测所述步骤c和步骤d的蚀刻生成物的光谱波长的步骤;所述步骤c中在侦测到所述蚀刻停止层的蚀刻生成物的特征光谱波长浓度上升时停止蚀刻,并执行步骤d;所述步骤d在侦测到所述蚀刻停止层的蚀刻生成物的特征光谱波长浓度下降时停止蚀刻,并执行步骤e。

34.在其中一个实施例中,所述蚀刻停止层的材质包括氮化硅;所述步骤c中在侦测到光谱波长的浓度上升时停止蚀刻,并执行步骤d;所述步骤d在侦测到光谱波长的浓度下降时停止蚀刻,并执行步骤e。

35.在其中一个实施例中,所述步骤c和步骤d在相同的设备中进行干法蚀刻。

36.在其中一个实施例中,所述步骤c、步骤d及步骤e在相同的设备中进行干法蚀刻。

37.在其中一个实施例中,所述步骤c和步骤d的蚀刻气体包括cf4、chf3、ar、sf6及n2。

38.在其中一个实施例中,所述步骤b是光刻形成接触孔的蚀刻窗口。

39.在其中一个实施例中,所述金属结构为顶层金属,所述步骤a中获取的晶圆结构还包括顶层金属之前的层次。

附图说明

40.为了更好地描述和说明这里公开的那些发明的实施例和/或示例,可以参考一幅或多幅附图。用于描述附图的附加细节或示例不应当被认为是对所公开的发明、目前描述的实施例和/或示例以及目前理解的这些发明的最佳模式中的任何一者的范围的限制。

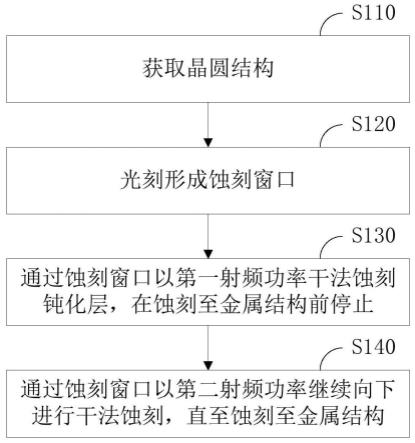

41.图1是一实施例中钝化层蚀刻的改进方法的流程图;

42.图2a至图2e是一实施例中采用图1所示的方法制造器件的过程中器件的剖面示意图;

43.图3a至图3d是一实施例中采用图4所示的方法制造器件的过程中器件的剖面示意图;

44.图4是另一实施例中钝化层蚀刻的改进方法的流程图;

45.图5是一实施例采用钝化层蚀刻的改进方法制成的器件与对比例的wat的开启电压测试结果对比图;

46.图6是另一实施例采用钝化层蚀刻的改进方法制成的器件与对比例的wat的开启电压测试结果对比图。

具体实施方式

47.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的首选实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

48.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

49.应当明白,当元件或层被称为“在...上”、“与...相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或

者可以存在居间的元件或层。相反,当元件被称为“直接在...上”、“与...直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。

50.空间关系术语例如“在...下”、“在...下面”、“下面的”、“在...之下”、“在...之上”、“上面的”等,在这里可为了方便描述而被使用从而描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,然后,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下面”和“在...下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

51.在此使用的术语的目的仅在于描述具体实施例并且不作为本发明的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

52.这里参考作为本发明的理想实施例(和中间结构)的示意图的横截面图来描述发明的实施例。这样,可以预期由于例如制造技术和/或容差导致的从所示形状的变化。因此,本发明的实施例不应当局限于在此所示的区的特定形状,而是包括由于例如制造导致的形状偏差。例如,显示为矩形的注入区在其边缘通常具有圆的或弯曲特征和/或注入浓度梯度,而不是从注入区到非注入区的二元改变。同样,通过注入形成的埋藏区可导致该埋藏区和注入进行时所经过的表面之间的区中的一些注入。因此,图中显示的区实质上是示意性的,它们的形状并不意图显示器件的区的实际形状且并不意图限定本发明的范围。

53.本文所使用的半导体领域词汇为本领域技术人员常用的技术词汇,例如对于p型和n型杂质,为区分掺杂浓度,简易的将p+型代表重掺杂浓度的p型,p型代表中掺杂浓度的p型,p-型代表轻掺杂浓度的p型,n+型代表重掺杂浓度的n型,n型代表中掺杂浓度的n型,n-型代表轻掺杂浓度的n型。

54.发明人对vt片内均匀性偏大的测试结果进行分析,发现该异常和钝化层蚀刻腔体可以一一对应,器件的物理结构无明显差异,发明人认为是等离子体损伤导致的电性异常。

55.等离子体损伤的核心影响因素为在局部区域内等离子体的不平衡性,这种不平衡性是一定存在的,业界对于等离子体损伤的研究大概有以下几个方案:

56.1.针对产品设计端:在新品中加入保护电路,增强芯片的抗等离子体损伤能力。

57.2.针对设备端:优化腔体,使等离子体源更稳定,更均匀。

58.3.针对工艺端:在等离子体刚开始产生的步骤引入渐变过程,避免等离子体突变导致其不稳定,不均匀。

59.其中方案3主要考虑到的是对等离子体起使过程中可能产生的不稳定/不均匀做

改善,例如其将功率由0w提升至2000w,进一步分为0w至500w,500w至1000w,1000w至2000w多个步骤逐步提升的过程。或者将压力稳定过程分为多个步骤逐步变化。其核心思想是减小等离子体工艺条件的突变因素,进而降低等离子体不稳定/不均匀的可能性。

60.在尝试解决等离子体损伤问题的过程中,发明人曾试过减小等离子体工艺条件的突变(起始步骤逐步变化),但实践证明其无效。经分析原因如下:减小等离子体工艺条件突变只适用于起始步骤和工艺变化大的制程,而示例性的制程在钝化层蚀刻的整个过程中工艺条件并无变化,所以只能在起始步骤逐步变化来增强等离子体稳定性,而实验发现无论起始步骤如何优化都不能改善wat的电性表现,说明等离子体损伤并不是发生在起始步骤。

61.基于上述现象,本技术结合钝化层的整个蚀刻过程,考虑改善整个钝化层蚀刻过程的等离子体损伤效应。

62.本技术为了改善整个钝化层蚀刻过程的等离子体损伤效应,必须重点关注蚀刻过程中的关键点,主要从以下几个方面考虑:

63.1.蚀刻工艺条件:示例性的制程在蚀刻过程从开始到结束,工艺条件保持一致无变化。

64.2.对应设备:示例性的制程在蚀刻过程从开始到结束,蚀刻设备无任何报警讯息。

65.3.所蚀刻材料:通过分析发现示例性的制程在整个蚀刻过程中最大的变化是由绝缘材料(氮化硅和二氧化硅)至导体材料(氮化钛和钛和铝铜)。

66.整个蚀刻过程中工艺条件和对应设备均无变化,唯一有变化的是蚀刻的材料在变化。发明人首先通过优化工艺条件确认了改善蚀刻过程中的等离子体损伤效应的效果,经过长期实验最终确定对等离子影响最大的工艺条件为功率,最关键的过程点在绝缘材料到导体材料接触的时刻。该时刻的功率越大,等离子体损伤越严重(发明人使用了强化后的敏感产品进行等离子体损伤验证)。等离子体在整个钝化层蚀刻工艺过程中始终是连续存在的,只要在蚀刻过程接触到金属层之前将功率降低,使等离子体中电荷密度降低,即可改善等离子体损伤效应。发明人基于实际情况设计了一个便于量产和精细化管控的器件结构,及配套的钝化层蚀刻的改进方法。

67.图1是一实施例中钝化层蚀刻的改进方法的流程图,包括下列步骤:

68.s110,获取晶圆结构。

69.参照图2a,晶圆结构包括衬底210、衬底210上的金属结构220以及覆盖金属结构220的钝化层230。衬底210中可以形成有本领域习知的各类器件结构,例如有源区、阱区、接触区等。衬底210上还可以形成有本领域习知的其他器件结构,例如栅极、介质层等。金属结构220可以是顶层金属,例如金属互联线等;衬底210和衬底上形成有顶层金属之前的层次,即顶层金属之前的多道前道加工制程形成的结构。衬底210可以是以下所提到的材料中的至少一种:si、ge、sige、sic、sigec、inas、gaas、inp或者其它iii/v化合物半导体,也可以是这些半导体构成的多层结构等或者为绝缘体上硅(soi)、绝缘体上层叠硅(ssoi)、绝缘体上层叠锗化硅(s-sigeoi)、绝缘体上锗化硅(sigeoi)以及绝缘体上锗(geoi)等。

70.在图2a所示的实施例中,钝化层230包括硅氧化物层232和硅氧化物层上的硅氮化物层234。进一步地,硅氧化物层232可以是二氧化硅层,硅氮化物层234可以是氮化硅层。

71.在本技术的一个实施例中,金属结构220包括导电主体和导电主体上的辅助层。进一步地,导电主体包括铝铜,辅助层包括钛层和钛层上的氮化钛层。

72.s120,光刻形成蚀刻窗口。

73.参见图2b,在钝化层230上光刻形成图形化的光刻胶层240以露出钝化层蚀刻的蚀刻窗口241。

74.光刻胶层240可以采用常用的正胶或负胶材料,并通过曝光、显影等操作进行图形化,从而露出蚀刻窗口241。

75.在本技术的一个实施例中,蚀刻窗口241是接触孔的蚀刻窗口。

76.s130,通过蚀刻窗口以第一射频功率干法蚀刻钝化层,在蚀刻至金属结构前停止。

77.参见图2c,蚀刻掉全部的硅氮化物层234和大部分的硅氧化物层232。在本技术的一个实施例中,是使用时间模式(即蚀刻预设的时长)进行步骤s130的蚀刻。

78.s140,通过蚀刻窗口以第二射频功率继续向下进行干法蚀刻,直至蚀刻至金属结构。

79.在本技术的一个实施例中,是将步骤s130使用的干法蚀刻机台的射频功率调低后,继续对产品进行蚀刻。具体地,我们希望第二射频功率是干法蚀刻产生的等离子体不会对金属结构220造成等离子体损伤的功率。发明人经过实验确认,当功率在800~1000w时,等离子体损伤发生概率会有一个显著的变化,因此蚀刻过程接触到金属结构220时蚀刻机台的射频功率不能太高。在本技术的一个实施例中,第二射频功率为400w至600w,第一射频功率为800w至1500w。

80.上述钝化层蚀刻的改进方法,在钝化层蚀刻至金属结构220前,降低干法蚀刻的射频功率,从而能够降低干法蚀刻的等离子体开始接触到金属结构时的等离子体电荷密度,改善等离子体损伤,避免等离子体损伤导致器件开启电压异常。

81.在本技术的一个实施例中,步骤s140是在蚀刻至金属结构220中的氮化钛层后停止,参见图2d。步骤s140之后还包括步骤s150:通过蚀刻窗口241以第三射频功率继续向下进行干法蚀刻至金属结构220中的铝铜,参见图2e。第三射频功率大于第二射频功率。步骤s140完成后重新采用高功率进行蚀刻,有利于提高蚀刻过程中氮化钛/钛材料和阻挡层光刻胶材料的选择比,避免光刻胶损失过多而导致光刻胶下方被保护的材料在刻蚀时被去除/损伤。

82.在本技术的一个实施例中,第三射频功率为800w至1500w。在本技术的一个实施例中,第一射频功率和第三射频功率相等。可以理解的,步骤s150与步骤s130和s140都是采用同一蚀刻机台进行蚀刻。在本技术的一个实施例中,钝化层蚀刻是采用amat公司的emax设备进行。

83.在本技术的一个实施例中,步骤s140的蚀刻使用终点模式。在本技术的一个实施例中,步骤s150的蚀刻采用时间模式。

84.在本技术的一个实施例中,步骤s130、s140及s150使用的蚀刻气体一共包括cf4、chf3、ar、sf6及n2。

85.在本技术的一个实施例中,步骤s130、s140及s150除了rf功率以外,其他工艺条件均相同。

86.使用优化后的钝化层蚀刻工艺,用产品进行分片验证发现,当老工艺发生等离子体损伤影响产品wat vt时,新的工艺条件可以有效改善此现象,如图5和图6所示。这证明上述钝化层蚀刻的改进方法可以有效改善钝化层蚀刻的等离子体损伤效应。基于此,已经证

明高功率的等离子体直接接触到金属结构220是导致等离子体损伤的主要因素,在蚀刻到金属结构220前转换为低功率是一个行之有效的方法。

87.图4是另一实施例中钝化层蚀刻的改进方法的流程图。该实施例中在金属结构上增设了蚀刻停止层,便于对干法蚀刻的rf功率由高变为低的时间点进行更准确的控制。图4所示实施例的方法包括下列步骤:

88.s410,获取晶圆结构。

89.参见图3a,晶圆结构包括衬底310、衬底310上的金属结构320、覆盖金属结构320的蚀刻停止层324以及蚀刻停止层324上的钝化层330。

90.衬底310中可以形成有本领域习知的各类器件结构,例如有源区、阱区、接触区等,衬底310上还可以形成有本领域习知的其他器件结构,例如栅极、介质层等。衬底310可以是以下所提到的材料中的至少一种:si、ge、sige、sic、sigec、inas、gaas、inp或者其它iii/v化合物半导体,也可以是这些半导体构成的多层结构等或者为绝缘体上硅(soi)、绝缘体上层叠硅(ssoi)、绝缘体上层叠锗化硅(s-sigeoi)、绝缘体上锗化硅(sigeoi)以及绝缘体上锗(geoi)等。金属结构320可以是顶层金属,例如金属互联线等。

91.在图3a所示的实施例中,钝化层330包括硅氧化物层332和硅氧化物层上的硅氮化物层334。进一步地,硅氧化物层332可以是二氧化硅层,硅氮化物层334可以是氮化硅层。

92.蚀刻停止层324为绝缘介质,且需要与硅氧化物层332有高的蚀刻选择比,因此选择可以与硅氧化物层332有高的蚀刻选择比的材料作为蚀刻停止层324。在本技术的一个实施例中,蚀刻停止层324为氮化硅层。

93.在本技术的一个实施例中,金属结构320包括导电主体和导电主体上的辅助层。进一步地,导电主体包括铝铜,辅助层包括钛层和钛层上的氮化钛层。

94.s420,光刻形成蚀刻窗口。

95.在本技术的一个实施例中,蚀刻窗口341是接触孔的蚀刻窗口。

96.s430,通过蚀刻窗口以第一射频功率干法蚀刻钝化层,在蚀刻至蚀刻停止层时停止。

97.先使用高功率蚀刻,蚀刻掉蚀刻窗口341位置处的硅氧化物层332和硅氮化物层334,停在蚀刻停止层324上。具体地,在蚀刻过程中侦测蚀刻生成物的光谱波长,在侦测到蚀刻停止层324的蚀刻生成物的特征光谱波长的浓度上升时停止蚀刻。

98.在本技术的一个实施例中,基于实际蚀刻过程,在蚀刻过程中过滤掉硅氮化物层334的光谱信号,在侦测到光谱波长的浓度上升时停止步骤s430的蚀刻(是蚀刻停止层324为氮化硅层时的蚀刻生成物cn的特征光谱)。

99.s440,通过蚀刻窗口以第二射频功率蚀刻蚀刻停止层,直至蚀刻至金属结构。

100.转换为低功率蚀刻,蚀刻蚀刻停止层324。在侦测到蚀刻停止层324的蚀刻生成物的特征光谱波长的浓度下降时停止蚀刻。在本技术的一个实施例中,在侦测到光谱波长的浓度下降时停止步骤s440的蚀刻。

101.在本技术的另一个实施例中,步骤s440的蚀刻采用时间模式。对于一部分半导体产品,可能出现由于产品设计问题导致特征光谱信号弱的情况,也可以按照固定时间来进行蚀刻。

102.在本技术的一个实施例中,第二射频功率为400w至600w,第一射频功率为800w至1500w。

103.上述钝化层蚀刻的改进方法,增设了一层薄的蚀刻停止层324,使得干法蚀刻至蚀刻停止层324时蚀刻速率显著降低,从而能够保证在蚀刻至金属结构320前切换至低rf功率,实现稳定的工艺控制。

104.在本技术的一个实施例中,步骤s440是在蚀刻至金属结构320中的氮化钛层后停止,参见图3c。步骤s440之后还包括步骤s450:通过蚀刻窗口341以第三射频功率继续向下进行干法蚀刻至铝铜。参见图3d,基于实际产品需求,设定对应的过蚀刻量,蚀刻金属结构320的铝铜上的钛和氮化钛。第三射频功率大于第二射频功率。在本技术的一个实施例中,第三射频功率为800w至1500w。在本技术的一个实施例中,第一射频功率和第三射频功率相等。可以理解的,步骤s450与步骤s430和s440都是采用同一蚀刻机台进行蚀刻。

105.应该理解的是,虽然本技术的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且本技术的流程图中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

106.在本说明书的描述中,参考术语“有些实施例”、“其他实施例”、“理想实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

107.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

108.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1