一种LED芯片的制作方法

一种led芯片

技术领域

1.本发明涉及半导体技术领域,更为具体地说,涉及一种led(light emitting diode,发光二极管)芯片。

背景技术:

2.随着发光二极管技术的发展,现有发光二极管被广泛应用于电子、光学等领域,更是在照明、显示、数码方面有着长足的发展。并且,随着led(light emitting diode,发光二极管)应用端的逐渐扩大,市场对led性能要求也越来越高。

技术实现要素:

3.有鉴于此,本发明提供了一种led芯片,有效解决现有技术存在的技术问题,保证led芯片的性能优良。

4.为实现上述目的,本发明提供的技术方案如下:

5.一种led芯片,包括外延结构,所述外延结构包括:

6.第一半导体层;

7.位于所述第一半导体层一侧上的电流阻挡层;

8.位于所述电流阻挡层背离所述第一半导体层上的第二半导体层,所述第一半导体层和所述第二半导体层的导电类型相同;

9.位于所述第二半导体层背离所述第一半导体层上的位错阻挡层;

10.位于所述位错阻挡层背离所述第一半导体层上的有源层,其中,在所述第一半导体层朝向所述有源层方向,所述有源层包括叠加的至少一个重复层,所述重复层包括叠加的势垒层和势阱层;

11.位于所述有源层背离所述第一半导体层上的第三半导体层,所述第三半导体层与所述第一半导体层的导电类型不同。

12.可选的,所述外延结构还包括:

13.位于所述有源层与所述第三半导体层之间的尾垒层;

14.位于所述尾垒层与所述第三半导体层之间的低温层;

15.位于所述低温层与所述第三半导体层之间的电子阻挡层;

16.位于所述第三半导体层背离所述第一半导体层一侧的欧姆接触层。

17.可选的,所述第一半导体层、所述电流阻挡层、所述第二半导体层、所述位错阻挡层、所述势垒层、所述势阱层、所述第三半导体层、所述尾垒层、所述低温层、所述电子阻挡层和所述欧姆接触层的材质均包括al组分;

18.其中,所述尾垒层的al组分大于所述位错阻挡层的al组分,所述位错阻挡层的al组分大于所述电子阻挡层的al组分,所述电子阻挡层的al组分大于所述电流阻挡层的al组分,所述电流阻挡层的al组分大于所述势垒层的al组分;

19.及所述势垒层的al组分大于或等于所述第一半导体层、所述第二半导体层、所述

势阱层、所述低温层、所述第三半导体层和所述欧姆接触层各自相应的al组分。

20.可选的,所述外延结构还包括:位于所述第一半导体层背离所述电流阻挡层一侧的辅助位错阻挡层。

21.可选的,所述辅助位错阻挡层、所述第一半导体层、所述电流阻挡层、所述第二半导体层、所述位错阻挡层、所述势垒层、所述势阱层、所述第三半导体层、所述尾垒层、所述低温层、所述电子阻挡层和所述欧姆接触层的材质均包括al组分;

22.其中,所述尾垒层的al组分大于所述辅助位错阻挡层的al组分,所述辅助位错阻挡层的al组分大于所述位错阻挡层的al组分,所述位错阻挡层的al组分大于所述电子阻挡层的al组分,所述电子阻挡层的al组分大于所述电流阻挡层的al组分,所述电流阻挡层的al组分大于所述势垒层的al组分;

23.及所述势垒层的al组分大于或等于所述第一半导体层、所述第二半导体层、所述势阱层、所述低温层、所述第三半导体层和所述欧姆接触层各自相应的al组分。

24.可选的,所述外延结构还包括:位于所述辅助位错阻挡层背离所述第一半导体层一侧的非掺杂层;

25.位于所述非掺杂层背离所述第一半导体层一侧的缓冲层。

26.可选的,所述第一半导体层和所述第二半导体层的厚度,大于所述辅助位错阻挡层和所述位错阻挡层的厚度。

27.可选的,所述势阱层和所述欧姆接触层的材质还包括in组分,其中,所述势阱层的in组分大于或等于欧姆接触层的in组分。

28.可选的,所述led芯片包括:位于所述第一半导体层背离所述电流阻挡层一侧的透明导电层;

29.位于所述透明导电层背离所述电流阻挡层一侧的第一电极;

30.以及,所述led芯片包括:位于所述欧姆接触层背离所述第三半导体层一侧的金属反射层;

31.位于所述金属反射层背离所述第三半导体层一侧的键合层;

32.位于所述键合层背离所述第三半导体层一侧的导电衬底;

33.位于所述导电衬底背离所述第三半导体层一侧的第二电极。

34.可选的,所述led芯片包括:位于所述欧姆接触层背离所述第三半导体层一侧的金属反射层;

35.位于所述金属层反射层背离所述第三半导体层一侧的介质层,其中,在所述介质层一侧,所述led芯片包括至少一个第一通孔和至少一个第二通孔,所述第一通孔裸露所述第一半导体层,所述第二通孔裸露所述金属反射层,且所述介质层覆盖所述第一通孔的侧壁;

36.通过所述第一通孔与所述第一半导体层接触的第一电极,及通过所述第二通孔与所述金属反射层接触的第二电极;

37.以及,所述led芯片包括:位于所述外延结构背离所述第一电极一侧的外延衬底。

38.相较于现有技术,本发明提供的技术方案至少具有以下优点:

39.发明提供了一种led芯片,包括外延结构,所述外延结构包括:第一半导体层;位于所述第一半导体层一侧上的电流阻挡层;位于所述电流阻挡层背离所述第一半导体层上的

第二半导体层,所述第一半导体层和所述第二半导体层的导电类型相同;位于所述第二半导体层背离所述第一半导体层上的位错阻挡层;位于所述位错阻挡层背离所述第一半导体层上的有源层,其中,在所述第一半导体层朝向所述有源层方向,所述有源层包括叠加的至少一个重复层,所述重复层包括叠加的势垒层和势阱层;位于所述有源层背离所述第一半导体层上的第三半导体层,所述第三半导体层与所述第一半导体层的导电类型不同。

40.由上述内容可知,本发明提供的技术方案,通过设置位错阻挡层能够减小led芯片的位错密度,同时能够实现应力释放功能,进而降低led芯片外延生长过程中出现翘曲的情况的几率。以及通过设置电流阻挡层能够实现led芯片更好的电流阻挡效果,进而保证led芯片的性能优良。

附图说明

41.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

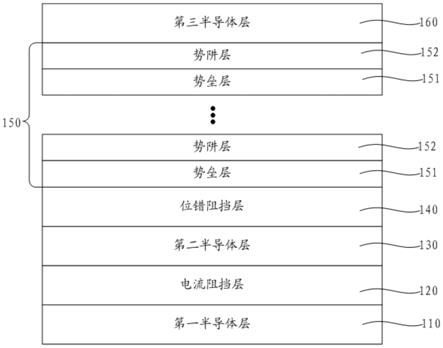

42.图1为本发明实施例提供的一种led芯片的结构示意图;

43.图2为本发明实施例提供的另一种led芯片的结构示意图;

44.图3为本发明实施例提供的又一种led芯片的结构示意图;

45.图4为本发明实施例提供的又一种led芯片的结构示意图;

46.图5为本发明实施例提供的又一种led芯片的结构示意图;

47.图6为本发明实施例提供的又一种led芯片的结构示意图。

具体实施方式

48.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

49.正如背景技术所述,随着发光二极管技术的发展,现有发光二极管被广泛应用于电子、光学等领域,更是在照明、显示、数码方面有着长足的发展。并且,随着led(light emitting diode,发光二极管)应用端的逐渐扩大,市场对led性能要求也越来越高。

50.基于此,本发明实施例提供了一种led芯片,有效解决现有技术存在的技术问题,保证led芯片的性能优良。

51.为实现上述目的,本发明实施例提供的技术方案如下,具体结合图1至图6对本发明实施例提供的技术方案进行详细的描述。

52.参考图1所示,为本发明实施例提供的一种led芯片的结构示意图,其中,led芯片包括外延结构,所述外延结构包括:

53.第一半导体层110。

54.位于所述第一半导体层110一侧上的电流阻挡层120。

55.位于所述电流阻挡层120背离所述第一半导体层110上的第二半导体层130,所述

第一半导体层110和所述第二半导体层130的导电类型相同。

56.位于所述第二半导体层130背离所述第一半导体层110上的位错阻挡层140。

57.位于所述位错阻挡层140背离所述第一半导体层110上的有源层150,其中,在所述第一半导体层110朝向所述有源层150方向,所述有源层150包括叠加的至少一个重复层,所述重复层包括叠加的势垒层151和势阱层152。

58.位于所述有源层150背离所述第一半导体层110上的第三半导体层160,所述第三半导体层160与所述第一半导体层110的导电类型不同。

59.在本发明一实施例中,本发明所提供的第一半导体层和第二半导体层可以为n型半导体层,其中第三半导体层为p型半导体层,对此本发明不做具体限制,需要根据实际应用进行具体设置。

60.可以理解的,本发明实施例提供的技术方案,通过设置位错阻挡层能够减小led芯片的位错密度,同时能够实现应力释放功能,进而降低led芯片外延生长过程中出现翘曲的情况的几率。以及通过设置电流阻挡层能够实现led芯片更好的电流阻挡效果,进而保证led芯片的性能优良。

61.本发明还可以通过设置功能层以对外延结构进行优化,进一步提高led芯片的性能。具体如图2所示,为本发明实施例提供的另一种led芯片的结构示意图,其中,本发明实施例提供的所述外延结构还包括:

62.位于所述有源层150与所述第三半导体层160之间的尾垒层170。

63.位于所述尾垒层170与所述第三半导体层160之间的低温层180,其中低温层180的生长工艺温度小于尾垒层170的生长工艺温度。

64.位于所述低温层180与所述第三半导体层160之间的电子阻挡层190。

65.位于所述第三半导体层160背离所述第一半导体层110一侧的欧姆接触层200。

66.在本发明一实施例中,本发明提供的所述第一半导体层、所述电流阻挡层、所述第二半导体层、所述位错阻挡层、所述势垒层、所述势阱层、所述第三半导体层、所述尾垒层、所述低温层、所述电子阻挡层和所述欧姆接触层的材质均包括al组分。

67.其中,所述尾垒层的al组分大于所述位错阻挡层的al组分,所述位错阻挡层的al组分大于所述电子阻挡层的al组分,所述电子阻挡层的al组分大于所述电流阻挡层的al组分,所述电流阻挡层的al组分大于所述势垒层的al组分。

68.及所述势垒层的al组分大于或等于所述第一半导体层、所述第二半导体层、所述势阱层、所述低温层、所述第三半导体层和所述欧姆接触层各自相应的al组分。

69.以及,本发明实施例提供的所述势阱层和所述欧姆接触层的材质还包括in组分,其中,所述势阱层的in组分大于或等于欧姆接触层的in组分。

70.可以理解的,本发明实施例通过优化第一半导体层、电流阻挡层、第二半导体层、位错阻挡层、势垒层、势阱层、第三半导体层、尾垒层、低温层、电子阻挡层和欧姆接触层中al组分的大小关系,即通过对外延结构中各层包括al组分的高低设计,实现外延结构生长的可控性,进一步实现外延结构应力释放且降低外延生长翘曲的目的,进一步提高led芯片的性能。

71.本发明实施例提供的led芯片可以为垂直型led芯片。如图3所示,为本发明实施例提供的又一种led芯片的结构示意图,其中,图3所示led芯片包括图2所示led芯片中的外延

结构。以及,本发明图3提供的所述led芯片包括:位于所述第一半导体层110背离所述电流阻挡层120一侧的透明导电层210。

72.位于所述透明导电层背210离所述电流阻挡层120一侧的第一电极221。

73.以及,所述led芯片包括:位于所述欧姆接触层200背离所述第三半导体层160一侧的金属反射层230。

74.位于所述金属反射层230背离所述第三半导体层160一侧的键合层240。

75.位于所述键合层240背离所述第三半导体层160一侧的导电衬底250。

76.位于所述导电衬底250背离所述第三半导体层160一侧的第二电极222。

77.在本发明一实施例中,本发明提供的透明导电层层的材质可以为ito,导电衬底的材质可以为硅,对此本发明不做具体限制,需要根据实际应用进行具体选取。

78.在图2所示led芯片的外延结构的基础上,本发明还可以对外延结构进一步优化。如图4所示,为本发明实施例提供的又一种led芯片的结构示意图,其中,在图2所示led芯片的外延结构的基础上,本发明图4所示所述外延结构还包括:位于所述第一半导体层110背离所述电流阻挡层120一侧的辅助位错阻挡层260,通过辅助位错阻挡层260进一步降低外延结构的位错密度,提高外延结构的生长质量。

79.在本发明一实施例中,所述辅助位错阻挡层、所述第一半导体层、所述电流阻挡层、所述第二半导体层、所述位错阻挡层、所述势垒层、所述势阱层、所述第三半导体层、所述尾垒层、所述低温层、所述电子阻挡层和所述欧姆接触层的材质均包括al组分。

80.其中,所述尾垒层的al组分大于所述辅助位错阻挡层的al组分,所述辅助位错阻挡层的al组分大于所述位错阻挡层的al组分,所述位错阻挡层的al组分大于所述电子阻挡层的al组分,所述电子阻挡层的al组分大于所述电流阻挡层的al组分,所述电流阻挡层的al组分大于所述势垒层的al组分。

81.及所述势垒层的al组分大于或等于所述第一半导体层、所述第二半导体层、所述势阱层、所述低温层、所述第三半导体层和所述欧姆接触层各自相应的al组分。

82.以及,本发明实施例提供的所述势阱层和所述欧姆接触层的材质还包括in组分,其中,所述势阱层的in组分大于或等于欧姆接触层的in组分。及,本发明实施例提供的所述第一半导体层和所述第二半导体层的厚度,大于所述辅助位错阻挡层和所述位错阻挡层的厚度;其中,本发明实施例提供的第一半导体层和第二半导体层的厚度可以为微米级,其中第一半导体层和第二半导体层的厚度可以大于或等于1微米;及辅助位错阻挡层和位错阻挡层的厚度可以为纳米级,其中辅助位错阻挡层和位错阻挡层的厚度可以小于或等于100纳米,对此具体厚度数值本发明实施例不做限制。

83.进一步如图5所示,为本发明实施例提供的又一种led芯片的结构示意图,其中在图4所示led芯片的外延结构的基础上,本发明图5所示所述外延结构还包括:位于所述辅助位错阻挡层260背离所述第一半导体层110一侧的非掺杂层270。及位于所述非掺杂层270背离所述第一半导体层110一侧的缓冲层280,进而通过缓冲层280和非掺杂层270的生长,提高外延结构的晶体生长质量。

84.本发明实施例提供的led芯片可以为倒装型led芯片。如图6所示,为本发明实施例提供的又一种led芯片的结构示意图,其中图6所示led芯片可以包括图5所示led芯片中的外延结构。以及,本发明图6提供的所述led芯片包括:位于所述欧姆接触层200背离所述第

三半导体层160一侧的金属反射层290。

85.位于所述金属层反射层290背离所述第三半导体层160一侧的介质层300,其中,在所述介质层300一侧,所述led芯片包括至少一个第一通孔和至少一个第二通孔,所述第一通孔裸露所述第一半导体层110,所述第二通孔裸露所述金属反射层290,且所述介质层300覆盖所述金属反射层290的表面及延伸覆盖所述第一通孔的侧壁。

86.通过所述第一通孔与所述第一半导体层110接触的第一电极311,及通过所述第二通孔与所述金属反射层290接触的第二电极312;其中第一电极311和第二电极312可以通过介质层300实现隔离。

87.以及,所述led芯片包括:位于所述外延结构背离所述第一电极311一侧的外延衬底320。

88.在本发明一实施例中,本发明所提供的金属反射层的材质可以为金或银,或者其他材质。及本发明实施例提供的外延衬底可以为al2o3或者其他材质。及如图6所示本发明实施例提供的介质层300的材质可以为sin,对此本发明不做具体限制。

89.在本发明上述任意一实施例中,本发明提供的led芯片可以为uv(紫外)

‑

led芯片。其中,本发明实施例提供的缓冲层的材质可以为algan;非掺杂层的材质可以为algan;辅助位错阻挡层的材质可以为algan;第一半导体层的材质可以为algan;电流阻挡层的材质可以为algan;第二半导体层的材质可以为algan;位错阻挡层的材质可以为algan;势垒层的材质可以为algan;势阱层的材质可以为algan或alingan;尾垒层的材质可以为algan;低温层的材质可以为algan;电子阻挡层的材质可以为algan;第三半导体层的材质可以为algan;欧姆接触层的材质可以为algan或alingan,对此本发明不做具体限制。

90.发明实施例提供了一种led芯片,包括外延结构,所述外延结构包括:第一半导体层;位于所述第一半导体层一侧上的电流阻挡层;位于所述电流阻挡层背离所述第一半导体层上的第二半导体层,所述第一半导体层和所述第二半导体层的导电类型相同;位于所述第二半导体层背离所述第一半导体层上的位错阻挡层;位于所述位错阻挡层背离所述第一半导体层上的有源层,其中,在所述第一半导体层朝向所述有源层方向,所述有源层包括叠加的至少一个重复层,所述重复层包括叠加的势垒层和势阱层;位于所述有源层背离所述第一半导体层上的第三半导体层,所述第三半导体层与所述第一半导体层的导电类型不同。

91.由上述内容可知,本发明实施例提供的技术方案,通过设置位错阻挡层能够减小led芯片的位错密度,同时能够实现应力释放功能,进而降低led芯片外延生长过程中出现翘曲的情况的几率。以及通过设置电流阻挡层能够实现led芯片更好的电流阻挡效果,进而保证led芯片的性能优良。

92.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1