用于制造具有嵌入式迹线层的多层电路结构的方法与流程

1.本发明涉及集成电路与封装领域,并且涉及一种用于制造多层电路结构的方法及由其制造的结构。

背景技术:

2.随着消费电子及通讯产品具有更轻、更薄、更高效率的趋势,电子产品的主板所使用的电路基板需要具有更高的布局密度。在电子产品中,电路基板,例如用于封装集成电路(ic或芯片)的印刷电路板(pcb)也起着重要的作用。随着芯片的触点数量和触点密度的增加,用于封装芯片的电路基板的触点数量和触点密度也相应增加。因此,对具有更高布局密度的电路基板的要求是持续的需要。

3.目前,在电路基板上堆叠多个图案化导电层和多个介电层的方法包括层压过程和堆积过程。这些过程包括在图案化电路层的表面上层压介电层;然后镀通孔(pth)或过孔用作连接位于不同介电层上的图案化导电层的通道。

4.美国专利号9,237,643b2公开了一种用于在一面上具有嵌入式电路的电路板的常规制造过程。该制造过程包括:i)提供在两个外表面上均具有介电层的芯板,ii)通过激光烧蚀在一个外表面上形成精细电路凹槽(即沟槽)和至少一个通孔或过孔;iii)通过电镀用导电材料填充精细电路凹槽和通孔和/或过孔;iv)例如通过研磨去除过量导电材料以在芯板的一个表面上形成嵌入式精细电路图案。现在,芯板的覆盖有未图案化导电层的另一表面可以通过减成过程、加成过程或半加成过程进一步加工以形成图案化导电层。最后,可以在每个外表面上形成图案化的阻焊层以完成电路板结构的制造。

5.美国专利号8,164,004b2公开了一种用于在芯板10的两面上均具有嵌入式电路11a和11b的电路板(见图1)的类似制造过程。该制作过程包括:i)在芯板中形成通孔12,ii)通过激光烧蚀在芯板的两个相反表面上分别形成两个凹入图案,iii)通过电镀用导电材料填充通孔和凹入图案,iv)分别通过刻蚀或抛光将电路图案平坦化至与芯板的两个表面齐平,以得到嵌入式电路11a和11b。

6.根据上述制造过程,通过激光烧蚀在芯板的一个或两个表面上在介电材料中形成电路图案。激光烧蚀过程的缺点之一是过程缓慢,因此产出低,并导致生产成本增加。另一个问题是通过激光烧蚀形成的电路11a和11b包括具有倾斜侧壁的梯形与具有竖直侧壁的期望矩形的沟槽轮廓(见图1)。所得的具有倾斜侧壁的图案电路预期增加高速和高频信号传输的信号损失。因此,电路板制造商热切寻求用于制造具有高产出的嵌入式电路结构的基板的新方法并提供适合高速和高频应用的基板。

技术实现要素:

7.本发明涉及一种用于制造具有嵌入式迹线层的多层电路结构的方法及由此制成的多层电路结构。

8.根据本发明的第一方面,提供一种用于制造多层电路结构的方法,其包括:

9.(i)提供具有至少一层现有导体的基板,其中所述基板为单面pcb、双面pcb或封装基板;

10.(ii)形成覆盖所述现有导体的介电层;

11.(iii)在所述介电层上形成金属层;

12.(iv)通过光成像将所述金属层图案化以形成金属掩模;

13.(v)等离子蚀刻所述介电层,以在所述介电层的表面上在未被所述金属掩模遮蔽的区域中形成包含多个沟槽的凹入图案(indent pattern);

14.(vi)任选地,通过化学蚀刻或等离子蚀刻去除所述金属硬掩模;

15.(vii)通过激光钻孔或等离子蚀刻形成至少一个过孔以露出下方的现有导体的一部分;

16.(viii)沉积导电金属,完全填充所述图案化介电层,以形成嵌入式迹线层;以及

17.(ix)将步骤(viii)中的过量导电金属平坦化,以获得嵌入在所述基板的介电层中的新电路;

18.其中

19.步骤(ii)-(ix)可以重复多次以获得多层电路结构,

20.步骤(ii)和(iii)通过在步骤(i)的所述基板上层压金属包层而组合,其中所述金属包层包含步骤(ii)的介电层和步骤(iii)的金属层,以及

21.当所述基板为具有至少一个通孔的双面pcb时,则步骤(ii)-(ix)适用于位于所述基板两面上的现有导体,并且所述通孔填充有包含cu或cu合金的金属材料或包含环氧树脂或酚醛树脂的有机聚合物。

22.在一个实施方案中,在本发明的方法中,其中,通过光成像将每个金属层图案化的步骤(iv)包括:

23.(a)在所述金属层上涂覆或层压光致抗蚀剂层,

24.(b)将所述光致抗蚀剂图案化,

25.(c)通过等离子蚀刻或湿法化学蚀刻,蚀刻暴露区域中的金属层,以得到金属掩模;以及

26.(d)通过剥离或蚀刻去除剩余的光致抗蚀剂图案。

27.根据本发明的第二方面,提供一种由本发明的方法制造的多层电路结构,其包括:

28.基板,所述基板具有至少一层现有导体,其中所述基板为单面pcb、双面pcb或封装基板;

29.介电层,所述介电层具有形成在所述基板的现有导体的顶部上的嵌入式新电路;

30.其中

31.所述基板是厚度为约40μm至约800μm的单面印刷电路板;

32.所述基板是具有至少一个通孔的双面印刷电路板,所述通孔填充有金属材料或有机聚合物,并且所述双面印刷电路板具有约40μm至约800μm的厚度;或者

33.所述基板是封装基板,所述封装基板装载有至少一个芯片及多个暴露铜凸块,并且所述封装基板具有约100μm至约300μm的厚度;

34.所述介电层具有约10μm至约80μm的厚度;

35.所述新电路具有约5μm至约50μm的嵌入深度,由填充有导电金属的多个沟槽和过

孔组成,每个沟槽具有约5μm至约2500μm的宽度,并且每个过孔具有约20μm至约250μm的直径。

36.参考以下附图、描述、实施例和所附权利要求,本发明的各种其他特征、方面和优点将变得更加明显。包括以下附图以更好地理解本发明,并且以下附图包含在本说明书中并构成本说明书的一部分。

附图说明

37.图1展示了通过常规制造过程制造的在芯板的两个表面上具有嵌入式电路的电路板,该电路板具有梯形沟槽轮廓。

38.图2a至图2i为展示根据本发明第一实施方案的用于制造多层电路结构的方法的剖面流程图。

39.图3a至图3i为展示根据本发明第二实施方案的用于制造多层电路结构的方法的剖面流程图。

40.图4a至图4h为展示根据本发明第三实施方案的用于制造多层电路结构的方法的剖面流程图。

41.图5a至图5i为展示根据本发明第四实施方案的用于制造多层电路结构的方法的剖面流程图。

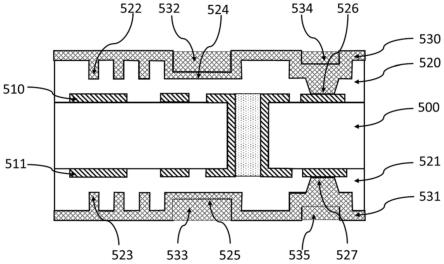

42.图6a至图6f为展示根据本发明第五实施方案的用于制造多层电路结构的方法的剖面流程图。

具体实施方式

43.除非另外说明,本文所提及的所有出版物、专利申请、专利和其他参考文献,出于所有目的通过引用以其整体明确地结合在此,如同完全阐述的一样。

44.除非另有定义,否则本文所使用的所有技术和科学术语均具有与本发明所属领域普通技术人员所通常理解的相同含义。在冲突的情况下,则以本说明书,包括定义为准。

45.除非另外说明,所有的百分比、份数、比率等都是按重量计。

46.如本文中所使用,术语“由

…

制得”与“包含”同义。如在此所用,术语“包含”、“包括”、“具有”、“含有”或其任何其他变型均旨在涵盖非排他性的包含。例如,包括要素列表的组合物、工艺、方法、制品或设备不必仅限于那些要素,而是可包括未明确列出的或此种组合物、工艺、方法、制品或设备所固有的其他要素。

47.连接短语“由

……

组成”排除任何未指出的元素、步骤或成分。如果在权利要求中,则此种短语将使权利要求为封闭式,使其不包含除那些描述的材料以外的材料,但与其相关的常规杂质除外。当短语“由

……

组成”出现在权利要求的特征部分的句子中,而非紧接前序部分时,则它仅仅限制所述句子中所述的要素;其他元素不作为整体从所述权利要求中被排除。

48.连接短语“基本上由

…

组成”用于限定除了字面讨论的那些以外还包括材料、步骤、特征、组分、或元素的组合物、方法、或设备,前提是这些附加的材料、步骤、特征、组分、或元素不会实质影响要求保护的发明的一个或多个基本特征和新颖特征。术语“基本上由

…

组成”居于“包含”和“由

…

组成”中间。

49.术语“包括”旨在包括由术语“基本上由

……

组成”和“由

……

组成”所涵盖的实施方案。类似地,术语“基本上由

……

组成”旨在包括由术语“由

……

组成”所涵盖的实施方案。

50.当量、浓度、或者其他值或参数以范围、优选范围、或一系列上限优选值和下限优选值给出时,这应当被理解为具体公开了由任何范围上限或优选值与任何范围下限或优选值的任一配对所形成的所有范围,而不论所述范围是否被单独公开。例如,当陈述“1至5”的范围时,所述的范围应解释为包括“1至4”、“1至3”、“1至2”、“1至2和4至5”、“1至3和5”等范围。当在此描述数值范围时,除非另行说明,所述范围旨在包括其端点,以及所述范围中的所有整数和分数。

51.当术语“约”在描述范围的值或端点中使用时,本公开应被理解为包括被提及的特定值或端点。

52.此外,除非有相反的明确说明,否则“或”是指包含性的“或”,而不是指排他性的“或”。例如,以下中的任一项均满足条件a“或”b:a为真(或存在)且b为假(或不存在),a为假(或不存在)且b为真(或存在),以及a和b均为真(或存在)。

53.本发明的如在发明内容中所述的实施方案包括本文描述的任何其他实施方案,可以以任何方式组合。

54.下文详细描述本发明。

55.第一实施方案

56.在本发明的第一实施方案中,描述一种用于制造具有双面导电层的多层电路结构的方法。图2a至图2i是展示根据本发明第一实施方案的步骤的剖面流程图。

57.参照图2a,根据本方法的步骤(i),提供单面pcb。基板包含介电芯100和介电芯表面上的现有电路110。

58.在一个实施方案中,基板具有约40μm至约800μm的厚度,并且源自具有包含增强树脂的基片或涂树脂铜(rcc)箔的铜箔层压板,并且所述树脂选自环氧树脂、酚醛树脂、双马来酰亚胺-三嗪(bt)树脂、聚酰亚胺(pi)、氰酸酯树脂(ce)、聚苯醚(ppe)、液晶聚合物(lcp)、聚四氟乙烯(ptfe)或它们的混合物。参照图2b,根据本方法的步骤(ii),通过在电路110上涂覆热固化聚合物来形成介电层120。步骤(ii)的介电层通常具有约10μm至约80μm的厚度。

59.在一个实施方案中,热固化聚合物选自环氧树脂、双马来酰亚胺-三嗪(bt)树脂、聚酰亚胺(pi)、氰酸酯树脂(ce)、聚苯醚(ppe)、液晶聚合物(lcp)、聚四氟乙烯(ptfe)及它们的混合物。

60.在另一实施方案中,介电层还包含增强材料或多种填料。

61.在又一实施方案中,所述增强材料为纤维或织物形式,并且包括e-玻璃、s-玻璃、石英、陶瓷或芳族聚酰胺。

62.在其他实施方案中,所述多种填料是包括氧化硅、氧化铝、氮化硼或它们的混合物的颗粒;并且具有约1μm至约20μm的平均直径。

63.参照图2c,根据本方法的步骤(iii),在介电层120的顶部沉积金属层130。所述金属层通常具有约0.1μm至约15μm的厚度。

64.在一个实施方案中,所述金属层通过物理气相沉积(pvd)、化学气相沉积(cvd)或化学镀形成。注意,在pcb制造行业中,pvd方法也称为“溅射(sputtering)”。

65.在一个实施方案中,金属层包含cu、ni、ti、w、al、cr、co、ag、au、pd及它们的合金。在另一实施方案中,金属层包含cu和cu合金。

66.参照图2d,根据本方法的步骤(iv),通过光成像将金属层130图案化,以在介电层120的表面上形成金属掩模132。下面详细描述用于形成金属掩模132的光成像过程。

67.根据本方法,光成像过程包括:

68.(a)在相应金属层上涂覆或层压光致抗蚀剂层,

69.(b)将所述光致抗蚀剂图案化,

70.(c)通过等离子蚀刻或湿法化学蚀刻,蚀刻暴露区域中的金属层,以得到金属掩模;以及

71.(d)通过剥离或蚀刻去除剩余的光致抗蚀剂图案。

72.参照图2e,根据本方法的步骤(v),然后在未被金属掩模132掩蔽的区域通过等离子蚀刻将介电层120图案化,以在介电质的表面形成包括多个沟槽122和焊盘124的凹入图案。注意,由等离子蚀刻产生的沟槽和焊盘将具有竖直侧壁,也称为矩形轮廓。

73.注意,可以在过孔形成步骤(vii)之前或之后去除金属掩模。或者,如果金属掩模的金属材料与步骤(viii)中使用的导电金属相同,则它可以根本不用去除。

74.参照图2f,根据本方法的步骤(vii),可以通过在焊盘124处进行激光钻孔来形成至少一个过孔126以露出下面的现有导体即电路110的一部分。如图所示,通过激光钻孔制成的过孔126具有梯形轮廓。

75.根据多层电路结构的应用,形成至少一个过孔的步骤(vii)可以通过等离子蚀刻来完成以提供具有竖直侧壁的通孔轮廓以使信号损失最小化。

76.参照图2g,根据本方法的步骤(viii),沉积导电金属以完全填充包括沟槽122和过孔126的图案化介电层120,以形成具有过量导电金属的导电金属层140。优选地,该导电金属与用于形成金属硬掩模132的导电材料相同。由于导电金属也已填充过孔,因此导电金属填充的过孔142用作新形成的导电金属层140与现有电路110之间的连接通道。

77.沉积导电金属的方法可以包括预先形成种子层,然后进行电镀。用于形成种子层的合适方法包括但不限于物理气相沉积(pvd)、化学气相沉积(cvd)或化学镀。

78.当介电层的迹线图案包含宽度和直径范围广的沟槽和过孔时,通过单个镀覆过程获得厚度均匀的导电金属层140成为挑战。尤其是当迹线图案的多个沟槽(包括接地区域)和过孔具有大于150μm的宽度和直径时。

79.本发明的一个方面是提供一种双镀法(dual plating)来解决上述问题。

80.在一个实施方案中,电镀包括单镀法(single plating)或双镀法。

81.本发明的双镀法可以包括如下步骤i-iv:

82.i.形成图案化抗蚀剂层以掩蔽宽度为150μm或更小的沟槽和过孔;

83.ii.第一次电镀以将导电金属沉积到宽度大于150μm的未掩蔽的沟槽和过孔,直到填充沟槽深度的约50至90%;

84.iii.去除图案化抗蚀剂层以露出宽度为150μm或更小的沟槽和过孔;以及

85.iv.第二次电镀以确保所有沟槽和过孔100%被导电金属填充。

86.或者,本发明的双镀法可以包括如下步骤a-d:

87.a.第一次电镀以沉积导电金属,以完全填充宽度为150μm或更小的每个沟槽和过

孔的深度;

88.b.形成图案化抗蚀剂层,以掩蔽已被导电金属完全填充的沟槽和过孔;

89.c.第二次电镀以确保宽度大于150μm的所有未掩蔽的沟槽和过孔至少填充到沟槽深度的100%;以及

90.d.去除图案化抗蚀剂层以露出宽度为150μm或更小的沟槽和过孔。

91.参照图2h,根据本方法的步骤(ix),去除导电金属层140的过量部分,使得填充在沟槽140和过孔142中的导电金属的表面与介电层的表面共平面120。该步骤也称为“平坦化”。所得基板是2层电路结构,其中新电路140嵌入在介电层120中。不包括过孔的新电路140具有约5μm至约50μm的嵌入深度。

92.在一个实施方案中,平坦化方法包括蚀刻、机械研磨或化学机械抛光(cmp)。

93.在另一个实施方案中,平坦化方法包括电解减薄、闪蚀(flash etching)、表面烧蚀/等离子清洁或其他相关技术。

94.参照图2i,根据本方法,2层电路结构可以经受图2b至图2h所示的步骤(ii)-(ix),以提供在相应介电层150和120内具有嵌入式电路170和140的3层电路结构。

95.注意,本方法的步骤(ii)-(ix)可以根据需要重复多次以提供多层电路结构。

96.第二实施方案

97.在本发明的第二实施方案中,描述一种用于制造具有双面导电层的多层电路结构的方法。图3a至图3i是展示根据本发明第二实施方案的步骤的剖面流程图。

98.参照图3a,根据本方法的步骤(i),提供双面pcb。基板包含介电芯200、位于介电芯的相反表面上的两个电路210a和210b以及通孔212,所述通孔是平均直径为约50μm至约250μm的中空圆柱体。通孔涂覆有连接电路210a和210b的金属材料层214。在进行下一步之前,通孔被填充以包含环氧树脂、酚醛树脂等的有机聚合物216。

99.在一个实施方案中,所述通孔是中空圆柱体,其具有包含cu或cu合金的层厚为约15μm至约25μm的金属材料层。

100.在另一个实施方案中,涂覆有金属材料层的通孔然后被填充以包含环氧树脂或酚醛树脂的有机聚合物。

101.参照图3b,根据本方法的步骤(ii),通过分别在电路210a和210b上涂覆热固化聚合物或层压包含热固化聚合物的预浸材料而形成介电层222和224。

102.注意,由于通孔212已填充有有机聚合物216,因此用于形成介电层222和224的热固化聚合物可以相同或不同。

103.在一个实施方案中,用于形成介电层222和224的热固化聚合物是相同的。

104.参照图3c,根据本方法的步骤(iii),通过沉积导电金属或层压金属箔,在介电层222和224上分别形成金属层232和234。

105.参照图3d,根据本方法的步骤(iv),通过光成像将金属层图案化以在相应表面上形成金属掩模242和244。

106.参照图3e,根据本方法的步骤(v),在未被金属掩模242和244遮蔽的区域通过等离子蚀刻将介电层图案化,以在相应介电层的表面上形成凹入图案252和254。

107.参照图3f,根据本方法的步骤(vi),通过化学蚀刻和等离子蚀刻去除金属掩模242和244,以露出具有凹入图案252和254的介电层。

108.参照图3g,根据本方法的步骤(vii),通过激光钻孔形成多个过孔,例如262和264,以露出下面的现有导体即电路210a和210b的一部分。

109.参照图3h,根据本方法的步骤(viii),沉积导电金属以完全填充相应凹入图案252或254,以分别形成具有过量导电金属的导电金属层272或274。由于导电材料也已填充过孔262和264,因此这些导电金属填充的过孔用作新形成的导电金属层272(或274)与现有电路210a(或210b)之间的连接通道。

110.参照图3i,根据本方法的步骤(ix),然后去除导电金属层272或274的过量部分,使得填充在每面的迹线层(272和274)以及多个过孔(276和278)中的导电金属的表面与相应介电层222或224的表面共平面。所得基板是4层电路结构,其中新电路272或274嵌入在相应介电层222或224中。

111.如前所述,合适的平坦化方法包括蚀刻、机械研磨或化学机械抛光(cmp)。

112.第三实施方案

113.在本发明的第三实施方案中,描述一种用于制造具有双面导电层的多层电路结构的方法。图4a至图4h是展示根据本发明第三实施方案的本发明方法的剖面流程图。

114.参照图4a,根据本方法的步骤(i),提供双面pcb。基板包含介电芯300、位于介电芯的相反表面上的两个电路310a和310b以及填充有金属材料的通孔312。优选地,所述金属材料包含cu或cu合金。

115.参照图4b,根据本方法的步骤(ii)-(iii),介电层322和324以及金属层332和334分别通过将单面金属包层320a或320b与和电路310a和310b接触的介电层322或324层压而形成。

116.注意,由于通孔312已填充有金属材料,因此单面金属包层320a或320b可以相同或不同。通常,单面金属包层320a或320b具有约10μm至约50μm的厚度。所述单面金属包层的金属箔包含cu、ni、ti、w、al、cr、co、ag、au、pd及它们的合金;并且具有约3μm至约15μm的厚度。

117.在一个实施方案中,单面金属包层320a或320b是相同的。

118.在另一实施方案中,单面金属包层的金属箔包含铜或铜合金。

119.参照图4c,根据本方法的步骤(iv),通过光成像将金属层332和334图案化,以在相应表面上形成金属掩模342和344。

120.参照图4d,根据本方法的步骤(v),在未被金属掩模342和344遮蔽的区域通过等离子蚀刻将介电层322和324图案化,以在相应介电层的表面上形成凹入图案352和354。

121.参照图4e,根据本方法的步骤(vi),通过化学蚀刻和等离子蚀刻去除金属掩模342和344,以露出具有凹入图案352和354的介电层。

122.参照图4f,根据本方法的步骤(vii),可以通过激光钻孔或等离子蚀刻形成多个过孔,例如362和364,以露出下面的导体即电路310a和310b的一部分。

123.参照图4g,根据本方法的步骤(viii),沉积导电金属以完全填充相应凹入图案352或354以形成每面的具有过量导电金属的导电金属层372或374。由于导电材料已填充过孔362和364,因此这些导电金属填充的过孔用作新形成的导电金属层372(或374)与相应下方电路310a(或310b)之间的连接通道。

124.参照图4h,根据本方法的步骤(ix),去除导电金属层372或374的过量部分,使得填充在每面的迹线层和多个过孔中的导电金属的表面与相应介电层322或324的表面共平面。

所得基板是4层电路结构,其中新电路372或374嵌入在相应介电层222或224中。

125.第四实施方案

126.在本发明的第四实施方案中,描述一种用于制造内部具有导电层和ic芯片的多层电路结构的方法。图5a至图5i是展示根据本发明第四实施方案的步骤的剖面流程图。

127.参照图5a,根据本方法的步骤(i),提供封装基板。封装基板包含具有多个铜凸块402的芯片404,芯片被介电芯400包围,其中金属柱402露出并且与芯块400的表面共平面。封装基板通常具有约100μm至约300μm的厚度。

128.参照图5b,根据本方法的步骤(ii),通过层压在介电芯400上形成介电层410。

129.参照图5c,根据本方法的步骤(iii),在介电层410上沉积金属层420。

130.参照图5d,根据本方法的步骤(iv),通过光成像将金属层420图案化以形成金属掩模422。用于形成金属掩模422的光成像过程与前述实施方案中描述的相同。

131.参照图5e,根据本方法的步骤(v),在未被金属掩模422遮蔽的区域通过等离子蚀刻将介电层410图案化,以在介电层的表面上形成凹入图案412。

132.参照图5f,根据本方法的步骤(vi),通过化学蚀刻和等离子蚀刻去除金属掩模422。

133.参照图5g,根据本方法的步骤(vii),通过激光钻孔形成过孔414以露出芯片的金属柱402的一部分。

134.参照图5h,根据本方法的步骤(viii),沉积导电材料以完全填充凹入图案412和过孔414以形成导电金属层420,其中导电金属的过量部分完全覆盖介电层410。

135.参照图5i,根据本方法的步骤(ix),去除导电材料420的过量部分,使得填充在迹线层和过孔中的导电金属的表面与相应介电层410的表面共平面。因此,嵌入的导电迹线和过孔成为封装基板的新形成的电路。

136.第五实施方案

137.在本发明的第五实施方案中,描述一种用于制造具有双面导电层的多层电路结构的方法。图6a至图6f是展示根据本方法的第五实施方案的步骤的剖面流程图,其中沉积导电材料的步骤(vii)通过双重电镀法执行。

138.参照图6a,提供双面pcb基板并使其经受本方法的步骤(ii)-(vii)。步骤(vii)之后的基板包含介电芯500、位于介电芯500的相反表面上的两个介电层520和521,两个电路510和511通过具有金属材料薄涂层512的通孔连接。通孔完全填充有有机聚合物514,例如环氧树脂、酚醛树脂等。

139.介电层520和521具有嵌入其中的凹入图案。每个凹入图案包括多个窄沟槽(522或523,即沟槽具有不超过150μm的宽度)、宽沟槽(524或525,即沟槽具有大于150μm的宽度)和过孔(526或527,具有约20μm至约250μm的直径)。

140.参照图6b,根据本方法的步骤(viii),通过第一次电镀沉积导电金属以形成相应的导电材料层530和531。如图所示,较窄的沟槽522和523填充有过量导电金属,而较宽的沟槽524和525填充到沟槽深度的约50至90%。

141.参照图6c,在第一轮电镀后,封装基板经受光刻过程,以形成图案化光致抗蚀剂层540和541,其中已经完全填充有导电金属的较窄沟槽522和523被掩蔽,而部分填充的沟槽524和525以及过孔526和527被露出。

142.参照图6d,通过第二次电镀沉积相同的导电金属以在标记为532/533和534/535的区域中完全填充所述部分填充的沟槽524和525以及过孔526和527。

143.参照图6e,去除图案化光致抗蚀剂层540和541以露出完全填充有导电金属的所有沟槽和过孔。

144.参照图6f,通过前面提到的平坦化方法去除每个导电金属层的过量部分。所得基板是4层电路结构,其中新电路530或531嵌入在相应介电层520或521中。

145.下面详细描述根据本方法制造多层电路结构的实施例。

146.实施例1

147.步骤1.形成介电层

148.单面pcb(试样尺寸:50mm x 150mm)用作基板。所述基板具有带有迹线和焊盘的现有电路。将介电膜(由ajinomoto build film制造,型号为gx-92r,厚度60μm)在真空下在90℃下以0.7mpa的压力层压在基板上持续60秒,然后在90℃下以1.0mpa的压力压平持续60秒。

149.步骤2.形成金属层

150.通过pvd涂覆机(uvat technology co.制造,型号:uhsd-060302t)溅射铜,在步骤1得到的基板的介电层上沉积铜层。基准浓度是铜4n以形成厚度为0.2μm的cu层。

151.步骤3.形成金属硬掩模

152.通过在步骤2获得的基板的铜层上层压干膜(th1015,厚度15μm,由dupont electronics,inc.制造)而形成光致抗蚀剂层。使用辊式层压机并在100℃下以1.4mpa的压力和1.0米/分钟的轧制速度下进行层压。

153.光致抗蚀剂图案是通过使用波长为405nm的adtec ip-8、通过sst=18/41产生的。使用pcb制造商常规设计的测试图案,其包括设置为20μm/20μm的线/间距、高达60μm的较宽沟槽、120μm的焊盘和》2000μm的接地区域。暴露完成后,通过2%的na2co3溶液处理3分钟而将光致抗蚀剂层的未固化部分剥离并去除,用去离子水冲洗并且干燥。

154.使用过硫酸钠(na2s2o8)溶液(130g/l)在常规水平线处以1m/min的速度蚀刻掉未掩蔽的铜区域直到完成,用去离子水冲洗并且干燥。

155.然后通过用10%的naoh溶液处理90秒来剥离和去除光致抗蚀剂图案。冲洗和干燥后,在基板上形成铜硬掩模。

156.步骤4.将介电层图案化

157.在形成硬掩模后,使用电感耦合等离子反应离子蚀刻(icp-rie)系统(schmid group制造)通过等离子蚀刻去除介电层的暴露区域,工艺气体为cf4、o2和n2的混合物以反应20分钟,在介电层上形成蚀刻深度为15μm的凹入图案。

158.步骤5.金属硬掩模的去除

159.使用过硫酸钠溶液(130g/l)在常规水平线处以1m/min的速度去除铜硬掩模,直至完成,用去离子水冲洗并干燥。

160.步骤6.过孔形成

161.为了在现有导体和后续步骤中要制成的电路之间进行电路连接,使用mitsubishi laser drill(型号:gtw5,带有co2激光器)通过激光钻孔到达下方的导体/焊盘,从而产生直径为75μm的250个过孔。

162.步骤7.沉积导电金属

163.使用pvd涂覆机(uvat technology co.制造,型号:uhsd-060302t)通过溅射ti,然后溅射cu来形成种子层。基准浓度是钛2n7和铜4n。所得ti层具有0.1μm的厚度,cu层具有0.2μm的厚度。

164.在形成种子层后,用电镀溶液(microfill

tm aet-1,购自dupont electronics,inc.)和2.0asd的电流密度下,在20l桨式电镀机中进行第一次电镀31分钟,得到约12μm的电镀厚度。凹入图案的细线,即宽度为20μm至150μm的那些沟槽被完全填充。

165.在第一次电镀后,通过层压干膜(th1015,厚度为15μm)在基板上形成光致抗蚀剂层。使用辊式层压机并在100℃下以1.4mpa的压力和1.0米/分钟的轧制速度下进行层压。

166.光致抗蚀剂图案是通过使用波长为405nm的adtec ip-8、通过sst=18/41产生的。使用将覆盖铜填充的细线的图案。暴露完成后,用2%的na2co3溶液处理3分钟去除光致抗蚀剂层的未固化部分,用去离子水冲洗并且干燥。

167.在抗蚀剂图案形成后,用电镀溶液(dupont microfill

tm aet-1)和2.0asd的电流密度,在20l桨式电镀机中进行第二次电镀20分钟,得到约8μm的电镀厚度。介电层的凹入图案的所有沟槽/过孔/接地区域都填充有铜。

168.然后通过10%的naoh溶液处理90秒去除光致抗蚀剂图案。冲洗和干燥后,在基板上形成铜硬掩模。

169.步骤8.平坦化

170.双镀过程后的基板用垫(由dupont制造,suba

tm 600)和浆料(rds mk10-001)通过化学机械抛光(cmp)平坦化。操作参数如下:垫/支架速度为223/211,下压力(down force)为3psi,处理时间为120秒,浆料流速为80ml/min。

171.冲洗和干燥后,得到具有新嵌入式电路的基板,即本多层电路结构的实施方案。然后用显微镜进行截面分析来评价通过本方法制造的多层电路结构。

172.虽然已在典型的实施方案中说明且描述了本发明,但不旨在限制所示的细节,因为可能有各种修改和替换而不脱离本发明的精神。同样地,在此公开的本发明的修改和等同物可由本领域技术人员仅使用常规实验即得出,并且认为所有此类修改和等同物是处于如所附权利要求限定的本发明的精神和范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1