一种具有多晶硅二极管栅极结构的浮空P区CSTBT器件的制作方法

一种具有多晶硅二极管栅极结构的浮空p区cstbt器件

技术领域

1.本发明属于功率半导体器件技术领域,具体涉及一种具有多晶硅二极管栅极结构的浮空p区cstbt器件。

背景技术:

2.绝缘栅双极晶体管(insulated

‑

gate bipolar transistors,igbt)综合了场控器件和双极型器件的优点,既具有mosfet输入阻抗高、栅极易驱动等特点,又具有双极型晶体管电流密度大、功率密度高等优势,目前被广泛应用于轨道交通、新能源汽车、智能电网、风力发电等领域。由于应用环境和电路拓扑结构的需求,igbt一直沿着降低器件开关功耗、提高器件工作频率以及提高器件可靠性的趋势发展。

3.igbt作为一种双极型器件,在导通时会发生电导调制效应,从而大幅度提高漂移区内的载流子浓度,降低器件的正向导通压降和通态损耗,尤其是在中高压应用领域其优势更加明显。但是,在大幅度降低正向导通压降的同时,过多的存储载流子将导致关断时的抽取过程变长,电流拖尾显著增大,从而大幅度增加igbt的关断损耗。因此,改善器件导通压降与关断损耗的矛盾关系已经成为了当前研究的热点。为了降低igbt的导通压降,一方面利用沟槽栅极结构取代传统的平面栅igbt结构,消除了传统igbt的jfet区域,极大地减小了器件的导通电阻,降低了器件的静态功耗;另一方面在采用沟槽栅极的基础上,在两沟槽之间引入浮空p区结构(即该区域未与发射极作欧姆接触),增强了器件的电子注入效应从而进一步减小器件的导通压降。为了改善器件导通压降与关断能量损耗之间的折中关系,通常采用具有场截止(field stop,fs)技术以及载流子存储(carrier store,cs)技术从而实现igbt导通压降以及关断能量损耗之间的更好地优化。传统的fp

‑

cstbt(如图1所示)虽然可利用cs层以及浮空p区有效减小器件的导通压降,但浮空p区的存在会引入较大的位移电流,从而影响器件的emi噪声,同时漂移区内的大量的载流子也会增大器件关断时间。因此,亟需开发出一种能够更好地实现器件导通压降与关断损耗的矛盾关系的优化的igbt器件。

技术实现要素:

4.本发明所要解决的技术问题是针对现有技术存在的问题,提供一种具有多晶硅二极管栅极结构的浮空p区cstbt器件,以进一步改善导通压降和关断损耗之间的折中关系。

5.为解决上述技术问题,本发明实施例提供一种具有多晶硅二极管栅极结构的浮空p区cstbt器件,其元胞结构包括从下至上依次层叠设置的金属集电极1、p+集电区2、n型缓冲层3、n型漂移区4和金属发射极13;

6.所述n型漂移区4的顶层具有间隔设置的沟槽栅极结构,沟槽栅结构一侧的所述n型漂移区4的顶层具有浮空p区9,沟槽栅极结构另一侧的所述n型漂移区4的顶层具有p型基区6,所述p型基区6的顶层具有侧面相互接触的p型重掺杂区7和n型重掺杂区8,所述p型基区6下方的所述n型漂移区4中具有n型载流子存储层5;

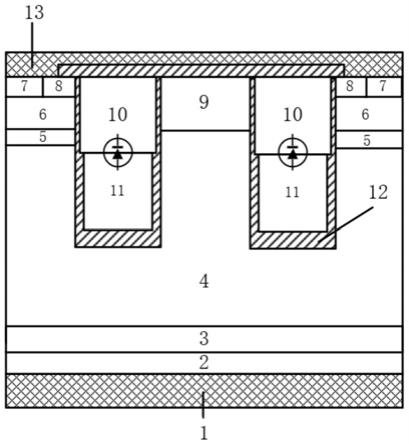

7.所述沟槽栅极结构包括氧化层12以及从上至下依次设置的n+栅极10和p+栅极11;所述n+栅极10与n型载流子存储层5、p型基区6、n型重掺杂区8和浮空p区9之间均具有所述氧化层12,所述p+栅极11与n型漂移区4之间具有氧化层12;

8.所述n型重掺杂区8的第一部分、所述沟槽栅极结构以及所述浮空p区9上具有氧化层12,所述金属发射极13位于所述n型重掺杂区8的第二部分、所述p型重掺杂区7和所述氧化层12上。

9.在上述技术方案的基础上,本发明还可以做如下改进。

10.进一步的,所述p+栅极11与n型漂移区4之间的氧化层12的厚度厚于所述n+栅极10与n型载流子存储层5、p型基区6、n型重掺杂区8和浮空p区9之间的氧化层12的厚度。

11.进一步的,所述n+栅极10和所述p+栅极11的材料均为多晶硅。

12.进一步的,其元胞结构左右对称。

13.与现有技术相比,本发明的有益效果是:本发明在fp

‑

cstbt结构的基础上,提出了一种具有多晶硅二极管栅极结构的浮空p区cstbt器件。在有效降低器件导通压降的基础上,一方面通过在沟槽结构中引入多晶硅二极管,利用沟槽内二极管形成的pn结的结电容,将栅极和集电极进一步屏蔽,实现更小的密勒电容和输入电容,优化器件的开关特性;另一方面增加p型poly栅极周围的栅氧化层厚度,进一步减小器件的密勒电容的同时优化沟槽底部及拐角处的电场,从而更好地实现功率器件导通压降与关断损耗之间的折中关系。

附图说明

14.图1为传统的具有浮空p区的cstbt(floating

‑

p trench igbt with cs layer,fp

‑

cstbt)的横向截面结构示意图。

15.图2为本发明实施例的一种具有多晶硅二极管栅极结构的浮空p区cstbt器件(anode polysilicon diodes gate structure for fp

‑

cstbt,apd

‑

fp

‑

cstbt)的横向截面结构示意图。

16.附图中,各标号所代表的部件列表如下:

17.1为金属集电极,2为p+集电区,3为n型缓冲层,4为n型漂移区,5为n型载流子存储层,6为p型基区,7为p型重掺杂区,8为n型重掺杂区,9为浮空p区,10为n+栅极,11为p+栅极,12为氧化层,13为金属发射极。

具体实施方式

18.以下结合附图对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

19.如图2所示,本发明第一实施例提供的一种具有多晶硅二极管栅极结构的浮空p区cstbt器件,其元胞结构包括从下至上依次层叠设置的金属集电极1、p+集电区2、n型缓冲层3、n型漂移区4和金属发射极13;

20.所述n型漂移区4的顶层具有间隔设置的沟槽栅极结构,沟槽栅结构一侧的所述n型漂移区4的顶层具有浮空p区9,沟槽栅极结构另一侧的所述n型漂移区4的顶层具有p型基区6,所述p型基区6的顶层具有侧面相互接触的p型重掺杂区7和n型重掺杂区8,所述p型基区6下方的所述n型漂移区4中具有n型载流子存储层5;

21.所述沟槽栅极结构包括氧化层12以及从上至下依次设置的n+栅极10和p+栅极11;所述n+栅极10与n型载流子存储层5、p型基区6、n型重掺杂区8和浮空p区9之间均具有所述氧化层12,所述p+栅极11与n型漂移区4之间具有氧化层12;

22.所述n型重掺杂区8的第一部分、所述沟槽栅极结构以及所述浮空p区9上具有氧化层12,所述金属发射极13位于所述n型重掺杂区8的第二部分、所述p型重掺杂区7和所述氧化层12上。

23.上述实施例中,n型载流子存储层5用于提高n型漂移区4载流子浓度,从而降低器件导通压降。浮空p区9用于增强电子注入效应,从而降低器件导通压降。n+栅极10、p+栅极11构成多晶硅二极管栅极结构,用于降低器件的密勒电容。

24.可选地,所述p+栅极11与n型漂移区4之间的氧化层12的厚度厚于所述n+栅极10与n型载流子存储层5、p型基区6、n型重掺杂区8和浮空p区9之间的氧化层12的厚度。

25.上述实施例中,p+栅极(11)与n型漂移区(4)之间的厚氧化层一方面用于降低器件的密勒电容,另一方面用于优化沟槽栅极底部和拐角处的电场。

26.可选地,所述n+栅极10和所述p+栅极11的材料均为多晶硅。

27.可选地,其元胞结构左右对称。

28.本发明的原理如下:本发明基于传统fp

‑

cstbt结构,提出了一种具有多晶硅二极管栅极结构的浮空p区cstbt(anode polysilicon diodes gate structure for fp

‑

cstbt,apd

‑

fp

‑

cstbt)器件。在利用cs层以及浮空p区有效降低器件导通压降的基础上,一方面通过在沟槽结构中引入多晶硅二极管,利用沟槽内二极管形成的pn结的结电容将栅极和集电极进一步屏蔽,实现更小的密勒电容和输入电容,优化器件的开关特性;另一方面增加p型poly栅极周围的栅氧化层厚度,进一步减小器件的密勒电容的同时优化沟槽底部及拐角处的电场,从而更好地实现功率器件导通压降与关断损耗之间的折中关系。

29.本发明基于传统fp

‑

cstbt结构提出了一种具有多晶硅二极管栅极结构的浮空p区cstbt,该结构相较于传统结构,可有效减小器件的密勒电容并实现更优的导通压降与关断损耗之间的折中关系。

30.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

31.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1