半导体器件、器件和封装的制作方法

1.一些示例实施方式涉及包括具有外围电路的第一结构和具有栅极层的第二结构的器件。

背景技术:

2.由于对更高集成的需求,能够存储数据的器件需要在减小器件的体积的同时保持高容量的数据处理。作为提高这样的器件的集成度的方法,已经提出其中结构使用晶片键合方法(wafer bonding method)来接合的半导体器件。

技术实现要素:

3.一些示例实施方式提供一种能够提高其集成度的器件。

4.一些示例实施方式提供一种能够提高其可靠性的器件。

5.一些示例实施方式提供一种半导体器件。该半导体器件包括:基板;在基板上的外围电路和第一接合焊盘;第一绝缘结构,在基板上并围绕第一接合焊盘的侧表面;第二接合焊盘,接触第一接合焊盘;第二绝缘结构,在第一绝缘结构上并围绕第二接合焊盘的侧表面;在第二绝缘结构上的钝化层;在钝化层和第二绝缘结构之间的上绝缘结构;阻挡盖层,在上绝缘结构和钝化层之间,并包括与上绝缘结构的材料和钝化层的材料不同的材料;导电图案,在上绝缘结构中彼此间隔开;第一图案结构,在上绝缘结构和第二绝缘结构之间;堆叠结构,在第二绝缘结构和第一图案结构之间,并包括在垂直方向上彼此间隔开的栅极层;以及在垂直方向上穿过堆叠结构的垂直结构,该垂直结构包括数据存储结构和沟道层。

6.一些示例实施方式提供一种器件。该器件包括:基板;在基板上的外围电路和第一接合焊盘;第一绝缘结构,在基板上并围绕第一接合焊盘的侧表面;第二接合焊盘,接触第一接合焊盘;第二绝缘结构,在第一绝缘结构上并围绕第二接合焊盘的侧表面;在第二绝缘结构上的钝化层;上绝缘结构,在钝化层和第一绝缘结构之间;图案结构,在上绝缘结构和第二绝缘结构之间;第一导电图案和第二导电图案,在上绝缘结构中并在垂直方向上与图案结构重叠;输入输出导电图案,在上绝缘结构中并在垂直方向上不与图案结构重叠;输入输出焊盘开口,穿过钝化层,延伸到上绝缘结构中,并暴露输入输出导电图案的一部分;在第二绝缘结构和图案结构之间的堆叠结构,该堆叠结构包括在垂直方向上彼此间隔开的栅极层;以及在垂直方向上穿过堆叠结构的垂直结构,该垂直结构包括沟道层和数据存储层。

7.一些示例实施方式提供一种封装。该封装包括:封装基底;在封装基底上的多个半导体芯片,所述多个半导体芯片在垂直方向上彼此间隔开;以及连接结构,电连接所述多个半导体芯片和封装基底,其中所述多个半导体芯片中的至少一个包括所述器件。

8.一些示例实施方式提供一种器件。该器件包括:基板;在基板上的外围电路和第一接合焊盘;第一绝缘结构,在基板上并围绕第一接合焊盘的侧表面;第二接合焊盘,接触第一接合焊盘;第二绝缘结构,在第一绝缘结构上并围绕第二接合焊盘的侧表面;在第二绝缘结构上的钝化层;上绝缘结构,在钝化层和第一绝缘结构之间;阻挡盖层,在上绝缘结构和

钝化层之间,并包括与上绝缘结构的材料和钝化层的材料不同的材料;图案结构,在上绝缘结构和第二绝缘结构之间;第一导电图案和第二导电图案,在上绝缘结构中并在垂直方向上与图案结构重叠;输入输出导电图案,在上绝缘结构中并在垂直方向上不与图案结构重叠;输入输出接触结构,在输入输出导电图案下面并与输入输出导电图案重叠;输入输出焊盘开口,穿过钝化层、延伸到上绝缘结构中并暴露输入输出导电图案的一部分;在第二绝缘结构和图案结构之间的堆叠结构,该堆叠结构包括在垂直方向上彼此间隔开的栅极层;在垂直方向上穿过堆叠结构的垂直结构,该垂直结构包括沟道层和数据存储层;以及分隔结构,在垂直方向上穿过堆叠结构,其中图案结构包括接触沟道层和分隔结构的硅层,第一导电图案、第二导电图案和输入输出导电图案的每个包括第一导电层、在第一导电层上并比第一导电层厚的第二导电层以及在第二导电层上并比第二导电层薄的第三导电层,输入输出焊盘开口穿过输入输出导电图案的第三导电层,输入输出导电图案的被暴露的第二导电层限定输入输出键合焊盘(input

‑

output bonding pad),并且输入输出焊盘开口不与输入输出接触结构重叠。

9.一些示例实施方式提供一种封装。该封装包括:封装基底;多个半导体芯片,在封装基底上,同时在垂直方向上彼此间隔开;键合引线,电连接所述多个半导体芯片和封装基底;以及模制层,在封装基底上并覆盖所述多个半导体芯片和键合引线,其中所述多个半导体芯片中的至少一个包括所述器件,所述多个半导体芯片在垂直方向上堆叠,同时暴露输入输出键合焊盘,输入输出键合焊盘与键合引线中的至少一条接触。

附图说明

10.从以下结合附图的详细描述,本发明构思的以上和其它的方面、特征和优点将被更清楚地理解,附图中:

11.图1是示出根据本发明构思的一示例实施方式的器件的示意性分解透视图。

12.图2a和图2b是示出根据本发明构思的一示例实施方式的器件的一示例的剖视图。

13.图3a和图3b是示出图2a的部分的放大图。

14.图4a至图4d是示出根据本发明构思的一示例实施方式的器件的修改示例的剖视图。

15.图5至图9是示出根据本发明构思的一示例实施方式的器件的另一些修改示例的剖视图。

16.图10是示出根据本发明构思的一示例实施方式的器件的另一示例的剖视图。

17.图11是示出根据本发明构思的一示例实施方式的器件的另一示例的剖视图。

18.图12a至图17b是示出根据本发明构思的一示例实施方式的形成器件的方法的一示例的剖视图。

具体实施方式

19.在下文,将参照附图描述本发明构思的示例实施方式。

20.在下文,诸如

‘

在

……

上’、

‘

上部分’、

‘

上表面’、

‘

在

……

下面’、

‘

下部分’、

‘

下表面’、

‘

侧表面’等可以被理解为指代在元件、部件、区域、层和/或部分之间的空间关系,基于那些元件、部件、区域、层和/或部分在附图中的取向,除非另外地指示。类似地,尽管术语

‘

第一’、

‘

第二’、

‘

第三’等可以在这里用于描述各种元件、部件、区域、层和/或部分,但是这些元件、部件、区域、层和/或部分不应受这些术语限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一元件、部件、区域、层或部分区别开。

21.图1是示出根据本发明构思的一示例实施方式的器件的示意性分解透视图。

22.参照图1,根据示例实施方式的器件1可以包括第一结构101和第二结构201。第一结构101和第二结构201可以彼此连接并彼此键合。第一结构101可以包括外围电路pc。第二结构201可以包括存储单元阵列区域mca以及与存储单元阵列区域mca相邻的阶梯区域sa。存储单元阵列区域mca可以被提供为多个存储单元阵列区域。

23.外围电路pc可以包括行解码器dec、页缓冲器pb和其它电路peri。其它电路peri可以包括锁存电路、高速缓存电路、感测放大器、静电放电(esd)元件、输入输出缓冲器和/或数据输入输出电路。

24.外围电路pc中的行解码器dec、页缓冲器pb和其它电路peri可以布置为各种形式,并且例如不限于图1所示的特定取向和/或配置,并可以被各种各样地修改。

25.第二结构201可以包括多个输入输出键合焊盘299p。所述多个输入输出键合焊盘299p可以设置在第二结构201的至少一侧。例如,所述多个输入输出键合焊盘299p可以沿着第二结构201的至少一个边缘布置成一行。第二结构201中的所述多个输入输出键合焊盘299p的布置的形状不限于图1所示的形状,并可以被各种各样地修改。

26.在一示例中,第一结构101可以被称为逻辑芯片结构,第二结构201可以被称为存储器芯片结构。

27.在下文,将参照图2a和图2b描述器件1的示例。图2a和图2b是示出根据本发明构思的一示例实施方式的器件的一示例的剖视图。

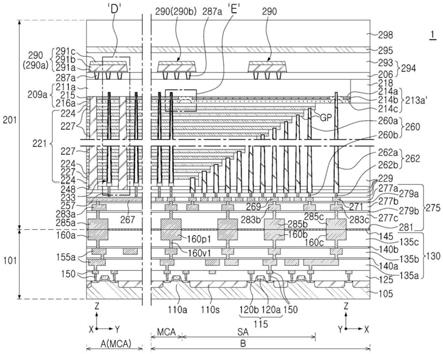

28.在图2a中,由“a”指示的区域可以示意性地代表器件1在第一方向x上的剖面形状,在其中包括存储单元阵列区域mca的一部分,由“b”指示的区域可以示意性地代表器件1在垂直于第一方向x的第二方向y上的剖面形状,在其中包括存储单元阵列区域mca的一部分和与存储单元阵列区域mca相邻的阶梯区域sa。图2b可以示意性地示出沿着图1所示的输入输出键合焊盘299p和与输入输出键合焊盘299p相邻的区域的器件1的剖面形状。

29.参照图1、图2a和图2b,如图1所示,器件1可以包括彼此接触并彼此键合的第一结构101和第二结构201。

30.第一结构101可以包括:基板105;布置在基板105上的外围电路(图1中的pc)和第一接合焊盘160a、160b、160c和160d;以及第一绝缘结构130,设置在基板105上并至少围绕第一接合焊盘160a、160b、160c和160d的侧表面。基板105可以是半导体基板。

31.外围电路(图1中的pc)可以包括外围元件115、第一外围布线150、第二外围布线155a和输入输出外围布线155b。

32.在一示例中,外围元件115可以包括在基板105上的晶体管,所述晶体管包括设置在有源区110a上的外围栅极120a以及设置在外围栅极120a的两侧且在有源区110a中的外围源极/漏极120b。在其中基板105是半导体基板的情况下,有源区110a可以是例如基板105的一部分并可以由在基板105中的隔离层110s限定。在这种情况下,有源区110a可以包括与基板105相同的基础成分,但是还可以包括不同类型和/或浓度的掺杂剂。有源区110a还可以包括在有源区110a上的半导体和/或绝缘层。外围源极/漏极120b可以是例如导电材料

(例如金属)和/或包括与有源区120和/或基板105不同的类型和/或浓度的掺杂剂的区域。外围元件115不限于诸如晶体管的有源元件,并且还可以包括诸如电阻器、电容器等的无源元件。

33.第一结构101还可以包括下绝缘层125。下绝缘层125可以覆盖外围元件115。第一外围布线150可以穿过下绝缘层125,并可以电连接到外围元件115。第二外围布线155a可以在第一外围布线150上和/或电连接到第一外围布线150。在一示例中,第一外围布线150可以包括导电材料(例如钨(w)),第二外围布线155a可以包括与第一外围布线150的材料不同的导电材料(例如铜(cu))。

34.第一绝缘结构130可以包括多个下金属间电介质层135a、135b和135c、多个下阻挡层140a和140b以及第一接合绝缘层145。例如,第一绝缘结构130可以包括依次堆叠的第一下金属间电介质层135a、第一下阻挡层140a、第二下金属间电介质层135b以及第二下阻挡层140b、第三下金属间电介质层135c和第一接合绝缘层145。

35.所述多个下金属间电介质层135a、135b和135c可以包括硅氧化物或低k电介质材料。所述多个下阻挡层140a和140b可以包括硅氮化物或高k电介质材料。在一示例中,第一接合绝缘层145可以包括氧化物和/或氮化物,像sio、sicn、sioc、sion、sin、siocn或其组合。例如,第一接合绝缘层145可以包括sicn、sioc、sion、sin和siocn中的至少一种和/或sio。

36.第一接合焊盘160a、160b、160c和160d可以包括下位线接合焊盘160a、下栅极接合焊盘160b、下源极接合焊盘160c和下输入输出接合焊盘160d。第一接合焊盘160a、160b、160c和160d可以包括导电材料,例如铜(cu)。例如,第一接合焊盘160a、160b、160c和160d可以包括与第二外围布线155a相同的材料。

37.下位线接合焊盘160a、下栅极接合焊盘160b和下源极接合焊盘160c中的每个可以电连接到第二外围布线155a。下输入输出接合焊盘160d可以电连接到输入输出外围布线155b。

38.在一示例中,下位线接合焊盘160a、下栅极接合焊盘160b和下源极接合焊盘160c中的每个可以包括第一接合部分160p1和从第一接合部分160p1延伸的第一通路部分160v1。

39.在一示例中,下输入输出接合焊盘160d可以包括输入输出接合部分160p2和从输入输出接合部分160p2延伸的多个输入输出通路部分160v2。

40.在一示例中,第二结构201可以包括分别接触第一接合焊盘160a、160b、160c和160d的第二接合焊盘285a、285b、285c和285d、以及接触第一绝缘结构130并围绕第二接合焊盘285a、285b、285c和285d的侧表面的第二绝缘结构275。

41.第二绝缘结构275可以包括多个上金属间电介质层277a、277b和277c、多个上阻挡层279a和279b以及第二接合绝缘层281。例如,第二绝缘结构275可以包括依次堆叠的第一上金属间电介质层277a、第一上阻挡层279a、第二上金属间电介质层277b、第二上阻挡层279b、第三上金属间电介质层277c和第二接合绝缘层281。所述多个上金属间电介质层277a、277b和277c可以包括硅氧化物或低k电介质材料。所述多个上阻挡层279a和279b可以包括硅氮化物或高k电介质材料。在一示例中,第二接合绝缘层281可以由与第一接合绝缘层145相同的材料形成。在一示例中,在第一接合绝缘层145和第二接合绝缘层281之间的界

面可以是不清晰和/或不可区分的。

42.在一示例中,第二结构201可以包括设置在第二绝缘结构275上的钝化层298、设置在钝化层298和第二绝缘结构275之间的上绝缘结构294、以及设置在上绝缘结构294和钝化层298之间的阻挡盖层295。阻挡盖层295可以包括与上绝缘结构294的材料和钝化层298的材料不同的材料。上绝缘结构294可以包括第一上绝缘层206和设置在第一上绝缘层206上的第二上绝缘层293。

43.钝化层298可以包括聚酰亚胺和/或基于聚酰亚胺的材料,阻挡盖层295可以包括硅氮化物和/或基于硅氮化物的材料,上绝缘结构294可以包括硅氧化物。第一上绝缘层206和/或第二上绝缘层293可以包括hdp(高密度等离子体)硅氧化物和/或teos(原硅酸四乙酯或四乙氧基硅烷)硅氧化物,并且可以包含氢。

44.在一示例中,第二结构201可以包括在上绝缘结构294和第二绝缘结构275之间的第一图案结构(图2a中的209a)、设置在第二绝缘结构275和第一图案结构209a之间并包括在垂直方向z上彼此间隔开的栅极层227的堆叠结构221、以及在垂直方向z上穿过堆叠结构221的垂直结构233。

45.堆叠结构221还可以包括与栅极层227交替且重复堆叠的层间绝缘层224。

46.例如,在存储单元阵列区域mca中,栅极层227和层间绝缘层224可以交替且重复地堆叠,并且在阶梯区域sa中,栅极层227可以包括在第一水平方向x上从存储单元阵列区域mca延伸并在阶梯区域sa中布置成阶梯形状的栅极焊盘gp。堆叠结构221可以具有一形状,该形状具有靠近第一图案结构209a在宽度上增大的趋势。例如,最下面的栅极层227可以具有比最上面的栅极层227小的宽度。

47.在一示例中,第二结构201还可以包括第二图案结构(图2b中的209b)以及围绕第一图案结构209a的侧表面和第二图案结构209b的侧表面的中间绝缘层218。第二图案结构209b可以具有与第一图案结构209a的上表面共面的上表面。中间绝缘层218可以包括硅氧化物。

48.在一示例中,第二结构201还可以包括设置在上绝缘结构294和第二绝缘结构275之间并覆盖堆叠结构221、第一图案结构209a和第二图案结构209b的盖绝缘结构229。例如,盖绝缘结构229可以被包括在阶梯区域sa中,并可以在结构上支撑栅极层227和/或层间绝缘层224的阶梯形状。堆叠结构221可以设置在盖绝缘结构229和第一图案结构209a之间。盖绝缘结构229可以包括单层和/或多层结构。例如,盖绝缘结构229可以由多层结构形成,但是多层之间的界面可以是不明显和/或不可区分的。盖绝缘结构229可以包括硅氧化物。

49.在一示例中,第二结构201还可以包括穿过堆叠结构221的分隔结构248。每个分隔结构248可以具有在第一水平方向x上延伸的线性形状。分隔结构248可以是渐缩的(tapered)。例如,分隔结构248可以越靠近第二绝缘结构275越宽,和/或越靠近上绝缘结构294越窄。在一示例中,每个分隔结构248可以包括绝缘材料。在另一示例中,每个分隔结构248可以包括导电图案和围绕导电图案的侧表面的绝缘层。

50.在一示例中,第二结构201还可以包括位线接触插塞257、栅极接触结构260、源极接触结构262和输入输出接触结构264。

51.位线接触插塞257可以电连接到垂直结构233,并可以穿过盖绝缘结构229。栅极接触结构260可以电连接到栅极层227的栅极焊盘gp,并可以穿过盖绝缘结构229。源极接触结

构262可以电连接到第一图案结构209a,并可以穿过盖绝缘结构229。图2b中的输入输出接触结构264可以电连接到第二图案结构209b,并可以穿过盖绝缘结构229。

52.每个栅极接触结构260可以包括第一栅极接触插塞260a和设置在第一栅极接触插塞260a下面的第二栅极接触插塞260b。源极接触结构262可以包括第一源极接触插塞262a和设置在第一源极接触插塞262a下面的第二源极接触插塞262b。输入输出接触结构264可以包括第一输入输出接触插塞264a和设置在第一输入输出接触插塞264a下面的第二输入输出接触插塞264b。

53.在第一图案结构209a与第一栅极接触插塞260a的下表面、第一源极接触插塞262a的下表面和第一输入输出接触插塞264a的下表面中的每个之间的距离可以大于在栅极层227当中的最下面的栅极层与第一图案结构209a之间的距离。

54.第一栅极接触插塞260a、第一源极接触插塞262a和第一输入输出接触插塞264a可以包括相同的材料。例如,第一栅极接触插塞260a、第一源极接触插塞262a和第一输入输出接触插塞264a中的每个可以包括导电插塞264a_2以及覆盖导电插塞264a_2的侧表面和上表面的导电阻挡层264a_1。导电插塞264a_2可以包括金属材料(诸如钨等),导电阻挡层264a_1可以包括金属氮化物,诸如tin、wn、tan等。

55.在一示例中,第二结构201还可以包括穿过第一上金属间电介质层277a的位线267、栅极布线269、源极布线271和输入输出布线273。位线267可以在位线接触插塞257的下部电连接到位线接触插塞257,栅极布线269可以在栅极接触结构260的下部电连接到栅极接触结构260,源极布线271可以在源极接触结构262的下部电连接到源极接触结构262,输入输出布线273可以在输入输出接触结构264的下部电连接到输入输出接触结构264。

56.在一示例中,第二结构201还可以包括穿过第一上阻挡层279a和第二上金属间电介质层277b的位线连接布线283a、栅极连接布线283b、源极连接布线283c和输入输出连接布线283d。位线连接布线283a可以在位线267的下部电连接到位线267,栅极连接布线283b可以在栅极布线269的下部电连接到栅极布线269,源极连接布线283c可以在源极布线271的下部电连接到源极布线271,输入输出连接布线283d可以在输入输出布线277的下部电连接到输入输出布线273。

57.第二接合焊盘285a、285b、285c和285d可以穿过第二上阻挡层279b、第三金属间电介质层277c和第二接合绝缘层281。第二接合焊盘285a、285b、285c和285d可以包括在位线连接布线283a的下部电连接到位线连接布线283a的上位线接合焊盘285a、在栅极连接布线283b的下部电连接到栅极连接布线283b的上栅极接合焊盘285b、在源极连接布线283c的下部电连接到源极连接布线283c的上源极接合焊盘285c、以及在输入输出连接布线283d的下部电连接到输入输出连接布线283d的上输入输出接合焊盘285d。

58.下位线接合焊盘160a可以与上位线接合焊盘285a接触并接合到上位线接合焊盘285a。下栅极接合焊盘160b可以与上栅极接合焊盘285b接触并接合到上栅极接合焊盘285b。下源极接合焊盘160c可以与上源极接合焊盘285c接触并接合到上源极接合焊盘285c。下输入输出接合焊盘160d可以与上输入输出接合焊盘285d接触并接合到上输入输出接合焊盘285d。第一接合焊盘160a、160b、160c和160d以及第二接合焊盘285a、285b、285c和285d可以包括相同的导电材料,例如铜(cu)。

59.第一图案结构(图2a中的209a)可以包括第一图案基底211a、中间图案层215和第

一下图案层216a。第一下图案层216a可以包括在第一图案基底211a的下部接触第一图案基底211a的部分以及与第一图案基底211a间隔开的部分。中间图案层215可以设置在第一下图案层216a和第一图案基底211a之间。第一图案结构209a还可以包括在与阶梯区域sa相邻和/或重叠的区域中的第一虚设图案层213a'。

60.第二图案结构(图2b中的209b)可以包括第二图案基底211b、第二虚设图案层213b和第二下图案层216b。第二下图案层216b可以在第二图案基底211b下面和/或与第二图案基底211b间隔开,第二虚设图案层213b可以设置在第二下图案层216b和第二图案基底211b之间。

61.第一虚设图案层213a'和第二虚设图案层213b中的每个可以包括依次堆叠的第一层214a、第二层214b和第三层214c。

62.第一图案基底211a和第二图案基底211b可以包括具有n型导电类型的硅层。第一层214a和第三层214c可以包括硅氧化物,第二层214b可以包括硅氮化物或多晶硅。第一下图案层216a和第二下图案层216b可以包括具有n型导电类型的硅层。第一图案基底211a和第二图案基底211b以及第一下图案层216a和第二下图案层216b可以例如包括相同的材料。

63.在一示例中,第二结构201还可以包括在上绝缘结构294中彼此间隔开的导电图案290和/或与导电图案290接触的多个通路287a和287b。

64.导电图案290可以包括与第一图案结构209a重叠的第一导电图案290a和第二导电图案290b以及与第二图案结构209b重叠的输入输出导电图案290c。导电图案290可以与第一图案结构209a和第二图案结构209b间隔开。导电图案290可以与阻挡盖层295间隔开。每个导电图案290可以包括依次堆叠的第一导电层291a、第二导电层291b和第三导电层291c。第二导电层291b可以具有比第一导电层291a和第三导电层291c中的每个的厚度大的厚度。第三导电层291c可以具有比第一导电层291a的厚度大的厚度。第一导电层291a、第二导电层291b和第三导电层291c可以由不同的材料形成。例如,第一导电层291a可以包括钛(ti),第二导电层291b可以包括铝(al),第三导电层291c可以包括tin。

65.导电图案290可以设置在第一上绝缘层206上,并且导电图案290的侧表面和底表面可以被第二上绝缘层293覆盖。所述多个通路287a和287b可以穿过第一上绝缘层206。

66.当在平面图中观看时,第一导电图案290a和第二导电图案290b中的每个可以包括各种形状,诸如正方形、矩形、条形、圆形、椭圆形、网格形状等。

67.所述多个通路287a和287b可以包括设置在第一导电图案290a和第二导电图案290b与第一图案结构209a之间的多个第一通路287a以及设置在输入输出导电图案290c与第二图案结构209b之间的多个第二通路287b。所述多个第一通路287a可以与第一导电图案290a和第二导电图案290b以及第一图案结构209a接触。所述多个第二通路287b可以接触输入输出导电图案290c和第二图案结构209b。

68.第二结构201还可以包括输入输出焊盘开口299o,该输入输出焊盘开口299o穿过钝化层298和阻挡盖层295、延伸到上绝缘结构294中并穿过输入输出导电图案290c的第三导电层291c。输入输出焊盘开口299o可以暴露输入输出导电图案290c的第二导电层291b。输入输出导电图案290c的由输入输出焊盘开口299o暴露的部分可以被定义为输入输出键合焊盘299p。

69.接下来,将参照图3a和图3b描述堆叠结构221、垂直结构233以及与垂直结构233相

邻的部件。图3a是由图2a的“d”指示的部分的局部放大剖视图,图3b是由图2a的“e”指示的部分的局部放大剖视图。

70.参照图3a和图3b,在堆叠结构221中,每个栅极层227还可以包括第一栅极层227a和第二栅极层227b。第二栅极层227b可以覆盖第一栅极层227a的上表面、下表面和侧表面。例如,第二栅极层227b可以在第一栅极层227a和垂直结构233之间和/或在第一栅极层227a与在第一栅极层227a之上和/或之下的层间绝缘层224之间。

71.在一示例中,第一栅极层227a可以是导电材料,诸如掺杂的多晶硅、金属(例如w等)、金属氮化物(例如tin等)和金属半导体化合物(例如tisi、wn、tan、nisi等),第二栅极层227b可以包括高k电介质材料。

72.在另一示例中,第一栅极层227a和第二栅极层227b可以包括不同的导电材料。例如,第一栅极层227a可以包括金属(诸如w等),第二栅极层227b可以包括金属氮化物(诸如tin等)。

73.在一些示例实施方式中,由导电材料形成的每个栅极层227的一部分(例如第一栅极层227a)可以是栅电极。

74.在一些示例实施方式中,栅极层227中的一些可以是选择栅电极(例如选择栅极线),选择栅极线中的一些可以是字栅电极(例如字栅极线)。

75.绝缘层(图3b中的218')可以设置在第一下图案层216a的接触第一图案基底211a的部分与堆叠结构221的层间绝缘层224之间。

76.垂直结构233可以包括芯图案239、至少覆盖芯图案239的侧表面的沟道层237、以及设置在沟道层237和堆叠结构221之间的数据存储结构235。数据存储结构235可以包括第一电介质层235a、第二电介质层235c以及设置在第一电介质层235a和第二电介质层235c之间的数据存储层235b。第二电介质层235c可以与沟道层237接触。沟道层237的一部分可以与第一图案结构209a接触。垂直结构233还可以包括在芯图案239下面的接触沟道层237的焊盘图案242。垂直结构233可以依次穿过第一下图案层216a和中间图案层215,并可以延伸到第一图案基底211a中。垂直结构233可以与第一虚设图案层213a'间隔开。中间图案层215可以穿过数据存储结构235,并可以与沟道层237接触。

77.在一示例中,在诸如nand快闪存储器件的存储器件中,数据存储层235b可以包括信息可存储在其中的区域。例如,数据存储层235b可以包括在栅极层227(例如字线)和沟道层237之间的可存储信息的区域。数据存储层235b可以包括能够通过捕获电荷来存储数据的材料,如在快闪存储器件中。数据存储层235b可以包括例如硅氮化物。在一示例实施方式中,数据存储层235b的硅氮化物可以用能够存储数据的另一材料代替。

78.在另一示例中,在不同于nand快闪存储器件的存储器件(例如,诸如reram等的可变电阻存储器件)中,数据存储结构235可以包括能够存储信息的数据存储层。

79.第一电介质层235a可以包括硅氧化物或高k电介质材料。

80.第二电介质层235c可以包括硅氧化物。第二电介质层235c可以掺有杂质。第二电介质层235c可以是例如隧道氧化物。

81.沟道层237可以是硅层。焊盘图案242可以包括导电材料(例如掺杂的多晶硅、金属(例如w等)、金属氮化物(例如tin)和金属半导体化合物(例如tisi、wn、tan、nisi等))中的至少一种。

82.所述多个通路287a和287b中的每个可以包括覆盖通路插塞288b的侧表面并设置在通路插塞288b的下表面和第一图案基底211a之间的通路阻挡层288a。通路阻挡层288a可以包括金属氮化物,诸如tin。

83.通路插塞288b可以包括与第二导电层291b的材料不同的材料。例如,通路插塞288b可以包括诸如w等的第一金属材料,第二导电层291b可以包括诸如al等的第二金属材料。

84.在一示例实施方式中,上绝缘结构294可以包括含有氢h的第一材料,并且氢扩散路径hp可以形成在沟道层237的接触第一图案结构209a的部分与上绝缘结构294之间,在上绝缘结构294中的氢h通过该氢扩散路径hp扩散并运动到接触沟道层237的第二电介质层235c。阻挡盖层295可以包括防止上绝缘结构294中的氢h扩散的第二材料。上绝缘结构294的第一材料可以是hdp硅氧化物和/或teos硅氧化物,阻挡盖层295的第二材料可以是硅氮化物。第二材料可以不存在于氢扩散路径hp中。例如,由氢h可通过其扩散而运动的材料形成的部件可以位于氢扩散路径hp中,例如第一导电图案290a和第二导电图案290b、所述多个第一通路287a、第一图案结构209a中的由硅层形成的中间图案层215和第一图案基底211a以及由硅层形成的沟道层237。

85.根据一些示例实施方式,在上绝缘结构294中的氢h可以不通过阻挡盖层295向外扩散和/或排放并且可以通过氢扩散路径hp扩散且运动到沟道层237,并可以通过沟道层237运动到第二电介质层235c(其可以是隧道氧化物)。因此,由于氢h可以扩散到第二电介质层235c,所以可以提高根据本发明构思的一些示例实施方式的器件1的可靠性。

86.接下来,将分别参照图4a至图4d描述图2b的剖面结构中的修改示例。图4a至图4d是对应于图2b的剖面结构的剖视图。在下文,在参照图4a至图4d的描述中,将主要基于在图2b的剖面结构中修改的部件或在先前实施方式中修改的部件给出描述,并将省略重复的描述。

87.在一修改示例中,参照图4a,图2b中的第二图案结构209b可以被省略,并且图2b中的第一输入输出接触插塞264a和所述多个第二通路287b可以用彼此接触的第一输入输出接触插塞364a和多个第二通路387代替。第一输入输出接触插塞364a可以穿过中间绝缘层218。第一输入输出接触插塞364a可以包括分别对应于导电插塞(图2b中的264a_2)和导电阻挡层(图2b中的264a_1)的导电插塞364a_2和导电阻挡层364a_1。

88.输入输出接触结构364可以包括第二输入输出接触插塞364b。第二输入输出接触插塞364b可以与第二输入输出接触插塞(图2b中的264b)相同。因此,每个输入输出接触结构364可以包括第一输入输出接触插塞364a和第二输入输出接触插塞364b。

89.所述多个第二通路387中的每个可以包括分别对应于通路插塞(图3a中的288b)和通路阻挡层(图3a中的288a)的通路插塞388b和通路阻挡层388a。所述多个第二通路387可以分别对应于第一输入输出接触插塞364a。所述多个第二通路387中的每个可以覆盖对应的第一输入输出接触插塞364a的上表面和部分侧表面。所述多个第二通路387中的每个可以具有比每个第一输入输出接触插塞364a的宽度宽的宽度。

90.在一修改示例中,参照图4b,图2b中的第二图案结构209b和所述多个第二通路287b可以被省略,并且图2b中的第一输入输出接触插塞264a可以用穿过中间绝缘层218和第一上绝缘层206的第一输入输出接触插塞464a代替。

91.图2b中的输入输出导电图案290c可以用接触第一输入输出接触插塞464a的输入输出导电图案490c代替。与输入输出导电图案490c的其它部分的上表面相比,输入输出导电图案490c的与第一输入输出接触插塞464a重叠的部分的上表面可以在向上方向上是凸起的。第一输入输出接触插塞464a可以延伸到输入输出导电图案490c中。因此,输入输出导电图案490c可以覆盖第一输入输出接触插塞464a的侧表面的部分和上表面。

92.第一输入输出接触插塞464a可以包括分别对应于导电插塞(图2b中的264a_2)和导电阻挡层(图2b中的264a_1)的导电插塞464a_2和导电阻挡层464a_1。

93.输入输出接触结构464可以包括第二输入输出接触插塞464b。第二输入输出接触插塞464b可以与第二输入输出接触插塞(图2b中的264b)相同。因此,每个输入输出接触结构464可以包括第一输入输出接触插塞464a和第二输入输出接触插塞464b。

94.在一修改示例中,参照图4c,图2b中的第二图案结构209b和所述多个第二通路287b可以被省略,并且图2b中的输入输出接触结构264可以用图4b中的输入输出接触结构464代替,图2b中的输入输出导电图案290c可以用穿过第一上绝缘层206且接触输入输出接触结构464的第一输入输出接触插塞464a的输入输出导电图案590c代替。第一上绝缘层206可以具有开口206o,输入输出导电图案590c可以在开口206o中与第一输入输出接触插塞464a接触。输入输出导电图案590c可以覆盖第一输入输出接触插塞464a的侧表面的部分和上表面。

95.在一修改示例中,参照图4d,在图2b中的第二图案结构209b中,第二下图案层216b可以被修改为穿过第二虚设图案层213b并接触第二图案基底211b。绝缘层218'可以设置在第二下图案层216b的接触第二图案基底211b的部分与盖绝缘结构229之间。第一输入输出接触插塞264a可以在与第二虚设图案层213b间隔开的位置穿过第二下图案层216b,并可以延伸到第二图案基底211b中。

96.接下来,将分别参照图5至图8描述图2a的剖面结构中的修改示例。图5至图8是对应于图2a的剖面结构的剖视图。在下文,在参照图5至图8的描述中,将主要基于在图2a的剖面结构中修改的部件或在先前实施方式中修改的部件给出描述,并将省略重复的描述。

97.在一修改示例中,参照图5,图2a中示出的所述多个第一通路287a可以用从第一图案基底211a延伸的多个第一通路687a代替,如图5所示。所述多个第一通路687a可以包括与第一图案基底211a相同的材料。例如,所述多个第一通路687a可以包括具有n型导电类型的硅层。所述多个第一通路687a可以与第一导电图案290a和第二导电图案290b接触。

98.在一修改示例中,参照图6,图2a中示出的所述多个第一通路287a可以被省略,并且图2a中示出的第一导电图案290a和第二导电图案290b可以用第一导电图案790a和第二导电图案790b代替。第一导电图案790a和第二导电图案790b可以包括通过第一上绝缘层206中的开口206a接触第一图案基底211a的部分。

99.因此,第一导电图案790a和第二导电图案790b中的每个可以具有接触第一上绝缘层206的上表面的第一下表面790s1和接触第一图案基底211a的第二下表面790s2。

100.第一导电图案790a和第二导电图案790b中的每个可以具有在第一高度水平上的第一上表面790u1和在低于第一高度水平的第二高度水平上的第二上表面790u2。第一导电图案790a和第二导电图案790b中的每个可以具有其中心部分具有相对低的水平的上表面。

101.在一修改示例中,参照图7,图2a中示出的所述多个第一通路287a可以被省略,并

且图2a中示出的第一导电图案290a和第二导电图案290b可以用第一导电图案890a和第二导电图案890b代替,其中第一导电图案890a和第二导电图案890b的各自的整个下表面与第一上绝缘层206接触。因此,第一导电图案890a和第二导电图案890b可以与第一图案基底211a电绝缘。

102.在一修改示例中,参照图8,图2a中示出的包括不同的导电材料的所述多个第一通路287a和导电图案290可以用如图8所示的导电图案990代替。例如,导电图案990的第一导电图案990a和第二导电图案990b中的每个可以包括在与图2a中示出的所述多个第一通路287a相对应的位置的通路部分990_2、以及在与图2a中示出的第一导电图案290a和第二导电图案290b相对应的位置的图案部分990_1。通路部分990_2和图案部分990_1可以包括相同的材料和/或彼此一体地形成。导电图案990可以包括例如钨或铜。

103.上绝缘结构294可以包括围绕导电图案990的侧表面的第一上绝缘层906以及设置在第一上绝缘层906上并覆盖导电图案990的第二上绝缘层993。第一上绝缘层906可以包括围绕通路部分990_2的侧表面的第一部分906a以及围绕图案部分990_1的侧表面的第二部分906b。

104.接下来,将参照图9描述图2b的剖面结构中的修改示例。图9是与图2b的剖面结构相对应的剖视图。在下文,在参照图9的描述中,将主要基于在图2b的剖面结构中修改的部件或在先前实施方式中修改的部件给出描述,并将省略重复的描述。

105.在一修改示例中,参照图9,第一结构101还可以包括:后绝缘层1010,设置在基板105的下表面下面;贯通电极1020,穿过后绝缘层1010和基板105并向上延伸以电连接到输入输出外围布线155b;绝缘间隔物1025,围绕贯通电极1020的侧表面并使贯通电极1020和基板105绝缘;以及后输入输出焊盘1030,设置在后绝缘层1010下面并电连接到贯通电极1020。贯通电极1020可以包括导电材料。

106.接下来,将参照图10描述根据一示例实施方式的器件。图10是示出根据本发明构思的一示例实施方式的器件的另一示例的剖视图。

107.参照图10,根据一示例实施方式的器件2000可以包括半导体封装,该半导体封装包括图1至图9中示出的器件1中的任何一个。器件2000可以是电子系统、数据存储系统和/或数据存储器件。根据一示例实施方式,器件2000可以包括:封装基底2010;在垂直方向上堆叠在封装基底2010上的多个半导体芯片1a、1b、1c和1d;分别设置在所述多个半导体芯片1a、1b、1c和1d的下表面上的粘合层2510、2520、2530和2540;电连接所述多个半导体芯片1a、1b、1c和1d和封装基底2010的键合引线2600;以及设置在封装基底2010上并覆盖所述多个半导体芯片1a、1b、1c和1d以及键合引线2600的绝缘模制层2700。器件2000还可以包括设置在封装基底2010下面的焊球2800。封装基底2010可以是例如印刷电路板。封装基底2010可以包括封装基板2020、设置在封装基板2020的上表面上的上焊盘2030、设置在封装基板2020的下表面上的下焊盘2025、以及设置在封装基板2020中并电连接上焊盘2030和下焊盘2025的内部布线2035。上焊盘2030可以电连接到键合引线2600。下焊盘2025可以电连接到焊球2800。

108.所述多个半导体芯片1a、1b、1c和1d中的每个可以包括图1至图9中示出的第一结构101和第二结构201。

109.所述多个半导体芯片1a、1b、1c和1d中的每个可以在其上部包括第二结构201的输

入输出键合焊盘(图2b和图10中的299p)。所述多个半导体芯片1a、1b、1c和1d可以包括第一半导体芯片1a、第二半导体芯片1b、第三半导体芯片1c和第四半导体芯片1d,每个半导体芯片具有在垂直方向上暴露并依次布置的输入输出键合焊盘(图2b和图10中的299p)。当以如图10所示的剖面取向观看时,第一半导体芯片1a和第二半导体芯片1b的输入输出键合焊盘(图2b和图10中的299p)可以设置在一侧(例如右侧)。当以如图10所示的剖面取向观看时,第三半导体芯片1c和第四半导体芯片1d的输入输出键合焊盘(图2b和图10中的299p)可以设置在其余侧(例如左侧)。

110.键合引线2600可以与输入输出键合焊盘(图2b和图10中的299p)接触并电连接到该输入输出键合焊盘。

111.所述多个半导体芯片1a、1b、1c和1d中的每个可以包括如图2a所示的堆叠结构221。堆叠结构221可以包括存储单元阵列区域mca和阶梯区域sa。图2a中示出的分隔结构248可以穿过堆叠结构221。在所述多个半导体芯片1a、1b、1c和1d的每个中,多个堆叠结构221可以被包括。在所述多个半导体芯片1a、1b、1c和1d的每个中,堆叠结构221可以具有其宽度从底部到顶部增大的形状。

112.接下来,将参照图11描述根据一示例实施方式的器件。图11是示出根据一示例实施方式的器件的一示例的剖视图。

113.参照图11,根据一示例实施方式的器件3000可以是包括如图9所示的第一结构101和第二结构201的半导体封装。器件2000可以是电子系统、数据存储系统和/或数据存储器件。例如,器件3000可以包括:封装基底3010;在垂直方向上堆叠在封装基底3010上的多个半导体芯片1a'、1b'、1c'和1d';设置在所述多个半导体芯片1a'、1b'、1c'和1d'的每个的下表面上的底部填充材料层3200;电连接所述多个半导体芯片1a'、1b'、1c'和1d'的导电凸块3100;以及设置在封装基底3010上并覆盖所述多个半导体芯片1a'、1b'、1c'和1d'的模制层3700。

114.器件3000还可以包括设置在封装基底3010下面的焊球3800。封装基底3010可以是例如印刷电路板。封装基底3010可以包括封装基板3020、在封装基板3020的上表面上的上焊盘3030、设置在封装基板3020的下表面上的下焊盘3025、以及设置在封装基板3020中并电连接上焊盘3030和下焊盘3025的内部布线3035。

115.所述多个半导体芯片1a'、1b'、1c'和1d'可以包括在垂直方向上依次布置的第一半导体芯片1a'、第二半导体芯片1b'、第三半导体芯片1c'和第四半导体芯片1d'。

116.所述多个半导体芯片1a'、1b'、1c'和1d'当中的最上面的半导体芯片可以包括如图1至图8所示的第一结构101和第二结构201,并且其余的半导体芯片可以包括如图9所示的第一结构101和第二结构201。例如,第一至第三半导体芯片1a'、1b'和1c'中的每个可以包括如图9所示的第一结构101和第二结构201,第四半导体芯片1d'可以包括如参照图1至图8描述的第一结构101和第二结构201。

117.第二结构201的输入输出键合焊盘(图2b和图10中的299p)可以位于第一至第四半导体芯片1a'、1b'、1c'和1d'的每个下面,并且后输入输出焊盘(图9和图11中的1030)可以位于第一至第三半导体芯片1a'、1b'和1c'的每个之上。

118.导电凸块3100中的一些可以设置于在所述多个半导体芯片1a'、1b'、1c'和1d'当中的位于相对高的水平上的半导体芯片的输入输出键合焊盘(图2b和图11中的299p)和位

于相对低的水平上的半导体芯片的后输入输出焊盘(图9和图11中的1030)之间,其余的导电凸块3100可以设置在最下面的半导体芯片1a'的输入输出键合焊盘(图2b和图11中的299p)与封装基底3010的上焊盘3030之间。

119.所述多个半导体芯片1a'、1b'、1c'和1d'中的每个可以包括如图2a所示的堆叠结构221。堆叠结构221可以包括存储单元阵列区域mca和阶梯区域sa。图2a中示出的分隔结构248可以穿过堆叠结构221。在所述多个半导体芯片1a'、1b'、1c'和1d'的每个中,多个堆叠结构221可以被包括。在所述多个半导体芯片1a'、1b'、1c'和1d'的每个中,堆叠结构221可以具有其宽度从底部到顶部减小的形状。

120.接下来,将参照图12a至图17b描述根据本发明构思的一示例实施方式的用于形成器件的方法的一示例。在图12a至图17b中,图12a、图13a、图14a、图15a、图16a和图17a是示出形成图2a的剖面结构的方法的剖视图,图12b、图13b、图14b、图15b、图16b和图17b是示出形成图2b的剖面结构的方法的剖视图,图13c是图13a的部分“f”的局部放大图。

121.参照图12a和图12b,可以形成第一芯片结构100。第一芯片结构100的形成可以包括在基板105上形成外围元件115。外围元件115的形成可以包括在基板105上形成限定有源区110a的隔离层110s、在有源区110a上形成外围栅极120a、以及在外围栅极120a的两侧在有源区110a中形成外围源极/漏极120b。

122.第一芯片结构100的形成还可以包括在基板105上形成下绝缘层125和第一外围布线150。下绝缘层125可以覆盖外围元件115。第一外围布线150可以电连接到外围元件115。

123.第一芯片结构100的形成还可以包括在下绝缘层125上形成第一绝缘结构130、第二外围布线155a、输入输出外围布线155b和第一接合焊盘160a、160b、160c和160d。

124.第一绝缘结构130可以形成为包括多个金属间电介质层135a、135b和135c、多个下阻挡层140a和140b以及第一接合绝缘层145。例如,第一金属间电介质层135a、第一下阻挡层140a、第二金属间电介质层135b和第二下阻挡层140b、第三金属间电介质层135c和第一接合绝缘层145可以依次堆叠以形成绝缘结构130。第二外围布线155a可以形成为与第一外围布线150电连接。

125.第一接合焊盘160a、160b、160c和160d可以包括下位线接合焊盘160a、下栅极接合焊盘160b、下源极接合焊盘160c和下输入输出接合焊盘160d。下位线接合焊盘160a、下栅极接合焊盘160b和下源极接合焊盘160c中的每个可以电连接到第二外围布线155a。下输入输出接合焊盘160d可以电连接到输入输出外围布线155b。

126.参照图13a、图13b和图13c,可以形成第二芯片结构200。第二芯片结构200的形成可以包括在牺牲基板203上形成绝缘层206。绝缘层206可以由例如含氢的硅氧化物形成。

127.第二芯片结构200的形成还可以包括形成第一图案结构209a和第二图案结构209b以及围绕第一图案结构209a的侧表面和第二图案结构209b的侧表面的中间绝缘层218。

128.第一图案结构209a和第二图案结构209b的形成可以包括依次形成和图案化图案基底、在图案基底上具有开口的下图案层以及覆盖下图案层并通过下图案层的开口接触图案基底的上图案层。

129.例如,第一图案结构209a可以包括第一图案基底211a、在第一图案基底211a上具有开口的图案层213a、以及覆盖图案层213a并通过图案层213a的开口接触第一图案基底211a的第一下图案层216a。第二图案结构209b可以包括第二图案基底211b、设置在第二图

案基底211b上的图案层213b以及设置在图案层213b上的第二下图案层216b。图案层213a和213b中的每个可以包括依次堆叠的第一层214a、第二层214b和第三层214c。

130.第一图案基底211a和第二图案基底211b可以包括具有n型导电类型的硅。第一层214a和第三层214c可以包括硅氧化物,第二层214b可以包括硅氮化物或多晶硅。第一下图案层216a和第二下图案层216b可以包括具有n型导电类型的硅。

131.第二芯片结构200的形成还可以包括在第一图案结构209a上形成模制结构220。模制结构220可以包括交替且重复堆叠的层间绝缘层224和模制层226。模制结构220可以在至少一侧具有台阶形状。在层间绝缘层224和模制层226当中,最下面的层和最上面的层可以是层间绝缘层。

132.第二芯片结构200的形成可以包括:在具有模制结构220的基板上形成绝缘层以及平坦化该绝缘层以形成第一盖绝缘层231;形成穿过模制结构220并延伸到第一图案结构209a中的沟道孔;以及在沟道孔中形成垂直结构233。垂直结构233的形成可以包括依次形成数据存储结构235和沟道层237以覆盖沟道孔的内壁、形成部分填充沟道孔的芯图案239、以及形成填充沟道孔的其余部分的焊盘图案242。

133.数据存储结构235的形成可以包括依次形成第一电介质层235a、数据存储层235b和第二电介质层235c。

134.沟道层237可以包括半导体,例如未掺杂的硅。芯图案239可以包括硅氧化物。焊盘图案242可以包括掺杂的半导体(例如具有n型导电类型的硅)。第一电介质层235a可以包括硅氧化物或掺有杂质的硅氧化物。数据存储层235b可以由能够捕获电荷的数据存储材料形成,诸如硅氮化物等。第二电介质层235c可以包括硅氧化物或高k电介质材料。

135.第二芯片结构200的形成还可以包括在模制结构220和第一盖绝缘层231上形成第二盖绝缘层245、以及形成穿过第二盖绝缘层245和模制结构220并延伸到第一图案结构209a中的分隔沟槽247。

136.参照图14a和图14b,第二芯片结构200的形成还可以包括蚀刻图案层213a的通过分隔沟槽247暴露的部分以暴露垂直结构233的数据存储结构235;蚀刻暴露的数据存储结构235以暴露垂直结构233的沟道层237;填充开口;以及形成接触沟道层237的中间图案层215。中间图案层215可以由具有n型导电类型的硅层形成。

137.图案层213a中的一些可以保留并可以被称为第一虚设图案层213a',接触第二图案基底211a的图案层213b可以被称为第二虚设图案层。

138.第二芯片结构200的形成还可以包括去除通过分隔沟槽247暴露的模制层226、在从其去除模制层226的空间中形成栅极层227、以及填充分隔沟槽247以形成分隔结构248。依次堆叠的层间绝缘层224和栅极层227可以形成堆叠结构221。

139.第二芯片结构200的形成可以包括在分隔结构248和第二盖绝缘层245上形成第三盖绝缘层251和第四盖绝缘层254。第一至第四盖绝缘层231、245、251和254可以形成盖绝缘结构229。

140.第二芯片结构200的形成还可以包括形成位线接触插塞257、栅极接触结构260、源极接触结构262和输入输出接触结构264。

141.栅极接触结构260可以与栅极层227的栅极焊盘接触并可以在垂直方向z上延伸以穿过盖绝缘结构229。源极接触结构262可以与第一图案结构209a接触并可以在垂直方向z

上延伸以穿过盖绝缘结构229。输入输出接触结构264可以与第二图案结构209b接触并可以在垂直方向z上延伸以穿过盖绝缘结构229。

142.每个栅极接触结构260可以包括第一栅极接触插塞260a和设置在第一栅极接触插塞260a上的第二栅极接触插塞260b。源极接触结构262可以包括第一源极接触插塞262a和设置在第一源极接触插塞262a上的第二源极接触插塞262b。每个输入输出接触结构264可以包括第一输入输出接触插塞264a和设置在第一输入输出接触插塞264a上的第二输入输出接触插塞264b。

143.第一栅极接触插塞260a的上表面、第一源极接触插塞262a的上表面和第一输入输出接触插塞264a的上表面可以形成在比栅极层227当中的最上面的栅极层的水平高的水平上。

144.第二芯片结构200的形成还可以包括在盖绝缘结构229上形成第一金属间电介质层277a、以及形成穿过第一金属间电介质层277a的位线267、栅极布线269、源极布线271和输入输出布线273。位线267可以电连接到位线接触插塞257,栅极线269可以电连接到栅极接触结构260,源极线271可以电连接到源极接触结构262,输入输出布线273可以电连接到输入输出接触结构264。

145.第二芯片结构200的形成还可以包括依次形成第一上阻挡层279a和第二金属间电介质层277b、以及形成穿过第一上阻挡层279a和第二金属间电介质层277b的位线连接布线283a、栅极连接布线283b、源极连接布线283c和输入输出连接布线283d。

146.位线连接布线283a可以电连接到位线267,栅极连接布线283b可以电连接到栅极布线269,源极连接布线283c可以电连接到源极布线271,输入输出连接布线283d可以电连接到输入输出布线273。

147.第二芯片结构200的形成可以包括依次形成第二上阻挡层279b、第三金属间电介质层277c和第二接合绝缘层281、以及形成穿过第二上阻挡层279b、第三金属间电介质层277c和第二接合绝缘层281的第二接合焊盘285a、285b、285c和285d。

148.第二接合焊盘285a、285b、285c和285d可以包括电连接到位线连接布线283a的上位线接合焊盘285a、电连接到栅极连接布线283b的上栅极接合焊盘285b、电连接到源极连接布线283c的上源极接合焊盘285c以及电连接到输入输出连接布线283d的上输入输出接合焊盘285d。

149.参照图15a和图15b,图12a和图12b中的第一芯片结构100和图14a和图14b中的第二芯片结构200可以彼此接合。例如,第一芯片结构100的第一接合绝缘层145和第二芯片结构200的第二接合绝缘层281可以彼此接触并彼此键合,第一芯片结构100的第一接合焊盘160a、160b和160c和第二芯片结构200的第二接合焊盘285a、285b和285c可以彼此接触并彼此键合。

150.在接触第二芯片结构200之后,第一芯片结构100可以被称为第一结构101。

151.第二芯片结构200的牺牲基板203可以被去除以暴露绝缘层206。绝缘层206可以被称为第一上绝缘层。

152.参照图16a和图16b,可以形成穿过第一上绝缘层206的通路287a和287b。通路287a和287b可以包括接触第一图案基底211a的第一通路287a和接触第二图案基底211b的第二通路287b。

153.可以在第一上绝缘层206上形成导电图案290。导电图案290包括与第一图案结构209a重叠的第一金属图案290a和第二金属图案290b、以及不与第一图案结构209a重叠的输入输出金属图案290c。每个导电图案290可以包括依次堆叠的第一导电层291a、第二导电层291b和第三导电层291c。第一导电图案290a和第二导电图案290b中的每个可以与第一通路287a接触,输入输出金属图案290c可以与第二通路287b接触。

154.参照图17a和图17b,可以在第一上绝缘层206上依次形成第二上绝缘层293和阻挡盖层295以覆盖导电图案290。第一上绝缘层206和第二上绝缘层293可以由含氢的硅氧化物形成。例如,第一上绝缘层206或第二上绝缘层293中的至少一个可以由hdp氧化物或teos氧化物形成。

155.阻挡盖层295可以由能够防止第一上绝缘层206和第二上绝缘层293中的氢通过阻挡盖层295逸出到外部的材料形成。例如,阻挡盖层295可以包括硅氮化物。

156.可以执行热处理297。在热处理297期间,在第一上绝缘层206和第二上绝缘层293中的氢可以扩散到第二电介质层235c中。氢通过其扩散的氢扩散路径可以与图3a中示出的氢扩散路径hp相同。

157.再次,参照图2a和图2b,可以在阻挡盖层295上形成钝化层298。可以形成依次穿过钝化层298、阻挡盖层295和第二上绝缘层293并暴露输入输出金属图案290c的第二导电层291b的焊盘开口299o。输入输出金属图案290c的第二导电层291b的通过输入输出焊盘开口299o暴露的部分可以被定义为输入输出键合焊盘299p。

158.根据上述示例实施方式的器件1可以用于需要数据存储的计算机系统、无线通信装置、便携式计算机、便携式智能手机、网络平板电脑、固态盘(ssd)、便携式存储装置、家用电器和/或能够在无线环境中发送和接收信息的任何装置。例如,本发明构思可以包括固态盘(ssd)和/或系统,其包括根据上述实施方式的器件1。

159.根据本发明构思的示例实施方式,可以提供能够提高其集成度和其可靠性的器件。

160.本发明构思的各种有益的优点和效果可以不限于上述内容,并可以在描述本发明构思的具体实施方式的过程中被更容易地理解。

161.尽管以上已经示出和描述了示例实施方式,但是对于本领域技术人员将是明显的,在不脱离如由所附权利要求限定的本发明构思的范围的情况下,可以进行修改和变化。

162.本技术要求于2020年6月26日在韩国知识产权局提交的韩国专利申请第10

‑

2020

‑

0078286号的优先权权益,其公开内容通过引用整体地结合于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1