一种降低WLCSP芯片的RDSON的阻值的方法与流程

一种降低wlcsp芯片的rdson的阻值的方法

技术领域

1.本发明涉及半导体器件封装技术领域,特别是涉及一种降低wlcsp芯片的rdson的阻值的方法。

背景技术:

2.在微机电系统(mems)行业中,晶圆片级芯片规模封装技术(wafer level chip scale packaging,wlcsp)因具有高密度、体积小、可靠性高,电热性能优良等优点而应用愈加广泛。金氧半场效晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)采用wlcsp封装工艺所制备的wlcsp芯片能通过常规的表面贴装技术与印刷电路板(pcb)连接,从而能降低该wlcsp芯片与pcb之间的杂散电感电容,为了在相同面积的pcb上连接更多的mosfet,现有的技术方案是将多个mosfet采用wlcsp封装工艺制备单个wlcsp芯片。

3.本技术中,将多个mosfet采用wlcsp封装工艺制备的单个芯片记载为wlcsp芯片,wlcsp芯片的静态通态电阻(static drain

‑

to

‑

source on

‑

resistance,rdson)的阻值大小是判断该wlcsp芯片性能的一个重要指标,rdson的阻值减小能提高该wlcsp芯片的导通电流。

技术实现要素:

4.本发明提供一种降低wlcsp芯片的rdson的阻值的方法,为方便叙述,本技术中,将wlcsp芯片上设置有g基极和s源极的端面记载为底端面,将wlcsp芯片上设置有d漏极的另一端面记载为顶端面。

5.为实现上述目的,本发明采用如下技术方案:一种降低wlcsp芯片的rdson的阻值的方法,包括如下步骤:

6.s1、在wlcsp芯片的顶端面制备焊盘,焊盘覆盖顶端面上的d漏极,焊盘包括堆叠的粘附层、连接层和结合层,粘附层和d漏极相黏附;其中,粘附层为金属钛(ti)形成的金属层,连接层为金属镍(ni)形成的金属层,结合层为金属银(ag)形成的金属层;

7.s2、在结合层上制备金属铜(cu)层,形成外延层。

8.其中,粘附层的厚度不大于0.1μm,粘附层的导电性能良好且与d漏极能够形成良好欧姆接触。

9.其中,连接层的厚度不大于0.2μm,由于粘附层和结合层之间的结合力较差,因此在粘附层和结合层之间设置连接层来提高结合力,若连接层的厚度过厚则由于应力过大会造成焊盘脱落现象。

10.其中,结合层的厚度不大于1μm,若结合层的厚度过厚会导致wlcsp芯片的成本显著提升。

11.其中,金属铜层的厚度为20

‑

25μm。

12.在一实施例中,在wlcsp芯片的顶端面采用物理气相沉积工艺制备焊盘,在wlcsp

芯片的顶端面上依次制备粘附层、连接层和结合层。

13.在一实施例中,采用电镀工艺在结合层上沉积铜层。

14.相比于现有技术,本发明提供的技术方案的有益效果为:在焊盘的结合层上增加金属铜层,能在不显著增加wlcsp芯片的成本的情况下有效降低wlcsp芯片的rdson的阻值,从而能提高该wlcsp芯片的导通电流。

15.下面结合具体实施例进行说明。

附图说明

16.附图对本发明作进一步说明,但附图中的实施例不构成对本发明的任何限制。

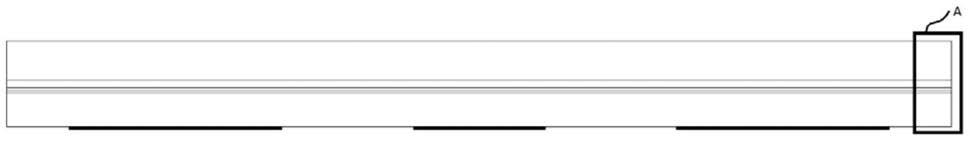

17.图1为本发明一实施例提供的wlcsp芯片的正视图。

18.图2为图1局部a的放大图。

19.图3为本发明一实施例提供的wlcsp芯片的仰视图。

20.图4为本发明一实施例提供的wlcsp芯片的电流走向和电阻分布示意图。

21.其中,附图标记为:1.wlcsp芯片;21.ti金属层;22.ni金属层;23.ag金属层;3.cu金属层。

具体实施方式

22.应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

23.本实施例提供一种降低wlcsp芯片1的rdson的阻值的方法,包括如下步骤:

24.s1、将wlcsp芯片1的顶端面进行清洁处理后装载到磁控溅射炉中,采用磁控溅射炉溅射完ti金属层21后,继续溅射ni金属层22,最后溅射ag金属层23,将wlcsp芯片1从磁控溅射炉中取出后进行清洗和烘干,完成制备焊盘;

25.s2、将除了wlcsp芯片1的顶端面外的其余面进行物理隔绝和绝缘处理(例如涂覆保护胶),然后将wlcsp芯片1作为阴极浸入电镀液中进行电镀铜,阳极采用电解铜,电镀液包括200

‑

300ml/l的铜补充剂和270

‑

330g/l的焦磷酸钾,1asd对应的金属铜的还原沉积的速率约0.1微米/分钟;

26.s3、在ag金属层23上沉积的cu金属层3达到设定的厚度后停止电镀,从电镀液中取出wlcsp芯片1后进行清洗和烘干。

27.在步骤s1中溅射ti金属层21的溅射条件为:溅射功率为2500

‑

2700w,ar气流量40

‑

44sccm,工作气压为0.5

‑

0.7pa,ti金属层21的厚度为0.1μm;

28.在步骤s1中溅射ni金属层22的溅射条件为:溅射功率为2100

‑

2300w,ar气流量为34

‑

38sccm,工作气压为0.5

‑

0.7pa,ni金属层22厚度为0.2μm。

29.在步骤s1中溅射ag金属层23的溅射条件为:溅射功率为2500

‑

2700w,ar气流量为18

‑

22sccm,n2气流量为7

‑

9sccm,工作气压为0.5

‑

0.7pa,ag金属层23的厚度为1μm。

30.在步骤s2中沉积金属铜的厚度为20

‑

25μm。

31.本实施例提供一种降低wlcsp芯片1的rdson的阻值的方法,该方法得到的wlcsp芯片1的结构如图1

‑

3中所示。本实施中,wlcsp芯片1是两个mosfet采用wlcsp封装工艺制备的单个芯片,因此wlcsp芯片1的底端面设置有两个s1源极、一个g1基极、两个s2源极和一个g2基极,wlcsp芯片1的顶端面设置有d1漏极和d2漏极(附图中未显示)。d1漏极和d2漏极互不

连接,d1漏极、两个s1源极和一个g1基极属于其中一个mosfet,d2漏极、两个s2源极和一个g2基极属于另一个mosfet。焊盘完全覆盖wlcsp芯片1的顶端面的d1漏极和d2漏极,d1漏极和d2漏极之间通过焊盘电性连接。焊盘远离wlcsp芯片1的端面沉积有铜层。

32.如图4所示,该wlcsp芯片1处于工作状态时,电流的依次流过s1源极、d1漏极、d2漏极、s2源极,因此该wlcsp芯片1可等效为两个串联的mosfet,g1基极和g2基极能够分别独立驱动控制。因此对于该wlcsp芯片1上的电流路径的分析,可以得出该wlcsp芯片1的rdson的阻值为r1+r2+r3,由于r=ρl/s(其中,ρ表示电阻的电阻率,是由其本身性质决定,l表示电阻的长度,s表示电阻的横截面积),因此r1的主要影响因素为s1源极至d1漏极的路程(可等效为wlcsp芯片1的厚度),r3的主要影响因素为d2漏极至s2源极的路程(可等效为wlcsp芯片1的厚度),由于wlcsp芯片1的厚度是固定的,因此r1和r3可以认定为是固定值,因此需要降低wlcsp芯片1的rdson的阻值则需要降低r2的阻值。r2的主要影响因素为横截面积s和电阻率ρ。本实施例提供的方法,在焊盘的结合层上沉积金属铜层,即焊盘的厚度叠加金属铜层的厚度,能显著提升横截面积s并同时保持较低的电阻率ρ,从而显著降低r2的阻值。

33.本实施例提供一种降低wlcsp芯片1的rdson的阻值的方法,该方法在保证不显著增加wlcsp芯片1的整体厚度的情况下显著降低rdson的阻值,该方法在wlcsp芯片1的顶端面制备焊盘和cu金属层3是基于以下考虑因素:

34.1.在不能显著增加wlcsp芯片1的成本的情况下选择电阻率ρ低的金属来增加厚度,由于cu的导电性仅次于ag,但差异不大,因此选择在焊盘上沉积一定厚度的cu金属层3来增加横截面积s;

35.2.由于wlcsp芯片1的表面为硅基材料,因此需要确保作为打底层的粘附层要同时满足和d漏极形成良好欧姆接触,并且粘附层要与wlcsp芯片1的表面的结合力好,因此粘附层选用ti金属层21;

36.3.ag金属层23能增强cu金属层3和焊盘的结合力,由于cu金属层3的厚度大于焊盘的厚度,因此需要根据cu金属层3的厚度来设置ag金属层23的厚度,通过一定厚度的ag金属层23来保证cu金属层3和焊盘的结合力;

37.4.经过测试发现沉积cu金属层3的厚度为20

‑

25μm时,wlcsp芯片1的rdson的阻值降低显著,cu金属层3的厚度超过25μm时,wlcsp芯片1的rdson的阻值降低不明显,出于成本的考虑和过厚的cu金属层3有从焊盘上脱落的风险,因此将cu金属层3的厚度限定为20

‑

25μm。

38.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

39.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1