一种微显示器件及其制作方法与流程

1.本技术属于半导体技术领域,特别是涉及一种微显示器件及其制作方法。

背景技术:

2.随着传统平板显示和微型投影显示技术的发展,未来可期的主流核心显示micro-led无机发光二极管技术具有显著的性能优势越来越引起人们的广泛关注。micro-led可视为微小化的led,可单独点亮,具有低功耗、高亮度、高清晰度与长寿命等优势,其未来将成为能与amoled显示并驾齐驱的新型显示技术。

3.micro-led芯片结构主要包括正装芯片、倒装芯片和垂直芯片,正装芯片的金属电极位于出光面,出光效率较低;垂直芯片制作工艺复杂且不成熟;倒装芯片在microled尺寸缩小后,也存在发光效率较低的问题。

技术实现要素:

4.有鉴于此,本技术主要解决的技术问题是提供一种微显示器件及其制作方法。

5.为解决上述技术问题,本技术采用的一个技术方案是:提供一种微显示器件,包括衬底层、第一半导体层、多量子阱层、第二半导体层、绝缘层、第一电极和第二电极;第一半导体层、多量子阱层和第二半导体层依次设置于衬底层上,多量子阱层与第一半导体层接触的面为第一端面;绝缘层与多量子阱层同层设置,且具有一开孔,多量子阱层是位于开孔的沉积层和/或生长层,绝缘层与第一半导体层接触的面为第二端面,第一端面和第二端面共面;第一电极与第一半导体层电连接,第二电极层与第二半导体层电连接。

6.其中,第二半导体层是位于多量子阱层上的沉积层和/或生长层;第一半导体层一侧在衬底层的投影超出第二半导体层和多量子阱层同侧在衬底层的投影,使得第一半导体层的一侧露出于第二半导体层并形成台阶部。

7.其中,第一电极设置于台阶部上。

8.为解决上述技术问题,本技术采用的又一个技术方案是:提供一种微显示器件的制作方法,包括:

9.在衬底层上制作一层第一半导体层;

10.在第一半导体层远离衬底层一侧制作第一绝缘层;

11.图案化刻蚀第一绝缘层,形成第一开孔;

12.在第一开孔位置的第一半导体层上沉积和/或生长多量子阱层;

13.在多量子阱层上形成第二半导体层。

14.其中,第一绝缘层所处位置构成目标位置;

15.在多量子阱层上形成第二半导体层之后包括:

16.在目标位置处形成第一电极,第一电极与第一半导体层电连接。

17.其中,在第一绝缘层所处位置形成第一电极包括:

18.去除第一绝缘层,

19.在多量子阱层的侧面、以及目标位置处的第一半导体层背离衬底层的表面,形成第二绝缘层;

20.图案化刻蚀目标位置处的第二绝缘层,形成第二开孔,第二开孔正对第一半导体层,且不与多量子阱层接触;

21.在第二开孔中沉积和/或生长第一电极。

22.其中,在多量子阱层的侧面、以及目标位置处的第一半导体层背离衬底层的表面,形成第二绝缘层,包括:

23.制作第二绝缘层,第二绝缘层覆盖第一半导体层和第二半导体层背离衬底层的表面、第二半导体层和多量子阱层的侧面。

24.其中,第一开孔的数量为至少两个,多量子阱层的数量为至少两个;

25.去除第一绝缘层包括:

26.制作第三绝缘层,第三绝缘层覆盖第二半导体层、多量子阱层和第一绝缘层;

27.刻蚀第三绝缘层、第一绝缘层以及第一半导体层,形成沟槽,沟槽将相邻两个第一开孔分离,且沟槽侧壁与多量子阱层不直接接触;

28.去除第一绝缘层和第三绝缘层;

29.其中,第二开孔靠近于多量子阱层。

30.其中,在第一开孔位置的第一半导体层上沉积和/或生长多量子阱层包括:

31.在至少两个第一开孔位置的第一半导体层上一次沉积和/或生长多量子阱层,使得多量子阱层与第一开孔一一对应;

32.在多量子阱层上形成第二半导体层包括:在至少两个多量子阱层一次形成第二半导体层。

33.其中,在多量子阱层上形成第二半导体层之后包括:

34.制作第二电极,第二电极与第二半导体层电连接。

35.本技术的有益效果是:区别于现有技术,本技术提供的微显示器件可以包括至少两个阵列设置的微显示器件,且相邻两个微显示器件相互不影响。本技术实施例中,制作的微显示器件多量子阱层通过直接沉积制作而成,不会对多量子阱层的侧壁造成损伤,可以提高微显示器件的发光效率。本技术实施例制作的微显示器件不需要刻蚀第二半导体层以使得第一半导体层形成台阶部,可以减少缩短微显示器件的工艺制作流程,简化制程,确保微显示器件的外观形貌的完整性。本技术实施例的微显示器件的制作方法,通过设置第二绝缘层,可以保护多量子阱层的侧壁,确保外界环境不会对多量子阱层造成损伤。

附图说明

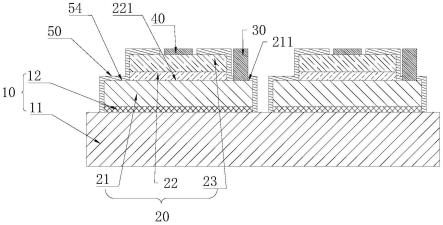

36.图1是本技术微显示器件一实施例的结构示意图;

37.图2是本技术微显示器件另一实施例的结构示意图;

38.图3是本技术微显示器件制作方法第一实施例的流程步骤示意图;

39.图4是本技术微显示器件制作一实施例的流程示意图;

40.图5是本技术微显示器件制作方法第二实施例的流程步骤示意图;

41.图6是本技术微显示器件制作方法第三实施例的流程步骤示意图;

42.图7a-7g是本技术微显示器件制作另一实施例的流程示意图;

43.图8本技术微显示器件制作方法第四实施例的流程步骤示意图;

44.图9a-9i是本技术微显示器件制作再一实施例的流程示意图。

45.其中,10、衬底层;11、蓝宝石衬底;12、缓冲层;20、发光组件;21、第一半导体层;211、台阶部;22、多量子阱层;221、第一端面;23、第二半导体层;24、导电层;30、第一电极;40、第二电极;50、绝缘层;51、第一绝缘层;52、第二绝缘层;53、第三绝缘层;54、第二端面;61、第一开孔;62、第二开孔;63、第三开孔;65、沟槽。

具体实施方式

46.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。

47.如图1所示,本技术实施例提供一种微显示器件,包括衬底层10、第一半导体层21、多量子阱层22、第二半导体层23、绝缘层50、第一电极30和第二电极40;第一半导体层21、多量子阱层22和第二半导体层23依次设置于衬底层10上,多量子阱层22与第一半导体层21接触的面为第一端221;绝缘层50与多量子阱层22同层设置,且具有一开孔(图未标),多量子阱层22是位于开孔的沉积层和/或生长层,绝缘层50与第一半导体层21接触的面为第二端面54,第一端面221和第二端面54共面;第一电极30与第一半导体层21电连接,第二电极40层与第二半导体层23电连接。

48.本技术实施例的微显示器件,多量子阱层22直接沉积和/或生长于绝缘层50所在的开孔位置处,使得多量子阱层22的第一端面221与绝缘层50的第二端面54在同一平面上;本技术实施例采用直接沉积和/或生长在开孔所在位置处,使得在制作微显示器件的过程中不需要刻蚀多量子阱层22,不会对多量子阱层22的侧壁造成损伤,本技术实施例的微显示器件可以保持多量子阱层22侧壁完整,不会有刻蚀的划痕,提高微显示器件的内量子效率,从而可以提高微显示器件的发光效率,本技术实施例的微显示器件尤其可以提高微显示器件在低电流密度下的发光效率,减小微显示器件的功耗。

49.本技术实施例,第二半导体层23是位于多量子阱层22上的沉积层和/或生长层;第一半导体层21一侧在衬底层10的投影超出第二半导体层23和多量子阱层22同侧在衬底层10的投影,使得第一半导体层21的一侧露出于第二半导体层23并形成台阶部211。本技术实施例中,第二半导体层23也通过直接沉积和/或生长在绝缘层50开孔位置处的多量子阱层22上,使得也不需要刻蚀第二半导体层23,即可以在第一半导体层21上直接形成台阶部211。

50.本技术实施例,第一电极30设置于台阶部211上,本技术实施例中,第一电极30直接设置于台阶部211上,使得第一电极30可以直接与第一半导体层21接触,使得第一电极30与第一半导体层21电连接。

51.本技术实施例的微显示器件,不需要通过刻蚀工艺刻蚀第一半导体层21和多量子阱层22以使得第一半导体层21裸露以便于沉积第一电极30。若通过刻蚀工艺刻蚀第一半导体层21和多量子阱层22制作第一半导体层21的台阶部211时,为了使得第一半导体层21露出台阶部211,必定会过渡刻蚀第一半导体层21和多量子阱层22,以确保台阶部211上的多量子阱层22刻蚀完全,此时必定导致第一半导体层21的台阶部211要低于第一半导体层21靠近多量子阱层22位置处的台阶部211,造成绝缘层50的第二端面54与多量子阱层22的第

一端面221不在同一平面上。

52.本技术实施例中,第一半导体层21为n型半导体层,具体地,本技术是实施例中,n型半导体层的材质包括n型gan。第二半导体层23为p型半导体层,具体地,本技术是实施例中,p型半导体层的材质包括p型gan。第一电极30为n电极,第二电极40为p电极,本技术实施例中,第一电极30、第二电极40的材质包括铬、铂和金等材质,上述仅为具体举例,本技术实施例,对第一半导体层21、第二半导体层23、第一电极30和第二电极40的材质并不做具体限定。本技术实施例,第二电极40直接与第二半导体层23接触,在其他实施例中,如图2所示,第二半导体层23上还设置ito导电层24,第二电极40通过ito导电层24与第二半导体层23点连接。

53.继续如图1和图2所示,本技术实施例中,衬底层10包括蓝宝石衬底11以及设置在蓝宝石衬底11上的缓冲层12,缓冲层12可以是一层,也可以是两层以上,在本技术一具体实施例中,缓冲层12包括一层aln层和一层gan层,在其他实施例中,蓝宝石衬底11也可以为其他材质的衬底层10,缓冲层12也可以是其他材质。

54.本技术实施例还包括第二个技术方案,如图3和图4,本技术一种微显示器件的制作方法的第一实施例,包括:

55.s110,在衬底层10上制作一层第一半导体层21。

56.本技术实施例中,在蓝宝石衬底11上采用气相外延生长法(mocvd)生长一层aln缓冲层12和一层gan缓冲层12作为衬底层10。并在gan缓冲层12上采用气相外延生长法继续生长一层n-gan层作为第一半导体层21。本技术实施例仅为举例,在其他实施例中,也可以采用其他方法沉积或生长一层第一半导体层21。

57.s120,在第一半导体层21远离衬底层10一侧制作第一绝缘层51。

58.本技术实施例中,在步骤s110制作的第一半导体层21上继续采用气相外延生长法(mocvd)生长一层siox层作为第一绝缘层51。本技术实施例中,第一绝缘层51为siox,在其他实施例中,第一绝缘层51的材质也可以为其他材质,本技术实施例中对第一绝缘层51的材质并不做具体限定。

59.s130,图案化刻蚀第一绝缘层51,形成第一开孔61。

60.本技术实施例中,采用图形化掩膜版遮挡,刻蚀第一绝缘层51,像素化开孔,形成第一开孔61,通过控制第一开孔61的大小,可以控制微显示器件的发光区域的大小。本技术实施例中,采用湿法刻蚀第一绝缘层51,采用固化图形化的光刻胶遮挡第一绝缘层51,固化图形化的光刻胶,并采用刻蚀液刻蚀第一绝缘层51,形成第一开孔61,去除光刻胶,即获得在第一绝缘层51上形成第一开孔61。在其他实施例中,也可采用干法刻蚀第一绝缘层51,通过采用图形化的光刻胶遮挡,采用离子束轰击制作第一开孔61,去除图形化的光刻胶。

61.s140,在第一开孔61位置的第一半导体层21上沉积和/或生长多量子阱层22。

62.本技术实施例中,继续采用气相外延生长法在第一开孔61位置的第一半导体层21上生长一层多量子阱层22。本技术实施例中生长的多量子阱层22恰好位于微显示器件的发光区域。本技术实施例并不限制多量子阱层22的制作方法,在其他实施例中,也可以采用其他沉积或生长方法制作。

63.s150,在多量子阱层22上形成第二半导体层23。

64.本技术实施例中,继续采用气相外延生长法在多量子阱层22上生长一层第二半导

体层23,本技术实施例中,还可以在第二半导体层23上继续采用气相外延生长法生长一层电子束蒸发ito导电层24等,在其他实施例中,也可以不生长ito导电层24。

65.本技术实施例中,还包括制作第一电极30和第二电极40,使得第一电极30与第一半导体层21电连接,第二电极40与第二半导体层23电连接。

66.本技术实施例的微显示器件的制作方法,采用第一绝缘层51形成第一开孔61,使得多量子阱层22可以直接形成于第一开孔61位置处,使得本技术实施例的微显示器件可以不用通过刻蚀法刻蚀多量子阱层22,即可以在第一半导体层21未形成第一开孔61的位置处形成台阶部211,便于第一电极30的制作。本技术实施例不会对多量子阱层22的侧壁造成损伤,使得多量子阱层22的侧壁不会有刻蚀的划痕,可以保持多量子阱层22侧壁完整,提高微显示器件的内量子效率,提高微显示器件的发光效率,减小微显示器件的功耗。

67.本技术的第二实施例中,如图4和图5所示,一种微显示器件的制作方法,包括:

68.s210,在衬底层10上制作一层第一半导体层21。

69.同上述实施例,在此不再赘述。

70.s220,在第一半导体层21远离衬底层10一侧制作第一绝缘层51。

71.同上述实施例,在此不再赘述。

72.s230,图案化刻蚀第一绝缘层51,形成第一开孔61。

73.本技术实施例中,采用图形化掩膜版遮挡,刻蚀第一绝缘层51,像素化开孔,形成第一开孔61,通过控制第一开孔61的大小,可以控制微显示器件的发光区域的大小。本技术实施例中,采用湿法刻蚀第一绝缘层51,采用固化图形化的光刻胶遮挡第一绝缘层51,固化图形化的光刻胶,并采用刻蚀液刻蚀第一绝缘层51,形成第一开孔61,去除光刻胶,即获得在第一绝缘层51上形成第一开孔61。在其他实施例中,也可采用干法刻蚀第一绝缘层51,通过采用图形化的光刻胶遮挡,采用离子束轰击制作第一开孔61,去除图形化的光刻胶,即可形成第一开孔61。

74.本技术实施例中,第一绝缘层51未形成第一开孔61的位置定义为目标位置。

75.s240,在第一开孔61位置的第一半导体层21上沉积和/或生长多量子阱层22。

76.同上述实施例,在此不再赘述。

77.s250,在多量子阱层22上形成第二半导体层23。

78.同上述实施例,在此不再赘述。

79.s260,在目标位置处形成第一电极30,第一电极30与第一半导体层21电连接。

80.本技术实施例中,第二半导体层23和多量子阱层22与目标位置处的第一半导体层21形成台阶,本技术实施例中,使得第一半导体层21形成台阶部211,本技术实施例中,在目标位置处可以通过刻蚀形成第二开孔62,采用热蒸镀的工艺方法在第二开孔62位置处蒸镀形成第一电极30,此时第一电极30与第一半导体层21电连接。在其他实施例中,也可以通过直接去除第一绝缘层51,在目标位置处采用图形化的掩膜版遮挡,热蒸镀形成第一电极30,使得第一电极30与第一半导体层21直接接触形成电连接。

81.本技术实施例中,还包括在第二半导体层23上或第二半导体生上的ito导电层24上制作第二电极40,使得第二电极40与第二半导体层23电连接。

82.本技术实施例中,通过直接在目标位置处制作第一电极30,可以完成第一电极30的制作,使得制作微显示器件的制作步骤简单。

83.本技术的第三实施例中,如图6所示,一种微显示器件的制作方法,包括:

84.s310,如图7a所示,在衬底层10上制作一层第一半导体层21。

85.本技术实施例中,在蓝宝石衬底11上采用气相外延生长法(mocvd)生长一层aln缓冲层12和一层gan缓冲层12作为衬底层10。并在gan缓冲层12上采用气相外延生长法继续生长一层n-gan层作为第一半导体层21。本技术实施例仅为举例,在其他实施例中,也可以采用其他方法沉积或生长一层第一半导体层21。

86.本另一实施例也可以在衬底层10上制作一层第四绝缘层(图未示),并通过图案化刻蚀第四绝缘层,以形成第四开孔(图未示),并在第四开孔中制作第一半导体层21,本技术实施例中,第四开孔的数量可以为一个或至少两个。

87.s320,如图7a所示,在第一半导体层21远离衬底层10一侧制作第一绝缘层51。

88.同上述实施例,在此不再赘述。

89.s330,如图7b所示,图案化刻蚀第一绝缘层51,形成第一开孔61。

90.本技术实施例与上述实施例相同,在此不再赘述。

91.在其他实施例中,若第一半导体层21在第四开孔中沉积或生长而成,则第四开孔在衬底层上投影覆盖第一开孔61在衬底层上的投影,且第四开孔面积大于第一开孔61面积。

92.s340,如图7c所示,在第一开孔61位置的第一半导体层21上沉积和/或生长多量子阱层22。

93.同上述实施例,在此不再赘述。

94.s350,如图7c所示,在多量子阱层22上形成第二半导体层23。

95.同上述实施例,在此不再赘述。

96.s361,如图7d所示,去除第一绝缘层51。

97.本技术实施例中,可以通过湿法腐蚀法将材质为siox等的第一绝缘层51去除。使得第二半导体层23和多量子阱层22的侧壁、以及目标位置处的第一半导体层21裸露出来,以便于第一半导体层21形成台阶部211。

98.s362,如图7e所示,在多量子阱层22的侧面、以及目标位置处的第一半导体层21背离衬底层10的表面,形成第二绝缘层52。

99.本技术实施例中,继续通过气相沉积法制作一层第二绝缘层52,本技术实施例中第二绝缘层52的材质为siox,在其他实施例中,第二绝缘层52的材质也可以为其他材质。

100.本技术实施例中,通过制作第二绝缘层52覆盖多量子阱层22的侧面,使得第二绝缘层52能够保护多量子阱层22,防止第一绝缘层51与多量子阱层22的侧壁接触不紧密,避免外界环境对多量子阱层22的影响,确保微显示器件的发光效率。本技术实施例中,第二绝缘层52同时覆盖第二半导体层23背离衬底层10的表面或覆盖ito导电层24背离衬底层的表面,同时覆盖第二半导体层23的侧壁,以及覆盖目标位置处的第一半导体层21,即第二绝缘层52覆盖第一半导体层21和第二半导体层23背离衬底层10的表面、第二半导体层23和多量子阱层22的侧面。在其他实施例中,也可以通过采用图形化掩膜版遮挡,制作的第二绝缘层52未完全覆盖第二半导体层23背离衬底层10的表面或覆盖ito导电层24背离衬底层10的表面。

101.s363,如图7f所示,图案化刻蚀目标位置处的第二绝缘层52,形成第二开孔62,第

二开孔62正对第一半导体层21,且与多量子阱层22不接触。

102.本技术实施例中,本技术实施例中,通过对湿法或干法刻蚀目标位置处的第二绝缘层52,形成第二开孔62,本技术实施例中,第二开孔62设置于多量子阱层22的侧边的目标位置处,使得第二开孔62不会与多量子阱层22直接接触,从而避免对多量子阱层22的影响。

103.本技术实施例中,第二绝缘层52同时覆盖第二半导体层23背离衬底层10的表面,在图形化刻蚀第二绝缘层52时,可以同时图形化刻蚀形成第二开孔62和第三开孔63,即第二半导体层23表面上的第二绝缘层52上刻蚀,形成第三开孔63。

104.s364,如图7g所示,在第二开孔62中沉积和/或生长第一电极30,第一电极30与第一半导体层21电连接。

105.本技术实施例中,采用热蒸镀法在第二开孔62位置处蒸镀第一电极30,本技术实施例中,第一电极30的厚度可以为1.5微米,在其他实施例中,第一电极30的厚度也可以为其他数值。本技术实施例直接形成的第一电极30与第一半导体层21在第二开孔62位置处直接接触电连接。

106.在本技术实施例中,可以在s364之前或者s364之后,制作第二电极40,第二电极40与第二半导体层23电连接。本技术实施例中,第二电极40也通过热蒸镀法制作,在第三开孔63位置处蒸镀一层第二电极40,第二电极40直接形成于第二半导体层23上或形成于ito导电层24上,使得第二电极40与第二半导体层23电连接。

107.本技术实施例中,通过去除第一绝缘层51,直接形成第二绝缘层52,使得目标位置处的第一半导体层21形成台阶部211,便于制作第一电极30。在其他实施例中,也可以不去除第一绝缘层51,直接制作第二绝缘层52,使得第二绝缘层52可以进一步覆盖多量子阱层22的侧面,保护多量子阱层22,同时第二绝缘层52可以进一步覆盖目标位置处的第一绝缘层51。通过同时刻蚀目标位置处的第一绝缘层51和第二绝缘层52,即可以形成第二开孔62,以使得第一电极30与第一半导体层21电连接。

108.本技术的第四实施例中,如图8所示,一种微显示器件的制作方法,包括:

109.s410,如图9a所示,在衬底层10上制作一层第一半导体层21。

110.与实施例一和实施例二相同,在此不再赘述。

111.s420,如图9a所示,在第一半导体层21远离衬底层10一侧制作第一绝缘层51。

112.与上述实施例相同,在此不再赘述。

113.s430,如图9b所示,图案化刻蚀第一绝缘层51,形成第一开孔61。

114.采用图形化掩膜版遮挡,刻蚀第一绝缘层51,像素化开孔,形成第一开孔61,通过控制第一开孔61的大小,可以控制微显示器件的发光区域的大小。本技术实施例中,采用湿法刻蚀第一绝缘层51,采用固化图形化的光刻胶遮挡第一绝缘层51,固化图形化的光刻胶,并采用刻蚀液刻蚀第一绝缘层51,形成第一开孔61,去除光刻胶,即获得在第一绝缘层51上形成第一开孔61。在其他实施例中,也可采用干法刻蚀第一绝缘层51,通过采用图形化的光刻胶遮挡,采用离子束轰击制作第一开孔61,去除图形化的光刻胶。

115.本技术实施例中,第一开孔61的数量为至少两个,例如,本技术实施例中第一开孔61的数量为多个,且可以阵列设置。

116.s440,如图9c所示,在第一开孔61位置的第一半导体层21上沉积和/或生长多量子阱层22。

117.本技术实施例中,采用气相外延生长法在至少两个第一开孔61位置的第一半导体层21上生长一层多量子阱层22。本技术实施例中,多量子阱层22的数量为至少两个,且多量子阱层22与第一开孔61一一对应。即一个第一开孔61位置处的多量子阱层22为一个单元,即多量子阱层22单元的数量为至少两个。使得每个多量子阱层22填充与第一开孔61位置处。在其他实施例中,也可以采用其他方法制作多量子阱层22。

118.s450,如图9c所示,在多量子阱层22上形成第二半导体层23。

119.继续采用气相外延生长法在至少两个多量子阱层22上生长一层第二半导体层23,本技术实施例中,还可以在至少两个第二半导体层23上继续采用气相外延生长法生长一层电子束蒸发ito导电层24等,在其他实施例中,也可以不生长ito导电层24。本技术实施例中,至少两个多量子阱层22一次形成于第二半导体层23上方,可以减少制作步骤,提高微显示器件的制作效率。

120.s461,如图9d所示,制作第三绝缘层53,第三绝缘层53覆盖第二半导体层23、多量子阱层22和第一绝缘层51。

121.本技术实施例中,可以采用化学气相沉积法继续沉积第三绝缘层53。本技术实施例中,第三绝缘层53覆盖第二半导体层23、多量子阱层22和第一绝缘层51,本技术实施例中,第三绝缘层53的材质为siox,在其他实施例中,第三绝缘层53的材质也可以为其他材质。

122.s462,如图9e和图9f所示,刻蚀第三绝缘层53、第一绝缘层51以及第一半导体层21,形成沟槽65,沟槽65将相邻两个第一开孔61分离,且沟槽65侧壁与多量子阱层22不直接接触。

123.本技术实施例中,先采用湿法刻蚀或干法刻蚀,或同时采用湿法刻蚀和干法刻蚀,刻蚀第三绝缘层53和第一绝缘层51,在相邻两个第一开孔61位置处形成沟槽65。本技术实施例中,沟槽65的侧壁与多量子阱层22不直接接触,可以避免刻蚀过程对多量子阱层22造成损伤。

124.本技术实施例中,采用湿法刻蚀第三绝缘层53和第一绝缘层51,采用固化图形化的光刻胶遮挡第三绝缘层53和第一绝缘层51,固化图形化的光刻胶,并采用刻蚀液刻蚀第三绝缘层53和第一绝缘层51,去除光刻胶,即形成位于第三绝缘层53和第一绝缘层51上的沟槽65。在其他实施例中,也可采用干法刻蚀第三绝缘层53和第一绝缘层51,通过采用图形化的光刻胶遮挡,采用离子束轰击第三绝缘层53和第一绝缘层51,制作沟槽65,去除图形化的光刻胶。或者通过采用图形化的光刻胶遮挡,先采用离子束轰击第三绝缘层53,或第三绝缘层53和第一绝缘层51;再采用湿法刻蚀的所采用的刻蚀液刻蚀第一绝缘层51,或第三绝缘层53和第一绝缘层51,形成沟槽65。

125.本技术实施例中,再进一步采用电感偶合等离子体刻蚀(icp)法,在沟槽65位置处继续刻蚀第一半导体层21,使得第一半导体层21在沟槽65位置处断开。本技术实施例中,为了保证第一半导体在沟槽65位置处完全断开,可以进一步刻蚀部分缓冲层12。

126.本技术实施例中,第一半导体层21、多量子阱层22和第二半导体层23构成发光组件20,本技术实施例中,沟槽65将相邻两个发光组件20分离,使得相邻两个发光组件20互不影响。

127.s463,如图9g所示,去除第一绝缘层51和第三绝缘层53。

128.本技术实施例中,可以通过湿法腐蚀法将材质为siox等的第一绝缘层51和第三绝缘层53去除。使得第二半导体层23和多量子阱层22的侧壁、以及目标位置处的第一半导体层21裸露出来。并使得第二半导体层23和多量子阱层22与第一半导体层21形成台阶,使得第一半导体层21形成台阶部211。

129.s464,如图9h所示,在多量子阱层22的侧面、以及目标位置处的第一半导体层21背离衬底层10的表面,形成第二绝缘层52。

130.本技术实施例中,通过气相沉积法制作一层第二绝缘层52,本技术实施例中第二绝缘层52的材质为siox,在其他实施例中,第二绝缘层52的材质也可以为其他材质。

131.本技术实施例中,制作的第二绝缘层52覆盖多量子阱层22的侧面、以及目标位置处的第一半导体层21背离衬底层10的表面,第二绝缘层52能够保护多量子阱层22,避免外界环境对多量子阱层22的影响,确保微显示器件的发光效率。同时,第一半导体层21在目标位置处仍然能够形成台阶部211。本技术实施例中,第二绝缘层52同时覆盖第二半导体层23背离衬底层10的表面或覆盖ito导电层24背离衬底层10的表面,同时覆盖第二半导体层23的侧壁,以及覆盖目标位置处的第一半导体层21。在其他实施例中,也可以通过采用图形化掩膜版遮挡,制作的第二绝缘层52未完全覆盖第二半导体层23背离衬底层10的表面或覆盖ito导电层24背离衬底层10的表面。

132.本技术实施例中,制作的第二绝缘层52可以一次制作,覆盖于至少两个发光组件20。

133.s465,如图9i所示,图案化刻蚀目标位置处的第二绝缘层52,形成第二开孔62,第二开孔62正对第一半导体层21,且不与多量子阱层22接触。

134.本技术实施例中,采用湿法刻蚀工艺刻蚀第二绝缘层52,在目标位置处刻蚀出第二开孔62,并在第二半导体层23上的第二绝缘层52上同时刻蚀出第三开孔63。在其他实施例中,当第二绝缘层52未完全覆盖第二半导体层23背离衬底层10的表面时,可以不需要刻蚀出第三开孔63,仅刻蚀出第二开孔62即可。

135.本技术实施例中,第二开孔62靠近于多量子阱层22,即,每个发光组件20对应至少一个第二开孔62。

136.s466,如图2所示,在第二开孔62中沉积和/或生长第一电极30,第一电极30与第一半导体层21电连接。

137.本技术实施例可以同时在至少两个发光组件20上同时沉积和/或生长第一电极30,或同时沉积和/或生长第二电极40,本技术实施例的制作步骤与s364相同,在此不再赘述。

138.本技术实施例制作出的微显示器件可以包括至少两个微显示器件,且相邻两个微显示器件相互不影响。本技术实施例中,制作的微显示器件多量子阱层22通过直接沉积制作而成,不会对多量子阱层22的侧壁造成损伤,可以提高微显示器件的发光效率。本技术实施例制作的微显示器件不需要刻蚀第二半导体层23以使得第一半导体层21形成台阶部211,可以减少缩短微显示器件的工艺制作流程,简化制程,确保微显示器件的外观形貌的完整性。本技术实施例的微显示器件的制作方法,通过设置第二绝缘层52,可以保护多量子阱层22的侧壁,确保外界环境不会对多量子阱层22造成损伤。

139.以上仅为本技术的实施方式,并非因此限制本技术的专利范围,凡是利用本技术

说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1