半导体装置及其制造方法与流程

1.本发明涉及一种半导体装置及其制造方法,且特别是涉及一种栅极全环式半导体装置。

背景技术:

2.近来,人们对于微型化半导体装置的需求日益增加。栅极全环式(gate-all-around,gaa)半导体纳米线场效晶体管(field effect transistor,fet)与传统场效晶体管相比具有尺寸更小、电特性更好的优势,因此栅极全环式半导体纳米线场效晶体管的发展越来越重要。

技术实现要素:

3.本发明是有关于一种半导体装置及其制造方法,可通过简化的制作工艺形成电特性优良的纳米线。

4.根据本发明的一实施例,提出一种半导体装置。半导体装置,包括基板及多个纳米线。基板具有一上表面。纳米线沿着第一方向堆叠于基板的上表面上。其中纳米线在一横截面中包括一三角形,纳米线包括沿着一第二方向延伸的一平面、在一(111)晶面上的一第一下斜刻面以及在另一(111)晶面上的一第二下斜刻面。

5.根据本发明的另一实施例,提出一种半导体装置的制造方法。方法包括下列步骤。首先,提供一基板。接着,沿着第一方向在基板上依序形成堆叠及硬掩模层,其中堆叠包括交替堆叠的多个蚀刻停止层和多个半导体层。移除部分的基板、堆叠及硬掩模层以形成多个鳍状结构,其中每个鳍状结构包括一基板部分、多个蚀刻停止部分、多个半导体部分和一硬掩模部分。此后,通过一湿蚀刻制作工艺图案化基板部分与半导体部分,以形成多个纳米线,其中纳米线沿着第一方向堆叠于基板的上表面上,并沿着第二方向延伸,在横截面中包括一三角形。

6.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

7.图1~图5为本发明一实施例的半导体装置的制造方法的流程图。

具体实施方式

8.本案提供一种半导体装置及其制造方法,可以解决现有制造过程繁复而衍生的成本高及耗费时间长的问题。为了对本发明的目的、特征和优点能更明显易懂,下文特举一实施例,并配合所附的附图作详细说明。

9.但必须注意的是,此特定的实施例与方法,并非用以限定本发明。本发明仍可采用其他特征、元件、方法及参数来加以实施。优选实施例的提出,仅用以例示本发明的技术特

征,并非用以限定本发明的申请专利范围。该技术领域中具有通常知识者,将可根据以下说明书的描述,在不脱离本发明的精神范围内,作均等的修饰与变化。

10.图1~图5绘示依照本发明一实施例的半导体装置10的制造方法的流程图。

11.首先,请参照图1,可提供一基板100。基板100可具有一第一表面100s。在本实施例中,基板100可包括单晶半导体材料,例如是单晶硅。

12.接着,沿着第一方向(例如是z方向)在基板100上依序形成一堆叠110及一硬掩模层120,其中堆叠110包括交替堆叠的多个蚀刻停止层102与106和多个半导体层104与108,如图2所示。堆叠110例如是沿着第二方向(例如是x方向)及第三方向(例如是y方向)连续性地延伸于基板100的第一表面100s上。第一方向、第二方向及第三方向可彼此交错。在本实施例中,第一方向、第二方向及第三方向可互相垂直,然本发明并不以此为限。

13.根据一实施例,蚀刻停止层102与106的材料可包括氧化物,硬掩模层120的材料可包括氮化物,然而本发明并不以此为限。在一实施例中,半导体层104与108可包括单晶半导体材料,例如是单晶硅。

14.根据一实施例,在基板100上形成堆叠110的方法可类似于形成绝缘层上覆硅(silicon on insulator,soi)的晶片接合(bonding)方法,亦即是类似于接合及回蚀绝缘层上覆硅制作工艺(bond and etch-back soi process,besoi process)。

15.根据一实施例,硬掩模层120可通过沉积制作工艺所形成,沉积制作工艺例如是化学气相沉积(chemical vapor deposition,cvd)或等离子体辅助化学气相沉积(plasma-enhanced cvd,pecvd)。

16.此后,请参照图3,可沿着第一方向(z方向)移除部分的基板100、堆叠110及硬掩模层120以形成多个鳍状结构(fin structure)fs。其中,移除部分的基板100、堆叠110及硬掩模层120以形成多个鳍状结构fs的步骤例如是通过一干蚀刻制作工艺所进行。多个鳍状结构fs例如是分别沿着第一方向突出于剩余的基板100上,且分别沿着第二方向延伸于剩余的基板100上。亦即,多个鳍状结构fs可彼此平行延伸,并可在第三方向上互相分开。在本实施例中,每个鳍状结构fs可包括一基板部分100a、2个蚀刻停止部分102a与106a、2个半导体部分104a与108a及一硬掩模部分120a,然而本发明并不以此为限。在本实施例中,基板部分100a、蚀刻停止部分102a与106a、半导体部分104a与108a及硬掩模部分120a在第三方向上的宽度是类似或相同,然而本发明并不以此为限。

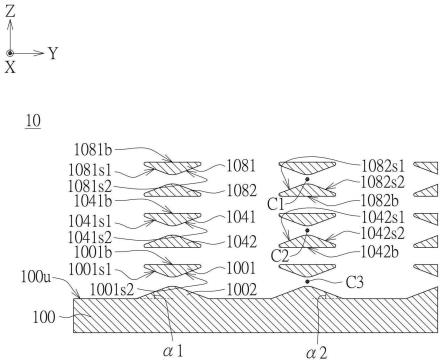

17.在形成鳍状结构fs之后,请参照图4,可通过一湿蚀刻制作工艺图案化基板部分100a及半导体部分104a与108a,以形成纳米线1081、1082、1041、1042及1001及基板突出部1002。

18.在一实施例中,湿蚀刻制作工艺中使用的蚀刻剂可包括四甲基氢氧化铵或其他合适的蚀刻剂。湿蚀刻制作工艺例如是选择性地蚀刻硅,蚀刻剂对于硅的(111)晶面具有较快的蚀刻速率,且需蚀刻至纳米线1081、1082、1041、1042及1001之间可完全断开,且纳米线1001与基板突出部1002之间也完全断开。因此,通过湿蚀刻制作工艺所形成的纳米线1081、1082、1041、1042及1001在横截面(例如是由第一方向及第二方向所形成的横截面)中包括一三角形。具有三角形横截面的纳米线1081、1082、1041、1042及1001分别包括沿着第二方向延伸的一平面1081b、1082b、1041b、1042b及1001b、在一(111)晶面上的一第一下斜刻面1081s1、1082s1、1041s1、1042s1及1001s1以及在另一(111)晶面上的一第二下斜刻面

1081s2、1082s2、1041s2、1042s2及1001s2。纳米线1081、1082、1041、1042及1001及基板突出部1002沿着第一方向堆叠于基板100的上表面100u及基板突出部1002上,并沿着第二方向延伸。基板突出部1002在横截面中也为三角形,且与基板100的上表面100u彼此连接,事实上基板突出部1002与基板100为一体成形的结构。

19.如图4所示,在通过湿蚀刻制作工艺图案化基板部分100a与半导体部分104a及108a的上述步骤中,没有间隔物形成在基板部分104a与半导体部分108a的旁边。在一些形成纳米线的传统方法中,需要形成间隔物于基板部分与半导体部分的旁边,以保护基板部分与半导体部分受到后续制作工艺(例如蚀刻制作工艺)的损坏,且所形成的纳米线在横截面中通常为矩形。相较于制作工艺期间需要形成间隔物保护基板部分与半导体部分的比较例而言,根据本案的一实施例的纳米线的形成方法并不需要形成间隔物,直接通过湿蚀刻制作工艺即可形成三角形的纳米线,故能够省略多道制作工艺,不论是在制作工艺成本或时间方面都有大幅的改善。

20.此后,请参照图5,可通过不同的蚀刻制作工艺移除蚀刻停止部分102a与106a以及硬掩模部分120a,保留纳米线1081、1082、1041、1042及1001以及基板突出部1002,以形成半导体装置10。在一实施例中,蚀刻停止部分102a与106a可通过包括氢氟酸(hf)的蚀刻剂所移除,硬掩模部分120a可通过包括磷酸(h3po4)的蚀刻剂所移除,然而本发明并不限于此。

21.在一些实施例中,可进一步通过退火制作工艺(anneal process)将纳米线1081、1082、1041、1042及1001的尖角形成圆角,亦即是在横截面中,纳米线1081、1082、1041、1042及1001可包括圆角三角形,如此一来,可让纳米线1081、1082、1041、1042及1001具有更佳的电特性,例如是避免漏电。此后,可进行后续制作工艺,形成环绕纳米线1081、1082、1041、1042及1001的栅极介电材料层(未绘示)之后,在栅极介电材料层(未绘示)之间填入导电材料,以形成环绕纳米线1081、1082、1041、1042及1001及栅极介电材料层(未绘示)的导电栅极(未绘示)。换言之,半导体装置10可应用于栅极全环式半导体纳米线场效晶体管。

22.如图5所示,半导体装置10可包括一基板100以及多个纳米线1081、1082、1041、1042及1001。基板100具有一上表面100u。纳米线1081、1082、1041、1042及1001沿着一第一方向(例如z方向)堆叠于基板100的上表面100u上。纳米线1081、1082、1041、1042及1001在一横截面中包括一三角形。其中,沿着第一方向堆叠之纳米线1081、1082、1041、1042及1001中的最顶部纳米线1091及最底部纳米线1001在横截面中为倒三角形。纳米线1081、1082、1041、1042及1001包括沿着一第二方向(例如x方向)延伸的平面1081b、1082b、1041b、1042b及1001b、在一(111)晶面上的一第一下斜刻面1081s1、1082s1、1041s1、1042s1及1001s1以及在另一(111)晶面上的一第二下斜刻面1081s2、1082s2、1041s2、1042s2及1001s2。在本实施例中,平面1081b、1082b、1041b、1042b及1001b可平行于基板100的上表面100u,然而本发明并不限于此。

23.在本实施例中,沿着第一方向堆叠的纳米线1081、1082、1041、1042及1001的数量为5个,然而本发明并不限于此,纳米线的数量可以是任意的奇数。在一实施例中,当半导体层的数量为n(如图2所示,半导体层104及108的数量为2),纳米线的数量为2n+1(如图5所示,纳米线1081、1082、1041、1042及1001的数量为2

×

2+1=5),n为正整数。由于本发明是通过湿蚀刻将n个半导体层或半导体部分分别分隔为上及下2个三角形,以形成2n+1个纳米线,故相较于没有将半导体层或半导体部分分别分隔为上及下2个三角形的比较例而言,本

发明的半导体装置可包括较多数量的纳米线,并使得纳米线1081、1082、1041、1042及1001与栅极(未绘示)之间可具有较大的接触面积,故可提升导通效果,使得半导体装置10具备更优良的电特性。

24.在一实施例中,平面1081b、1082b、1041b、1042b及1001b与第一下斜刻面1081s1、1082s1、1041s1、1042s1及1001s1之间的夹角α1的范围可介于54.5度至55度,例如是54.7度;平面1081b、1082b、1041b、1042b及1001b与第二下斜刻面1081s2、1082s2、1041s2、1042s2及1001s2之间的夹角α2的范围可介于54.5度至55度,例如是54.7度。基板100及纳米线1081、1082、1041、1042及1001可包括单晶半导体材料,例如是单晶硅。

25.根据一实施例,纳米线1081、1082、1041、1042及1001中的至少2个纳米线可沿着第二方向互相对称。例如,纳米线1081与1082之间可具有一中心点c1,纳米线1041与1042之间可具有一中心点c2,纳米线1001与基板突出部1002之间可具有一中心点c3。纳米线1081可以穿过中心点c1且沿着第二方向延伸的对称轴镜像对称于纳米线1082。纳米线1041可以穿过中心点c2且沿着第二方向延伸的对称轴镜像对称于纳米线1042。纳米线1001可以穿过中心点c3且沿着第二方向延伸的对称轴镜像对称于基板突出部1002。

26.根据上述实施例,本发明提供一半导体装置及其制造方法。相较于现有需要形成间隔物在基板部分与半导体部分的旁边的比较例而言,由于本发明的半导体装置的制造方法中,可通过一湿蚀刻制作工艺图案化基板部分与半导体部分,以形成横截面包括三角形的多个纳米线,并不需要形成间隔物在基板部分与半导体部分的旁边,故可简化原本繁复制作工艺,使得制作工艺成本或时间都获得大幅改善。此外,相较于当半导体层的数量为n时,纳米线的数量为n(n为正整数)的比较例而言,本发明的半导体装置中,当半导体层的数量为n时,纳米线的数量可为2n+1(n为正整数),即纳米线的形成数量可较多,可形成纳米线更紧密堆叠的半导体装置,且纳米线与栅极之间可具有较大的接触面积,故可提升导通效果,使得半导体装置具备更优良的电特性。

27.综上所述,虽然结合以上实施例公开了本发明,然而其并非用以限定本发明。本发明所属技术领域中的技术人员,在不脱离本发明的精神和范围内,可作各种的更动与润饰。因此,本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1