一种干法制备单层二维半导体阵列的方法

1.本发明涉及材料技术领域,尤其是干法制备大面积单层二维半导体阵列及异质结阵列方法领域。

背景技术:

2.近年来,二维(2d)材料以其优异的电学、光学和力学性能引起了人们的广泛关注。然而实现大规模化生产高质量的单层薄膜仍是二维材料领域的关键挑战。现有获得二维材料单分子层的方法往往受到材料质量和材料尺寸权衡的限制。例如:液相剥离是最大规模化的方法,通过简单的旋转涂覆方法就可以生产大量2d薄膜,然而液相剥离的过程基于溶液浸泡,这容易导致获得的薄片厚度随机不可控,并且溶液会污染和损害二维材料表面,而导致薄膜质量变差。另一方面,化学气相沉积法可以合成具有生长条件可控和均匀层厚的大面积材料,但获得的材料往往以高缺陷密度和存在预应变的多晶形式存在。相比之下,机械剥离法(也称为scotch胶带法)可以获得最高质量的单层半导体薄膜,这也大大加快了二维材料研究的进展,因此被广泛用于二维材料的研究中。然而,传统的机械剥离法获得二维材料的尺寸一般在几微米左右,且产量很低,受限于无法获得大尺寸的二维材料单分子层。

3.为了提高机械剥离法二维材料单分子层的尺寸和产量,人们致力于对剥离胶带进行升级。一种是以降低胶带表面粗糙度,从而提高胶带与二维材料的接触;另一种是提高胶带的附着力,从而尝试提高产量。早期的尝试是直接将金膜蒸发到大块mos2晶体的表面作为胶带,以进行后续的胶带剥离。在胶带剥离过程中,蒸发的金和最上层的mos2层之间的强相互作用力确保了横向尺寸高达0.5mm的大面积单层的均匀剥离。然而,金直接沉积在二维材料表面已被证明会引入缺陷和应变,降低精细二维材料晶格的固有性能,特别是对单层而言尤为严重。现有技术中还有通过将二维块状晶体压印在预先沉积的金薄膜表面来提高材料产量。金膜的预制可以避免直接金属沉积对材料表面造成的损伤,原子级平整的金表面可以与二维材料块体表面形成密切接触,从而可以获得横向尺寸高达1cm的大尺寸剥离,大大提高了二维材料单层膜的产量。虽然该方法具有优化的剥离材料尺寸和材料质量,但受二维单层材料与金之间的强作用力的限制,导致剥离获得的材料不能机械地释放,不能直接用于随后的电学测量或各种范德华异质结构(vdwhs)的构建。如果需要进行后续电学测量或转移,必须经过溶液蚀刻法(通常是ki/i2溶液)来化学去除au膜,这不仅会对材料产生不可避免的污染,而且与使用胶带剥离获得干净材料的初衷相矛盾。

技术实现要素:

4.本发明所要解决的技术问题是,克服现有技术存在的上述缺陷,提供一种干法制备大面积单层二维半导体阵列及范德华异质结阵列的方法。

5.本发明所采用的技术方案如下:一种干法制备单层二维半导体阵列的方法,包括:

6.(1)预制金网格胶带:在基底上制备图案化的金网格薄膜,在金网格薄膜表面旋涂聚合物并烘干,聚合物作为支撑层,将金网格薄膜从基底上剥离,制备金网格胶带;

7.(2)制备连续单层二维半导体薄膜:将预制的金网格胶带按压到块状二维半导体材料表面,剥离金网格胶带,获得连续单层二维半导体薄膜;

8.(3)制备单层二维半导体阵列:将带有连续二维单层半导体薄膜的金网格胶带对准目标基底,按压接触,剥离金网格胶带,在目标基底上释放单层二维半导体阵列。

9.优选地,步骤(1)中,通过光刻掩膜和金属镀膜技术在基底上制备图案化的金网格薄膜,蒸镀金的厚度为30

‑

150nm,蒸镀速率为0.04

‑

0.06nm/s。

10.优选地,步骤(1)中,金网格表面旋涂的聚合物采用具有高玻璃化温度的聚合物,从而能够形成支撑层,例如:聚碳酸酯(简称pc)等。聚合物作为支撑层将蒸镀的金网格从基底表面剥离,以获得具有原子级平整表面的金网格胶带。

11.优选地,步骤(1)中,所述聚合物质量比浓度为5%,溶质为聚碳酸酯,溶剂为氯仿。

12.优选地,步骤(1)中,所述聚合物旋涂速度为2000

‑

5000rpm,旋涂时间为1

‑

2分钟,之后100

‑

150℃烘烤1

‑

3分钟。

13.优选的,步骤(2)中,所述二维半导体块材为层状二维半导体块材,包括但不仅限于过渡金属硫属化合物;所述过渡金属硫属化合物包括但不仅限于mos2、wse2、mose2、ws2。

14.优选的,步骤(2)中,在按压的同时进行加热处理,以促进金网格胶带与块状二维半导体表面接触,从而可以获得大面积的具有原子级平整表面的单层二维半导体薄膜。例如加热温度为70

‑

150℃,加热时间1

‑

5分钟。

15.优选的,步骤(3)中所述对准是通过光学转移平台实现,所述按压接触是通过转移平台机械臂施加恒定压力让金网格胶带表面的连续单层二维半导体薄膜与目标基底接触。

16.优选的,步骤(3)中所述目标基底是指功能化处理的基底,在表面旋涂薄层聚乙烯醇(pva)或交联的聚乙烯醇(c

‑

pva)形成粘结层,以增加基底的粘性。

17.由于单层二维半导体薄膜与目标基底的作用力大于其与支撑层的作用力,小于其与金的作用力,即与单层二维半导体薄膜材料间的作用力大小:金>目标基底>支撑层,从而使得剥离金网格胶带之后,由于金表面材料被带走,网格孔(支撑层)材料留在目标基底表面,形成单层二维半导体阵列。

18.优选的,步骤(3)中在按压的同时进行加热处理,以促进目标基底与二维单层半导体薄膜接触,从而使其更易向目标基底释放,这样可以更容易的分离二维单层半导体薄膜,从而提高了产率。例如所述加热温度为90

‑

130℃,加热时间1

‑

5分钟。

19.一种制备范德华异质结阵列的方法,第一层二维半导体阵列采用上述制备方法释放到pva(聚乙烯醇)基底表面,第二层二维半导体阵列采用上述制备方法释放到交联pva(c

‑

pva,不溶于水)功能化的基底表面,然后通过光学转移平台将两层阵列对准堆叠;之后通过去离子水浸泡去掉pva层,经过高温真空退火处理获得二维半导体范德华异质结阵列。

20.优选的,所述高温真空退火,温度为300

‑

400℃,时间3

‑

10小时。

21.本发明的有益效果如下:

22.(1)本发明步骤(2)中剥离金网格胶带的过程中与金接触区域的二维半导体材料由于与金网格紧密结合被带走,而网格孔洞上的材料因为与聚合物pc表面作用力较弱,会被释放在目标基底表面,最终成功地获得大面积单层二维半导体阵列。

23.(2)本发明可以直接在绝缘基底表面获得大面积单层二维半导体材料,不需要传统方法过程中的溶液(ki/i2)刻蚀二维半导体材料表面的金膜,再转移材料到绝缘基底。本

发明不仅操作流程简化,同时整个过程无任何溶液参与,保证了获得材料表面的洁净度和本征性质不受影响。

24.(3)本发明在绝缘基底表面直接获得单层二维半导体阵列,方便于后续的场效应管阵列器件制备和范德华异质结阵列堆叠,相比较于传统方法获得大面积材料之后再经过图案刻蚀获得阵列单独材料,具有更简洁的流程,同时避免了图形刻蚀过程二次污染物的引入。

25.(4)本发明所述干法剥离获得材料的过程无任何溶液参与,得到本征高质量的单层二维半导体薄膜;本征高质量在光学性能方面体现在单层mos2的光致发光强度与胶带直接剥离材料相近,且明显高于溶液刻蚀样品;本征高质量在电学性能方面体现在单层mos2的场效应晶体管的载流子迁移率达到63cm2/vs,开关比108,驱动电流280μa/μm,超过溶液刻蚀样品的性能两倍。

26.(5)本发明所述干法剥离获得单层材料阵列可以进一步范德华堆叠,首次制备得到了具有高质量界面的范德华异质结阵列。界面高质量体现在界面无气泡,且双层异质结的光致发光能谱存在明显层间激子。

附图说明

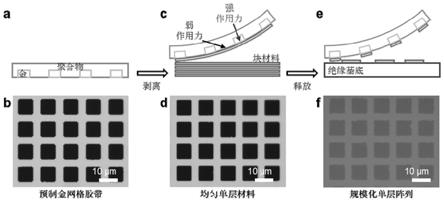

27.图1为本发明实施例1大面积单层mos2阵列材料制备的流程图和相应的光学显微镜图;

28.图2本发明实施例1通过设计不同形状的金网格胶带,从而干法剥离出各种形状的单层mos2阵列

29.图3为本发明实施例1旋涂在sio2基底表面的超薄pva层厚度测试结果图;

30.图4为本发明实施例1所得宏观尺度下金网格胶带表面的大面积完整材料和sio2基底表面的大面积mos2阵列材料;

31.图5为本发明实施例1所得单层材料(附图5a和附图5b)与ki/i2溶液刻蚀样品(附图5c和附图5d)的原子力显微镜和光致发光能谱测试结果;

32.图6为由本发明实施例1所得的单层材料制备的背栅场效应晶体管阵列及电学测试结果。

33.图7为本发明实施案例1获得的多种单层材料阵列图和对应的pl、raman图。

34.图8为本发明实施例2异质结制备的示意图和相应的光学显微镜图、afm图、pl和raman图。

具体实施方式

35.下面结合实施例和附图对本发明作进一步说明。

36.实施案例1

37.本实施案例具体制备工艺包括以下步骤:在sio2基底表面光刻掩膜然后蒸镀50nm厚的au获得金网格。将5%浓度的pc溶液以3000rpm的速度旋涂1分钟到金网格上,然后150℃烘烤1分钟,获得金网格胶带。

38.将金网格胶带按压到mos2块材料表面,加热130℃,3分钟促进接触,然后剥离胶带获得大面积完整单层mos2。

39.将带有大面积连续单层mos2的金网格胶带对准旋涂了薄层pva的sio2基底,pva用于增加基底粘性,按压接触,然后100℃加热3分钟促进材料与基底表面充分接触,最后剥离金网格胶带,由于金表面材料被带走,网格孔中材料留在基底表面,所以获得了大面积单层mos2阵列。

40.从附图1可以看出首先在金网格胶带表面获得了大面积完整材料,然后通过干法转移,网格孔表面的材料可以释放到目标基底表面,从而获得了大面积的均匀单层材料阵列。

41.附图2展示了可以设计各种不同形状的金网格胶带,从而干法剥离和释放出各种形状的单层mos2阵列,如图2中a、b、c、d、e所示,其分别为六边形、三角形、正方形、字母图形、条形。

42.从附图3可以看出旋涂在sio2基底表面的超薄pva层的厚度仅为18nm,它用来提升基底表面粘附力,但不影响该基底主要性质和应用。

43.附图4为本发明实施例1所得宏观尺度下金网格胶带表面的大面积完整材料和sio2基底表面的大面积阵列材料。

44.附图5可以看出本发明实施例1所获得的材料表面粗糙度仅为0.395nm,远低于传统ki/i2溶液刻蚀金之后获得的单层材料表面粗糙度2.54nm。我们的干法转移材料由于制备过程未有溶液的参与,无化学试剂及污染残留,保留了材料本征原子级平整表面。

45.此外,干法转移样品的光致发光强度与直接胶带剥离样品接近,明显高于刻蚀样品,充分说明了我们干法转移样品保证了材料本征性质。

46.附图6可以看出,在同样的栅介质表面,本实施例1干法转移的单层mos2样品相比于ki/i2溶液刻蚀样品展示出了更优良的电学性能,载流子迁移率达到63cm2/v s,开关比108,驱动电流280μa/μm。

47.附图7可以看出,本发明的制备方法同样可以适用于获得大面积单层wse2,mose2,ws2阵列,pl和raman光谱证明了他们是单层材料。

48.实施案例2

49.本实施案例具体制备工艺包括以下步骤:在sio2基底表面光刻掩膜然后蒸镀70nm厚的au获得金网格。将5%浓度的pc溶液以2000rpm的速度旋涂2分钟到金网格上,然后100℃烘烤3分钟,获得金网格胶带。

50.将金网格胶带依次按压到wse2,mos2块材料表面,加热130℃,3分钟促进接触,然后剥离胶带获得大面积均匀单层wse2,mos2。

51.在pva基底表面干法转移大面积单层wse2阵列。同时,在交联pva(c

‑

pva,不溶于水)/sio2基底表面干法转移大面积单层mos2阵列。

52.在光学显微镜下将两层材料对准,然后堆叠在一起。将叠好的异质结放到去离子水中浸泡,除去最顶层的pva层,从而获得大面积范德华双层异质结阵列,后续350℃真空退火6小时处理,除去表面杂质及残留物。

53.由附图8以看到本实案施例制备的异质结阵列并不受上下层层材料尺寸限制,我们可以依次制备出上层wse2大于、小于、等于下层mos2尺寸的异质结;afm测试结果显示异质结的界面没有气泡和杂质,pl光谱结果显示在1.57ev出现了明显的层间激子峰,两者充分说明异质结界面足够干净,达到强耦合效果;双层异质结经过退火后,材料上表面同样足够

干净(rms=0.415nm),同样适合后续逐层堆叠制备多层异质结阵列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1