一种p型氮化镓基器件的电极及其制备方法和用途与流程

1.本发明属于半导体器件的技术领域,涉及一种p型氮化镓基器件的电极及其制备方法和用途。

背景技术:

2.宽禁带(wbg)半导体(例如碳化硅sic和氮化镓gan),被认为是下一代电力电子设备中最具潜力的材料。它们凭借超凡的物理特性,如禁带宽度>3ev,高临界电场(2

‑

4mv/cm)和低的固有载流子浓度(

‑

〖10〗^(

‑

10)〖cm〗^(

‑

3)),可用于制造比硅材料更能在高压,高温和高频下工作的器件。gan材料作为宽禁带半导体材料的主流材料,它的一个特殊方面是可以生长algan/gan异质结构,通过压电极化梯度在界面处生成二维电子气(2deg),2deg的存在使得基于gan的高电子迁移率晶体管(hemt)相对于si和sic器件,具有更低的沟道电阻。hemt因其高的电子迁移率、饱和速度、异质结界面处的高载流子浓度、高击穿场和低热阻等诸多优点,而在高功率及高温应用中引起了广泛关注。随着高集成化的发展,gan hemt因具有更低的沟道电阻,所以被用来做coms晶体管的沟道材料,有效提高了高功率栅极驱动电路的效率。

3.但是,p

‑

type gan晶体管的性能仍然明显低于n

‑

type gan器件的性能,这极大的削弱了cmos电路的pull

‑

up network。造成p

‑

type gan晶体管性能差的一个重要因素是p

‑

type gan器件的源极/漏极的欧姆接触质量差,这是由于p

‑

type掺杂剂的活化能大,而造成电离受体的密度低引起的。欧姆接触是gan晶体管的基石,是将器件与外部电路连通的桥梁,用于电信号的传输,人们对欧姆接触电阻的期待是越小越好。欧姆电阻越小,损耗就越小,器件效率就高。欧姆接触与金属/半导体肖特基势垒高度φ_b有关,φ_b与金属的功函数φ_m相关,可以通过选择合适的φ_m值的金属材料来降低欧姆电阻。因此为p

‑

type gan寻找有效的接触金属方案是一个巨大的挑战。

4.人们在为p

‑

type gan选择合适的金属材料方案方面做了大量的研究,目前存在的欧姆金属组合方案有cr/au、pt/au、pd/au、pt/ni/au、pd/ni/au、ni/au、ta/ti、pt/ni/au、ni/pd/au、ti/pt/au、ni/ito、ru、ir、ru/ni、ir/ni、au/ni/au、ni/alzno、ni/ag、pd/ni/au、ag、ni/au/tan/ti/au、ni/au/tin/ti/au、ni/au/zrn/ti/au、ni/ag/ni、ni/ag/au或pd/pt/au。ρ

c

(比接触电阻,用来描述欧姆接触阻值)范围在〖10〗^(

‑

1)~〖10〗^(

‑

5)ω〖cm〗^2,比n

‑

type gan的值高约1

‑

2个数量级,现有的金属材料方案还是无法满足发展需求,因此在为p

‑

type gan形成稳定可靠且欧姆阻值小的金属材料方案方面,还有很大的前进空间。

5.cn111599865a公开了一种gan基p沟道mosfet及其制备方法,属于电子材料技术领域。本发明利用氟正离子注入氮化镓(gan)后形成的二维空穴气(2dhg)能够在gan表面层以下形成导电沟道的原理,将氟离子注入gan制备出了一种gan基p沟道mosfet。该文献中采用离子注入的方法对源漏极电极区进行n型注入掺杂,增加接触层的掺杂浓度,提高了隧穿几率,从而减小欧姆接触电阻,但这种工艺较为复杂,成本较高,注入的离子需要1000摄氏度以上温度才能激活,这种高温可能会影响材料其他性能。

6.cn104409344a公开了一种降低ni/au与p

‑

gan欧姆接触的比接触电阻率的方法,包括如下步骤:步骤1:在p

‑

gan层上生长重掺杂的p

‑

gan薄层;步骤2:对p

‑

gan层和p

‑

gan薄层进行mg激活退火;步骤3:在p

‑

gan薄层上生长重掺杂的p

‑

ingan薄层;步骤4:对p

‑

ingan薄层进行mg激活退火,形成样品;步骤5:将样品表面进行处理,在样品表面光刻,形成图形;步骤6:在样品的表面通过电子束蒸发来蒸发ni/au金属层;步骤7:将多余的ni/au金属层剥离;步骤8:退火形成ni/au合金,形成欧姆接触,完成制备。该文献中ni/au组合存在一些缺陷,主要体现在au的向内扩散,ni向外扩散和au向内扩散形成的au

‑

ni固溶体以及ni向外扩散在金属表面形成nio。使得氮化镓的欧姆接触电阻变高。

7.如何降低p型氮化镓基器件中金属半导体接触面的肖特基势垒高度,阻止金属层被氧化,降低p型氮化镓基器件的欧姆接触电阻,是亟待解决的技术问题。

技术实现要素:

8.本发明的目的在于提供一种p型氮化镓基器件的电极及其制备方法和用途。本发明所提供的p型氮化镓基器件的电极,用于p型氮化镓基器件的源极和漏极,解决了电极中金属层的氧化问题,还降低了器件中金属/半导体接触面的肖特基势垒高度,同时通过超高真空热处理,解决了ga2o3污染层导致的肖特基势垒高度升高问题,降低了器件源漏极欧姆接触电阻,提高了p型氮化镓基晶体管的性能,使得p型氮化镓基器件能够在cmos电路发挥更大的作用,从劣势变为优势。

9.为达到此发明目的,本发明采用以下技术方案:

10.第一方面,本发明提供一种p型氮化镓基器件的电极,所述电极包括依次层叠设置的氧化镍层、铂层和金层,其中,所述氧化镍层为p型结构,所述铂层位于所述氧化镍层和金层的中间,所述氧化镍层为p型氮化镓基器件的欧姆接触层。

11.本发明所提供的电极中,金层作为电极的保护层,利用au的稳定性,阻止了金属层被氧化,铂层作为电极的中间阻挡层,阻止了au和nio的扩散,用p型结构的nio来取代ni金属,nio属于半导体,它的功函数对比ni更接近p

‑

gan,与p

‑

gan因此nio/p

‑

gan之间形成的肖特基势垒高度要低于ni/p

‑

gan,从而降低了金属半导体接触面的肖特基势垒高度,改善了p型氮化镓基器件中电极(源极和漏极)欧姆接触电阻高的问题。

12.现阶段中,ni/au组合能形成稳定且阻值较小的欧姆接触,在ni与p型氮化镓基器件的接触界面处形成了薄的p型半导体nio层,nio层使得肖特基势垒高度φ_b(0.19ev)降低,从而能够得到较小的ρ

c

。nio层的来源分为两部分,第一部分是,在源漏极金属沉积后,把器件放进n2/o2环境氛围里进行高温退火,在退火过程中生成nio层。第二部分是,金属ni和p

‑

type gan表面的ga2o3发生反应,把ga2o3中的氧元素夺过来形成nio。mocvd技术生长p

‑

type gan外延片后或对外延片进行化学清洗后,外延片暴露在空气中会在表面形成大约2nm厚的ga2o3层。ga2o3吸收周围环境的c、o元素从而形成一层污染层,将接触面的肖特基势垒高度提高了0.2~0.3ev,从而提高了ρ

c

。金属ni和p

‑

type gan表面的ga2o3发生反应,就能将表面的污染层去除,消除了污染层在载流子传输通过界面的过程中起到的阻挡作用,并且生成了nio,降低了肖特基势垒,而本发明中,直接将原有的镍层用p型氧化镍层代替,进一步降低了肖特基势垒,同时加入铂层这一中间阻挡层,又阻挡了au和nio的进一步扩散,进一步的降低了器件的欧姆接触电阻,从而提高了源漏极金属电极的导电性,用来做coms

晶体管的沟道材料,有效提高了高功率栅极驱动电路的效率。

13.优选地,所述电极的厚度为60~200nm,例如60nm、70nm、80n、90nm、100nm、110nm、120nm、130nm、140nm、150nm、160nm或170nm、180nm、190nm或200nm等。

14.本发明中,电极的厚度不能过厚,过厚会导致非源漏极区域的金属在剥离过程中不能完全脱落,同时也不能过薄,过薄会导致造成电极的热稳定性差。

15.优选地,所述铂层的厚度大于或等于氧化镍层的厚度且小于金层的厚度。

16.优选地,所述氧化镍层的厚度为5~50nm,例如5nm、8nm、10nm、13nm、15nm、18nm、25nm、30nm、40nm或50nm等。

17.优选地,所述铂层的厚度为5~50nm,例如5nm、8nm、10nm、13nm、15nm、18nm、25nm、30nm、40nm或50nm等等。

18.优选地,所述金层的厚度为50~100nm,例如50nm、55nm、60nm、65nm、70nm、75nm、80nm、85nm、90nm、95nm或100nm等。

19.本发明中,氧化镍层、铂层和金层的厚度均不能过薄或者过厚,无论是哪一层的厚度过大或过小,都会对电极造成影响。氧化镍层厚度过小,会导致肖特基势垒高度无明显下降,pt厚度过小会导致起不到阻碍,ni/au相互扩散,au厚度过小会导致氧气扩散进去电极层,从而起不到防止氧化的作用,若每层金属过厚,会导致电极制备过程中,金属剥离不完全。

20.第二方面,本发明提供一种如第一方面所述的p型氮化镓基器件的电极的制备方法,所述制备方法包括以下步骤:

21.(1)在p型氮化镓外延结构上进行区域化处理,露出p型氮化镓基器件的电极区域;

22.(2)将步骤(1)经过处理的p型氮化镓外延结构进行真空热处理,然后在步骤(1)所述p型氮化镓基器件的电极区域上依次沉积氧化镍层、铂层和金层,再进行金属剥离,得到所述的p型氮化镓基器件的电极;

23.其中,所沉积的氧化镍层为p型结构。

24.本发明中,p型氮化镓外延结构包括沿着外延结构生长的p型氮化镓,均为外延结构的一部分,且真空热处理和金属沉积在同一腔体进行,保证金属热处理后,金属沉积之前样品p型氮化镓表面没有接触到氧气,未被再次氧化。

25.本发明所提供的制备方法,操作简单,在沉积金属层之前,进行了热处理操作,通过真空环境的高温预处理,将p型氮化镓表面的氧化钾层去除,消除了氧化钾带来的肖特基势垒高度升高的影响,这一步主要是在金属沉积前,对外延生长的p型氮化镓表面形状的2nm的氧化钾进行高温解离,如果解离不完全,这一次氧化钾会提高肖特基势垒高度,从而增大比接触电阻。因此热处理这一操作解吸了p型氮化镓基器件表面的ga2o3污染物,解决了ga2o3污染层导致的肖特基势垒高度升高问题,使得得到的电极的比接触电阻进一步减小,增加了p型氮化镓基器件在cmos电路中的作用。

26.优选地,步骤(1)所述区域化处理包括:

27.在p型氮化镓外延结构上旋涂光刻胶,然后进行曝光显影。

28.优选地,对步骤(1)得到的p型氮化镓基器件的电极区域进行刻蚀处理。

29.本发明中,对电极区域进行进一步刻蚀,有利于去除表面的氧化物,从而消除表面氧化物带来的肖特基势垒升高的问题。

30.优选地,所述刻蚀处理包括干法刻蚀处理。

31.本发明中,干法刻蚀的目的为将电极区域处的p型氮化镓从垂直方向去除,可以对p型氮化镓基器件的电极区域进行全刻蚀,也可以对p型氮化镓基器件的电极区域进行图形化处理,图形包括但不限于圆形、矩形形、五边形、六边形等。

32.优选地,步骤(2)所述热处理的方法为将步骤(1)经过处理的p型氮化镓外延结构放入真空磁控溅射设备腔中进行热处理。

33.本发明,在超高真空环境中对p型氮化镓外延结构进行处理,有利于在去除p型氮化镓表面的氧化物的同时,而不被氧气再次氧化表面,充分消除氧化物带来的肖特基势垒高度升高的问题。

34.优选地,步骤(2)所述热处理的温度为80~150℃,例如80℃、90℃、100℃、110℃、120℃、130℃、140℃或150℃等。

35.本发明中,热处理的温度过高会带来其它的负面影响,比如破坏氮化镓的晶格结构等,温度温度过低,会使氧化钾表面污染物解离不完全。

36.优选地,步骤(2)所述热处理的时间为20~40min,例如20min、25min、30min、35min或40min等。

37.优选地,步骤(2)所述沉积的方法为真空磁控溅射法。

38.作为优选的技术方案,所述p型氮化镓基器件的电极的制备方法包括以下步骤:

39.(1)在p型氮化镓外延结构上旋涂光刻胶,然后进行曝光显影,露出p型氮化镓基器件的电极区域;

40.(2)对步骤(2)得到的p型氮化镓基器件的电极区域进行干法刻蚀处理,得到经过处理后的样品;

41.(3)将步骤(2)经过处理后的样品放入真空磁控溅射设备腔中以80~150℃的温度进行热处理20~40min,然后在步骤(1)所述p型氮化镓基器件的电极区域上用真空磁控溅射法依次沉积氧化镍层、铂层和金层,再进行金属剥离,得到所述的p型氮化镓基器件的电极;

42.其中,所沉积的氧化镍层为p型结构。

43.第三方面,本发明还提供一种p型氮化镓基器件,所述p型氮化镓基器件包括依次层叠设置的衬底、p型氮化镓外延结构和如第一方面所述的p型氮化镓基器件的电极,其中,所述p型氮化镓外延结构位于所述衬底的表面,所述电极位于p型氮化镓外延结构上;

44.如第一方面所述的p型氮化镓基器件的电极在所述p型氮化镓基器件中用作源极和漏极。

45.优选地,所述衬底包括蓝宝石、硅或碳化硅中的任意一种或至少两种的组合。

46.相对于现有技术,本发明具有以下有益效果:

47.本发明所提供的p型氮化镓基器件的电极,用于p型氮化镓基器件的源极和漏极,解决了电极中金属层的氧化问题,还降低了器件中金属/半导体接触面的肖特基势垒高度,同时通过超高真空热处理,解决了ga2o3污染层导致的肖特基势垒高度升高问题,降低了器件源漏极欧姆接触电阻,提高了p型氮化镓基晶体管的性能,使得p型氮化镓基器件能够在cmos电路发挥更大的作用,其比接触电阻ρ

c

可降至10

‑5~10

‑7ω

·

mm。

附图说明

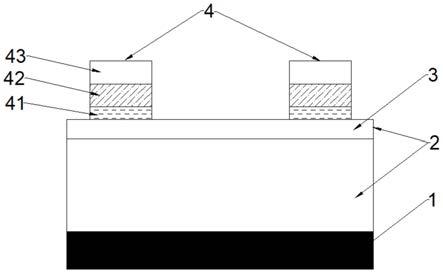

48.图1为实施例1提供的p型氮化镓基器件的结构示意图。

[0049]1‑

衬底,2

‑

p型氮化镓外延结构,3

‑

p型氮化镓,4

‑

电极,41

‑

氧化镍层,42

‑

铂层,43

‑

金层。

具体实施方式

[0050]

下面通过具体实施方式来进一步说明本发明的技术方案。本领域技术人员应该明了,所述实施例仅仅是帮助理解本发明,不应视为对本发明的具体限制。

[0051]

实施例1

[0052]

如图1所示:本实施例提供一种p型氮化镓基器件的电极4,所述电极4包括依次层叠设置的氧化镍层41、铂层42和金层43,其中,所述氧化镍层41为p型结构,,所述铂层42位于所述氧化镍层41和金层43的中间,所述氧化镍层41为p型氮化镓基器件的欧姆接触层,所述电极用于器件的源极和漏极。

[0053]

其中,源极的总厚度为115nm,氧化镍层41的厚度为10nm,铂层42的厚度为30nm,金层43的厚度为75nm;

[0054]

漏极的总厚度为115nm,氧化镍层41的厚度为10nm,铂层42的厚度为30nm,金层43的厚度为75nm。

[0055]

所述电极的制备方法如下:

[0056]

(1)在p型氮化镓外延结构2包括的p型氮化镓3上旋涂一层光刻胶,然后经过曝光显影后,露出p型氮化镓基器件的源极和漏极区域;

[0057]

(2)将经过步骤(1)处理后的样品放入科特莱思科的型号为lab18的真空磁控溅射设备的进样室内,先在真空度为10

‑7pa,温度为80℃的条件下,对样品加热30min;

[0058]

(3)步骤(2)加热结束后,在原有进样室内,依然在真空度为10

‑7pa条件下,在p型氮化镓基器件的源极和漏极区域上,同时打开li源和nio源的盖板,使两个源同时溅射,先沉积p型nio,形成p型nio层41,然后再后依次沉积铂层42和金层43;

[0059]

(4)用dmso(二甲基乙枫)溶液,在90℃水浴下,进行金属剥离,得到所述的p型氮化镓基器件的电极4。

[0060]

本实施例还提供一种p型氮化镓基器件,所述器件包括依次层叠设置的衬底1、p型氮化镓外延结构2和上述制备得到的电极4,所述衬底1为蓝宝石衬底。

[0061]

实施例2

[0062]

本实施例与实施例1的区别为,本实施例中电极经过刻蚀,电极区域形成个凹坑,然后金属沉积在凹坑上。

[0063]

所述电极的制备方法如下:

[0064]

(1)在p型氮化镓外延结构上沉积一层100nm厚的氧化硅,做为硬掩模,在p型氮化镓外延结构包括的p型氮化镓上旋涂一层光刻胶,然后经过曝光显影后,露出p型氮化镓基器件的源极和漏极区域;

[0065]

(2)用icp干法刻蚀将覆盖在源漏极区域的氧化硅去除,然后用去离子水冲洗步骤(1)的样品3min,并最终用氮气吹干,清洗掉光刻胶;

[0066]

(3)将经过步骤(2)处理的样品在beo中浸泡3min,随后用去离子水冲洗3min,并用

氮气吹干,然后再用icp刻蚀未被氧化硅覆盖的源极和漏极区域,刻蚀深度5nm;

[0067]

(4)将经过步骤(3)处理后的样品放入型号放入科特莱思科的型号为lab18的真空磁控溅射设备的进样室内,先在真空度为10

‑7pa,温度为150℃的条件下,对样品加热20min;

[0068]

(5)步骤(4)加热结束后,在原有进样室内,依然在真空度为10

‑7pa条件下,在p型氮化镓基器件的源极和漏极区域上,同时打开li源和nio源的盖板,使两个源同时溅射,先沉积p型nio,形成p型nio层,然后再后依次沉积铂层和金层

[0069]

(6)用dmso(二甲基乙枫)溶液,在90℃水浴下,进行金属剥离,得到所述的p型氮化镓基器件的电极。

[0070]

实施例3

[0071]

本实施例所提供的电极与实施例2的区别为,电极经过图形化处理,会表现为在电极区域内会表现为有间隔的矩阵分布的刻蚀孔。

[0072]

本实施例与实施例2的区别还包括,在步骤(2)和步骤(3)之间,增加一个步骤,所增加的步骤为:

[0073]

经过步骤(2)的清洗后,在源极和漏极区域旋涂一层光刻胶,然后经过曝光显影后,使得源极和漏极区域处具有多个矩形;

[0074]

其余制备方法与参数与实施例2保持一致。

[0075]

实施例4

[0076]

本实施例提供一种p型氮化镓基器件的电极,所述电极包括依次层叠设置的氧化镍层、铂层和金层,其中,所述氧化镍层为p型结构,所述铂层位于所述氧化镍层和金层的中间,所述氧化镍层为p型氮化镓基器件的欧姆接触层,所述电极用于器件的源极和漏极。

[0077]

其中,源极的总厚度为60nm,氧化镍层的厚度为5nm,铂层的厚度为5nm,金层的厚度为50nm;

[0078]

漏极的总厚度为60nm,氧化镍层的厚度为5nm,铂层的厚度为5nm,金层的厚度为50nm。

[0079]

所述电极的制备方法如下:

[0080]

本实施例所提供的制备方法与步骤(1)所提供的制备方法除步骤(2)中热处理的温度为110℃,加热时间为40min外,其余制备方法与参数与实施例1保持一致。

[0081]

本实施例还提供一种p型氮化镓基器件,所述器件包括依次层叠设置的衬底、p型氮化镓外延结构和上述制备得到的电极,所述衬底为硅衬底。

[0082]

实施例5

[0083]

本实施例提供一种p型氮化镓基器件的电极,所述电极包括依次层叠设置的氧化镍层、铂层和金层,其中,所述氧化镍层为p型结构,所述铂层位于所述氧化镍层和金层的中间,所述氧化镍层为p型氮化镓基器件的欧姆接触层,所述电极用于器件的源极和漏极。

[0084]

其中,源极的总厚度为200nm,氧化镍层的厚度为50nm,铂层的厚度为50nm,金层的厚度为100nm;

[0085]

漏极的总厚度为200nm,氧化镍层的厚度为50nm,铂层的厚度为50nm,金层的厚度为100nm。

[0086]

本实施例所提供的电极的制备方法与实施例1保持一致。

[0087]

本实施例还提供一种p型氮化镓基器件,所述器件包括依次层叠设置的衬底、p型

氮化镓外延结构和上述制备得到的电极,所述衬底为碳化硅衬底。

[0088]

实施例6

[0089]

本实施例与实施例1的区别为,制备电极过程中,步骤(2)的热处理的温度为40℃。

[0090]

其余制备方法与参数与实施例1保持一致。

[0091]

实施例7

[0092]

本实施例与实施例1的区别为,制备电极过程中,步骤(2)的热处理的温度为160℃。

[0093]

其余制备方法与参数与实施例1保持一致。

[0094]

对比例1

[0095]

本对比例提供一种p型氮化镓基器件的电极,所述电极包括依次层叠设置的氧化镍层和金层,其中,所述氧化镍层为p型氮化镓基器件的欧姆接触层,所述电极用于器件的源极和漏极。

[0096]

其中,源极的总厚度为85nm,氧化镍层的厚度为10nm,金层的厚度为75nm;

[0097]

漏极的总厚度为85nm,氧化镍层的厚度为10nm,金层的厚度为75nm。

[0098]

所述电极的制备方法如下:

[0099]

(1)在p型氮化镓外延结构包括的p型氮化镓上旋涂一层光刻胶,然后经过曝光显影后,露出p型氮化镓基器件的源极和漏极区域;

[0100]

(2)将经过步骤(1)处理后的样品放入科特莱思科的型号为lab18的真空磁控溅射设备的进样室内,先在真空度为10

‑7pa,温度为80℃的条件下,对样品加热30min;

[0101]

(3)步骤(2)加热结束后,在原有进样室内,依然在真空度为10

‑7pa条件下,在p型氮化镓基器件的源极和漏极区域上,同时打开li源和nio源的盖板,使两个源同时溅射,先沉积p型nio,形成p型nio层,然后再后沉积金层

[0102]

(4)用dmso(二甲基乙枫)溶液,在90℃水浴下,进行金属剥离,得到所述的p型氮化镓基器件的电极。

[0103]

本对比例还提供一种p型氮化镓基器件,所述器件包括依次层叠设置的衬底、p型氮化镓外延结构和上述制备得到的电极,所述衬底为蓝宝石衬底。

[0104]

对比例2

[0105]

本对比例提供一种p型氮化镓基器件的电极,所述电极包括依次层叠设置的铂层、氧化镍层和金层,其中,所述氧化镍层位于所述铂层和金层的中间,所述铂层为p型氮化镓基器件的欧姆接触层,所述电极用于器件的源极和漏极。

[0106]

其中,源极的总厚度为115nm,铂层的厚度为30nm,氧化镍层的厚度为10nm,金层的厚度为75nm;

[0107]

漏极的总厚度为115nm,铂层的厚度为30nm,氧化镍层的厚度为10nm,金层的厚度为75nm;

[0108]

所述电极的制备方法如下:

[0109]

(1)在p型氮化镓外延结构包括的p型氮化镓上旋涂一层光刻胶,然后经过曝光显影后,露出p型氮化镓基器件的源极和漏极区域;

[0110]

(2)将经过步骤(1)处理后的样品放入科特莱思科的型号为lab18的真空磁控溅射设备的进样室内,先在真空度为10

‑7pa,温度为80℃的条件下,对样品加热30min;

实施例610

‑5~10

‑6实施例710

‑5~10

‑6对比例110

‑3~10

‑6对比例210

‑3~10

‑5对比例310

‑5~10

‑6[0128]

从实施例1与实施例2和3的数据结果可知,对电极中露出源极和漏极的区域处进一步进行刻蚀,有利于去除表面氧化物,降低比接触电阻。

[0129]

从实施例1与实施例6和实施例7的数据结果可知,热处理过程中温度过高或过低,均会导致欧姆接触电阻降低。

[0130]

从实施例1与对比例1的数据结果可知,当电极中不加入铂层时,会导致金属扩散,从而增大比接触电阻。

[0131]

从实施例1与对比例2的数据结果可知,当欧姆接触层变为铂层时,会导致热稳定性变差,欧姆接触不稳定。

[0132]

从实施例1与对比例3的数据结果可知,欧姆接触层为镍层时,相比于氧化镍层,欧姆接触阻值会偏大一些。

[0133]

综上所述,nio做为欧姆接触层,与p型氮化镓形成欧姆接触,au做为保护层,pt作为扩散阻挡层位于最中间时,p型氮化镓基器件的欧姆接触电阻可以显著降低,最终提高了p型氮化镓晶体管的性能,使得p型氮化镓基器件能够在cmos电路中发挥更大的作用。

[0134]

申请人声明,以上所述仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,所属技术领域的技术人员应该明了,任何属于本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,均落在本发明的保护范围和公开范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1