静电放电保护半导体结构及其制造方法与流程

1.本发明涉及一种静电放电保护半导体结构和形成静电放电保护半导体结构的方法。本发明还涉及一种包括静电放电保护半导体结构的集成电路。

背景技术:

2.众所周知,高速数据传输集成电路容易受到静电放电(esd)事件的影响。由于寄生线路电容的限制,内部保护结构必须很小。此外,由于处理高数据速率需要先进的半导体,因此最大钳位电压和最大允许电流很小。

3.当使用外部板载(on-board)保护时,应力电流在作为集成电路的一部分的内部保护与外部保护装置之间共享。内部路径中的阻抗越大,系统稳健性越高。但是信号路径中的大阻抗使信号的可检测性劣化。

4.worley在2019年esd研讨会上提出的一种已知解决方案建议使用扩散电阻器。扩散电阻器的电阻是非线性的。对于高电流密度,电子速度饱和并且电阻增加。这种扩散电阻器在正常数据传输期间将呈现低阻抗,其中使用几ma范围内的低电流,同时为esd事件提供高阻抗,其中电流较高,例如,在几安培的范围内。

5.瞬态电压抑制器(tvs)钳位的一个非常重要的问题是它们能够将电压限制在可能损坏最先进的片上系统(soc)输入/输出(i/o)的电平以下,而该输入/输出(i/o)可能在低至3.5v的电压下发生故障。由于将tvs的分流电阻降低到可接受的电平非常困难,因此另一种选择是在tvs和i/o之间引入衰减电阻器。一种选择是使用饱和电阻器作为保护低电平i/o的手段。

6.tvs装置用于保护经受外部产品级esd的soc i/o。在某些情况下,soc i/o可以在8kv电平下经受高达30a的峰值放电电流,在接触模式下变成短路。同时,soc i/o可能会在电压低至3.5v时出现故障。当输入电流超过10a时,tvs钳位不可能将电压钳位到3.5v。例如,当处于触发状态时具有包括电路板走线电阻的0.4ω的低分流电阻和2v的偏置电压的良好的tvs钳位对于具有8kv接触的30a峰值放电电流具有14v的电压降,假设没有电流分流到芯片的i/o。

7.一种保护灵敏soc i/o的新方法是使用具有电流饱和特性的衰减电阻器。

8.这可以是以其工艺简单而闻名的n型速度饱和电阻器。该分析将假设所讨论的soc i/o可以通过人体模型(hbm)1kv规范,同时假设在系统电平下应用8kv接触放电。

9.另一个问题涉及使用基于经验的模型确定i/o的故障点。生成故障数据的i/o的传输线脉冲(tlp)测试很常见,但将该数据转换为国际电工委员会(iec)的关于esd放电波形的抗扰度标准的故障点是有问题的。一种方法是使100ns tlp放电的故障阈值处的总能量等于对应的iec放电曲线的总能量。不幸的是,导致故障的热过程不是绝热的,大部分放电功率进入保护网络而不是进入通常确定i/o的故障点的受保护装置。另一个复杂因素是tvs钳位的瞬态响应。

10.由于其电子载流子的速度饱和,已知的n阱(nwell)电阻器可具有电流饱和特性。

唯一的要求是使n+到n+的长度为几微米或更短,以便获得足够高的场用于在击穿之前发生速度饱和。因此,对于低场、低电流条件,i-v特性基本上是线性的,适用于正常的i/o操作。

11.对于电压较高的esd条件,电阻器可以使电流饱和并限制流入i/o的电流低于故障条件,并允许tvs和i/o之间的电压增加。

12.in阱-vn阱(inwell-vnwell)曲线如图1a中所示。线性区域电阻为1.3ω,足够低,不会干扰正常的i/o操作。信号线的特性阻抗通常在50到100ω的范围内。16v处的饱和电流为0.68a,其对应于1k hbm放电的峰值电流。

13.图1b示出了使用1.2ns vftlp以通用180nm cmos工艺制造的n阱电阻器的i-v图。图1c示出了使用来自以通用0.18μm工艺布局的n阱电阻器的tlp数据(100ns)的i-v图。图中还示出了归一化dc电阻rdc/ro(初始r测量值)。

14.vftlp和tlp曲线在击穿点之前基本相同。vftlp曲线示出了更高电流下击穿电压的回弹(snap-back)。

15.发现一种方法可以使tvs分流器两端的电压降远大于受保护soc i/o的故障电压。tvs电压与i/o故障电压限制之间的差被速度饱和电阻器吸收。这消除了对tvs的严格电压降限制。引脚处的大部分功率被esd钳位电路吸收,而不是被受保护装置吸收。

16.worley在2019年esd研讨会上示出的这些扩散电阻器缺点:在足够高的电流下雪崩击穿与回弹相结合。这限制了扩散电阻器用于吸收tvs电压与i/o故障电压之间的电压差的有用性。由于回弹,这种扩散电阻器经常被细丝(filamentation)损坏。

技术实现要素:

17.各种示例实施例针对如上所述的缺点和/或从以下公开中可以变得明显的其他缺点。

18.根据本发明的实施例,放电保护半导体结构包括:

19.衬底,

20.阱,其设置在衬底上,以及

21.电阻器,其嵌入阱中。

22.放电保护半导体结构还可以包括第一触点扩散部和第二触点扩散部,第一触点扩散部和第二触点扩散部设置在阱的顶侧上。电阻器可以设置在第一触点扩散部与第二触点扩散部之间。

23.第一触点扩散部和第二触点扩散部可以突出到阱中或者阱下方的衬底中。

24.阱可以具有第一极性,电阻器可以具有第二极性,第二极性与第一极性相反。

25.阱的掺杂和电阻器的掺杂可以具有相似的水平。

26.根据本发明的实施例,衬底为p掺杂或n掺杂,其中,阱为n掺杂,并且其中,第一触点扩散部和第二触点扩散部为p掺杂,并且其中,电阻器为p掺杂。本发明的范围不限于这样的掺杂布置。其还包括相反的掺杂布置,即,衬底为p掺杂或n掺杂,其中,阱为p掺杂,其中,第一触点扩散部和第二触点扩散部为n掺杂,并且其中,电阻器为n掺杂。其还包括这样的布置:其中,衬底和阱具有相同的极性,而触点扩散部和电阻器具有相反的极性。

27.根据本发明的实施例,电阻器的长度在0.2μm与2μm的范围内。

28.根据本发明的实施例,电阻器的宽度在0.05mm与20mm的范围内。

29.根据本发明的实施例,电阻器可以在10e

17

至10e

19

的范围内掺杂,并且电阻器的厚度可以在0.01μm至0.5μm的范围内。

30.根据本发明的实施例,电阻器针对ma电流级别可以具有0.2与10ohm之间的电阻。

31.根据本发明的实施例,电阻器形成为多指布置。

32.根据本发明的实施例,第一触点扩散部和第二触点扩散部与阱一起形成具有浮动基极的双极晶体管。

33.本发明还涉及一种包括如以上实施例中公开的放电保护半导体结构的集成电路。

34.本发明还涉及一种制造如以上实施例中公开的放电保护半导体结构的方法。

35.本发明还涉及一种制造包括如以上实施例中公开的放电保护半导体结构的集成电路的方法。

36.如以上实施例中公开的放电保护半导体结构确保了非常良好的、非常稳健的静电放电保护。

37.如以上实施例中公开的双极晶体管具有以下特征:与电阻层的击穿电压相似的击穿电压,该特征提供了非常稳健的静电放电保护。

38.本发明还涉及两级保护系统。该两级保护系统包括第一保护级和第二保护级。第二保护级连接在信号线与电源线之间。两级保护系统还包括设置在第一保护级与第二保护级之间的信号线内的电阻器。

附图说明

39.为了可以详细地理解本公开的特征,参照其中一些在附图中示出的实施例进行了更具体的描述。然而,要注意,附图仅示出了典型的实施例,因此不应被认为是对其范围的限制。附图用于促进对本公开的理解,因此不一定按比例绘制。结合附图阅读本描述之后,所要求保护的主题的优点对于本领域技术人员将变得显而易见,在附图中,同样的附图标记用于表示同样的元件,并且在附图中:

40.图1a、图1b和图1c示出了worley在2019年esd研讨会上展示的已知扩散电阻器的i/v图;

41.图2示出了与本发明的实施例有关的图;

42.图3示出了本发明的实施例;

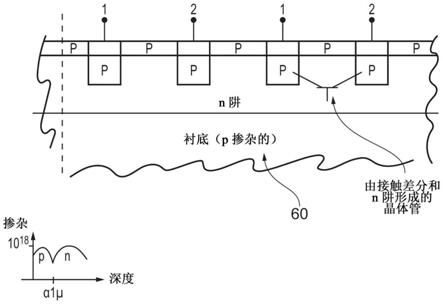

43.图4示出了本发明的实施例;

44.图5示出了本发明的实施例;

45.图6示出了具有两级保护系统的本发明的实施例。

具体实施方式

46.本发明的实施例涉及基于速度饱和的非线性电阻器,其对于信号传输电流电平具有低电阻值并且对于esd电流电平具有高电阻。非线性电阻器是通过嵌入在具有不同掺杂的较厚且相似的高度掺杂的阱中的薄且高度掺杂的扩散来实现的。

47.根据本发明的扩散电阻器没有回弹。电阻器对于高电流密度将是稳健的,因为不会发生细丝。这是通过电阻器来实现的,该电阻器由嵌入具有与掺杂水平相当但具有不同极性的阱中的短、薄且高度掺杂的层形成。

48.根据本发明的实施例,使用合适的注入来形成在0.1μm的范围内的非常薄的扩散层,其具有在10e

18

范围内的相对高的掺杂水平。对应的电阻层夹在覆盖有氧化物的硅表面与具有不同极性的相似高度掺杂的阱之间。

49.图2示出了使用硼时掺杂水平为20、使用磷掺杂时掺杂水平为22以及使用绝对掺杂时掺杂水平为24,示出了0.1μm处的结。

50.本发明的实施例示出在图3中。在该实施例中,电阻器34由两个触点扩散部(第一触点扩散部30和第二触点扩散部32)连接。电阻器38的长度(即,所述触点扩散部之间的距离)在1至2μm的范围内。电阻器40的总宽度是限定最终电阻值的参数。电阻器的总宽度在0.5mm至3mm的范围内。

51.电阻器最好以多指(multi-finger)布置形成。这在图4中进行了说明。在这种布置中,电流可以从触点的两侧流动,从而有效地将电阻器的宽度加倍。第一触点扩散部30和第二触点扩散部32位于阱36上。阱位于衬底60上。

52.在本发明的实施例中,第一触点扩散部30和第二触点扩散部32为p掺杂,电阻器34为p掺杂,阱36为n掺杂,并且衬底60为p掺杂。本发明的范围还包括相反的掺杂布置,即,第一触点扩散部30和第二触点扩散部32为n掺杂,电阻器34为n掺杂,阱36为p掺杂,并且衬底60为n掺杂。

53.触点扩散部30和32与阱36一起形成具有浮动基极52的双极晶体管。

54.该晶体管52与电阻器50并联。晶体管的击穿电压与电阻器的击穿电压相当或稍小于电阻器的击穿电压。这示出在图5中。

55.在本发明的另一实施例中,触点嵌入电阻层内。可以制作触点,使得触点扩散部比电阻扩散部更浅,或者可以用硅化/矽化(salicidation)来制作触点。

56.非常薄的两个触点扩散层30和32以及具有相似高掺杂水平的下方阱36的这种组合提供了非常好的esd保护。

57.本发明的该实施例的另一个有利特征是电阻器的触点扩散部与其击穿电压类似于电阻层的击穿电压的下方阱形成双极晶体管。触点扩散部30和32可以被限制在阱36内。

58.当电阻层内的雪崩在足够高的电压下开始时,少数载流子被注入电阻层。这些少数载流子引起回弹。本发明的该实施例确保了少数载流子中的大多数不会留在电阻层内,而是被下方的阱捕获,因为电阻层太薄。下方阱由于其高掺杂而具有低电阻。因此,被捕获的少数载流子可以有效地排出到触点之一。

59.由于少数载流子的有效捕获,回弹较小,这导致回弹电压较高。

60.此外,触点扩散部与下方阱一起形成对称的双极结型晶体管。如果该双极结型晶体管的击穿电压小于电阻器的击穿电压或与其相当,则可能无法达到电阻器内发生雪崩的条件。以这种方式,确保没有雪崩和回弹。

61.本发明的上述实施例(即,瞬态电流抑制器)可以用在板上的信号线内。瞬态电流抑制器放置在外部连接器(即,插座)与数据处理集成电路之间。

62.连同放置在瞬态电流抑制器与外部插座之间的附加板载保护装置,进一步提高了整个系统的稳健性。这种布置呈现如图6中所示的两级保护系统。两级保护系统包括第一保护级100和第二保护级102。第一保护级100和第二保护级102连接在信号线106与电源线之间。两级保护系统还包括设置在第一保护级100与第二保护级100之间的信号线106内的电

阻器104。

63.第一保护级100是例如板载保护装置或任何其他合适的装置。第二保护级102可以是例如集成电路或任何其他合适装置中的内部静电放电保护结构。应力电流被分为通过第一保护级100的电流和通过第二保护级102的电流。ic的内部保护结构只能承受一定的应力电流。因此,必须最小化通过第二保护级的电流。通过第二保护级的电流取决于电阻器104两端的电压降:电阻器两端的电压降越高,通过第二保护级的电流越小。根据本发明的电阻器对于应力电流将呈现大电阻值并且因此将降低通过第二保护级的电流。对于第二保护级的给定稳健性,当根据本发明的电阻器放置在第一保护级与第二保护级之间时,可以施加更大的应力。这显着提高了系统的稳健性。

64.所附独立权利要求中阐述了本发明的特定和优选的方面。来自从属权利要求和/或独立权利要求的特征的组合可以适当地结合,而不仅是如权利要求中所阐述的。

65.本公开的范围包括任何新颖的特征或其中明确或隐含地公开的特征的组合或其任何概括,而不管其是否涉及要求保护的发明或减轻了本发明所解决的任何或所有问题。申请人特此通知,在起诉本技术或由此衍生的任何此类进一步申请期间,可以对这样的特征提出新的权利要求。特别地,参照所附权利要求,可以将从属权利要求的特征与独立权利要求的特征组合,并且可以以任何适当的方式而不是仅仅以权利要求中列举的特定组合来组合来自各个独立权利要求的特征。

66.在单独的实施例的上下文中描述的特征也可以在单个实施例中组合提供。相反,为简洁起见,在单个实施例的上下文中描述的各种特征也可以单独地或以任何合适的子组合来提供。

67.术语“包括”不排除其他元件或步骤,术语“一”或“一个”不排除多个。权利要求中的附图标记不应解释为限制权利要求的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1