一种高压LED芯片双ISO工艺的制作方法

一种高压led芯片双iso工艺

技术领域

1.本发明涉及半导体器件领域,具体涉及一种高压led芯片双iso工艺。

背景技术:

2.随着半导体技术的不断发展,led芯片以节能、高亮、耐久性高、寿命长、轻巧等优势占据照明、显示两大领域的主导地位,高压(hv)led芯片更是极大的应用于球泡灯方向,高压(hv)led芯片在芯片制作阶段,将每个独立的发光单元串联,减少了封装阶段焊线次数,节约了成本,更是大大提高了生产效率,高压(hv)led芯片以电压高的优势,有效降低应用端的驱动成本;

3.随着技术逐渐的发展,目前高压产品逐渐推出双iso工艺进行发光效率的提升,目前主流双iso工艺采用的是先进行沟道光刻,干法刻蚀沟道处gan,然后进行金属桥接处光刻,干法刻蚀桥接处gan的工艺,以达到沟道和桥接双角度的效果;但是现有的工艺在成本上还需要进一步降低,同时对生产效率还需要提高。基于上述叙述,本发明在此基础上提供了一种高压led芯片双iso工艺的制造方法。

技术实现要素:

4.本发明的目的是提供一种高压led芯片双iso工艺的制造方法,对现有双iso工艺就行优化,降低双iso工艺的成本,提高生产效率。

5.本发明采用以下技术方案解决上述技术问题的:

6.一种高压led芯片双iso工艺,步骤包括:

7.步骤一:在一长有外延层的基板上涂布第一光刻胶,利用第一光罩版进行曝光,然后显影、坚膜;

8.步骤二:在所述步骤一基础上涂布第二光刻胶,利用第二光罩版进行曝光,然后显影、烘烤;

9.步骤三:在所述步骤二基础上进行icp刻蚀;

10.步骤四:去除光刻胶。

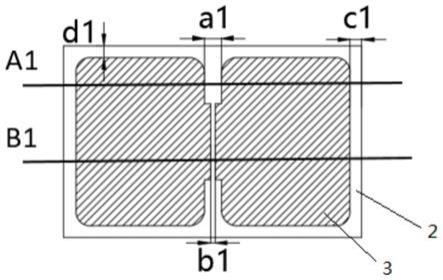

11.进一步地,所述第一光罩版中:10um≤c1=d1≤20um,20um≤a1≤30um,2um≤b1≤10um;其中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度。

12.进一步地,所述第二光罩版中:5um≤c2=d2≤15um,5um≤a2≤15um,50um≤b2≤70um;其中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度。

13.进一步地,所述第一光刻胶为正性光刻胶,厚度为6

‑

12um;所述第一光刻胶坚膜温度为100

‑

160℃,坚膜时间为30

‑

60min。

14.进一步地,所述第二光刻胶为正性光刻胶,厚度为4

‑

8um;所述第二光刻胶烘烤温度为80

‑

110℃,烘烤时间为10

‑

20min。

15.进一步地,所述第二光刻胶为正性光刻胶,步骤四完成后,沟道处外延层与基板夹角60

°

≤γ≤80

°

。

16.进一步地,所述第二光刻胶为正性光刻胶,步骤四完成后,桥接处外延层与基板夹角20

°

≤β≤50

°

,侧壁处外延层与基板夹角60

°

≤α≤80

°

。

17.进一步地,所述第二光刻胶为负性光刻胶,厚度为4

‑

10um;所述第二光刻胶烘烤温度为50

‑

80℃,烘烤时间为2

‑

4min。

18.进一步地,所述第二光刻胶为负性光刻胶,步骤四完成后,沟道处外延层与基板夹角75

°

≤γ2<90

°

。

19.进一步地,所述第二光刻胶为负性光刻胶,步骤四完成后,桥接处外延层与基板夹角20

°

≤β2≤50

°

,侧壁处外延层与基板夹角75

°

≤α2<90

°

20.本发明的优点在于:

21.1、本发明提供的高压led芯片双iso工艺为连续两次光刻,一次icp刻蚀,对现有双iso两次光刻,两次icp刻蚀的工艺进行优化,相比于现有工艺,减少了一道icp刻蚀工序,降低双iso工艺的成本,提高了生产效率;

22.2、本发明提供了一种第二次光刻自由选择正负胶性的工艺,从而可以自由调节沟道和侧壁的刻蚀角度;其中,由于光刻胶的光敏性,通过改变光刻能量,可以在25

°

~85

°

范围内自由调节沟道和侧壁的刻蚀角度。

23.3、本发明中的所述第一光罩版中:10um≤c1=d1≤20um,20um≤a1≤30um,2um≤b1≤10um;所述第二光罩版中:5um≤c2=d2≤15um,5um≤a2≤15um,50um≤b2≤70um;其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;相对于现有技术中的切割道的宽度,其数值大幅度降低,从而增大发光面积,提升发光效率。

附图说明

24.图1是本发明第一光罩示意图;

25.图2是本发明第一次光刻完成后沿图1中a1线的剖视图;

26.图3是本发明第一次光刻完成后沿图1中b1线的剖视图;

27.图4是本发明某一实施例中第二光罩示意图;

28.图5是本发明某一实施例中第二次光刻完成后沿图4中a2线的剖视图;

29.图6是本发明某一实施例中第二次光刻完成后沿图4中b2线的剖视图;

30.图7是本发明某一实施例中icp刻蚀完去胶后沿图4中a2线的剖视图;

31.图8是本发明某一实施例中icp刻蚀完去胶后沿图4中b2线的剖视图;

32.图9是本发明某一实施例中第二光罩示意图;

33.图10是本发明某一实施例中第二次光刻完成后沿图9中a2线的剖视图;

34.图11是本发明某一实施例中第二次光刻完成后沿图9中b2线的剖视图;

35.图12是本发明某一实施例中icp刻蚀完去胶后沿图9中a2线的剖视图;

36.图13是本发明某一实施例中icp刻蚀完去胶后沿图9中b2线的剖视图;

37.其中,1、基板;2、外延层;3、光刻胶。

具体实施方式

38.下面结合具体实施方式对本发明做进一步说明,以下实施例旨在说明本发明而不是对本发明的进一步限定。以下实施例中所用的技术手段为本领域技术人员所熟知的常规手段,所有原料均为通用材料。

39.实施例1

40.如图1~8中,图1是本发明第一光罩示意图;图2是本发明第一次光刻完成后沿图1中a1线的剖视图;图3是本发明第一次光刻完成后沿图1中b1线的剖视图;图4是本发明某一实施例中第二光罩示意图;图5是本发明某一实施例中第二次光刻完成后沿图4中a2线的剖视图;图6是本发明某一实施例中第二次光刻完成后沿图4中b2线的剖视图;图7是本发明某一实施例中icp刻蚀完去胶后沿图4中a2线的剖视图;图8是本发明某一实施例中icp刻蚀完去胶后沿图4中b2线的剖视图;

41.本技术实施例1中提供的高压led芯片双iso工艺,步骤包括:

42.步骤一:在一长有外延层的基板上涂布第一光刻胶,利用第一光罩版进行曝光,然后显影、坚膜;

43.步骤二:在所述步骤一基础上涂布第二光刻胶,利用第二光罩版进行曝光,然后显影、烘烤;

44.步骤三:在所述步骤二基础上进行icp刻蚀,将没有光刻胶保护的地方的外延层刻穿,刻蚀至基板;

45.步骤四:刻蚀完成后去除表面光刻胶。

46.其中:

47.第一光罩版中:c1=d1=15um,a1=25um,b1=6um;第二光罩版中:c2=d2=10um,a2=10um,b2=60um;

48.其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;

49.第一光刻胶为正性光刻胶,厚度为9um;第一光刻胶坚膜温度为130℃,坚膜时间为45min;第二光刻胶为正性光刻胶,厚度为6um;第二光刻胶烘烤温度为95℃,烘烤时间为15min;

50.步骤四完成后,沟道处外延层与基板夹角γ=70

°

;桥接处外延层与基板夹角β=35

°

,侧壁处外延层与基板夹角α=70

°

。

51.实施例2,

52.在实施例1工艺的基础上,对各步骤中参数进行调整,其中:

53.第一光罩版中:c1=d1=10um,a1=20um,b1=2um;第二光罩版中:c2=d2=5um,a2=5um,b2=50um;

54.其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;

55.第一光刻胶为正性光刻胶,厚度为6um;第一光刻胶坚膜温度为100℃,坚膜时间为30min;第二光刻胶为正性光刻胶,厚度为4um;第二光刻胶烘烤温度为80℃,烘烤时间为

10min;

56.步骤四完成后,沟道处外延层与基板夹角γ=60

°

;桥接处外延层与基板夹角β=20

°

,侧壁处外延层与基板夹角α=60

°

。

57.实施例3

58.在实施例1工艺的基础上,对各步骤中参数进行调整,其中:

59.第一光罩版中:c1=d1=20um,a1=30um,b1=10um;第二光罩版中:c2=d2=15um,a2=15um,b2=70um;

60.其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;

61.第一光刻胶为正性光刻胶,厚度为12um;第一光刻胶坚膜温度为160℃,坚膜时间为60min;第二光刻胶为正性光刻胶,厚度为8um;第二光刻胶烘烤温度为110℃,烘烤时间为20min;

62.步骤四完成后,沟道处外延层与基板夹角γ=80

°

;桥接处外延层与基板夹角β=50

°

,侧壁处外延层与基板夹角α=80

°

。

63.实施例4:

64.如图9~13所示,图9是本发明某一实施例中第二光罩示意图;图10是本发明某一实施例中第二次光刻完成后沿图9中a2线的剖视图;图11是本发明某一实施例中第二次光刻完成后沿图9中b2线的剖视图;图12是本发明某一实施例中icp刻蚀完去胶后沿图9中a2线的剖视图;图13是本发明某一实施例中icp刻蚀完去胶后沿图9中b2线的剖视图;

65.本技术实施例2中提供的高压led芯片双iso工艺,步骤包括:

66.步骤一:在一长有外延层的基板上涂布第一光刻胶,利用第一光罩版进行曝光,然后显影、坚膜;

67.步骤二:在所述步骤一基础上涂布第二光刻胶,利用第二光罩版进行曝光,然后显影、烘烤;

68.步骤三:在所述步骤二基础上进行icp刻蚀,将没有光刻胶保护的地方的外延层刻穿,刻蚀至基板;

69.步骤四:刻蚀完成后去除表面光刻胶。

70.其中:

71.第一光罩版中:c1=d1=15um,a1=25um,b1=6um;第二光罩版中:c2=d2=10um,a2=20um,b2=60um;

72.其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;

73.第一光刻胶为正性光刻胶,厚度为9um;第一光刻胶坚膜温度为130℃,坚膜时间为45min;第二光刻胶为负性光刻胶,厚度为6um;第二光刻胶烘烤温度为65℃,烘烤时间为3

74.min;

75.步骤四完成后,沟道处外延层与基板夹角γ2=80

°

;桥接处外延层与基板夹角β2=35

°

,侧壁处外延层与基板夹角75

°

≤α2<90

°

。

76.实施例5

77.在实施例4工艺的基础上,对各步骤中参数进行调整,其中:

78.第一光罩版中:c1=d1=10um,a1=20um,b1=2um;第二光罩版中:c2=d2=5um,a2=5um,b2=50um;

79.其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;

80.第一光刻胶为正性光刻胶,厚度为6um;第一光刻胶坚膜温度为100℃,坚膜时间为30min;第二光刻胶为负性光刻胶,厚度为4um;第二光刻胶烘烤温度为50℃,烘烤时间为2min;

81.步骤四完成后,沟道处外延层与基板夹角γ2=75

°

;桥接处外延层与基板夹角β2=20

°

,侧壁处外延层与基板夹角α2=75

°

。

82.实施例6

83.在实施例4工艺的基础上,对各步骤中参数进行调整,其中:

84.第一光罩版中:c1=d1=20um,a1=30um,b1=10um;第二光罩版中:c2=d2=15um,a2=15um,b2=70um;

85.其中,在第一光罩版中,a1为芯片内部隔离沟道宽度,b1为桥接宽度,c1、d1为不同方向上的芯片外围隔离沟道宽度;在第二光罩版中,a2为芯片内部隔离沟道宽度,b2为桥接宽度,c2、d2为不同方向上的芯片外围隔离沟道宽度;

86.第一光刻胶为正性光刻胶,厚度为12um;第一光刻胶坚膜温度为160℃,坚膜时间为60min;第二光刻胶为负性光刻胶,厚度为10um;第二光刻胶烘烤温度为80℃,烘烤时间为4min;

87.步骤四完成后,沟道处外延层与基板夹角γ2=89

°

;桥接处外延层与基板夹角β2=50

°

,侧壁处外延层与基板夹角α2=75

°

。

88.最后应说明的是:以上实施例仅用以说明本发明而并非限制本发明所描述的技术方案;本领域的普通技术人员应当理解,仍然可以对本发明进行修改或等同替换;而一切不脱离本发明的精神和范围的技术方案及其改进,其均应涵盖在本发明的权利要求范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1