阵列基板的制备方法、阵列基板和显示装置与流程

1.本公开属于显示技术领域,具体涉及一种阵列基板的阵列基板的制备方法、 阵列基板和显示装置。

背景技术:

2.tft

‑

lcd(thin film transistor liquid crystal display,薄膜晶体管

‑

液晶显示 器)作为一种平板显示装置,因其具有体积小、功耗低、无辐射以及制作成本相 对较低等特点,而越来越多地被应用于高性能显示领域当中。

技术实现要素:

3.本公开旨在至少解决现有技术中存在的技术问题之一,提供一种阵列基板 的制备方法、阵列基板和显示装置。

4.第一方面,本公开实施例提供一种阵列基板的制备方法,包括:

5.在基底上形成第一导电层;

6.在所述第一导电层背离所述基底的一侧形成第二导电层;

7.在所述第二导电层上涂覆光刻胶层,对所述光刻胶层进行曝光和显影,得 到光刻胶的第一保留部分;

8.通过构图工艺形成第一导电图案,以第一导电图案作为掩膜对第一导电层 进行刻蚀,得到第二导电图案;

9.对所述光刻胶的第一保留部分进行灰化处理,得到光刻胶的第二保留部分;

10.以光刻胶的第二保留部分作为掩膜,对第一导电图案进行刻蚀,得到第三 导电图案;其中,所述第二导电图案在基底上的正投影覆盖所述第三导电图案 在所述基底上的正投影。

11.可选地,在基底上形成第一导电层的步骤之前还包括:

12.在基底上形成第一绝缘层;

13.在所述第一绝缘层背离所述基底的一侧形成第二绝缘层。

14.可选地,所述阵列基板包括交叉设置的多条栅线和多条数据线,以及多个 子像素,所述子像素包括薄膜晶体管、像素电极和公共电极;

15.在形成所述第三导电图案的同时还形成有所述栅线和所述薄膜晶体管的栅 极;

16.在形成所述第二导电图案的同时还形成有所述公共电极。

17.可选地,在以光刻胶的第二保留部分作为掩膜,对第二导电图案进行刻蚀, 得到第三导电图案之后,还包括:

18.在所述第三导电图案背离所述基底的一侧形成第三绝缘层;

19.通过构图工艺在所述第三绝缘层上形成过孔,所述过孔出露出部分第二导 电图案;

20.在所述第三绝缘层背离所述基底的一侧形成第三电极层,通过构图工艺形 成第

四导电图案,所述第四导电图案通过所述过孔与所述第二导电图案电连接。

21.可选地,所述阵列基板包括交叉设置的多条栅线和多条数据线,以及多个 子像素,所述子像素包括薄膜晶体管、像素电极和公共电极;

22.在形成所述第四导电图案的同时还形成有所述像素电极。

23.可选地,所述阵列基板包括显示区和围绕所述显示区的周边区,阵列基板 还包括由显示区延伸至周边区的栅线,所述周边区内设置有栅极驱动电路,所 述栅极驱动电路包括多个移位寄存器,每个移位寄存器包括多个薄膜晶体管, 所述多个薄膜晶体管至少包括输出晶体管,所述输出晶体管的漏极连接信号输 出线,所述信号输出线连接所述栅线;

24.其中,所述第三导图案为所述栅线,所述第二导电图案和第四导电图案共 同形成所述信号输出线。

25.可选地,对所述第一导电层进行刻蚀所用的刻蚀液为第一刻蚀液,对第二 导电图案进行刻蚀所用的刻蚀液为第二刻蚀液,其中,所述第一刻蚀液与所述 第二刻蚀液不同。

26.可选地,所述第一导电层的材料包括透明金属氧化物。

27.可选地,所述第二导电层的材料包括铜。

28.第二方面,本公开实施例提供一种阵列基板,包括:基底、第一绝缘层、 第二绝缘层、第二导电图案、第三导电图案、第三绝缘层和第四导电图案;

29.所述第一绝缘层设置在所述基底上;

30.所述第二绝缘层设置在所述第一绝缘层背离所述基底的一侧;

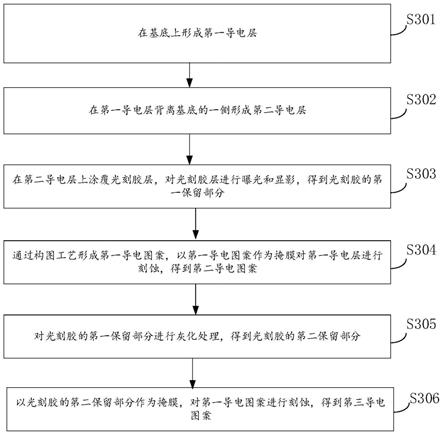

31.所述第二导电图案设置在所述第二绝缘层背离所述基底的一侧;

32.所述第三导电图案设置在所述第二导电图案背离所述基底的一侧,所述第 二导电图案在所基底上的正投影覆盖所述第三导电图案在所述基底上的正投影;

33.所述第三绝缘层设置在所述第三导电图案背离所述基底的一侧,所述第三 绝缘层具有过孔;

34.第四导电图案设置在所述第三导电图案背离所述基底的一侧,且所述第四 导电图案通过所述过孔与所述第二导电图案电连接。

35.第三方面,本公开实施例提供一种显示装置,包括上述的阵列基板。

附图说明

36.图1为的一种示例性的阵列基板制备方法的流程图;

37.图2a

‑

图2h为图1所示制备方法各步骤对应的阵列基板结构示意图;

38.图3为本公开实施例提供一种阵列基板的制备方法的流程图;

39.图4为本公开实施例提供另一种阵列基板的制备方法的流程图;

40.图5a

‑

图5i为图4所示制备方法各步骤对应的阵列基板结构示意图;

41.图6为本公开实施例提供的一种阵列基板的结构示意图;

42.图7为一种移位寄存器的电路示意图;

43.图8为本公开实施提供的一种显示面板的截面图。

具体实施方式

44.为使本领域技术人员更好地理解本公开的技术方案,下面结合附图和具体 实施

方式对本公开作进一步详细描述。

45.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领 域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二

”ꢀ

以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的 组成部分。同样,“一个”、“一”或者“该”等类似词语也不表示数量限制,而是表 示存在至少一个。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者 物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或 者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而 是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等 仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关 系也可能相应地改变。

46.需要说明的是,“构图工艺”是指形成具有特定的图形的结构的步骤,其 可为光刻工艺,光刻工艺包括形成材料层、涂布光刻胶、曝光、显影、刻蚀、 光刻胶剥离等步骤中的一步或多步;当然,“构图工艺”也可为压印工艺、喷 墨打印工艺等其它工艺。

47.图1为一种示例性的阵列基板制备方法的流程图,图2a

‑

图2h为图1所示 制备方法各步骤对应的阵列基板结构示意图,如图1

‑

图2h所示,阵列基板的制 备方法包括:

48.s101、如图2a,在基底10上形成有机绝缘层11。

49.s102、如图2b,在有机绝缘层11上形成第一导电薄膜层12,在第一导电 薄膜层12上形成第二导电薄膜层13。

50.s103、如图2c,在第二导电薄膜层13上涂覆光刻胶层,对光刻胶层进行曝 光和显影,得到第一光刻胶保留部分14,然后通过构图工艺形成第一导电图形 131。

51.s104、如图2d,对第一光刻胶保留部分14进行灰化处理,得到第二光刻胶 保留部分141。

52.s105、如图2e,以第一导电图形131为掩膜对第一导电薄膜层12进行刻蚀, 得到第二导电图形121。

53.s106、如图2f,以第一光刻胶保留部分141为掩膜对第一导电图形131进 行刻蚀,得到第三导电图形132。

54.s107、如图2g

‑

2h,在第三导电图形132背离基底10的一侧形成层间绝缘 层15,通过构图工艺在层间绝缘层15上形成过孔,在层间绝缘层15背离基底10 的一侧形成第三导电薄膜层16。

55.在本实施例中,如图2e

‑

2d所示,对第一光刻胶保留部分14进行灰化处理, 得到第二光刻胶保留部分141,在对光刻胶进行灰化处理时,会氧化未被光刻胶 覆盖的第一导电图形131,从而使第一导电图形131的致密性下降,从而在刻蚀 第一导电薄膜层12时(如图2e),刻蚀液会通过第一导电图形13渗透到第一 导电图形131下方的第一导电薄膜层12,进而使形成的第二导电图形121出现 孔洞g(如图2f)。

56.如图2g

‑

2h,由于第二导电图形121出现孔洞g,因此在层间绝缘层15形 成过孔的过程中,刻蚀液会通过第二导电图形121的孔洞g进入到有机绝缘层 11,从而将有机绝缘层11刻蚀,进而在形成第三导电薄膜层16过程中,第三 导电薄膜层16会出现断线不良,影响了第三导电薄膜层16与第二导电图形121 的搭接。

57.第一方面,如图3所示,本公开实施例提供一种阵列基板的制备方法,包 括:

58.s303、在基底上形成第一导电层。

59.s304、在第一导电层背离基底的一侧形成第二导电层。

60.s305、在第二导电层上涂覆光刻胶层,对光刻胶层进行曝光和显影,得到 光刻胶的第一保留部分。

61.s306、通过构图工艺形成第一导电图案,以第一导电图案作为掩膜对第一 导电层进行刻蚀,得到第二导电图案;

62.s307、对光刻胶的第一保留部分进行灰化处理,得到光刻胶的第二保留部 分;

63.s308、以光刻胶的第二保留部分作为掩膜,对第一导电图案进行刻蚀,得 到第三导电图案;其中,第二导电图案在基底上的正投影覆盖第三导电图案在 基底上的正投影。

64.在本实施例中,由于首先对第一导电层进行刻蚀,然后对第一导电图案上 的光刻胶的第一保留部分进行灰化处理,得到光刻胶的第二保留部分,最后以 光刻胶的第二保留部分作为掩膜,对第一导电图案进行刻蚀,得到第三导电图 案,因此,第三导电图案下的第二导电图案上不会出现贯穿其的孔洞,从而保 证了与其搭接的导电层不会出现断线不良。

65.在一些实施例中,在基底上形成第一导电层之前还包括:在基底上形成第 一绝缘层。在第一绝缘层背离基底的一侧形成第二绝缘层。并且,在基底上形 成第一导电层,具体为:在第二绝缘层背离基底的一侧形成第一导电层。

66.需要说明的是,第二绝缘层与基底之间还可以设置多个绝缘层,或者不设 置绝缘层,具体情况可以根据需要进行设置,在此不做具体限定。

67.下面以在基底上依次设置第一绝缘层和第二绝缘层为例进行说明,如图4

‑ꢀ

图5i所示,本公开实施提供的另一种阵列基板的制备方法包括:

68.s401、在基底上形成第一绝缘层。

69.s402、在第一绝缘层背离基底的一侧形成第二绝缘层。

70.具体的,如图5a,在该步骤中可采用热生长、常压化学气相沉积、低压化 学气相沉积、等离子体辅助化学气相淀积、溅射等制备方法在基底41的一侧依 次形成第一绝缘层42和第二绝缘层43。

71.第一绝缘层42和第二绝缘层43的材料可以根据需要进行选择,在此不做 具体限定,例如,第一绝缘层42和第二绝缘层43均采用无机材料,或者第一 绝缘层42和第二绝缘层43均采用有机材料,本实施例是以第一绝缘层42采用 有机材料,第二绝缘层43采用无机材料为例进行说明。无机材料可以为硅的氧 化物(siox)、硅的氮化物(sinx)、铪的氧化物(hfox)、硅的氮氧化物(sion)、铝 的氧化物(alox)等。

72.s403、在第二绝缘层43背离基底41的一侧形成第一导电层44。

73.具体的,如图5b所示,在该步骤中,可采用溅射方式、热蒸发方式、等离 子体增强化学气相沉积方式、低压化学气相沉积方式、大气压化学气相沉积方 式或电子回旋谐振化学气相沉积方式形成第一导电层金属薄膜。第一导电层44 的材料采用透明金属氧化物、钼(mo)、钼铌合金(monb)、铝(al)、铝钕合金(alnd)、 钛(ti)和铜(cu)中的一种或它们中多种材料形成的单层或多层复合叠层,优选为 氧化铟锡(ito)。

74.s404、在第一导电层44背离基底41的一侧形成第二导电层45。

75.具体的,如图5b所示,在该步骤中,可采用溅射方式、热蒸发方式、等离 子体增强化学气相沉积方式、低压化学气相沉积方式、大气压化学气相沉积方 式或电子回旋谐振化

学气相沉积方式形成第二导电层金属薄膜。第二导电层45 的材料采用铜(cu)、钼(mo)、钼铌合金(monb)、铝(al)、铝钕合金(alnd)、 钛(ti)和铜(cu)中的一种或它们中多种材料形成的单层或多层复合叠层,优选为 铜(cu)。

76.s405、在第二导电层45上涂覆光刻胶层,对光刻胶层进行曝光和显影,得 到光刻胶的第一保留部分461。

77.具体的,如图5c所示,在该步骤中,在第二导电层45上涂覆光刻胶层, 光刻胶的涂覆可以采用旋涂、刮涂或者辊涂等方式。利用掩膜版对光刻胶层进 行曝光显影,去掉光刻胶层的去除部分,得到光刻胶的第一保留部分461。

78.s406、通过构图工艺形成第一导电图案451,以第一导电图案451作为掩膜 对第一导电层44进行刻蚀,得到第二导电图案441。

79.具体地,如图5c

‑

5d所示,在该步骤中,以光刻胶的第一保留部分461作为 掩膜对第二导电层45进行刻蚀得到第一导电图案451。然后以第一导电图案451 作为掩膜对第一导电层44进行刻蚀,得到第二导电图案441。刻蚀可采用干法 刻蚀或湿法刻蚀,本实施例是以湿法刻蚀为例进行说明的。

80.s407、对光刻胶的第一保留部分461进行灰化处理,得到光刻胶的第二保 留部分462。

81.具体的,如图5e所示,在该步骤中,对光刻胶的第一保留部分461进行灰 化处理,得到光刻胶的第二保留部分462。

82.s408、以光刻胶的第二保留部分462作为掩膜,对第一导电图案451进行 刻蚀,得到第三导电图案452。

83.具体的,如图5f所示,在该步骤中,以光刻胶的第二保留部分462作为掩 膜,对第一导电图案451进行刻蚀,得到第三导电图案452。其中,第二导电图 案441在基底41上的正投影覆盖第三导电图案452在基底41上的正投影。

84.在本实施例中,由于首先对第一导电层44进行刻蚀,然后对第一导电图案 451上的光刻胶的第一保留部分461进行灰化处理,得到光刻胶的第二保留部分 162,最后以光刻胶的第二保留462部分作为掩膜,对第一导电图案451进行刻 蚀,得到第三导电图案452,因此,第三导电图案452下的第二导电图案441上 不会出现贯穿其的孔洞,从而保证了与第二导电图案441搭接的导电层不会出 现断线不良。同时,由于在第一绝缘层42上设置第二绝缘层43,因此,可以在 对第一导电层44进行刻蚀的过程中,阻挡刻蚀液与第一绝缘层42相接触,从 而避免了刻蚀液对第一绝缘层42的损伤。

85.在一些实施例中,如图4

‑

图5i所示,s408、在以光刻胶的第二保留部分462 作为掩膜,对第一导电图案451进行刻蚀,得到第三导电图案452之后,还包 括:

86.s409、在第三导电图案452背离基底41的一侧形成第三绝缘层47。

87.具体的,如图5g所示,在该步骤中采用热生长、常压化学气相沉积、低压 化学气相沉积、等离子体辅助化学气相淀积、溅射等制备方法在第三导电图案 452背离基底41的一侧形成第三绝缘层47。第三绝缘层47的材料可以根据需 要进行选择,在此不做具体限定,例如可以为硅的氧化物(siox)、硅的氮化物 (sinx)、铪的氧化物(hfox)、硅的氮氧化物(sion)、铝的氧化物(alox)等。

88.s410、通过构图工艺在第三绝缘层47上形成过孔,过孔出露出部分第二导 电图案

441。

89.具体的,如图5h所示,在第三绝缘层17上涂覆一层光刻胶。光刻胶的涂 覆可以采用旋涂、刮涂或者辊涂等方式。对涂覆在第三绝缘层47上的光刻胶进 行曝光和显影以形成光刻胶图案。利用光刻胶图案作为刻蚀掩模,通过刻蚀工 艺形成贯穿第三绝缘层47过孔,然后去除光刻胶。

90.s411、在第三绝缘层47背离基底的一侧形成第三电极层,通过构图工艺形 成第四导电图案48,第四导电图案48通过过孔与第二导电图案441电连接。

91.具体的,如图5i所示,在第三绝缘层47背离基底41的一侧形成第三电极 层(图中未示出),通过构图工艺形成第四导电图案48,第四导电图案48通过 过孔与第二导电图案441电连接。其中第三电极层的形成方法与第一电极层44 和第二电极层45的形成方法相同,在此不再赘述。

92.在本实施例中,由于首先对第一导电层44进行刻蚀,然后对第一导电图案 451上的光刻胶的第一保留部分461进行灰化处理,得到光刻胶的第二保留部分 162,最后以光刻胶的第二保留462部分作为掩膜,对第一导电图案451进行刻 蚀,得到第三导电图案452,因此,第三导电图案452下的第二导电图案441上 不会出现贯穿其的孔洞,从而保证了与第二导电图案441搭接的导电层不会出 现断线不良。同时,由于在第一绝缘层42上设置第二绝缘层43,因此,可以在 对第一导电层44进行刻蚀的过程中,阻挡刻蚀液与第一绝缘层42相接触,从 而避免了刻蚀液对第一绝缘层42的损伤。

93.在一些实施例中,对第一导电层44进行刻蚀所用的刻蚀液为第一刻蚀液, 对第二导电图案441进行刻蚀所用的刻蚀液为第二刻蚀液,其中,第一刻蚀液 与第二刻蚀液不同,即刻蚀第二导电图案441所用的第二刻蚀液不能够对第一 导电层44进行刻蚀。如图5e所示,对光刻胶的第一保留部分461进行灰化处 理过程中,第一导电图案451被氧化,第一导电图案451的致密性下降,在本 实施例中,由于第一刻蚀液与第二刻蚀液不同,因此即使第一导电图案451的 刻蚀液会通过第一导电图案451渗透到第一导电图案451下方的第一导电层44, 第一导电层44也不会出现孔洞。

94.在一些实施例中,图6为本公开实施例提供的一种阵列基板的结构示意图, 如图6所示,阵列基板包括显示区a1和围绕显示区的周边区a2,周边区a2 内设置有栅极驱动电路1102,栅极驱动电路1102包括多个移位寄存器1103。

95.图7为一种移位寄存器的电路示意图,如图7所示,该移位寄存器1103包 括:输入电路1、输出电路2、帧重置电路3、下拉控制电路4、下拉电路5、第 一降噪电路6。其中,输入电路1、输出输出电路2、下拉电路5之间的连接节 点为上拉节点pu;下拉控制电路4和下拉电路5之间的节点为下拉节点pd。 输入电路1被配置为对上拉节点pu进行充电和复位;输出电路2被配置响应于 上拉节点pu的电位,并将时钟信号通过信号输出端output输出;帧重置电路3 被配置为在消隐阶段,响应于重置信号,通过低电平信号对上拉节点pu和信号 输出端output的输出进行重置;下拉控制电路4被配置为响应于第一电源电压, 并通过第一电源电压控制下拉控下拉节点pd电位;下拉电路5配置为响应于上 拉节点pu,并通过低电平信号对下拉节点pd的电位进行下拉;第一降噪单路 被配置为响应于下拉节点pd的电位,对上拉节点pu和信号输出端output的输 出进行降噪。

96.参照图7,该移位寄存器中的输出电路2可以包括第三晶体管m3和存储电 容c1;其

中,该第三晶体管m3的源极连接时钟信号端clk,第三晶体管m3 的漏极连接信号输出端output,第三晶体管m3的栅极连接上拉节点pu;存储 电容c1的第一极板连接上拉节点pu,存储电容c1的第二极板连接信号输出端 output。在该种情况下,当上拉节点pu被充电至高电平信号时,存储电容c1 对高电平信号进行存储,同时第三晶体管m3打开,时钟信号端clk所输入的 时钟信号通过信号输出进行输出。

97.参照图7,该移位寄存器中的帧重置电路3可以包括第四晶体管m4和第七 晶体管m7;其中,第四晶体管m4的源极连接信号输出端output,第四晶体管 m4的漏极连接低电平信号端vgl,第四晶体管m4的栅极连接重置信号端trst; 第七晶体管m7的源极连接上拉节点pu,第七晶体管m7的漏极连接低电平信 号端vgl,第七晶体管m7的栅极连接重置信号端trst。在该种情况下,当显 示一帧或者多帧画面的显示阶段结束,进入消隐阶段时,给重置信号端trst写 入高电平信号,此时第四晶体管m4和第七晶体管m7打开,低电平信号端vgl 的低电平信号通过第四晶体管m4对信号输出端output进行重置,通过第七晶 体管m7对上拉节点pu进行重置。在移位寄存器中设置帧重置电路3,可以有 效的避免在一帧画面显示中上拉节点pu和信号输出端output的噪声传递到下 一帧显示画面。

98.参照图7,该移位寄存器中的下拉控制电路4可以包括第五晶体管m5和第 九晶体管m9;其中,第五晶体管m5的源极连接第一电源电压端vdd,第五 晶体管m5的漏极连接下拉节点pd,第五晶体管m5的栅极连接第九晶体管 m9的漏极;第九晶体管m9的源极和栅极连接第一电源电压端vdd。在该种 情况下,第一电源电压端vdd的第一电源电压控制第五晶体管m5和第九晶体 管m9打开,并上拉下拉节点pd的电位。

99.参照图7,该移位寄存器中的下拉电路5可以包括第六晶体管m6和第八晶 体管m8;其中,第六晶体管m6的源极下拉节点pd,第六晶体管m6的漏极 连接低电平信号端vgl,第六晶体管m6的栅极连接上拉节点pu;第八晶体管 m8的源极连接下拉控制电路4,第八晶体管m8的漏极连接低电平信号端vgl, 第八晶体管m8的栅极连接上拉节点pu。在该种情况下,当上拉节点pu的电 位为高电平信号时,第六晶体管m6和第八晶体管m8均被打开,低电平信号端 vgl的低电平信号通过第六晶体管m6对下拉节点pd的电位进行下拉,通过 第八晶体管m8对下拉控制电路4的电位进行下拉。

100.参照图7,该移位寄存器中的第一降噪电路6可以包括第十晶体管m10和 第十一晶体管m11;其中,第十晶体管m10的源极连接上拉节点pu,第十晶 体管m10的漏极连接低电平信号端vgl,第十晶体管m10的栅极连接下拉节 点pd;第十一晶体管m11的源极连接信号输出端output,第十一晶体管m11 的漏极连接低电平信号端vgl,第十一晶体管m11的栅极连接下拉节点pd。 在该种情况下,当下拉节点pd为高电平时,第十晶体管m10和第十一晶体管 m11打开,低电平信号端vgl的低电平信号通过第十晶体管m10对上拉节点 pu的输出进行降噪,通过第十晶体管m10对信号输出端output的输出进行降 噪。

101.如图6

‑

7所示,移位寄存器1103中的输出晶体管m3的漏极连接信号输出 端output,信号输出端output通过信号输出线1104与栅线gl连接。

102.如图5i所示的实施例中,第三导电图案452可为栅线gl,第二导电图案 441和第四导电图案48共同构成信号输出线1104。

103.在本实施例中,在本实施例中,由于首先对第一导电层44进行刻蚀,然后 对第一导电图案451上的光刻胶的第一保留部分461进行灰化处理,得到光刻 胶的第二保留部分

162,最后以光刻胶的第二保留462部分作为掩膜,对第一导 电图案451进行刻蚀,得到第三导电图案452,因此,第三导电图案452下的第 二导电图案441上不会出现贯穿其的孔洞,从而保证了与第二导电图案441搭 接的导电层不会出现断线不良。同时,由于在第一绝缘层42上设置第二绝缘层 43,因此,可以在对第一导电层44进行刻蚀的过程中,阻挡刻蚀液与第一绝缘 层42相接触,从而避免了刻蚀液对第一绝缘层42的损伤。

104.在一些实施例中,图8为本公开实施提供的一种显示面板的截面图,如图8 所示,液晶显示面板的主要结构包括阵列基板81、对盒基板82以及设置在阵列 基板81和对盒基板82之间的液晶层83。

105.如图8所示,对盒基板82包括设置在第二基底820上的彩色滤光层821, 在此情况下,对盒基板82也可以称为彩膜基板(color filter,简称cf)。其中, 彩色滤光层821至少包括设置在每个亚像素p的红色光阻单元、绿色光阻单元 或蓝色光阻单元。对盒基板82还包括设置在第二基底820上的黑矩阵822,黑 矩阵822用于将红色光阻单元、绿色光阻单元以及蓝色光阻单元间隔开。

106.阵列基板81的每个亚像素p包括有位于第一基底810上的薄膜晶体管811 和像素电极812。在一些实施例中,阵列基板81还包括设置在第一基底810上 的公共电极813。像素电极812和公共电极813可以设置在同一层,在此情况下, 像素电极812和公共电极813均包括多个条状子电极的梳齿结构。本公开实施 例是以像素电极812和公共电极813设置在不同层为例进行说明的,如图8所 示,像素电极812和公共电极813之间设置有第三绝缘层814。公共电极813与 薄膜晶体管811之间还设置有第二绝缘层815。阵列基板81还包括设置在薄膜 晶体管811和像素电极812远离第一基底810一侧的平坦层816。

107.在一些实施例中,本公开实施提供的阵列基板的制备方法,在形成第三导 电图案452的同时,还包括形成有栅线gl和薄膜晶体管的栅极的步骤。即在本 实施例中,可通过一次构图工艺同时形成第三导电图案452、栅线gl和薄膜晶 体管的栅极,从而减少了生产步骤,节约了制造成本。

108.在一些实施例中,本公开实施提供的阵列基板的制备方法,在形成第二导 电图案441的同时,还可形成有公共电极。即在本实施例中,可通过一次构图 工艺同时形成第二导电图案441和公共电极313,从而减少了生产步骤,节约了 制造成本。

109.在一些实施例中,本公开实施提供的阵列基板的制备方法,在形成第四导 电图案48的同时,还可以形成有像素电极312。即在本实施例中,可通过一次 构图工艺同时形成第四导电图案48和像素电极312,从而减少了生产步骤,节 约了制造成本。

110.第二方面,本公开实施例提供一种阵列基板,如图5i所示,包括:基底41、 第一绝缘层42、第二绝缘层43、第二导电图案441、第三导电图案452、第三 绝缘层47和第四导电图案48。第一绝缘层42设置在基底41上;第二绝缘层 43设置在第一绝缘层42背离基底41的一侧;第二导电图案441设置在第二绝 缘层43背离基底41的一侧;第三导电图案452设置在第一导电图案441背离 基底41的一侧,第二导电图案441在基底41上的正投影覆盖第三导电图案452 在基底41上的正投影;第三绝缘层47设置在第三导电图案452背离基底41的 一侧,第三绝缘层47具有过孔;第四导电图案48设置在第三导电图案452背 离基底41的一侧,且第四导电图案48通过过孔与第二导电图案441电连接。

111.在本实施例中,第三导电图案452下的第二导电图案441上不会出现贯穿 其的孔

洞,从而保证了与第二导电图案441搭接的导电层不会出现断线不良。 同时,由于在第一绝缘层42上设置第二绝缘层43,因此,可以在对第一导电层 44进行刻蚀的过程中,阻挡刻蚀液与第一绝缘层42相接触,从而避免了刻蚀液 对第一绝缘层42的损伤。

112.第三方面,本公开实施例提供一种显示装置,对于显示装置的类型不进行 限定。该显示装置可以是液晶显示装置(liquid crystal display,简称lcd)、电 致发光显示装置、led(light

‑

emitting diode,发光二极管)点阵装置、 micro

‑

led(micro light

‑

emittingdiode,简称微型发光二极管)显示装置中的一种。 本发明实施例提供的显示装置可以为显示器、电视、数码相机、手机、平板电 脑、电子相框、导航仪等任何具有显示功能的产品或者部件,本发明实施例对 此不作限定。

113.可以理解的是,以上实施方式仅仅是为了说明本公开的原理而采用的示例 性实施方式,然而本公开并不局限于此。对于本领域内的普通技术人员而言, 在不脱离本公开的精神和实质的情况下,可以做出各种变型和改进,这些变型 和改进也视为本公开的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1