一种沟槽形貌监控方法、结构器件与流程

1.本发明属于器件沟槽刻蚀工艺技术领域,尤其是涉及一种用于监控沟槽侧壁和拐角形貌的监控方法以及易于沟槽形貌监控的结构器件。

背景技术:

2.沟槽结构器件是很多器件的发展方向也逐步成为主流,如mos、sgt、igbt、trench sbd等,且沟槽刻蚀是器件加工的关键工艺。现有沟槽刻蚀工艺常采用光学或者台阶仪的方式监控沟槽的宽度和深度,定期对刻蚀后的晶圆进行裂片,通过扫描电子显微镜等对沟槽剖面进行测量;这种工艺仅是在产品加工完成后的电性能测试时才能确认沟槽的侧壁和拐角形貌有无问题;而且裂片后sem监控沟槽形貌仅是局部的一个点的形貌确认,无法做大面积的芯片监控;同时由于样品制备和sem监控都需要专用设备,测试时间也相对较长,导致无法对复杂的沟槽结构样品进行监控,而且无法完整地监控沟槽刻蚀的全部关键点,其仅对沟槽刻蚀的宽度、深度进行监控,而对于侧壁和拐角的形貌未有有效的监控。而沟槽的侧壁和拐角的形貌严重影响产品质量,由于侧壁和拐角监控的延迟导致质量问题的滞后发现,直接导致产品的报废,不仅生产效率低,而且产品质量不稳定。

技术实现要素:

3.本发明提供一种沟槽形貌监控方法以及易于沟槽形貌监控的结构器件,解决了现有技术中无法监控沟槽侧壁和拐角形貌的技术问题。

4.为解决上述技术问题,本发明采用的技术方案是:

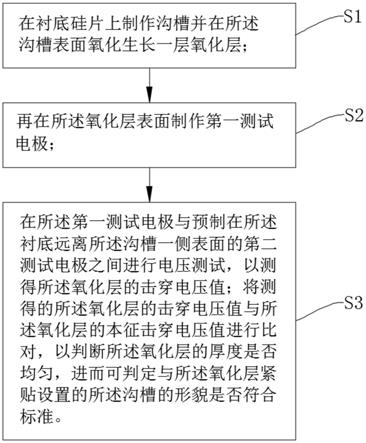

5.一种沟槽形貌监控方法,步骤包括:

6.在衬底硅片上制作沟槽并在所述沟槽表面氧化生长一层氧化层;

7.再在所述氧化层表面制作第一测试电极;

8.在所述第一测试电极与预制在所述衬底远离所述沟槽一侧表面的第二测试电极之间进行电压测试,以测得所述氧化层的击穿电压值;

9.将测得的所述氧化层的击穿电压值与所述氧化层的本征击穿电压值进行比对,以判断所述氧化层的厚度是否均匀,进而可判定与所述氧化层紧贴设置的所述沟槽的形貌是否符合标准。

10.进一步的,所述氧化层厚度为50

‑

5000a;且当测得的所述氧化层的击穿电压值不小于其本征击穿电压值的80

‑

90%时,表示所述氧化层的厚度均匀。

11.进一步的,所述在衬底硅片上制作沟槽并在所述沟槽表面氧化生长一层氧化层,步骤包括:

12.在所述衬底正面沉积一单层或多层的掩膜层,并使所述掩膜层覆盖所述衬底全面设置,且所述掩膜层厚度为1000

‑

10000a;

13.在所述掩膜层远离所述衬底一侧涂覆一层与所述掩膜层同面积的胶层一;

14.在所述胶层一中依次进行曝光、显影,以获得光刻图形;

15.基于所述光刻图形在所述衬底上进行刻蚀获得若干所述沟槽;

16.再在所述沟槽内表面氧化生长一层所述氧化层;

17.其中,所述沟槽宽度为0.2

‑

10um,且其深度为0.2

‑

400um。

18.进一步的,在刻蚀所述沟槽之前,还包括:

19.先在所述胶层一上沿其厚度方向进行刻蚀,以使所述胶层一中所述沟槽所对应的位置区域被刻蚀掉以获得所述光刻图形;

20.基于所述胶层一中的光刻位置,在所述掩膜层上对所述沟槽所在位置区域并沿所述掩膜层厚度进行刻蚀至所述衬底上表面上;

21.再去除所述掩膜层上的所有所述胶层一。

22.进一步的,对所述掩膜层中所述沟槽所在位置区域的刻蚀是采用干法刻蚀工艺;去除剩余所有所述胶层一是采用干法去除工艺或湿法去除工艺。

23.进一步的,所述再在所述氧化层表面制作第一测试电极的步骤包括:

24.在所述掩膜层上沉积一层厚度为500

‑

60000a且由多晶硅或金属薄膜形成的电极层,并使所述电极层填充至具有所述氧化层的所述沟槽内;

25.在所述电极层上涂覆一与所述电极层同面积的胶层二,在对所述胶层二依次进行曝光、显影,以定义电极图形;

26.再基于所述电极图形,在所述电极层上进行刻蚀,获得覆盖具有所述氧化层的所述沟槽所在位置的所述第一测试电极。

27.进一步的,基于所述电极图形在所述电极层刻蚀之前,还包括:

28.对所述胶层二进行光刻,以去除具有所述氧化层的所述沟槽所在位置之外的其它区域;

29.沿所述胶层二光刻的位置,再在所述电极层上进行刻蚀,以保留所述氧化层所在位置对应的所述第一测试电极的待测试区域;

30.去除剩余所有所述胶层二。

31.进一步的,对所述电极层中的非所述沟槽所在位置区域的刻蚀是采用干法刻蚀工艺或者湿法腐蚀工艺;去除剩余所有所述胶层二是采用干法去除工艺或湿法去除工艺。

32.一种采用如上任一项所述的沟槽监控方法获得的结构器件,至少包括:

33.所述衬底;以及

34.被定义在所述衬底内的所述沟槽;

35.其中,在所述沟槽内并紧贴所述沟槽内壁设置有所述氧化层;

36.在所述衬底远离所述沟槽一侧并配设有所述第一测试电极,所述第一测试电极充满具有所述氧化层的所述沟槽并覆盖所述衬底设置。

37.进一步的,还包括:在所述衬底和所述第一测试电极之间还配置有一层介质掩膜层;

38.所述掩膜层被所述沟槽贯穿设置,且所述氧化层的上端面与所述掩膜层平齐设置;

39.其中,所述掩膜层厚度1000a

‑

10000a;

40.所述沟槽宽度为0.2

‑

10um,且其深度为0.2

‑

400um;

41.所述氧化层厚度为50

‑

5000a;

42.所述第一测试电极厚度为500

‑

60000a。

43.相比现有的sem监控沟槽剖面形貌方式的点监控,采用本发明提出的一种沟槽形貌监控方法,可对一定面积区域的沟槽进行监控,仅通过测试沟槽内氧化层的击穿电压值来判断其厚度质量情况,即可间接判断沟槽形貌情况,不仅测试结果准确且可监测效率高,再现检测率高。

44.本发明通过对测得的氧化层的击穿电压值与其本征击穿电压值进行比较,即可精准地对沟槽的侧壁和拐角形貌进行监控,从而可及时判断沟槽结构的质量好坏,提前对生产工艺进行调整。尤其是,当测得的氧化层的击穿电压值不小于其本征击穿电压值的80

‑

90%时,表示氧化层的厚度均匀,进而可知紧贴氧化层的整个沟槽的形貌是均匀且稳定的。

45.同时根据这一监控方法获得的易于沟槽形貌监控的器件结构通用性强且结构稳定,可通用于条型沟槽、交叉沟槽等复杂结构的沟槽结构器件的生产及沟槽形貌的监控,并与实际产线工艺兼容,不需要额外的设备。

附图说明

46.图1是本发明一实施例的一种沟槽形貌监控方法的流程示意图;

47.图2是本发明一实施例的测试过程中各步骤的器件结构示意图。

48.图中:

49.10、衬底

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20、掩膜层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30、胶层一

50.40、沟槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

50、氧化层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

60、电极层

51.70、胶层二

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

80、第一测试电极

具体实施方式

52.下面结合附图和具体实施例对本发明进行详细说明。

53.本实施例提出一种沟槽形貌监控方法,流程如图1所示,各步骤的器件结构如图2所示,具体地,步骤包括:

54.s1、在衬底10硅片的正面一侧制作沟槽40并在沟槽40的内侧表面上氧化生长一层氧化层50。

55.s11、在硅片衬底10的正面氧化生长掩膜层20。

56.如图2a所示,在硅片衬底10的正面氧化生长一单层或多层的掩膜层20,掩膜层20一般是氧化硅、氮化硅或其它的介质膜形成,并使掩膜层50覆盖衬底10全面设置,且掩膜层20的厚度为1000

‑

10000a;掩膜层20的设置可便于对沟槽40的刻蚀。

57.s12、在掩膜层20的上方涂覆一层胶层一30,并获得光刻后的图形。

58.如图2b所示,在掩膜层20远离衬底10的一侧涂覆一层与掩膜层20同面积的胶层一30。

59.如图2c所示,再在胶层一30中依次进行曝光、显影,目的是在胶层一30上沿其厚度方向进行刻蚀,以使胶层一30中沟槽40所对应的位置区域被刻蚀掉,以获得留下需要的光刻图形,其中光刻图形是保留非沟槽40区域,将沟槽40的定义区域被光刻去掉。

60.s13、对掩膜层20进行刻蚀。

61.如图2d所示,基于胶层一30中的光刻位置,采用干法刻蚀工艺再在掩膜层20上对

沟槽40所在位置区域并沿掩膜层20厚度进行刻蚀,刻蚀深度贯穿掩膜层20的厚度至衬底10的上表面上,也即是保留非沟槽40所在区域,暴露出需要刻蚀沟槽40的区域,把沟槽40所在位置对应的掩膜层20的区域全部刻蚀去掉,刻蚀至硅片衬底10的上表面上,以便于下一步对衬底10上的沟槽40的制作。

62.s14、去除胶层一30。

63.如图2e所示,采用干法去除工艺或湿法去除工艺对掩膜层20上的所有胶层一30进行去除,仅保留带有刻蚀后的掩膜层20的衬底10。

64.s15、沟槽40的刻蚀。

65.如图2f所示,基于掩膜层20中的光刻图形的阻挡,保护不需要刻蚀的区域,需要刻蚀的区域用干法刻蚀的方式在衬底10上进行刻蚀,以获得若干深度垂直于衬底10的厚度方向且并排设置的沟槽40。其中,沟槽40的宽度为0.2

‑

10um,且其深度为0.2

‑

400um。沟槽40的深度和宽度取决于器件的结构设计,在此不具体限制。

66.s16、沟槽40氧化。

67.如图2g所示,在沟槽40内的硅表面上进行氧化,以生长一层氧化层50,也就是形成一层紧贴沟槽40内壁的氧化层50,氧化工艺为现有常规氧化工艺,氧化层50的厚度为50

‑

5000a,优选地,当氧化层50的厚度为50a、100a、350a、500a、850a、1000a和5000a时。氧化层50的厚度均匀程度完全能反映沟槽40的全貌,不仅可体现沟槽40的宽度和深度,而且还可体现侧壁和拐角的形貌情况,且氧化层50的上端面完全与掩膜层20的上端面平齐设置,也即是氧化层50的深度是沟槽40的深度和掩膜层20的厚度之和。

68.s2、再在氧化层50的表面制作第一测试电极80。

69.s21、沉积电极层60。

70.如图2h所示,在掩膜层20上沉积一层厚度为500

‑

60000a且由多晶硅或金属薄膜形成的电极层60,并使电极层60填充至具有氧化层50的沟槽40内,且使电极层60均匀沉积在掩膜层20的表面上,厚度可根据生产线常规工艺选择,在此不具体要求。

71.s22、涂覆、光刻胶层二70。

72.如图2i所示,在电极层60的上端面一侧涂覆一层与电极层60同面积的胶层二70。

73.如图2j所示,对胶层二70进行光刻,以去除氧化层50所在位置之外的其它区域,即是在胶层二70中依次进行曝光、显影,以定义电极图形,也就是留下需要测试的区域,这个测试的区域形状根据沟槽40所在位置区域而定。即是在胶层一30上沿其厚度方向进行光刻,以使胶层二70中光刻掉非测试区域,即非氧化层50所对应的位置区域,以获得留下需要的光刻电极图形,其中电极图形是保留具有氧化层50的测试区域,将氧化层50所在位置之外的其它非测试区域均光刻去掉。

74.s23、刻蚀电极层60。

75.如图2k所示,沿胶层二70光刻的位置,再在电极层60上进行刻蚀,即刻蚀掉不需要的电极部分,以保留具有氧化层50的沟槽40所在位置对应的第一测试电极80的测试区域;对电极层60中的非沟槽40位置区域即非测试区域的刻蚀是采用干法刻蚀工艺或者湿法腐蚀工艺。

76.再基于电极图形,在电极层60上进行刻蚀,获得覆盖具有氧化层50的沟槽40所在位置的第一测试电极80。

77.s24、去除胶层二70。

78.如图2l所示,采用干法去除工艺或湿法去除工艺将剩余所有胶层二70去除,最终获得测试时的沟槽结构器件。

79.s3、在第一测试电极80与预制在衬底10远离沟槽40一侧表面的第二测试电极之间进行电压测试,以测得氧化层50的击穿电压值。

80.制作完第一测试电极80后,再在衬底10的背面制备背面电极,即背面第二测试电极(图省略),采用常用的电压监控方法在第一测试电极80和第二测试电极之间进行电压测试,也即是测试衬底10和多晶的氧化层50之间的耐压能力,获得氧化层50的击穿电压值;将测得的氧化层50的击穿电压值与氧化层50的本征击穿电压值进行比对,以判断氧化层50的厚度是否均匀,进而可判定与氧化层50紧贴设置的沟槽40被刻蚀后的形貌是否存在损伤和形貌异常,是否符合标准。

81.氧化层50的质量主要与沟槽40的形貌相关,由于氧化是覆盖整个沟槽40的内壁,包含其侧壁、底部以及侧壁和底部的拐角处,若沟槽40的侧壁和拐角处有尖刺或者凹坑会导致氧化层50的厚度不均匀,这样会影响氧化层50的厚度,此时氧化层50的击穿电压会降低,从而使其与本征击穿电压的比值会减小,当比值低于80%时,可以间接的判断沟槽40的形貌是有问题的,也即是其侧壁和拐角出现异常,即可判断沟槽40的整体形貌有问题。

82.其中,电压值是按照氧化层50的厚度而定,在本实施例中,选用测试电压为5

‑

500v,氧化层50的厚度为50

‑

5000a。当测得的氧化层50的击穿电压值不小于其本征击穿电压值的80

‑

90%时,表示氧化层50的厚度均匀,整个刻蚀工艺稳定,刻蚀后的沟槽40的侧壁及底部拐角位置处的形貌正常。

83.取不同厚度的氧化层50和其对应的电压值,以获得的测试后的击穿电压值,并通过测得的击穿电压值与本征电压值进行相比,获得的比率值如下表1所示,从表格中可以看出,在同种工艺条件下,当氧化层50的厚度为50a、100a、350a、500a、850a、1000a和5000a时,获得的击穿电压值均大于本征击穿电压值的80%。这一结果完全与采用现有技术中的sem监控的沟槽剖面形貌获得的结果一致,表示采用这一监控方法获得的沟槽形貌结果的再现性好,且稳定性强。

84.表1不同氧化层厚度所获得的击穿电压值占本征击穿电压值的比率

[0085][0086]

采用本实施例提出的监控方法,通过对测得的氧化层50的击穿电压值与其本征击穿电压值进行比较,即可精准地对沟槽40的侧壁和拐角形貌进行监控,从而可及时判断沟槽40结构的质量好坏,提前对生产工艺进行调整。尤其是,当测得的氧化层50的击穿电压值

不小于其本征击穿电压值的80

‑

90%时,表示氧化层50的厚度均匀,进而可知紧贴氧化层50的整个沟槽40的形貌是均匀且稳定的,从而监控了沟槽40的侧壁和拐角的形貌。而且本实施例可对一定面积区域的沟槽40进行监控,仅通过测试沟槽40内氧化层50的击穿电压值来判断其厚度质量情况,即可间接判断沟槽40形貌情况,不仅测试结果准确且可监测效率高,且再现检测率高。

[0087]

一种易于沟槽形貌监控的结构器件,如图2l所示,采用如上所述的监控方法获得,至少包括:

[0088]

硅片衬底10以及被定义在衬底10内的沟槽40;其中,在沟槽40内并紧贴沟槽40内壁设置有氧化层50。

[0089]

在衬底10远离沟槽40一侧并配设有第一测试电极80,第一测试电极80充满具有氧化层50的沟槽40并覆盖衬底10设置。

[0090]

进一步的,还包括在衬底10和第一测试电极80之间还配置有一层介质掩膜层20;掩膜层20被沟槽40贯穿设置,且氧化层50的上端面与掩膜层20平齐设置。

[0091]

其中,掩膜层20的厚度1000a

‑

10000a;

[0092]

沟槽40的宽度为0.2

‑

10um,且其深度为0.2

‑

400um;

[0093]

氧化层50的厚度为50

‑

5000a;

[0094]

第一测试电极80的厚度为500

‑

60000a。

[0095]

相比现有的sem监控沟槽剖面形貌方式的点监控,采用本发明提出的一种沟槽形貌监控方法,可对一定面积区域的沟槽进行监控,仅通过测试沟槽内氧化层的击穿电压值来判断其厚度质量情况,即可间接判断沟槽形貌情况,不仅测试结果准确且可监测效率高,且再现检测率高。

[0096]

本发明通过对测得的氧化层的击穿电压值与其本征击穿电压值进行比较,即可精准地对沟槽的侧壁和拐角形貌进行监控,从而可及时判断沟槽结构的质量好坏,提前对生产工艺进行调整。尤其是,当测得的氧化层的击穿电压值不小于其本征击穿电压值的80

‑

90%时,表示氧化层的厚度均匀,进而可知紧贴氧化层的整个沟槽的形貌是均匀且稳定的。

[0097]

同时根据这一方法获得的易于沟槽形貌监控的器件结构,通用性强且结构稳定,可通用于条型沟槽、交叉沟槽等复杂结构的沟槽结构器件的沟槽形貌监控,并与实际产线工艺兼容,不需要额外的设备。

[0098]

以上对本发明的实施例进行了详细说明,所述内容仅为本发明的较佳实施例,不能被认为用于限定本发明的实施范围。凡依本发明申请范围所作的均等变化与改进等,均应仍归属于本发明的专利涵盖范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1