功率元件及其制造方法与流程

本发明涉及一种功率元件及其制造方法,特别涉及一种能够提高击穿电压(breakdown voltage)的功率元件及其制造方法。

背景技术:

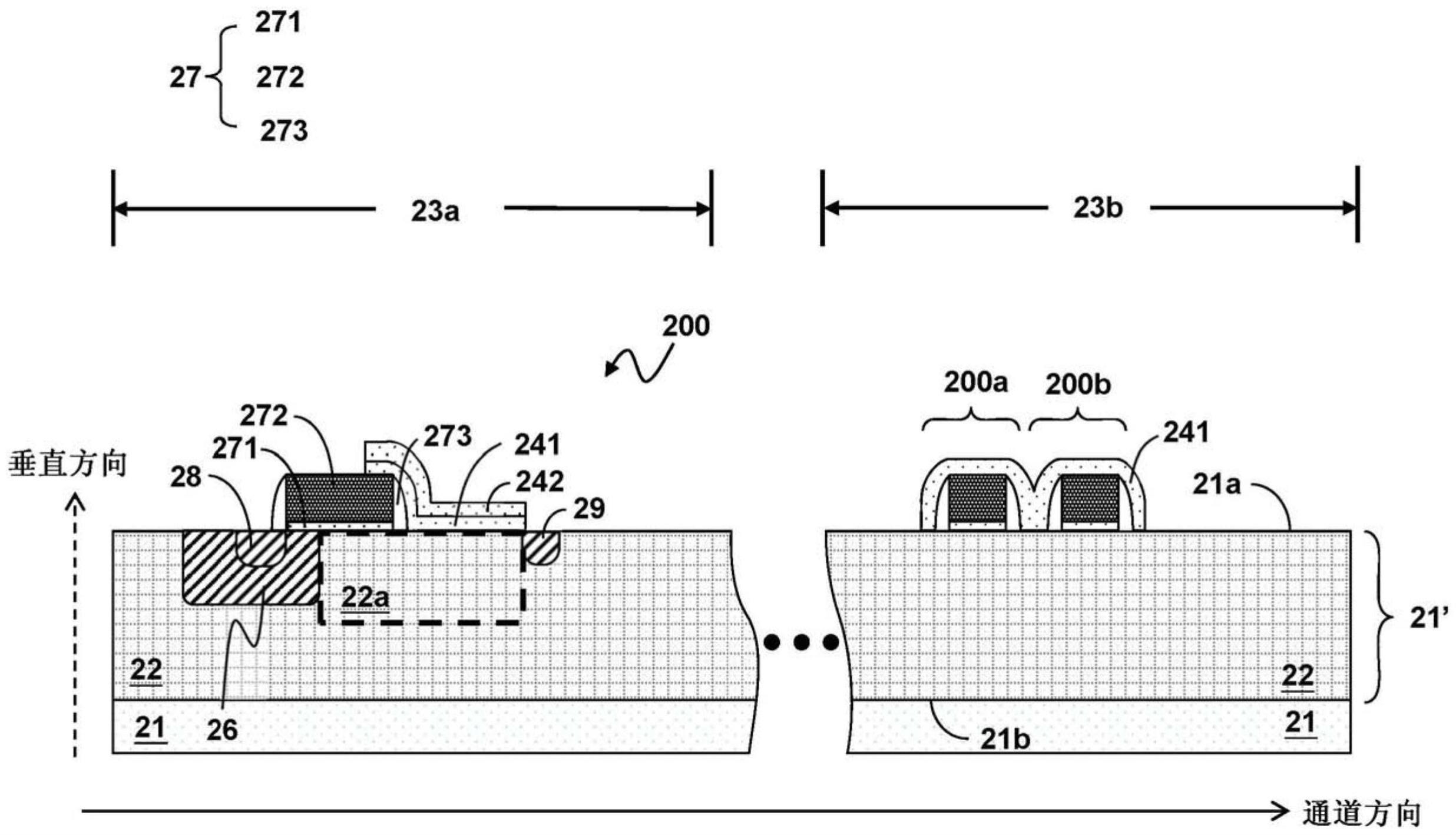

1、图1显示一种已知功率元件100与金属氧化物半导体(metal oxidesemiconductor,mos)元件100a及100b的剖视示意图。所谓的功率元件,是指于正常操作时,施加于漏极的电压高于5v。一般而言,功率元件的漏极与栅极间,具有漂移区12a(如图1中虚线框范围所示意),将漏极19与本体区16分隔,且漂移区12a的横向长度根据正常操作时所承受的操作电压而调整。如图1所示,功率元件100包含:阱区12、绝缘结构13、阻挡层14、本体区16、栅极17、源极18与漏极19。

2、其中,阱区12的导电型为n型,形成于基板11上。如图1所示,基板11区分为高压区13a与低压区13b。高压区13a与低压区13b的阱区12由同一工艺步骤形成;高压区13a与低压区13b的栅极由同一工艺步骤形成;高压区13a与低压区13b的阻挡层14由同一工艺步骤形成。基本上,施加于漏极的电压高于5v的功率元件100形成于高压区13a中,而施加于漏极的电压不高于5v的mos元件100a及100b则形成于低压区13b中。mos元件100a及100b以图1所示的栅极与阻挡层14所示意;mos元件100a及100b的其他部分如源极、漏极等在此省略。绝缘结构13为区域氧化(local oxidation of silicon,locos)结构,以定义操作区,作为功率元件100操作时主要的作用区。

3、为阻隔高压区13a与低压区13b的栅极后的金属层与部分阱区12,避免需要保护的区域与该金属层直接接触,阻挡层14会同时由同一工艺形成于高压区13a与低压区13b。在功率元件100中,阻挡层14的厚度会限制功率元件100的击穿电压,但在低压区13b中的mos元件100a与100b,因为尺寸微缩,使得mos元件100a与100b间的空隙相对于高压区13a中,功率元件与功率元件之间的空隙小;如此一来,功率元件100中的阻挡层14的厚度就受限于低压区13b中的mos元件100a与100b中的阻挡层14厚度,使得功率元件100的击穿防护电压受到限制,而限制了功率元件100的应用范围;而如果为使功率元件100的耐压(withstandvoltage)提高,可增加阻挡层14的厚度,但如此一来,mos元件100a与100b中的阻挡层14形成时,会产生残留的问题。

4、有鉴于此,本发明提出一种能够提高不导通操作时的击穿电压的功率元件及其制造方法。

技术实现思路

1、于一观点中,本发明提供一种功率元件,包含:一半导体层,形成于一基板上,该半导体层具有一上表面;一阱区,具有一第一导电型,形成于该半导体层中,且该阱区位于该上表面下并连接于该上表面;一本体区,具有一第二导电型,形成于该半导体层中,且该本体区位于该上表面下并连接于该上表面,该本体区于一通道方向上,与该阱区邻接;一栅极,形成于该上表面上,部分该本体区位于该栅极正下方并连接于该栅极,以提供该功率元件在一导通操作中的一反转电流通道,且邻接该本体区的部分该阱区位于该栅极正下方,以提供该功率元件在该导通操作中的一漂移电流通道;一源极与一漏极,具有该第一导电型,且该源极与该漏极形成于该上表面下并连接于该上表面,且该源极与该漏极分别位于该栅极的外部下方的该本体区中与远离该本体区侧的该阱区中;一第一对准金属硅化物阻挡(salicide block,sab)层,形成于该上表面上,且该第一sab层介于该栅极与该漏极之间,且部分该阱区位于并连接于该第一sab层正下方;以及一第二sab层,形成于该第一sab层正上方并连接该第一sab层。

2、于另一观点中,本发明提供一种功率元件制造方法包含:形成一半导体层于一基板上,该半导体层具有一上表面;形成一阱区于该半导体层中,且该阱区具有第一导电型,且该阱区位于该上表面下并连接于该上表面;形成一本体区于该半导体层中,且该本体区具有一第二导电型,且该本体区位于该上表面下并连接于该上表面,该本体区于一通道方向上,与该阱区邻接;形成一栅极于该上表面上,部分该本体区位于该栅极正下方并连接于该栅极,以提供该功率元件在一导通操作中的一反转电流通道,且邻接该本体区的部分该阱区位于该栅极正下方,以提供该功率元件在该导通操作中的一漂移电流通道;形成一源极与一漏极于该上表面下并连接于该上表面,且该源极与该漏极具有该第一导电型,且该源极与该漏极分别位于该栅极的外部下方的该本体区中与远离该本体区侧的该阱区中;形成一第一对准金属硅化物阻挡(salicide block,sab)层于该上表面上,且该第一sab层介于该栅极与该漏极之间,且部分该阱区位于并连接于该第一sab层正下方;以及形成一第二sab层于该第一sab层正上方并连接该第一sab层。

3、于一实施例中,该功率元件还包含一对准金属硅化物层,具有导电性,且该对准金属硅化物层形成于该第二sab层上且连接于该第二sab层,该对准金属硅化物层用以电连接于一预设电位,以缓和该功率元件操作时的电场分布。

4、于一实施例中,该功率元件是一横向扩散金属氧化物半导体(laterallydiffused metal oxide semiconductor,ldmos)元件。

5、于一实施例中,该第一sab层与该第二sab层叠加后具有一介电系数,该介电系数低于3.9。

6、于一实施例中,该第一sab层与该第二sab层叠加后具有一介电系数,该介电系数高于3.9。

7、于一实施例中,该第一sab层与该第二sab层叠加后具有一介电系数,该介电系数等于3.9。

8、于一实施例中,该基板具有一低压区与一高压区,其中该功率元件形成于该高压区;其中多个金属氧化物半导体(metal oxide semiconductor,mos)元件形成于该低压区;其中该第一sab层形成于该低压区与该高压区;其中该第二sab层形成于该高压区,且不位于该低压区。

9、于一实施例中,该第二sab层的厚度根据该功率元件的不导通击穿电压的需求而调整。

10、本发明的优点为本发明可提高不导通操作时的击穿电压。

11、以下通过具体实施例详加说明,会更容易了解本发明的目的、技术内容、特点及其所实现的效果。

技术特征:

1.一种功率元件,其特征在于,包含:

2.如权利要求1所述的功率元件,其中,还包含一对准金属硅化物层,具有导电性,且该对准金属硅化物层形成于该第二对准金属硅化物阻挡层上且连接于该第二对准金属硅化物阻挡层,该对准金属硅化物层用以电连接于一预设电位,以缓和该功率元件操作时的电场分布。

3.如权利要求1所述的功率元件,其中,该功率元件是一横向扩散金属氧化物半导体元件。

4.如权利要求1所述的功率元件,其中,该第一对准金属硅化物阻挡层与该第二对准金属硅化物阻挡层叠加后具有一介电系数,该介电系数低于3.9。

5.如权利要求1所述的功率元件,其中,该第一对准金属硅化物阻挡层与该第二对准金属硅化物阻挡层叠加后具有一介电系数,该介电系数高于3.9。

6.如权利要求1所述的功率元件,其中,该第一对准金属硅化物阻挡层与该第二对准金属硅化物阻挡层叠加后具有一介电系数,该介电系数等于3.9。

7.如权利要求1所述的功率元件,其中,该基板具有一低压区与一高压区,其中该功率元件形成于该高压区;

8.如权利要求7所述的功率元件,其中,该第二对准金属硅化物阻挡层的厚度根据该功率元件的不导通击穿电压的需求而调整。

9.一种功率元件制造方法,其特征在于,包含:

10.如权利要求9所述的功率元件制造方法,其中,还包含:形成一对准金属硅化物层于该第二对准金属硅化物阻挡层上且连接于该第二对准金属硅化物阻挡层,该对准金属硅化物层具有导电性,且用以电连接于一预设电位,以缓和该功率元件操作时的电场分布。

11.如权利要求9所述的功率元件制造方法,其中,该功率元件是一横向扩散金属氧化物半导体元件。

12.如权利要求9所述的功率元件制造方法,其中,该第一对准金属硅化物阻挡层与该第二对准金属硅化物阻挡层叠加后具有一介电系数,该介电系数低于3.9。

13.如权利要求9所述的功率元件制造方法,其中,该第一对准金属硅化物阻挡层与该第二对准金属硅化物阻挡层叠加后具有一介电系数,该介电系数高于3.9。

14.如权利要求9所述的功率元件制造方法,其中,该第一对准金属硅化物阻挡层与该第二对准金属硅化物阻挡层叠加后具有一介电系数,该介电系数等于3.9。

15.如权利要求9所述的功率元件制造方法,其中,该基板具有一低压区与一高压区,其中该功率元件形成于该高压区;

16.如权利要求15所述的功率元件制造方法,其中,该第二对准金属硅化物阻挡层的厚度根据该功率元件的不导通击穿电压的需求而调整。

技术总结

本发明提出一种功率元件及其制造方法。功率元件包含:半导体层、阱区、本体区、栅极、源极与漏极、第一对准金属硅化物阻挡层以及第二对准金属硅化物阻挡层。其中,第一对准金属硅化物阻挡层形成于半导体层的上表面上,且介于栅极与漏极之间,且部分阱区位于并连接于第一对准金属硅化物阻挡层正下方。第二对准金属硅化物阻挡层形成于第一对准金属硅化物阻挡层正上方并连接第一对准金属硅化物阻挡层。

技术研发人员:罗国轩,黄建豪,陈巨峰,翁武得

受保护的技术使用者:立锜科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!