一种含δ掺杂势垒层的常关型氧化镓基MIS-HEMT器件及其制备方法

一种含

δ

掺杂势垒层的常关型氧化镓基mis

‑

hemt器件及其制备方法

技术领域

1.本发明属于半导体器件技术领域,尤其涉及一种含δ掺杂势垒层的常关型氧化镓基mis

‑

hemt器件及其制备方法。

背景技术:

2.当今不断增长的电力电子技术应用需求从耐压、耐高温、效率、功率以及可靠性等方面向功率半导体器件提出了更高的性能要求。以异质结界面处的二维电子气(2deg)作为导电沟道的高电子迁移率晶体管(high electron mobility transistor(hemt),又称调制掺杂场效应晶体管(modfet)或异质结场效应晶体管(hfet))由于在空间上实现了施主杂质与电子的分离,避免了电离杂质的散射,因此在器件性能上具有高电子迁移率和高载流子密度等特点。这些特点使得高电子迁移率晶体管能够很好地工作于高频高功率场合,同时也让其成为功率半导体器件中不可分割的一部分。

3.β

‑

ga2o3由于拥有较大的禁带宽度(4.9ev),较高的电子迁移率(300cm2/v

·

s),超高的击穿场强(8mv/cm),以及低成本的单晶生长技术,被认为是制备新一代耐高压、耐高温的高电子迁移率晶体管的理想材料。(β

‑

ga2o3材料的优势)高电子迁移率晶体管按工作方式划分有两种类型:常开型(耗尽型)和常关型(增强型)。在零偏置状态下,由于二维电子气的存在,高电子迁移率晶体管通常为常开型。对于常开型高电子迁移率晶体管,只有在外加负偏置条件下才能实现器件的关断,此举一方面会造成额外的功率损耗,另一方面使得驱动电路的设计更加复杂,不仅增加了设计成本,而且还会存在安全隐患。而常关型高电子迁移率晶体管可以克服以上不足,因此在实际中具有很高的应用价值。

技术实现要素:

4.本发明所要解决的技术问题是针对现有技术的不足,提供一种含δ掺杂势垒层的常关型氧化镓基mis

‑

hemt器件及其制备方法。

5.为解决上述技术问题,本发明的一种含δ掺杂势垒层的常关型氧化镓基mis

‑

hemt器件,包括衬底和层叠设置在衬底一端面上的缓冲层,其还包括:沟道层、间隔层、δ掺杂层、势垒层、源电极、漏电极、介质层和栅电极;

6.其中,所述δ掺杂层设置在间隔层远离沟道层的端面上,用于避免产生平行导电沟道。

7.作为一种可能的实施方式,进一步的,

8.所述沟道层、间隔层依序层叠设置在缓冲层远离衬底的端面上,所述源电极和漏电极分别设置在沟道层远离缓冲层的端面两侧,所述间隔层设置在源电极和漏电极之间的沟道层的端面上,所述势垒层设置在δ掺杂层远离间隔层的端面上,所述介质层一体化分割为三部分分别横跨设置在势垒层、源电极和漏电极上,且其边缘向下延伸,将势垒层、源电极、漏电极和沟道层包覆其中,所述源电极和漏电极为倒t形结构,且其倒t形结构的上端穿

出介质层并外露出介质层;所述栅电极为t形结构,且与介质层连接。

9.作为一种可能的实施方式,进一步的,

10.所述衬底层和缓冲层的宽度相同;所述沟道层的左上侧和右上侧被刻蚀以形成台面;所述沟道层台面、间隔层、δ掺杂层以及势垒层的宽度相同,且比缓冲层的宽度小;所述势垒层上侧中间位置被刻蚀以形成沟槽,且沟槽位置与势垒层左侧的距离小于右侧;所述介质层在势垒层沟槽处形成由其包围的凹槽。

11.作为一种可能的实施方式,进一步的,

12.第一盖帽层,设置在源电极与沟道层之间,其一端与沟道层远离缓冲层的端面接触,另一端与源电极接触;

13.第二盖帽层,设置在漏电极与沟道层之间,其一端与沟道层远离缓冲层的端面接触,另一端与漏电极接触;

14.所述第一盖帽层、势垒层以及第二盖帽层的上边缘对齐。

15.作为一种可能的实施方式,进一步的,

16.所述δ掺杂层包括第一δ掺杂层和第二δ掺杂层,所述间隔层包括第一间隔层和第二间隔层,所述势垒层包括第一势垒层和第二势垒层;

17.所述第一势垒层、第一δ掺杂层、第一间隔层、沟道层、第二间隔层、第二δ掺杂层和第二势垒层依序自下而上叠设在缓冲层远离衬底的端面上,且介质层设在第二势垒层跨上。

18.其中,所述衬底层、缓冲层、第一势垒层、第一δ掺杂层以及第一间隔层的宽度相同;所述沟道层、第二间隔层、第二δ掺杂层以及第二势垒层的宽度相同,且比第一间隔层宽度小。

19.一种含δ掺杂势垒层的常关型氧化镓基mis

‑

hemt器件的制备方法,包括如下步骤:

20.s01、取用预设规格衬底,对其表面进行预处理;

21.s02、在衬底一端面同质外延生长形成缓冲层;

22.s03、在缓冲层远离衬底的端面上同质外延生长沟道层,在沟道层远离缓冲层的端面两侧刻蚀台阶,使其形成两侧具有相同高低落差的台面状;

23.s04、在沟道层的台面上外延生长间隔层;

24.s05、在间隔层的端面上外延生长δ掺杂层;

25.s06、在δ掺杂层远离间隔层的端面上外延生长势垒层;

26.s07、源电极和漏电极的制备:在沟道层两侧被刻蚀的区域淀积金属层制得源电极和漏电极;或,在沟道层两侧被刻蚀的区域外延生长第一盖帽层和第二盖帽层后在其上方淀积金属层制得源电极和漏电极;

27.s08、至少在沟道层、势垒层、源电极以及漏电极上包裹厚度为3~7nm的介质层;

28.s09、在由介质层包围的凹槽处淀积两层金属形成栅电极和mis结构;

29.s10、对源电极和漏电极表面介质层进行刻蚀,再蒸发淀积源、漏电极金属焊盘形成源、漏电极,完成器件的制备。

30.作为一种可能的实施方式,进一步的,其包括如下具体步骤:

31.s01、在反应室中对半绝缘或高阻β

‑

ga2o3衬底表面进行预处理,衬底的掺杂元素种类包含mg、fe、zn、n、p中的任意一种,掺杂所采取的摩尔百分比为0.05~0.06,厚度为400~

700μm;

32.s02、在衬底层上方同质外延生长厚度为6~12μm的非故意掺杂的β

‑

ga2o3缓冲层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;

33.s03、在缓冲层上同质外延生长厚度为250~700nm的非故意掺杂的β

‑

ga2o3沟道层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种,在外延生长完毕后,对其左上侧和右上侧进行干法刻蚀以形成台面;

34.s04、在沟道层台面上方异质外延生长厚度为15~35nm的本征(alga)2o3间隔层,其al组分为0.15~0.26。外延生长的方法采用mocvd、mbe、pld以及hvpe中的一种;

35.s05、在间隔层上方生长的δ掺杂层,掺杂元素种类包含si、sn、ge中的任意一种,生长方法采用mocvd、mbe中的一种;

36.s06、在δ掺杂层上方外延生长厚度为30~50nm的(alga)2o3势垒层,其al组分为0.14~0.28,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;在势垒层外延生长完毕后,对其上侧中间靠近左边缘位置进行干法刻蚀以形成沟槽,沟槽下方剩余势垒层厚度为0~6nm;

37.s07、在沟道层左上侧和右上侧被刻蚀处上方利用电子束蒸发依次淀积厚度分别为60nm、80nm和200nm的ti、al和au三层金属以分别形成源、漏电极,再对其进行高温退火以获得良好的欧姆接触;

38.s08、沉积将沟道层、势垒层、源电极以及漏电极包裹的厚度为3~7nm的介质层,其构成材料包含al2o3、sio2、si3n4、hfo2中的任意一种;

39.s09、在由介质层包围的凹槽处利用电子束蒸发依次淀积厚度分别60nm、250nm的ni、au两层金属以形成t型栅电极和mis结构;

40.s10、对源电极和漏电极表面的介质层进行干法刻蚀以形成金属互联窗口,此时介质层被分为三部分,再通过电子束蒸发淀积源、漏电极金属焊盘,以形成倒t型的源、漏电极,完成器件的制备。

41.作为一种可能的实施方式,进一步的,其包括如下具体步骤:

42.s01、在反应室中对半绝缘或高阻β

‑

ga2o3衬底表面进行预处理,衬底的掺杂元素种类包含mg、fe、zn、n、p中的任意一种,掺杂所采取的摩尔百分比为0.05~0.06,厚度为400~700μm;

43.s02、在衬底层上方同质外延生长厚度为6~12μm的非故意掺杂的β

‑

ga2o3缓冲层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;

44.s03、在缓冲层上同质外延生长厚度为250~700nm的非故意掺杂的β

‑

ga2o3沟道层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种,在外延生长完毕后,对其左上侧和右上侧进行干法刻蚀以形成台面;

45.s04、在沟道层台面上方异质外延生长厚度为15~35nm的本征(alga)2o3间隔层,其al组分为0.15~0.26。外延生长的方法采用mocvd、mbe、pld以及hvpe中的一种;

46.s05、在间隔层上方生长的δ掺杂层,掺杂元素种类包含si、sn、ge中的任意一种,生长方法采用mocvd、mbe中的一种;

47.s06、在δ掺杂层上方外延生长厚度为30~50nm的(alga)2o3势垒层,其al组分为0.14~0.28,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;在势垒层外延生长完毕

后,对其上侧中间靠近左边缘位置进行干法刻蚀以形成沟槽,沟槽下方剩余势垒层厚度为0~6nm;

48.s07、在沟道层左上侧和右上侧被刻蚀处上方分别同质外延生长n型重掺杂的β

‑

ga2o3第一盖帽层和第二盖帽层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;掺杂元素种类包含si、sn、ge、f、cl中的任意一种,掺杂浓度为1

×

1018~5

×

1019cm

‑3,厚度为60~120nm;在第一盖帽层和第二盖帽层上方利用电子束蒸发依次淀积厚度分别为60nm、80nm和200nm的ti、al和au三层金属以分别形成源、漏电极,再对其进行高温退火以获得良好的欧姆接触;

49.s08、沉积将沟道层、第一盖帽层、源电极、势垒层、漏电极以及第二盖帽层包裹的厚度为3~7nm的介质层,其构成材料包含al2o3、sio2、si3n4、hfo2中的任意一种;

50.s09、在由介质层包围的凹槽处利用电子束蒸发依次淀积厚度分别60nm、250nm的ni、au两层金属以形成t型栅电极和mis结构;

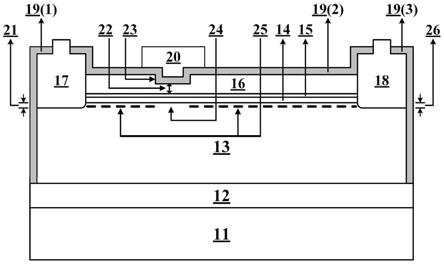

51.s10、对源电极和漏电极表面的介质层进行干法刻蚀以形成金属互联窗口,此时介质层被分为三部分,再通过电子束蒸发淀积源、漏电极金属焊盘,以形成倒t型的源、漏电极,完成器件的制备。

52.一种含δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件的制备方法,包括如下步骤:

53.s01、取用预设规格衬底,对其表面进行预处理;

54.s02、在衬底一端面同质外延生长形成缓冲层;

55.s03、在缓冲层远离衬底的端面上外延生长第一势垒层;

56.s04、在第一势垒层的端面上外延生长第一δ掺杂层;

57.s05、在第一δ掺杂层的端面上外延生长第一间隔层;

58.s06、在第一间隔层的端面上外延生长沟道层;

59.s07、在沟道层的端面上外延生长第二间隔层;

60.s08、在第二间隔层的端面上外延生长第二δ掺杂层;

61.s09、在第二δ掺杂层的端面上外延生长第二势垒层;

62.s10、在第一间隔层两侧被刻蚀的区域外延生长第一盖帽层和第二盖帽层;

63.s11、在第一盖帽层和第二盖帽层上方淀积金属层制得源电极和漏电极;

64.s12、在第一盖帽层、源电极、第二势垒层、漏电极以及第二盖帽层上包裹介质层;

65.s13、在由介质层包围的凹槽处淀积两层金属形成栅电极和mis结构;

66.s14、对源电极和漏电极表面介质层进行刻蚀,再蒸发淀积源、漏电极金属焊盘形成源、漏电极,完成器件的制备。

67.作为一种可能的实施方式,进一步的,其包括如下具体步骤:

68.s01、在反应室中对半绝缘或高阻β

‑

ga2o3衬底表面进行预处理,衬底的掺杂元素种类包含mg、fe、zn、n、p中的任意一种,掺杂所采取的摩尔百分比为0.05~0.06,厚度为400~700μm;

69.s02、在衬底层上方同质外延生长厚度为6~12μm的非故意掺杂的β

‑

ga2o3缓冲层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;

70.s03、在缓冲层上外延生长厚度为30~50nm的(alga)2o3第一势垒层,其al组分为

0.14~0.28,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;

71.s04、在第一势垒层上方外延生长第一δ掺杂层,掺杂元素种类包含si、sn、ge中的任意一种,生长方法采用mocvd、mbe中的一种;

72.s05、在第一δ掺杂层上方外延生长厚度为15~35nm的i

‑

(alga)2o3第一间隔层,其al组分为0.15~0.26。外延生长的方法采用mocvd、mbe、pld以及hvpe中的一种;

73.s06、在第一间隔层上方中间位置外延生长厚度为100~200nm的uidβ

‑

ga2o3沟道层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种;

74.s07、在沟道层上方外延生长厚度为15~35nm的i

‑

(alga)2o3第二间隔层,其al组分为0.15~0.26,外延生长的方法采用mocvd、mbe、pld以及hvpe中的一种;

75.s08、在第二间隔层上方外延生长第二δ掺杂层,掺杂元素种类包含si、sn、ge中的任意一种,,生长方法采用mocvd、mbe中的一种;

76.s09、在第二δ掺杂层上方外延生长厚度为30~50nm的(alga)2o3第二势垒层,其al组分为0.14~0.28,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种,在第二势垒层外延生长完毕后,对其上侧中间靠近左边缘位置进行干法刻蚀以形成沟槽,沟槽下方剩余第二势垒层厚度为0~6nm;

77.s10、在第一间隔层上方左侧和右侧分别外延生长n型重掺杂的β

‑

ga2o3第一盖帽层和第二盖帽层,外延生长方法采用mocvd、mbe、pld以及hvpe中的一种,掺杂元素种类包含si、sn、ge、f、cl中的任意一种,掺杂浓度为1

×

1018~5

×

1019cm

‑3,厚度为200~400nm;

78.s11、在第一盖帽层和第二盖帽层上方利用电子束蒸发依次淀积厚度分别为60nm、80nm和200nm的ti、al和au三层金属以分别形成源、漏电极,再对其进行高温退火以获得良好的欧姆接触;

79.s12、沉积将第一盖帽层、源电极、第二势垒层、漏电极以及第二盖帽层包裹的厚度为3~7nm的介质层,其构成材料包含al2o3、sio2、si3n4、hfo2中的任意一种;

80.s13、在由介质层包围的凹槽处利用电子束蒸发依次淀积厚度分别60nm、250nm的ni、au两层金属以形成t型栅电极和mis结构;

81.s14、对源电极和漏电极表面的介质层进行干法刻蚀以形成金属互联窗口,此时介质层被分为三部分,再通过电子束蒸发淀积源、漏电极金属焊盘,以形成倒t型的源、漏电极,完成器件的制备。

82.本发明采用以上技术方案,具有以下有益效果:本发明采用凹槽栅刻蚀技术切断由2deg构成的导电沟道实现hemt常关型操作,凹槽栅刻蚀技术具备工艺成熟、成本低、均匀性和重复性好等优点。更重要的是,本发明设计δ掺杂(平面掺杂)势垒层,具体做法是当(alga)2o3间隔层生长完毕之后,在其上生长一层几个原子层厚度的施主杂质层,即δ掺杂层,然后再生长不掺杂的(alga)2o3势垒层。本发明采用δ掺杂势垒层结构来代替对整层进行均匀掺杂的势垒层结构,一方面可以避免产生平行导电通道,并克服由其带来的器件跨导和击穿电压降低,射频特性功能下降和开关特性变差等不足。另一方面可以减弱陷阱效应,增大沟道中的2deg浓度,以及提高器件的击穿电压和可靠性。本发明用于实现器件常关操作所采用的凹槽栅刻蚀技术具备工艺成熟、成本低、均匀性和重复性好等优势。

附图说明

83.下面结合附图与具体实施方式对本发明做进一步详细的说明:

84.图1为本发明实施例1所提供的含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件结构示意图;

85.图2为实施例1含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件在不同势垒层厚度时的导带示意图;

86.图3为本发明实施例1所提供的含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件的制备流程图;

87.图4为本发明实施例2所提供的含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件结构示意图;

88.图5为实施例2含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件在不同势垒层厚度时的导带示意图;

89.图6为本发明实施例2所提供的含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件的制备流程图;

90.图7为本发明实施例3所提供的含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件结构示意图;

91.图8为实施例3含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件在不同势垒层厚度时的导带示意图;

92.图9为本发明实施例3所提供的含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件的制备流程图。

具体实施方式

93.为使本发明实施方式的目的、技术方案和优点更加清楚,下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述。

94.实施例1

95.本发明的一种含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件结构如图1所示,由下至上包括:

96.衬底11、缓冲层12、沟道层13、间隔层14、δ掺杂层15、势垒层16、源电极17、漏电极18,被分为19(1)、19(2)和19(3)三部分的介质层以及栅电极20。

97.其中,衬底11为半绝缘或高阻特性的β

‑

ga2o3,其掺杂元素种类为mg、fe、zn、n、p中的任意一种,但不限于此,掺杂所采取的摩尔百分比为0.05~0.06,厚度为400~700μm。衬底11上方为uidβ

‑

ga2o3缓冲层12,其厚度为6~12μm,该层的主要作用是降低外延层缺陷密度并减小来源于反应室或衬底杂质对沟道电子的影响以及防止衬底电子进入缓冲层而干扰栅极对沟道电子的调制作用。缓冲层12上方为uidβ

‑

ga2o3沟道层13,其左上侧和右上侧被刻蚀(刻蚀厚度分别为图1中的21和27),因此呈台面状。沟道层13未被刻蚀之前的厚度为250~700nm,该层的作用是用来聚集2deg(25)并作为电子运输通道。沟道层13的左上侧和右上侧被刻蚀的目的是增加沟道层表面的氧空位缺陷和提高界面处的载流子浓度,最终降低欧姆接触电阻。沟道层13台面上方为i

‑

(alga)2o3间隔层14,其厚度为15~35nm,al组分为0.15~0.26,该层的作用一是将处于δ掺杂层的电离施主杂质和电子在空间上分离,降低电

离杂质散射对沟道电子的影响,从而提高电子的迁移率,二是与沟道层接触以形成三角势阱,进而聚集2deg(25)。间隔层14上方为δ掺杂层15,其本质是一层厚度极薄的施主杂质层,掺杂的元素种类为si、sn、ge中的任意一种,但不限于此,所起的作用是向沟道层提供电子以形成2deg(25)。δ掺杂层15上方为上侧中间靠近左边缘位置被刻蚀的(alga)2o3势垒层16,其厚度为30~50nm,al组分为0.14~0.28,刻蚀剩余部分的厚度(即图1中22所示的厚度)为0~6nm。势垒层16的作用一是保证位于沟槽下方之外的沟道区存在足够大浓度的2deg,二是作为mis组成部分之一,三是作为被刻蚀区域以实现器件的常关操作。沟道层13左上侧和右上侧被刻蚀处上方分别为倒t型源电极17和漏电极18,其由厚度分别为60nm、80nm和200nm的ti、al和au三层金属组成。介质层将沟道层13、势垒层16、源电极17以及漏电极18包裹并被倒t型源电极17和漏电极18分成19(1)、19(2)和19(3)三部分,其组成材料可以是al2o3、sio2、si3n4、hfo2中的任意一种,但不限于此,厚度为3~7nm,其作用是降低刻蚀带来的损伤,减小栅极泄漏电流。由介质层19(2)包围的凹槽23处上方为t型栅电极20,其由厚度分别为60nm和250nm的ni、au两层金属构成。由t型栅电极20、介质层19(2)以及势垒层16构成该器件的金属

‑

绝缘体

‑

半导体(记作mis)结构。

98.对于含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件,采用的是凹槽栅刻蚀技术来实现器件的常关操作。该技术刻蚀的对象是势垒层16,通过减薄其位于栅电极20正下方部分的厚度,来达到器件常关的目的。由于该技术通过对势垒层16进行刻蚀形成了沟槽,导致在沉积介质层19(2)时形成了由其包围的凹槽23,进而使得栅电极20在制作时向凹槽23内凹陷,最终形成如图1(20)所示的t型凹槽栅结构,因此被称之为凹槽栅刻蚀技术。

99.结合图2所示的不同势垒层厚度时的导带示意图解释采用凹槽栅刻蚀技术切断由2deg构成的导电沟道实现器件常关操作的机理。对于势垒层16,由于被刻蚀,根据其位置和厚度可以分为两种,一种是被刻蚀剩余的位于凹槽23下方较薄的部分(即图1中的22),另一种是未被刻蚀位于凹槽23之外较厚的部分。势垒层16位于凹槽23下方较薄的部分(即被刻蚀剩余部分)、δ掺杂层15、间隔层14以及沟道层13等区域的导带如图2(a)所示,此时由于势垒层16较薄,抬高了异质结界面处的三角势阱的位置,使其位于费米能级上方,同时也使得位于凹槽23下方的沟道电子完全耗尽(即图1中的24处无2deg)。而势垒层16未被刻蚀位于凹槽23之外较厚的部分、δ掺杂层15、间隔层14以及沟道层13等区域的导带如图2(b)所示,此时由于势垒层16较厚,降低了异质结界面处的三角势阱的位置,使其位于费米能级下方,从而使得位于凹槽23下方之外的沟道层表面有电子聚集(即图1中的25处存在2deg)。而对于整个器件,当栅电极20不加偏置,仅在源电极17和漏电极18之间加偏置电压时,由于凹槽23下方的沟道层界面处(即图1中的24)无2deg,导致由2deg构成的连接源电极17和漏电极18之间的导电沟道被切断,进而使得源电极17和漏电极18连接断开,无漏电流输出,因此器件工作在常关状态下。

100.参照图3,本发明基于含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件的制备方法:

101.制备成厚度为600μm、fe掺杂且摩尔百分比为0.055的β

‑

ga2o3衬底11,厚度为8μm的β

‑

ga2o3缓冲层12,厚度为600nm的uidβ

‑

ga2o3沟道层13,厚度为25nm、al组分为0.16的i

‑

(alga)2o3间隔层14,采用si元素掺杂的δ掺杂层15,厚度为45nm、al组分为0.24的(alga)2o3势垒层16(剩余势垒层厚度22为3nm),由厚度分别为60nm、80nm和200nm的ti、al和au三层金

属组成的源电极17和漏电极18,厚度为4nm的si3n4介质层(由19(1)、19(2)和19(3)三部分组成),由厚度分别为60nm和250nm的ni、au两层金属组成的栅电极20的含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件,其步骤如下:

102.(1)准备fe掺杂的高阻或半绝缘β

‑

ga2o3衬底11,并对其进行预处理,该过程具体为先用丙酮和异丙醇分别清洗40~60s,再用去离子水清洗,最后用氮气枪吹干,如图3(a)。

103.(2)将衬底11放置于金属有机物化学气相沉积(mocvd)反应室中同质外延生长缓冲层12,如图3(b)。外延生长条件如下:采用三乙基镓(tega)作为镓源,其流量为40sccm;使用氩气作为载气将镓源输送至反应腔体;使用高纯氧作为反应剂,其流量为45sccm;生长温度为650℃,o2/tega(o2与镓源流量之比)为900。

104.(3)在缓冲层12上方同质外延生长沟道层13,并对其左上侧和右上侧进行刻蚀以形成台面,如图3(c)。外延生长采用mocvd技术,条件如下:采用三乙基镓(tega)作为镓源,其流量为30sccm;载气为氩气;反应剂高纯氧的流量为55sccm;生长温度为720℃,o2/tega为920。在沟道层13生长完毕之后,利用光刻胶并采用光刻的方式将沟道层13上表面中间位置进行保护,再对沟道层13左上侧和右上侧未被光刻胶保护区域采用电感耦合等离子体(icp)刻蚀以形成台面。刻蚀条件如下:采用的刻蚀气体为bcl3,其流量为40sccm;启辉功率为450w;整个刻蚀过程分为两步,第一步是主要刻蚀过程,采用的刻蚀功率为30w;第二步需要在低功率下完成,以减小表面刻蚀损伤,采用的刻蚀功率为15w。

105.(4)在沟道层13台面上方外延生长间隔层14,如图3(d)。外延生长采用mocvd技术,条件如下:采用三乙基镓(tega)为镓源,三甲基铝(tmal)为铝源,以moral(tmal)表示铝源的摩尔数,以moral(tega+tmga)表示镓源和铝源的摩尔数,反应时二者之比(moral(tmal)/moral(tega+tmga))为0.23;载气为氩气;反应剂高纯氧的流量为55sccm;生长温度为800℃,o2/(tega+tmga)(o2流量与镓源和铝源流量和之比)为940。

106.(5)在间隔层14上方外延生长δ掺杂层15,如图3(e)。外延生长采用mocvd技术,条件如下:采用硅烷作为前驱体,其摩尔流量为40nmol/min;载气为氩气,反应剂o2的流量为650sccm,生长温度为800℃。

107.(6)在δ掺杂层15上方外延生长势垒层16并对其上侧中间靠近左边缘位置进行干法刻蚀以形成沟槽,如图3(f)。外延生长采用mocvd技术,条件如下:采用三乙基镓(tega)为镓源,三甲基铝(tmal)为铝源,moral(tmal)/moral(tega+tmga)为0.26;载气为氩气;反应剂高纯氧的流量为52sccm;生长温度为850℃,o2/(tega+tmga)为960。在势垒层16外延生长完毕之后,利用光刻胶并采用光刻的方式将势垒层16位于沟槽下方之外的区域进行保护,再对势垒层未被光刻胶保护区域采用icp刻蚀以形成沟槽。刻蚀条件如下:采用的刻蚀气体为bcl3,其流量为35sccm;启辉功率为380w;整个刻蚀过程分为两步,第一步是主要刻蚀过程,采用的刻蚀功率为28w,第二步需要在低功率下完成,以减小表面刻蚀损伤,采用的刻蚀功率为12w。

108.(7)在沟道层13左上侧和右上侧被刻蚀处上方淀积源电极17和漏电极18,如图3(g)。淀积采用电子束蒸发技术,在高真空且功率为550w的工艺条件下依次淀积ti、al、au三层金属。在源电极17和漏电极18淀积完毕之后,在氮气气氛中且温度为480℃的条件下退火65s。

109.(8)沉积介质层19,如图3(h)。淀积采用的技术为等离子增强化学气相淀积pecvd,

条件如下:氨气流量为4sccm,氮气流量为920sccm,硅烷流量为280sccm,温度为450℃,功率为25w。

110.(9)淀积t型栅电极20,如图3(i)。淀积采用电子束蒸发技术,在高真空且功率为450w的工艺条件下依次淀积ni、au两层栅极金属。

111.(10)对源电极17和漏电极18表面的介质层进行干法刻蚀以形成金属互联窗口,再通过电子束蒸发淀积源电极17和漏电极18金属焊盘,以形成倒t型的源电极17和漏电极18,如图3(j)。干法刻蚀采用的是icp刻蚀,条件如下:刻蚀气体为cf4和o2组成的混合气体,流量分别为75sccm和5sccm;启辉功率为450w;刻蚀功率为75w。源电极17和漏电极18的淀积方法和条件与实施例1的步骤(7)相同。

112.实施例2

113.本发明的一种含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件如图4所示,由下至上包括:

114.衬底31、缓冲层32、沟道层33、间隔层34、δ掺杂层35、势垒层36、第一盖帽层37、第二盖帽层38、源电极39、漏电极40,被分为41(1)、41(2)和41(3)三部分的介质层以及栅电极42。

115.其中,衬底31、缓冲层32、沟道层33、间隔层34、δ掺杂层35、势垒层36分别与图1中的衬底11、缓冲层12、沟道层13、间隔层14、δ掺杂层15、势垒层16对应相同。43和48分别表示沟道层33左上侧和右上侧被刻蚀的厚度,取值范围分别与图1中的21和26相同。44表示剩余势垒层的厚度,其与图1中的22取值范围相同。位于沟道层33左上侧和右上侧被刻蚀处上方的第一盖帽层37和第二盖帽层38为n型重掺杂的β

‑

ga2o3,其掺杂元素种类为si、sn、ge、f、cl中的任意一种,但不限于此,掺杂浓度为1

×

1018~5

×

1019cm

‑3,厚度为60~120nm。第一盖帽层37和第二盖帽层38所起的作用是在得到良好的欧姆接触的前提下,降低工艺难度。源电极39和漏电极40分别与图1中的源电极17和漏电极18对应相同。作为介质层的组成之一的41(1)、41(2)和41(3)分别与图1中的19(1)、19(2)和19(3)对应相同。由介质层41(2)包围的凹槽45处上方为t型栅电极42,其与图1中的20相同。由t型栅电极42、介质层41(2)以及势垒层36构成该器件的mis结构。

116.含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件在不同势垒层厚度时的导带示意图如图5所示,由于图5中标识的势垒层36、δ掺杂层35、间隔层34以及沟道层33分别与图2中的势垒层16、δ掺杂层15、间隔层14以及沟道层13对应相同,因此含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件也是通过采用凹槽栅刻蚀技术切断由2deg构成的导电沟道实现器件的常关操作。其机理与含δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件完全相同,通过采用凹槽栅刻蚀技术减薄势垒层36位于凹槽45下方的厚度,以耗尽位于凹槽45正下方沟道层33中的电子,即46处无2deg(在图5(a)中表示为沟道33中的三角势阱位于费米能级ef上方),同时保证沟道层33位于凹槽45之外的区域可以聚集一定浓度的电子,即47处有2deg(在图5(b)中表示为沟道33中的三角势阱位于费米能级ef下方),最终使得当栅电极42不加偏置时,源电极39和漏电极40因由2deg构成的连接二者之间的导电沟道被切断而断开,完成器件的常关操作。

117.参照图6,本发明基于含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件的制备方法:

118.制备成厚度为600μm、fe掺杂且摩尔百分比为0.055的β

‑

ga2o3衬底31,厚度为8μm的β

‑

ga2o3缓冲层32,厚度为600nm的uidβ

‑

ga2o3沟道层33,厚度为25nm、al组分为0.16的i

‑

(alga)2o3间隔层34,采用si元素掺杂的δ掺杂层35,厚度为45nm、al组分为0.24的(alga)2o3势垒层36(剩余势垒层厚度44为3nm),厚度为70nm、掺杂元素和浓度分别为si和1

×

1019cm

‑3的第一盖帽层37和第二盖帽层38,厚度为4nm的si3n4介质层(由41(1)、41(2)和41(3)三部分组成),由厚度分别为60nm、80nm和200nm的ti、al和au三层金属组成的源电极39和漏电极40,由厚度分别为60nm和250nm的ni、au两层金属组成的栅电极42的含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件,其步骤如下:

119.(1)准备fe掺杂的高阻或半绝缘β

‑

ga2o3衬底31,并对其进行预处理,该过程具体为先用丙酮和异丙醇分别清洗40~60s,再用去离子水清洗,最后用氮气枪吹干,如图6(a)。

120.(2)将衬底31放置于金属有机物化学气相沉积(mocvd)反应室中同质外延生长β

‑

ga2o3缓冲层32,如图6(b)。外延生长的条件与实施例1中的步骤(2)相同。

121.(3)在缓冲层32上方同质外延生长沟道层33,并对其左上侧和右上侧进行刻蚀以形成台面,如图6(c)。外延生长方法和条件与实施例1中的步骤(3)相同。在沟道层33生长完毕之后,利用光刻胶并采用光刻的方式将沟道层上33表面中间位置进行保护,再对沟道层33左上侧和右上侧未被光刻胶保护区域采用电感耦合等离子体(icp)刻蚀以形成台面。刻蚀的方法和条件与实施例1中的步骤(3)相同。

122.(4)在沟道层33台面上方外延生长间隔层34,如图6(d)。外延生长方法和条件与实施例1中的步骤(4)相同。

123.(5)在间隔层34上方外延生长δ掺杂层35,如图6(e)。外延生长方法和条件与实施例1中的步骤(5)相同。

124.(6)在δ掺杂层35上方外延生长势垒层36并对其上侧中间靠近左边缘位置进行干法刻蚀以形成沟槽,如图6(f)。外延生长方法和条件与实施例1中的步骤(6)相同。在势垒层36外延生长完毕之后,利用光刻胶并采用光刻的方式将势垒层36位于沟槽下方之外的区域进行保护,再对势垒层未被光刻胶保护区域采用icp刻蚀以形成沟槽。刻蚀的方法和条件与实施例1中的步骤(6)相同。

125.(7)在沟道层33左上侧和右上侧被刻蚀处上方外延生长第一盖帽层37和第二盖帽层38,如图6(g)。外延生长采用mocvd技术,条件如下:采用三乙基镓(tega)作为镓源,其流量为35sccm;以硅烷(sih4)作为掺杂剂;载气为氩气;反应剂高纯氧的流量为60sccm;生长温度为600℃,o2/tega为970。

126.(8)在第一盖帽层37和第二盖帽层38上方淀积源电极39和漏电极40,如图6(h)。淀积的方法和条件与实施例1中的步骤(7)相同。在源电极39和漏电极39淀积完毕之后,对其进行退火,退火条件与实施例1中的步骤(7)相同。

127.(9)沉积介质层41,如图6(i)。淀积的方法和条件与实施例1中的步骤(8)相同。

128.(10)淀积t型栅电极20,如图6(j)。淀积的方法和条件与实施例1中的步骤(9)相同。

129.(11)对源电极39和漏电极40表面的介质层进行干法刻蚀以形成金属互联窗口,再通过电子束蒸发淀积源电极39和漏电极40金属焊盘,以形成倒t型的源、漏电极,如图6(k)。干法刻蚀的方法和条件与实施例1的步骤(10)相同。源电极39和漏电极40的淀积方法和条

件与实施例1中的步骤(10)相同。

130.实施例3

131.本发明的一种含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件如图7所示,由下至上包括:

132.衬底51、缓冲层52、第一势垒层53、第一δ掺杂层54、第一间隔层55、沟道层56、第二间隔层57、第二δ掺杂层58、第二势垒层59、第一盖帽60层、第二盖帽层61、源电极62、漏电极63,被分为64(1)、64(2)和64(3)三部分的介质层以及栅电极65。

133.其中,衬底51和缓冲层52与图2中的衬底31和缓冲层32对应相同。缓冲层52中间上方为(alga)2o3第一势垒层53,其厚度为30~50nm,al组分为0.14~0.28,其所起的作用是与第一间隔层55一起作为宽禁带半导体,以与窄禁带半导体β

‑

ga2o3接触形成异质结,耗尽第一δ掺杂层54内的电子。第一势垒层53上方为第一δ掺杂层54,其与图4中的35相同。第一δ掺杂层54上方为i

‑

(alga)2o3第一间隔层55,其与图4中的34相同。第一间隔层55上方中间位置为uidβ

‑

ga2o3沟道层56,其厚度为100~200nm。沟道层56上方为与第一间隔层55相同的第二间隔层57。第二间隔层57上方为与第一δ掺杂层54相同的第二δ掺杂层58。第二δ掺杂层58上方为与图4中的36相同的第二势垒层59,其刻蚀所剩厚度为图7中的67,取值范围与图4中的44相同。第一间隔层55上方左侧和右侧分别为n型重掺杂的β

‑

ga2o3第一盖帽层60和第二盖帽层61,掺杂元素种类为si、sn、ge、f、cl中的任意一种,但不限于此,掺杂浓度为1

×

1018~5

×

1019cm

‑3,厚度为200~400nm。第一盖帽层60和第二盖帽层上方分别为源电极62和漏电极63,其分别与图4中的源电极39和漏电极40对应相同。作为介质层的组成之一的64(1)、64(2)和64(3)分别与图4中的41(1)、41(2)和41(3)完全相同。由介质层64(2)包围的凹槽68处上方为t型栅电极65,其与图4中的42相同。由t型栅电极65、介质层64(2)以及第二势垒层59构成该器件的mis结构。

134.含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件在不同势垒层厚度时的导带示意图如图8所示。由于窄禁带沟道层56两侧分别为对称的宽禁带第一间隔层55和第二间隔层57,因此在沟道层56处出现由两个三角势阱组成的近似方形的势阱。含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件也是通过采用凹槽栅刻蚀技术切断由2deg构成的导电沟道实现器件的常关操作。其机理与含盖帽层和δ掺杂单势垒层的常关型氧化镓基mis

‑

hemt器件类似,其通过采用凹槽栅刻蚀技术减薄第二势垒层59位于凹槽68下方的厚度,以耗尽位于凹槽68正下方的沟道层56中的电子,即69处无2deg(在图8(a)中表示为沟道56中的方形势阱位于费米能级ef上方),同时保证沟道层56位于凹槽68之外的区域可以聚集一定浓度的电子,即66处有2deg(在图8(b)中表示为沟道56中的方形势阱位于费米能级ef下方),最终使得当栅电极不加偏置时,源电极62和漏电极63因由2deg构成的连接二者之间的导电沟道被切断而断开,完成器件的常关操作。

135.参照图9,本发明基于含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件的制备方法:

136.制备成厚度为600μm、fe掺杂且摩尔百分比为0.055的β

‑

ga2o3衬底51,厚度为8μm的β

‑

ga2o3缓冲层52,厚度为45nm、al组分为0.24的(alga)2o3第一势垒层53,采用si元素掺杂的第一δ掺杂层54,厚度为25nm、al组分为0.16的i

‑

(alga)2o3第一间隔层55,厚度为180nm的β

‑

ga2o3沟道56,厚度为25nm、al组分为0.16的i

‑

(alga)2o3第二间隔层57,采用si元素掺杂

的第二δ掺杂层58,厚度为45nm、al组分为0.24的(alga)2o3第二势垒层59(剩余势垒层厚度67为3nm),厚度为250nm、掺杂元素和浓度分别为si和1

×

1019cm

‑

3的第一盖帽层60和第二盖帽层61,厚度为4nm的si3n4介质层(由64(1)、64(2)和64(3)三部分组成),由厚度分别为60nm、80nm和200nm的ti、al和au三层金属组成的源电极62和漏电极63,由厚度分别为60nm和250nm的ni、au两层金属组成的栅电极65的含盖帽层和δ掺杂双势垒层的常关型氧化镓基mis

‑

hemt器件,其步骤如下:

137.(1)准备fe掺杂的高阻或半绝缘β

‑

ga2o3衬底51,并对其进行预处理,该过程具体为先用丙酮和异丙醇分别清洗40~60s,再用去离子水清洗,最后用氮气枪吹干,如图9(a)。

138.(2)将衬底51放置于金属有机物化学气相沉积(mocvd)反应室中同质外延生长缓冲层52,如图9(b)。外延生长的条件与实施例2中的步骤(2)相同。

139.(3)在缓冲层52上方外延生长第一势垒层53,如图9(c)。外延生长方法和条件与实施例2中的步骤(6)相同。

140.(4)在第一势垒层53上方外延生长第一δ掺杂层54,如图9(d)。外延生长方法和条件与实施例2中的步骤(5)相同。

141.(5)在第一δ掺杂层54上方外延生长第一间隔层55,如图9(e)。外延生长方法和条件与实施例2中的步骤(4)相同。

142.(6)在第一间隔层上方中间位置外延生长沟道层56,如图9(f)。外延生长采用mocvd技术,条件如下:采用三乙基镓(tega)作为镓源,其流量为30sccm;载气为氩气;反应剂高纯氧的流量为55sccm;生长温度为720℃,o2/tega为920。

143.(7)在沟道层56上方外延生长第二间隔层57,如图9(g)。外延生长方法和条件与实施例2中的步骤(4)相同。

144.(8)在第二间隔层57上外延方生长第二δ掺杂层58,如图9(h)。外延生长方法和条件与实施例2中的步骤(5)相同。

145.(9)在第二δ掺杂层上方外延生第二势垒层59,如图9(i)。外延生长方法和条件与实施例2中的步骤(6)相同。在势垒层36外延生长完毕之后,利用光刻胶并采用光刻的方式将势垒层59位于沟槽下方之外的区域进行保护,再对势垒层未被光刻胶保护区域采用icp刻蚀以形成沟槽。刻蚀的方法和条件与实施例2中的步骤(6)相同。

146.(10)在第一间隔层55上方左侧和右侧分别外延生长第一盖帽层60和第二盖帽层61,如图9(j)。外延生长采用mocvd技术,条件如下:采用三乙基镓(tega)作为镓源,其流量为35sccm;以硅烷(sih4)作为掺杂剂;载气为氩气;反应剂高纯氧的流量为60sccm;生长温度为600℃,o2/tega为970。

147.(11)在第一盖帽层60和第二盖帽层61上方淀积源电极62和漏电极63,如图9(k)。淀积的方法和条件与实施例2中的步骤(8)相同。在源电极62和漏电极63淀积完毕之后,对其进行退火,退火条件与实施例2中的步骤(8)相同。

148.(12)沉积介质层64,如图9(l)。淀积的方法和条件与实施例2中的步骤(9)相同。

149.(13)淀积t型栅电极65,如图9(m)。淀积的方法和条件与实施例2中的步骤(10)相同。

150.(14)对源电极62和漏电极63表面的介质层进行干法刻蚀以形成金属互联窗口,再通过电子束蒸发淀积源电极62和漏电极63金属焊盘,以形成倒t型的源电极62和漏电极63,

如图9(n)。干法刻蚀的方法和条件与实施例2的步骤(11)相同。源电极62和漏电极63的淀积方法和条件与实施例2中的步骤(11)相同。

151.以上所述为本发明的实施例,对于本领域的普通技术人员而言,根据本发明的教导,在不脱离本发明的原理和精神的情况下凡依本发明申请专利范围所做的均等变化、修改、替换和变型,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1