图像传感器及其形成方法与流程

1.本发明属于半导体制造领域,尤其涉及一种图像传感器及其形成方法。

背景技术:

2.cmos图像传感器(complementary metal oxide semiconductor image sensor, cis)是将光学图像转化为电信号的半导体器件。cis包括用于感光的光电二极管(photodiode, pd)和用于将所感测的光处理为电信号的逻辑电路。

3.随着cis的像素单元越来越小,满阱容量(full well capacity, fwc)也越来越小。针对小像素fwc不足以及动态范围小的情况,一般会从衬底的深度方向上去提升,例如,通过增加硅衬底的深度。仅仅增加硅衬底的厚度,fwc 的提升并不是明显,通常还会增加一步n-type的离子注入。

4.对于背照式cis,一般会在衬底背面形成深沟槽(backside deep trench isolation, bdti)进行隔离,以解决相邻像素间的光学/电学串扰(crosstalk)。在刻蚀衬底形成bdti结构过程中会带来不同程度的界面缺陷和损伤,后续会在bdti表面沉积氧化铪(hfo2)等高介电常数材料钝化界面缺陷,并进行填充氧化铝(al2o3)。而底部和侧面的隔离一般较弱,此时高介电常数材料的钝化作用很容易受到其他因素的影响。

5.如图1所示,通常小尺寸像素为了保证pd的fwc,对半导体衬底10采用两道n型离子注入掩膜版,形成离子掺杂区11和离子掺杂区12,其中,上半部分尺寸(critical dimension, cd)较大(主要贡献fwc 部分),考虑到拖尾(lag)和白点(white pixel,wp),下半部分cd 较小,并且采用的都是磷(phosphorus)元素注入。此种方法缺点是磷容易扩散到侧面导致p型隔离13不够,同时扩散到半导体衬底10底部导致bdti 15表面的高介电常数材料14的钉扎不足引起wp 明显增加。

技术实现要素:

6.基于现有技术中存在的问题,本发明提供了一种图像传感器的形成方法。该方法包括:提供半导体衬底,半导体衬底具有正面和背面;自半导体衬底正面对半导体衬底进行离子注入,分别形成第一离子掺杂区、第二离子掺杂区和第三离子掺杂区共同形成图像传感器的感光单元;所述第二离子掺杂区位于所述第一离子掺杂区下方;所述第三离子掺杂区至少部分包围所述第一离子掺杂区。

7.在一些实施例中,第一离子掺杂区为磷;第二离子掺杂区和第三离子掺杂区为砷;感光单元之间隔离的离子注入掺杂为硼或铟。

8.在一些实施例中,该方法还包括:自半导体衬底正面对感光单元之间进行离子注入,形成正面隔离区。

9.在一些实施例中,该方法还包括:在半导体衬底背面形成背面深沟槽隔离区;所述背面深沟槽隔离区底部被所述正面隔离区所包裹。

10.在一些实施例中,所述第二离子掺杂区先于所述第一离子掺杂区形成。

11.在一些实施例中,所述第二离子掺杂区先于所述第一离子掺杂区形成;在形成所述第二离子掺杂区之后,采用快速热处理进行离子激活。

12.在一些实施例中,所述第二离子掺杂区先于第一离子掺杂区形成;在形成所述第二离子掺杂区之后,采用快速热处理进行离子激活,然后采用高温退火进行离子注入损失修复。

13.在一些实施例中,快速热处理温度范围为750~1100℃,处理时间为10s-1min。

14.在一些实施例中,高温退火温度范围为750~1100℃,处理时间为10min-120min。

15.在一些实施例中,形成所述第二离子注入掺杂区以及快速热处理之后,再形成所述第一离子注入掺杂区和感光单元之间的正面隔离区。

16.在一些实施例中,所述第二离子掺杂区为砷,通过同一掩膜层多步离子注入完成。

17.在一些实施例中,所述第三离子掺杂区为砷,通过同一掩膜层多步离子注入完成。

18.在一些实施例中,形成所述第一次离子掺杂区和所述第二离子掺杂区共同使用同一掩膜层。

19.在一些实施例中,形成所述第三离子掺杂区使用的掩膜层暴露出所述第一离子掺杂区。

20.在一些实施例中,形成所述第三离子掺杂区使用的掩膜层将所述第一离子掺杂区部分遮挡或完全遮挡,暴露出环状的部分半导体衬底。

21.在一些实施例中,所述第三离子掺杂区的深度,根据半导体衬底的背面深沟槽隔离的深度进行调整。

22.在一些实施例中,所述第一离子掺杂区的深度超过半导体衬底的背面深沟槽隔离的底部。

23.在一些实施例中,所述第三离子掺杂区和所述第二离子掺杂区将所述第一离子掺杂区完全包围。

24.本发明还提供了一种图像传感器,包括:半导体衬底,半导体衬底具有正面和背面;位于半导体衬底内的第一离子掺杂区、第二离子掺杂区和第三离子掺杂区共同形成图像传感器的感光单元;所述第二离子掺杂区位于所述第一离子掺杂区下方;所述第三离子掺杂区至少部分包围所述第一离子掺杂区。

25.本发明还提供了一种图像传感器,通过上述方法形成。

26.与现有技术相比,本发明的技术方案具有以下有益效果:本发明的技术方案通过磷和砷共同对半导体衬底进行n型离子注入,具体为先用第一层掩膜层进行磷的离子注入, 自半导体衬底正面从上到下进行多步磷的离子注入,最后靠近半导体衬底底部区域掺杂砷,可以减少磷扩散到底部导致底部面上钉扎不足引起的wp增加;然后用第二层掩膜层注入砷,使注入的砷至少部分包围磷,从而可以有效利用砷扩散系数小来避免与侧面隔离区中的p型离子补偿掉,这样既保证了fwc不会降低,又避免侧面隔离区钉扎不足引起wp增加;同时没有完全用砷去替代磷,热预算较少,注入的离子容易激活,注入过程的损伤容易修复。

27.本发明的技术方案优点明显,既不需要增加任何新的掩膜层,也不会增加成本,即可得到较大的 fwc、wp 较小的高性能小尺寸高像素的图像传感器。

附图说明

28.本发明附图构成本说明书的一部分、用于进一步理解本发明,附图示出了本发明的实施例,并与说明书一起用来说明本发明的原理。

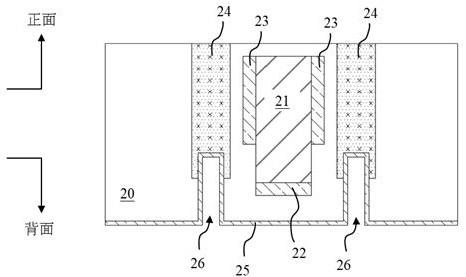

29.图1为现有技术的一种图像传感器的结构的截面示意图:图2为本发明实施例的一种图像传感器的形成方法的流程图;图3为本发明实施例的一种图像传感器的结构的截面示意图;图4为本发明实施例的另一种图像传感器的结构的截面示意图。

具体实施方式

30.以下详细说明都是例示性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

31.需要注意的是,这里所使用的术语仅是为了描述具体实施例,而非意图限制根据本发明的示例性实施例。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,当在本说明书中使用属于“包含”和/或“包括”时,其指明存在特征、步骤、操作、器件、组件和/或它们的组合。

32.图2为本发明实施例的一种图像传感器的形成方法的流程图,该方法包括以下步骤:步骤s1:提供半导体衬底,半导体衬底具有正面和背面。

33.步骤s2:自所述半导体正面对半导体衬底进行离子注入,分别形成第一离子掺杂区、第二离子掺杂区和第三离子掺杂区共同形成图像传感器的感光单元;所述第二离子掺杂区位于所述第一离子掺杂区下方;所述第三离子掺杂区至少部分包围所述第一离子掺杂区。

34.具体的,结合图3和图4对上述形成方法进行详细描述。如图3和图4所示,提供半导体衬底20,半导体衬底20具有正面和背面。可选的,半导体衬底20可以是掺杂或未掺杂的半导体材料,诸如硅、锗、硅锗、绝缘体上锗硅或其组合。可选的,半导体衬底10可以包括多层外延层的衬底。

35.如图3和图4所示,自半导体衬底20正面对半导体衬底20进行离子注入,分别形成第一离子掺杂区21、第二离子掺杂区22和第三离子掺杂区23共同形成图像传感器的感光单元。

36.可选的,第二离子掺杂区22位于第一离子掺杂区21下方;第三离子掺杂区23至少部分包围第一离子掺杂区21。如图4所示,第三离子掺杂区23可以完全包围第一离子掺杂区21。

37.可选的,第一离子掺杂区21为磷;第二离子掺杂区22和第三离子掺杂区22为砷。

38.本实施例的图像传感器的形成方法还包括:自半导体衬底20正面对感光单元之间进行离子注入,形成正面隔离区24。感光单元之间隔离的离子注入掺杂为硼或铟。

39.本实施例的图像传感器的形成方法还包括:在半导体衬底20背面形成背面深沟槽隔离区26(backside deep trench isolation, bdti),bdti底部被正面隔离区24所包裹。其中,bdti包括一层高介电常数侧层25,例如,氧化铪等材料。

40.可选的,第二离子掺杂区22先于第一离子掺杂区21形成。

41.可选的,第二离子掺杂区22先于第一离子掺杂区21形成;在形成第二离子掺杂区之后,采用快速热处理进行离子激活。

42.可选的,第二离子掺杂区22先于第一离子掺杂区21形成;在形成第二离子掺杂区之后,采用快速热处理进行离子激活,然后采用高温退火进行离子注入损失修复。

43.可选的,快速热处理温度范围为750~1100℃,处理时间为10s-1min。

44.可选的,高温退火温度范围为750~1100℃,处理时间为10min-120min。

45.可选的,形成所述第二离子注入掺杂区以及快速热处理之后,再形成所述第一离子注入掺杂区和感光单元之间的正面隔离区。

46.可选的,第二离子掺杂区22为砷,通过同一掩膜层多步离子注入完成。

47.可选的,第三离子掺杂区23为砷,通过同一掩膜层多步离子注入完成。

48.可选的,形成第一次离子掺杂区21和第二离子掺杂区22共同使用同一掩膜层。

49.可选的,形成第三离子掺杂区23使用的掩膜层暴露出第一离子掺杂区21。

50.可选的,形成第三离子掺杂区23使用的掩膜层将第一离子掺杂区21部分遮挡或完全遮挡,暴露出环状的部分半导体衬底20。

51.可选的,第三离子掺杂区23的深度,根据半导体衬底20的bdti的深度进行调整。

52.可选的,第一离子掺杂区21的深度超过半导体衬底20的bdti的底部。

53.可选的,如图4所示,第三离子掺杂区23和第二离子掺杂区22将第一离子掺杂区21完全包围。

54.如图3和图4所示,本发明还提供了一种图像传感器包括:半导体衬底20,半导体衬底20具有正面和背面;位于半导体衬底20内的第一离子掺杂区21、第二离子掺杂区22和第三离子掺杂区23共同形成图像传感器的感光单元;所述第二离子掺杂区22位于所述第一离子掺杂区21下方;所述第三离子掺杂区23至少部分包围所述第一离子掺杂区21。

55.需要注意的是,本发明实施例中的图像传感器只示出了部分结构,图像传感器的其他器件,例如,转移晶体管、复位晶体管等未示出。

56.对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论如何来看,均应将实施例看作是示范性的,而且是非限制性的。此外,明显的,“包括”一词不排除其他元素和步骤,并且措辞“一个”不排除复数。第一,第二等词语用来表示名称,而并不表示任何特定的顺序。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1