半导体电路及其制造方法与流程

1.本公开总体涉及半导体电路及其制造方法。

背景技术:

2.使用拉低(tie-low)电路将标准单元接地,而不是使标准单元直接接 地。拉低电路从而用于静电放电保护。拉低电路通常通过门控电源电压来 操作,该门控电源电压激活和停用拉低电路。

技术实现要素:

3.根据本公开的一方面,提供了一种修整跟随器电路的跟随器电压的电 路,该电路包括:拉低电路,连接在跟随器节点和第一参考电压之间,所 述拉低电路响应第二参考电压,所述跟随器节点能连接到所述跟随器电路; 以及抗噪电路,连接在所述跟随器节点和所述第二参考电压之间,所述抗 噪电路被配置为保护所述跟随器节点处的所述跟随器电压不因电容耦合到 所述跟随器节点的噪声电压而失真。

4.根据本公开的一方面,提供了一种保护电路免受寄生噪声影响的方法, 该方法包括:在跟随器电路处接收第一电源电压,所述跟随器电路耦合到 跟随器节点,所述第一电源电压被配置为处于第一状态或第二状态;在拉 低电路的控制节点处接收第二电源电压,所述拉低电路耦合在所述跟随器 节点和具有地电压的第一参考节点之间,所述第二电源电压被配置为处于 第一状态或第二状态;当所述第二电源电压处于所述第一状态时,控制所 述拉低电路将所述跟随器节点处的电压电平拉向所述地电压;当所述第二 电源电压处于所述第二状态时,控制所述拉低电路不将所述跟随器节点处 的电压电平拉向所述地电压;以及对于耦合在所述跟随器节点和具有所述 第二电源电压的至少第二参考节点之间的抗噪电路,当所述第二电源电压 处于所述第二状态时,使用所述抗噪电路来保护所述跟随器节点处的电压 电平不因寄生噪声电压而失真,所述寄生噪声电压对所述跟随器节点是电 容性的,所述寄生噪声电压基于所述第一电源电压对所述跟随器节点的寄 生电容耦合。

5.根据本公开的一方面,提供了一种制造半导体器件的方法,该方法包 括:在半导体衬底中形成一个或多个有源区域;在所述一个或多个有源区 域之上形成一个或多个栅极电极,使得与所述一个或多个有源区域相应地 形成场效应晶体管(fet),所述fet包括:被指定用于拉低电路的一个 或多个第一fet;以及被指定用于抗噪电路的一个或多个第二fet;形成 导体和过孔,所述导体和过孔连接所述fet而使得:所述一个或多个第一 fet被连接以表示所述拉低电路;所述一个或多个第二fet被连接以表示 所述抗噪电路;所述拉低电路连接到跟随器节点并被配置为接收地电压和 第一电源电压;所述第一电源电压被配置为至少呈现第一状态和第二状态; 所述拉低电路被配置为响应于所述第一电源电压处于所述第一状态而将跟 随器电压拉向所述地电压,以及响应于所述第一电源电压处于所述第二状 态而不将所述跟随器电压拉向所述地电压;以及所述抗噪电路连接到所述 跟

随器节点,所述抗噪电路被配置为在所述第一电源电压处于所述第二状 态时保护所述跟随器节点处的所述跟随电压不因噪声电压而失真

附图说明

6.在结合附图阅读下面的具体实施方式时,可以从下面的具体实施方式 最佳地理解本公开的各方面。应注意,根据行业的标准做法,各种特征不 是按比例绘制的。事实上,为了讨论的清楚起见,各种特征的尺寸可能被 任意增大或减小。

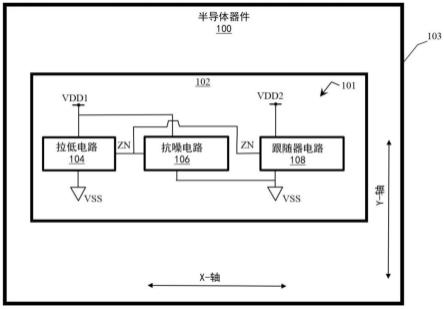

7.图1是根据一些实施例的半导体器件的框图。

8.图2a是根据一些实施例的电路的电路图。

9.图2b是根据一些实施例的半导体电路的布局图。

10.图3a是根据一些实施例的电路的电路图。

11.图3b是根据一些实施例的半导体电路的布局图。

12.图4a是根据一些实施例的电路的电路图。

13.图4b是根据一些实施例的半导体电路的布局图。

14.图4c是图4a所示电路的电源电压和跟随器(follower)节点处的跟 随器电压的电压波形图。

15.图5a是根据一些实施例的电路的电路图。

16.图5b是根据一些实施例的半导体电路的布局图。

17.图6是根据一些实施例的电路的电路图。

18.图7a是根据一些实施例的电路的电路图。

19.图7b是根据一些实施例的半导体电路的布局图。

20.图7c是图7a所示电路的电源电压和跟随器节点处的跟随器电压的电 压波形图。

21.图8a是根据一些实施例的电路的电路图。

22.图8b是根据一些实施例的半导体电路的布局图。

23.图9a是根据一些实施例的电路的电路图。

24.图9b是根据一些实施例的半导体电路的布局图。

25.图10是根据一些实施例的制造半导体器件的方法的流程图。

26.图11是根据一些实施例的制造半导体电路的方法的流程图。

27.图12是根据一些实施例的保护电路免受寄生噪声影响的方法的流程 图。

28.图13是根据一些实施例的eda系统的框图。

29.图14是根据一些实施例的ic制造系统的框图和与其相关联的ic制造 流程。

具体实施方式

30.下面的公开内容提供了用于实现所提供的主题的不同特征的许多不同 的实施例或示例。下文描述了组件、值、操作、材料、布置等的具体示例 以简化本公开。当然,这些仅是示例而不意图是限制性的。其他组件、值、 操作、材料、布置等是预期的。例如,在下面的描述中,在第二特征上方 或之上形成第一特征可以包括以直接接触的方式形成第一特征和第二特征 的实施例,并且还可以包括可以在第一特征和第二特征之间形成附加特征, 使得第一特征和第二特征可以不直接接触的实施例。此外,本公开可以在 各个示例中重复

参考数字和/或字母。该重复是出于简单和清楚的目的,并 且其本身并不指示所讨论的各种实施例和/或配置之间的关系。

31.此外,本文可使用空间相关术语(例如,“下方”、“之下”、“低 于”、“以上”、“上部”等)以易于描述图中所示的一个要素或特征相 对于另外(一个或多个)要素或(一个或多个)特征的关系。这些空间相 关术语意在涵盖器件在使用或工作中除了图中所示朝向之外的不同朝向。 装置可以以其他方式定向(旋转90度或处于其他朝向),并且本文中所 用的空间相关描述符同样可被相应地解释。

32.在一些实施例中,半导体电路包括拉低电路以选择性地将跟随器节点 处的电压下拉向参考电压,跟随器节点连接至跟随器电路。在一些实施例 中,拉低电路和跟随器电路在不同的电压域中操作。每个电压域相应地具 有不同的电源电压。当拉低电路开启时,拉低电路将跟随器节点处的电压 拉向参考电压。然而,当拉低电路关闭时,拉低电路未将跟随器节点处的 电压下拉向地。在其中当拉低电路关闭时,拉低电路未将跟随器节点处的 电压下拉向参考电压的一些实施例中,跟随器节点浮置。拉低电路通过第 一门控电源电压开启和关闭,该第一门控电源电压在对应于拉低电路的第 一电压域内。跟随器电路被提供有第二门控电源电压,该第二门控电源电 压在对应于跟随器电路的第二电压域内,第一门控电源电压不同于第二门 控电源电压。在一些情况下,第一门控电源电压的电平低于拉低电路的阈 值电平,该阈值电平关闭(即停用)拉低电路,而提供给跟随器电路的第 二门控电源电压的电平处于或接近第二门控电压的最大值。在这些情况下, 第二门控电源电压代表相对于跟随器节点的寄生噪声电压。为了在这些情 况下减少跟随器节点处的寄生噪声电压的影响,包括抗噪电路来抵消(例 如,放电)跟随器节点处的寄生噪声电压。

33.图1是根据一些实施例的半导体器件100的框图。

34.在图1中,半导体器件100还包括单元区域102。单元区域102位于 半导体衬底103之中和之上。单元区域102具有电路101,该电路101包 括拉低电路104、抗噪电路106和跟随器电路108。在一些实施例中,拉 低电路104和抗噪电路106被提供在第一单元区域中,并且跟随器电路 108被提供在第二单元区域中。在一些实施例中,拉低电路104、抗噪电 路106和跟随器电路108中的每一个被提供在单独的相应单元区域中。

35.拉低电路104连接在跟随器节点zn和参考电压vss之间。参考电压 vss是地电压(即≈0v)。在其他实施例中,参考电压vss(也称为地 电压vss)具有高于0v的正电压电平或低于0v的负电压电平。拉低电 路104响应参考电压vdd1。参考电压vdd1(也称为电源电压vdd1) 是电源电压。电源电压vdd1被配置为具有第一状态和第二状态。在一些 实施例中,当电源电压vdd1处于第一状态时,电源电压vdd1被设置为 正的第一dc电压电平。在一些实施例中,当电源电压vdd1处于第二状 态时,电源电压vdd1被设置为地电压或接近地电压。

36.在图1中,拉低电路104被配置为响应电源电压vdd1。在一些实施 例中,拉低电路104被配置为响应于电源电压vdd1处于第一状态而将跟 随器节点zn处的跟随器电压下拉向参考电压vss(例如,地电压)。在 一些实施例中,拉低电路104被配置为响应于电源电压vdd1处于第二状 态,不将跟随器节点zn处的跟随器电压下拉向参考电压vss。在一些实 施例中,在电源电压vdd1处于第二状态并因此拉低电路关闭(即拉低电 路未将跟随器节点处的电压下拉向参考电压vss)的给定情况下,跟随器 节点zn处的跟随器电压浮置。在给定情况下,第二门控电源电压代表相 对于跟随器节点的寄生噪声电压。因此跟随器节点zn处的

噪声电压。

43.图2a是根据一些实施例的电路200a的电路图。

44.电路200a包括拉低电路204和抗噪电路206。拉低电路204是图1中 的拉低电路104的示例。抗噪电路206是图1中的抗噪电路106的一个示 例。

45.在图2a中,拉低电路204包括n沟道场效应晶体管(nfet)t0。 nfet t0具有被配置为接收电源电压vdd1的栅极、连接到跟随器节点 zn的漏极、以及连接到参考端子210的源极。参考端子210被配置为接 收参考电压vss。

46.因此,nfet t0被配置为响应于电源电压vdd1处于第一状态(例如, 处于或接近第一dc电源电压电平)而将跟随器节点zn处的跟随器电压 下拉向参考电压vss。然而,当电源电压vdd1被设置为第二状态(例如, 设置为地电压或接近地电压)时,nfet t0被关断。因此,nfet t0被配 置为调整跟随器节点zn处的跟随器电压,使得跟随器节点zn处的跟随 器电压不会响应于电源电压vdd1处于第二状态而被下拉向参考电压vss。 在一些实施例中,跟随器节点zn处的跟随器电压响应于电源电压vdd1 处于第二状态而浮置。

47.如图2a所示,跟随器节点zn通过由电容cp表示的寄生电容而寄生 电容地耦合到电源电压vdd2。因此,对于其中电源电压vdd2处于第一 状态(例如,处于或接近第二dc电压电平)并且电源电压vdd1处于第 二状态(例如,处于或接近地)的给定情况,nfet t0关断,因此nfett0未下拉跟随器节点zn处的跟随器电压,其否则将抵消归因于电源电压 vdd2的跟随器节点处的寄生噪声电压。提供抗噪电路206以加强跟随器 节点zn抵抗寄生噪声电压,例如,在该给定情况下。

48.抗噪电路206连接在跟随器节点zn和电源电压vdd1之间。抗噪电 路206被配置为保护跟随器节点zn处的跟随器电压不因电容耦合到跟随 器节点zn的寄生噪声电压而失真。在图2a中,抗噪电路206包括二极 管连接fet t4。在图2a中,二极管连接fet t4是p沟道fet(pfet)。 二极管连接fet t4具有连接到电源节点212的第一漏极/源极端子、连接 到跟随器节点zn的第二漏极/源极端子、以及连接到第一漏极/源极端子和 电源节点212的栅极端子。电源节点212被配置为接收电源电压vdd1。 pfet t4的二极管配置代表其阴极连接到vdd1并且阳极连接到跟随器节 点zn的二极管。

49.在图2a中,当电源电压vdd1处于第一状态(例如,处于或接近第 一dc电压电平)时,二极管连接fet t4的第一漏极/源极端子用作二极 管连接fet t4的源极,并且二极管连接fet t4的第二漏极/源极端子 (其连接到跟随器节点zn并因此被拉向参考电压vss)用作二极管连接 fet t4的漏极。因此,二极管连接fet t4被反向偏置,但未达到二极管 连接fet t4的击穿电压的水平。当二极管连接fet t4被反向偏置时,二 极管连接fet t4未导通,因此二极管连接fet t4未将跟随器节点zn上 的跟随器电压上拉向电源电压vdd1,其否则将抵消pfet t0将跟随器节 点zn上的跟随器电压下拉向vss的影响。

50.当电源电压vdd1处于第二状态(例如,处于或接近地)时,二极管 连接fet t4的第一漏极/源极端子用作二极管连接fet t4的漏极,并且 二极管连接fet t4的第二源极/漏极端子(其连接到跟随器节点zn并因 此未被拉向参考电压vss)用作二极管连接fet t4的源极。这是因为电 源电压vdd2处于第一状态(例如,处于或接近第二dc电压电平),因 此寄生噪声电压在跟随器节点zn处呈现高电压,即vdd1《vdd2。因此, 二极管连接fet t4被正向偏置,因此二极管连接fet t4导通,其将跟随 器电压(即寄生噪声电压vdd2)下拉向vdd1,

结果寄生噪声电压通过 二极管连接fet t4被放电。

51.图2b是根据一些实施例的半导体电路的布局图200b。

52.布局图200b表示作为图2a所示的电路200a的示例的半导体电路中 的结构。图2b所示的半导体电路也是图1中的电路101的示例。半导体 器件中的结构由布局图中的形状(也称为图案)表示。为了讨论的简单起 见,图2b(以及本文包括的其他图)的布局图中的元素将被视为它们本 身是结构而不是图案。例如,形状260代表有源区域(也称为氧化物定义 (od)区域)。

53.在以下讨论中,元素260被称为有源区域260,而不是有源区域形状 260。

54.布局图200b包括拉低电路254和抗噪电路256。布局图200b包括对 半导体衬底253的表示。半导体衬底253是图1中的半导体衬底103的示 例。在至少一个实施例中,半导体衬底253由硅、硅锗(sige)、砷化镓、 或其他合适的半导体材料形成。

55.半导体衬底253包括有源区域260和有源区域261。有源区域260被 掺杂以具有p型导电性,而有源区域261被掺杂以具有n型导电性。有源 区域260位于已包括在半导体衬底253内的n阱262中。有源区域260和 有源区域261均具有沿第一方向(平行于x轴)延伸的长轴和沿第二方向 (平行于y轴)延伸的短轴。第二方向垂直于第一方向。有源区域260和 有源区域261相对于y轴分离。

56.栅极电极263被形成在有源区域260和有源区域261上并高于它们。 栅极电极263具有平行于y轴的长轴。在一些实施例中,栅极电极263形 成在多晶硅(poly)层中。栅极电极264位于栅极电极263的左侧并形成 在多晶硅层中。栅极电极264具有平行于y轴延伸的长轴。在该示例中, 栅极电极264是虚设电极并且未用于形成场效应晶体管(fet)。栅极电 极265位于栅极电极263的右侧并形成在多晶硅层中。栅极电极265具有 平行于y轴延伸的长轴。在该示例中,栅极电极265是虚设电极并且未用 于形成fet。栅极电极263、264、265相对于x轴分离。

57.nfet t0的示例(其在上文关于图2a讨论)位于拉低电路254中。 栅极电极263的一部分和有源区域261形成nfet t0。栅极电极263在有 源区域261上并高于有源区域261的部分是nfet t0的栅极gt0。有源区 域261在栅极gt0左侧的部分是nfet t0的源极st0,并且有源区域261 在栅极gt0右侧的部分是nfet t0的漏极dt0。

58.pfet t4的示例(其在上文关于图2a讨论)位于抗噪电路256中。 栅极电极263的一部分和有源区域260形成pfet t4。栅极电极263在有 源区域260上并高于有源区域260的部分是pfet t4的栅极gt4。有源区 域260在栅极gt4左侧的部分是pfet t4的第一漏极/源极ds1t4,并且 有源区域260在栅极gt4右侧的部分是pfet t4的第二漏极/源极ds2t4。 当电源电压vdd1处于第一状态时,第一漏极/源极ds1t4为pfet t4的 源极,并且第二漏极/源极ds2t4为pfet t4的漏极。当电源电压vdd1 处于第二状态时,第一漏极/源极ds1t4为pfet t4的漏极,并且第二漏 极/源极ds2t4为pfet t4的源极。

59.导体270具有平行于x轴延伸的长轴。导体270相对于y轴在有源区 域260和栅极电极263、264、265上方。导体270被配置为接收电源电压 vdd1。导体270对应于图2a中的电源节点212。导体271连接到导体 270并且具有平行于y轴延伸的长轴。导体271在第一漏极/源极ds1t4 之上延伸。过孔272(为清楚起见仅标记一个)将导体271连接到第一漏 极/源极ds1t4。

60.导体273连接到导体271并且具有平行于x轴延伸的长轴。导体273 在栅极电极263之上延伸。过孔274(为清楚起见仅标记一个)将导体 273连接到栅极电极263。

61.导体275具有平行于x轴延伸的长轴。导体275相对于y轴在有源区 域261和栅极电极263、264、265下方。导体275被配置为接收参考电压 vss。导体275对应于图2a中的地节点210。导体276连接到导体275并 且具有平行于y轴延伸的长轴。导体276在源极st0之上延伸。过孔277 (为清楚起见仅标记一个)将导体276连接到源极st0。

62.导体278具有平行于y轴延伸的长轴。导体278在第二漏极/源极 ds2t4之上和漏极dt0之上延伸。导体278对应于图2a中的跟随器节点 zn。过孔279(为清楚起见仅标记一个)将导体278连接到漏极/源极 ds2t4。过孔280(为清楚起见仅标记一个)将导体278连接到漏极dt0。

63.用于第一漏极/源极ds1t4、第二漏极/源极ds1t4、源极st0和漏极 dt0 ds1t4的端子接触件形成在金属到器件(md)层中,该md层相对 第三方向(平行于z轴,其在图2b中未示出但进出页面)在衬底之上。 第三方向垂直于第一方向和第二方向两者。过孔272、274、277、279、 280设置在过孔到器件(vd)层中。md层和vd层统称为md/vd层。 导体270、271、273、275、276、278位于金属层m0中。金属层m0是相 对于z轴在md/vd层之上的第一金属层。有源区域260、261形成为半导 体衬底253内的氧化物定义(od)区域。本文公开的布局图假设包括用于 生成布局图的各种设计规则的相应半导体工艺技术节点,并进一步假设设 计规则遵循编号约定,其中,第一级金属化(m_1st)和相应的第一级互 连结构(v_1st)相应地称为m0和v0。在一些实施例中,该编号约定假 设m_1st级和v_1st级相应地称为m1和v1。

64.在其他实施例中,导体270、271、273、275、276、278形成在其他 金属层(例如,金属层m1、金属层m2、金属层m3等)中,并且导体 270、271、273、275、276、278下方的过孔层和金属层中的导电组件将导 体270、271、273、275、276、278连接到布局图200b中的适当特征。

65.图3a是根据一些实施例的电路300a的电路图。

66.电路300a包括拉低电路304和抗噪电路206。拉低电路304是图1中 拉低电路104的示例。抗噪电路206在上面关于图2a进行了描述,并且 是图1中的抗噪电路106的一个示例。如先前关于图2a所讨论的,响应 于电源电压vdd2处于第一状态,寄生电容cp导致跟随器节点zn上的 跟随器电压出现寄生噪声电压。

67.拉低电路304还包括nfet t0,其具有连接到跟随器节点zn的漏极 和连接到地节点210的源极。然而,在该实施例中,拉低电路304还包括 nfet tl和pfet t2。nfet t1和pfet t2被配置为提供反馈效应,其确 保nfet t0响应于电源电压vdd1处于第一状态(例如,处于第一dc电 压电平)而保持导通。

68.在图3a中,nfet t0的栅极连接到中间节点net0。pfet t2的源极 连接到电源节点312。电源节点312被配置为接收电源电压vdd1。pfett2的漏极连接到电源节点312。pfet t2的栅极连接到中间节点net1。

69.nfet tl的栅极连接到中间节点net0并因此连接到pfet t2的漏极 和nfet t0的栅极。nfet t1的源极连接到参考节点314。参考节点314 被配置为接收参考电压vss。nfet t1的漏极连接到中间节点net1。因 此,nfet t1的漏极连接到pfet t2的栅极。

70.因此,当电源电压vdd1处于第一状态时,pfet t2被配置为将中间 节点net0拉向电源电压vdd1。作为响应,nfet t1导通并因此将中间 节点net1下拉向参考电压vss。作为

响应,pfet t2导通,使得中间节 点net0被拉向电源电压vdd1。因此,pfet t2对中间节点net0的上 拉通过nfet t1对中间节点net1的下拉而加强,反之亦然。这种反馈效 应确保nfet t0响应于电源电压vdd1被调整到第一状态而保持导通。

71.pfet t2和nfet t1都响应于电源电压vdd1处于第二状态而关断。 因此,nfet t0响应于电源电压vdd1处于第二状态而关断。

72.图3b是根据一些实施例的半导体电路的布局图300b。

73.半导体器件中的结构由布局图中的形状(也称为图案)表示。为了讨 论的简单起见,图3b(以及本文包括的其他图)的布局图中的元素将被 视为它们本身是结构而不是图案。布局图300b表示作为图3a所示的电路 300a的示例的半导体电路。图3b所示的半导体电路也是图1中的电路 101的示例。

74.布局图300b包括拉低电路354。布局图300b还包括与上文关于图 2b描述的抗噪电路256类似的抗噪电路356。

75.布局图300b包括半导体衬底253的一个实施例。半导体衬底253包 括n阱262、有源区域260和有源区域261,如上文关于图2a所述。布局 图300b还包括导体270、271、273、275、276、278和过孔272、274、 277、279、280,如上文关于图2a所述,不同在于导体273和过孔274仅 连接到栅极gt4而未连接到栅极gt0。在图3b中,栅极gt4和栅极gt0 由多晶硅层中的分离的栅极电极提供。栅极gt4的栅极电极在有源区域 260上延伸并高于有源区域260,并且栅极gt0的栅极电极在有源区域 261上延伸并高于有源区域261,但这些栅极电极是分离的。在图3b中, 导体273和通孔274仅连接到栅极gt4。

76.在该实施例中,有源区域360位于n阱262内并且在有源区域260左 侧。有源区域361在有源区域261左侧。有源区域360被掺杂以具有p型 导电性,而有源区域361被掺杂以具有n型导电性。有源区域360和有源 区域361均具有沿第一方向(平行于x轴)延伸的长轴和沿第二方向(平 行于y轴)延伸的短轴。第二方向垂直于第一方向。有源区域360和有源 区域361相对于x轴对准并相对于y轴分离。

77.栅极电极362在有源区域260和有源区域360之间形成在n阱262上 并高于n阱262。在该示例中,栅极电极362是虚设栅极电极。栅极电极 363在有源区域261和有源区域361之间形成在半导体衬底253上并高于 半导体衬底253。在该示例中,栅极电极362是虚设栅极电极。栅极电极 363在有源区域261和有源区域361之间形成在n阱361上并高于n阱 361。在该示例中,栅极电极363是虚设栅极电极。

78.pfet t2的栅极gt2(上面关于图3a讨论)由栅极电极形成,该栅 极电极具有平行于y轴的长轴并且在有源区域360上并高于有源区域360。 栅极gt2在栅极电极362左侧。nfet t1的栅极gt1(上面关于图3a讨 论)由栅极电极形成,该栅极电极具有平行于y轴的长轴并且在有源区域 361上并高于有源区域361。栅极gt1在栅极363左侧。

79.有源区域360在栅极gt2右侧的部分是pfet t2的漏极dt2。有源 区域360在栅极gt2左侧的部分是pfet t2的源极st2。有源区域361在 栅极gt1右侧的部分是nfet t1的源极st1。有源区域361在栅极gt1 左侧的部分是nfet t1的漏极dt1。有源区域360、361是半导体衬底 253中的od区域。

80.导体370具有平行于y轴延伸的长轴。导体270在pfet t2的漏极 dt2之上延伸。过孔371(为清楚起见仅标记一个)将漏极dt2连接到导 体370。导体372具有平行于x轴延伸的

长轴。导体372在栅极gt1、栅 极电极363和栅极gt0的顶部之上(相对于y轴在有源区域261、361之 上)延伸。过孔373(为清楚起见仅标记一个)将导体372连接到栅极 gt1,并且过孔374(为清楚起见仅标记一个)将导体372连接到栅极 gt0。导体372对应于图3a中的中间节点net0。

81.导体375具有平行于y轴延伸的长轴。导体375连接到导体270。导 体375也在pfet t2的源极st2之上延伸。过孔376(为清楚起见仅标记 一个)将导体375连接到源极st2。导体375对应于图3a中的电源节点 312。

82.导体377具有平行于y轴延伸的长轴。导体377也在nfet t1的漏极 dt1之上延伸。过孔378(为清楚起见仅标记一个)将导体377连接到漏 极dt1。导体379具有平行于x轴延伸的长轴。导体379连接到导体377 并在栅极gt2的底部(有源区域360下方)之上延伸。过孔380(为清楚 起见仅标记一个)将导体379连接到栅极gt2。导体377和导体379对应 于中间节点net1。

83.导体381具有平行于y轴延伸的长轴。导体381被配置为接收参考电 压vss。导体381在nfet t1的源极st1之上延伸。过孔382(为清楚起 见仅标记一个)将导体381连接到源极st1。导体381对应于图3a中的 地节点314。

84.导体370、373、375、377、379、381各自位于金属层m0中。过孔 371、373、374、376、378、380、382各自位于md/vd层中。在其他实 施例中,导体370、373、375、377、379、381被形成并且在其他金属层 (例如,金属层m1、金属层m2、金属层m3等)中,并且导体370、373、 375、377、379、381下方的过孔层和金属层中的导电组件将导体370、 373、375、377、379、381连接到布局图300b中的适当特征。

85.图4a是根据一些实施例的电路400a的电路图。

86.电路400a包括拉低电路404和抗噪电路206。拉低电路404是图1中 的拉低电路104的示例。抗噪电路206在上面关于图2a进行了描述,并 且是图1中的抗噪电路106的一个示例。如先前关于图2a所讨论的,响 应于电源电压vdd2处于第一状态,寄生电容cp导致跟随器节点zn上 的跟随器电压出现寄生噪声电压。

87.拉低电路404类似于图3a中的拉低电路304,不同在于拉低电路404 还包括pfet t3。pfet t3有助于在电源电压vdd1处于第一状态时上拉 中间节点net0。pfet t3的源极连接到电源节点412。电源节点412被配 置为接收电源电压vdd1。pfet t3的漏极和栅极都连接到中间节点 net0。因此,pfet t3以二极管配置连接。pfet t3被配置为响应于电源 电压vdd1处于第一状态而将中间节点net0上拉至电源电压vdd1或接 近电源电压vdd1。

88.图4b是根据一些实施例的半导体电路的布局图400b。

89.半导体器件中的结构由布局图中的形状(也称为图案)表示。为了讨 论的简单起见,图4b(以及本文包括的其他图)的布局图中的元素将被 视为它们本身是结构而不是图案。布局图400b表示作为图4a所示的电路 400a的示例的半导体电路。图4b所示的半导体电路也是图1中的电路 101的示例。

90.布局图400b包括抗噪电路456,其类似于上面关于图2b描述的抗噪 电路256。布局图400b还包括与上面关于图3b讨论的拉低电路354类似 的拉低电路454,不同在于拉低电路454包括pfet t3的示例(上面关于 图4a讨论的),并且pfet t2、pfet t3和pfet t4都形成在有源区域 460上而不是单独的有源区域上。

91.有源区域460具有平行于x轴延伸的长轴和平行于y轴延伸的短轴。 不同于图2a中的有源区域260、360,有源区域460中没有分离,使得有 源区域460是相对于x轴从栅极电极264附近延伸到栅极电极465附近的 od区域。在该示例中,栅极电极362是pfet t3的栅极gt3。有源区域 460在栅极t2左侧的部分是源极st2。有源区域460在栅极t2右侧和栅 极t3左侧的部分是pfet t2和pfet t3两者的漏极dt2、dt3。有源区 域460的一部分是pfet t3的源极st3,并且是pfet t4的第一漏极/源 极dst1t4。有源区域460在栅极t4右侧的部分是pfet t4的第二漏极/ 源极区域ds2t4。

92.此外,在该实施例中,导体470具有平行于x轴延伸的长轴。导体 470连接到导体370。导体470在有源区域460下方的栅极gt3的部分之 上延伸。过孔471(为清楚起见仅标记一个)将导体470连接到栅极gt3。

93.导体470位于金属层m0中。过孔471位于md/vd层中。在其他实 施例中,导体470被形成并且在其他金属层(例如,金属层m1、金属层 m2、金属层m3等)中,并且导体470下方的过孔层和金属层中的导电组 件将导体470连接到栅极gt3。

94.图4c是电压波形图,示出了图4a所示的电路400a的电源电压 vdd2、电源电压vdd1和跟随器节点zn处的跟随器电压。

95.顶部电压波形具有代表电源电压vdd2的电压曲线490,其中,顶部 电压图的纵轴代表电源电压vdd2的电压电平,并且顶部电压图的横轴代 表时间。

96.中间电压波形具有代表电源电压vdd1的电压曲线491,其中,中间 电压波形的纵轴代表电源电压vdd1的电压电平,并且中间电压波形的横 轴代表时间。

97.底部电压波形具有跟随器节点zn处的跟随器电压的电压曲线492, 其中,底部电压波形的纵轴代表跟随器电压的电压电平,并且底部电压波 形的横轴代表时间。

98.如电压曲线491所示,电源电压vdd1在标记为≈590ns到≈660ns 的整个时间间隔期间处于第二状态(例如,处于或接近0v)。

99.如电压曲线490所示,电源电压vdd2从标记为≈590ns的时间间隔 到标记为≈600ns的时间在第二状态(例如,处于或接近0v)中操作。

100.如电压曲线492所示,跟随器电压从标记为≈590ns的时间间隔到标 记为≈600ns的时间为≈0v。

101.在标记为≈600ns的时间,电压曲线490显示电源电压vdd2从第二 状态切换到第一状态(例如,处于或接近0.675v)。如电压曲线492所 示,这导致出现在跟随器节点zn处的跟随器电压的寄生噪声电压在标记 为≈600ns的时间附近上升至≈0.22v。

102.如电压曲线490所示,电源电压vdd2在标记为≈600ns到≈660ns 的时间间隔内保持在第一状态。

103.如电压曲线492所示,抗噪电路206(见图4a)使寄生噪声电压在标 记为≈600ns到≈660ns的时间间隔期间从≈0.22v放电到≈0.0916v。因 此,当电源电压vdd1处于第二状态并且电源电压vdd2处于第一状态时, 抗噪电路206减少了跟随器节点zn处的寄生噪声电压的影响。

104.图5a是根据一些实施例的电路500a的电路图。

105.电路500a包括拉低电路504和抗噪电路206。拉低电路504是图1中 的拉低电路104的示例。抗噪电路206在上面关于图2a进行了描述,并 且是图1中的抗噪电路106的一个示

例。如先前关于图2a所讨论的,响 应于电源电压vdd2处于第一状态,寄生电容cp导致跟随器节点zn上 的跟随器电压出现寄生噪声电压。

106.拉低电路504类似于图3a中的拉低电路304,不同在于拉低电路504 还包括nfet t5。nfet t5有助于在电源电压vdd1处于第一状态时将中 间节点net1下拉至参考电压vss或接近参考电压vss。nfet t5的源极 连接到地节点514。地节点514被配置为接收参考电压vss。nfet t5的 漏极和栅极都连接到中间节点net1。因此,nfet t5以二极管配置连接。 nfet t5被配置为响应于电源电压vdd1处于第一状态而将中间节点 net1下拉至参考电压vss或接近参考电压vss。

107.图5b是根据一些实施例的半导体电路的布局图500b。

108.半导体器件中的结构由布局图中的形状(也称为图案)表示。为了讨 论的简单起见,图5b(以及本文包括的其他图)的布局图中的元素将被 视为它们本身是结构而不是图案。布局图500b表示作为图5a所示的电路 500a的示例的半导体电路。图5b所示的半导体电路也是图1中的电路 101的示例。

109.布局图500b包括抗噪电路556,其类似于上面关于图2b描述的抗噪 电路256。布局图500b还包括与上面关于图3b讨论的拉低电路354类似 的拉低电路554,不同在于拉低电路554包括nfet t5的示例(上面关于 图5a讨论的),并且nfet t1和nfet t5形成在有源区域561上,栅极 电极562相对于x轴位于有源区域260、360和有源区域261、561之间, 并且栅极电极564位于栅极gt2、gt1和栅极电极564之间。

110.在图5b中,栅极电极562位于有源区域260、360和有源区域261、 561之间,而不是图3b的栅极电极362、363。因此,栅极电极562未分 离,而栅极电极362、363分离。栅极电极562的顶部相对于x轴在有源 区域260、261之间形成在n阱262上。栅极电极562的底部在有源区域 261、561之间形成在半导体衬底253上。

111.有源区域561位于半导体衬底253内。有源区域561是具有n型导电 性的od区域。有源区域561相对于y轴具有与图3b中的有源区域361 相同的高度,但相对于x轴具有图3b中的有源区域361两倍的长度。栅 极电极564的顶部形成在n阱262上。栅极电极564的顶部未用于形成 fet。

112.栅极电极564的底部形成在有源区域561上并高于有源区域561。栅 极电极564的底部是nfet t5的栅极gt5。在栅极gt5右侧,栅极gt1 也形成在有源区域561上并高于有源区域561。有源区域561在栅极gt1 右侧的部分是nfet t1的源极st1。有源区域561在栅极gt1左侧和 gt5右侧的部分是nfet t1和nfet t5两者的漏极dt1、dt5。有源区 域561在栅极gt5左侧的部分是nfet t5的源极st5。

113.导体570具有平行于x轴延伸的长轴。导体570在栅极电极564之上 延伸。过孔571(为清楚起见仅标记一个)将导体570连接到栅极gt5。 导体570连接到导体377。导体377和导体379对应于中间节点net1。在 图5b中,导体377形成在漏极dt1、dt5之上,并且过孔378将导体377 连接到漏极dt1、dt5。

114.导体572具有平行于y轴延伸的长轴。导体572连接到导体275。导 体572在源极st5之上延伸。过孔573将导体572连接到源极st5。导体 572对应于图5a中的地节点514。

115.导体570、572各自位于金属层m0中。过孔571、573各自位于 md/vd层中。在其他实施例中,导体570、572被形成并且在其他金属层 (例如,金属层m1、金属层m2、金属层m3等)

中,并且导体570、572 下方的过孔层和金属层中的导电组件将导体570、572连接到布局图500b 中的适当特征。

116.图6是根据一些实施例的电路600的电路图。

117.电路600包括拉低电路204和抗噪电路606。拉低电路204在上面关 于图2a进行了描述,并且是图1中的拉低电路104的一个示例。抗噪电 路606是图1中的抗噪电路106的示例。如先前关于图2a所讨论的,响 应于电源电压vdd2处于第一状态,寄生电容cp导致跟随器节点zn上 的跟随器电压出现寄生噪声电压。

118.抗噪电路606包括电容器连接pfet 602和电容器连接nfet 604。电 容器连接pfet 602连接在电源节点608和跟随器节点zn之间。电源节点 608被配置为接收电源电压vdd1。更具体地,电容器连接pfet 602的漏 极/源极端子都连接到电源节点608并因此彼此连接。电容器连接pfet602的栅极连接到跟随器节点zn。

119.在图6中,电容器连接nfet 604连接在地节点610和跟随器节点zn 之间。地节点610被配置为接收参考电压vss。更具体地,电容器连接 nfet 604的漏极/源极端子都连接到地节点610并因此彼此连接。电容器 连接nfet 604的栅极连接到跟随器节点zn。

120.在操作中,电容器连接pfet 602和电容器连接nfet 604被配置为将 跟随器节点zn处的跟随器电压出现的寄生噪声电压放电。更具体地,响 应于在电源电压vdd2处于第一状态时电源电压vdd1处于第二状态,即 在vdd1《vdd2时,跟随器节点zn处的寄生噪声电压通过对电容器连接 pfet 602充电而部分降低,并且还通过对电容器连接nfet 604充电而部 分降低。

121.图7a是根据一些实施例的电路700a的电路图。

122.电路700a包括拉低电路304和抗噪电路606。拉低电路304在上面关 于图3a进行了描述,并且是图1中的连接电路104的一个示例。抗噪电 路606在上面关于图6进行了描述,并且是图1中的抗噪电路106的一个 示例。如先前关于图2a所讨论的,响应于电源电压vdd2处于第一状态, 寄生电容cp导致跟随器节点zn上的跟随器电压出现寄生噪声电压。

123.图7b是根据一些实施例的半导体电路的布局图700b。

124.半导体器件中的结构由布局图中的形状(也称为图案)表示。为了讨 论的简单起见,图7b(以及本文包括的其他图)的布局图中的元素将被 视为它们本身是结构而不是图案。布局图700b表示作为图7a所示的电路 700a的示例的半导体电路。图7b所示的半导体电路也是图1中的电路 101的示例。

125.布局图700b包括拉低电路754,其是图7a中的拉低电路304的示例。 布局图700b还包括抗噪电路756。抗噪电路756是图7a中的抗噪电路 606的示例。在图7b中,有源区域360、pfet t2、导体370、过孔371、 导体375、过孔376、导体379、过孔380以与图3b中相同的方式布置在 图7b中。

126.在图7b中,nfet t0和nfet t1形成在半导体衬底内的有源区域 761上。有源区域761被掺杂以具有n型导电性,并且相对于y轴在有源 区域360下方。有源区域761相对于y轴具有与有源区域360相同的高度, 并且长度是有源区域360的两倍。有源区域761的左半部分相对于x轴与 有源区域360对齐。

127.有源区域762在n阱262内形成在有源区域360右侧。有源区域762 被掺杂以具有p型导电性。有源区域762相对于y轴与有源区域360对齐, 并且相对于x轴移位。有源区域762

相对于y轴具有与有源区域360相同 的高度,并且相对于x轴具有两倍的长度。

128.有源区域763在半导体衬底253内形成在有源区域761右侧。有源区 域763被掺杂以具有n型导电性。有源区域763相对于y轴与有源区域 761对齐,并且相对于x轴移位。有源区域761相对于y轴具有与有源区 域763相同的高度,并且相对于x轴具有两倍的长度。有源区域763相对 于x轴与有源区域762的右半部分对齐。

129.栅极gt1形成在有源区域761的左半部分上并高于有源区域761的左 半部分。栅极电极765形成在栅极gt2、gt1的右侧。栅极电极765具有 平行于y轴延伸的长轴。栅极电极765的顶部在有源区域360和有源区域 762之间在n阱262上并高于n阱262。栅极电极765的底部形成在有源 区域761上并高于有源区域761。栅极电极765位于多晶硅层中。栅极电 极765的底部是nfet t0的栅极gt0。

130.栅极电极766形成在栅极电极765的右侧。栅极电极765具有平行于 y轴延伸的长轴。栅极电极766的顶部在有源区域762的左半部分上并高 于有源区域762的左半部分。栅极电极766的底部在有源区域761和有源 区域763之间形成在半导体衬底253上并高于半导体衬底253。栅极电极 766位于多晶硅层。栅极电极766的顶部是电容器连接pfet 602的栅极 gpc的一部分。

131.栅极电极767形成在栅极电极766的右侧和栅极电极265的左侧。栅 极电极767具有平行于y轴延伸的长轴。栅极电极767的顶部在有源区域 762的右半部分上并高于有源区域762的右半部分。栅极电极767的底部 形成在有源区域763上并高于有源区域763。栅极电极767位于多晶层中。 栅极电极766的顶部是电容器连接pfet 602的栅极gpc的一部分,并且 栅极电极767的底部是电容器连接nfet 604的栅极gnc。

132.有源区域761在栅极gt1左侧的部分是nfet t1的漏极dt1。有源 区域761在栅极gt1右侧和栅极gt0左侧的部分是nfet t1和nfet t0 两者的源极st1、st0。有源区域761在栅极gt0右侧的部分是nfet t0 的漏极dt0。

133.有源区域762在栅极电极766左侧的部分是电容器连接pfet 602的 漏极/源极dsp1。有源区域762在栅极电极766右侧和栅极电极767左侧 的部分是电容器连接pfet 602的漏极/源极dsp2。有源区域762在栅极电 极767右侧的部分是电容器连接pfet 602的漏极/源极dsp3。

134.有源区域763在栅极电极767左侧的部分是电容器连接nfet 604的 漏极/源极dsn1。有源区域763在栅极电极767右侧的部分是电容器连接 nfet 604的漏极/源极dsn2。

135.导体770具有平行于y轴延伸的长轴。导体770在漏极/源极dsp1之 上延伸。导体770连接到导体270。过孔771(为清楚起见仅标记一个) 将导体770连接到漏极/源极dsp1。

136.导体772具有平行于y轴延伸的长轴。导体772在漏极/源极dsp2之 上延伸。导体772连接到导体270。过孔773(为清楚起见仅标记一个) 将导体772连接到漏极/源极dsp2。

137.导体774具有平行于y轴延伸的长轴。导体774在漏极/源极dsp3之 上延伸。导体774连接到导体270。过孔775(为清楚起见仅标记一个) 将导体774连接到漏极/源极dsp3。

138.导体776具有平行于x轴延伸的长轴。导体776在栅极电极766的顶 部和栅极电极767的顶部之上延伸。过孔777(为清楚起见仅标记一个) 将导体776连接到栅极电极766的顶部。过孔778(为清楚起见仅标记一 个)将导体776连接到栅极电极767的顶部。以此方式,栅极gpc的两个 部分彼此连接。

139.导体779具有平行于y轴延伸的长轴。导体779在漏极dt0之上延伸。 过孔780(为清楚起见仅标记一个)将导体779连接到漏极dt0。

140.导体781具有平行于x轴延伸的长轴。导体781在栅极电极767(即 栅极gnc)的底部之上延伸。过孔782(为清楚起见仅标记一个)将导体 781连接到栅极gnc。导体781对应于图7a中的跟随器节点zn。

141.导体783具有平行于y轴延伸的长轴。导体783在漏极/源极dsn1之 上延伸。导体783连接到导体275。过孔784(为清楚起见仅标记一个) 将导体783连接到漏极/源极dsn1。

142.导体785具有平行于y轴延伸的长轴。导体785在漏极/源极dsn2之 上延伸。导体785连接到导体275。过孔786(为清楚起见仅标记一个) 将导体785连接到漏极/源极dsn2。

143.导体770、772、774、776、779、781、783、785各自位于金属层m0 中。过孔771、773、775、777、778、780、782、784、786各自位于 md/vd层中。在其他实施例中,导体770、772、774、776、779、781、 783、785被形成并且在其他金属层(例如,金属层m1、金属层m2、金 属层m3等)中,并且导体770、772、774、776、779、781、783、785下 方的过孔层和金属层中的导电组件将导体770、772、774、776、779、781、 783、785连接到布局图700b中的适当特征。

144.图7c是电压波形图,示出了图7a所示的电路700a的电源电压 vdd2、电源电压vdd1和跟随器节点zn处的跟随器电压。

145.顶部电压波形具有电源电压vdd2的电压曲线790,其中,顶部电压 波形的纵轴代表电源电压vdd2的电压电平,并且顶部电压波形的横轴代 表时间。

146.中间电压波形具有电源电压vdd1的电压曲线791,其中,中间电压 波形的纵轴代表电源电压vdd1的电压电平,并且中间电压波形的横轴代 表时间。

147.底部电压波形具有跟随器节点zn处的跟随器电压的电压曲线792, 其中,底部电压波形的纵轴代表跟随器电压的电压电平,并且底部电压波 形的横轴代表时间。

148.如电压曲线791所示,电源电压vdd1在标记为≈590ns到≈660ns 的整个时间间隔期间处于第二状态(例如,处于或接近0v)。

149.如电压曲线790所示,电源电压vdd2从标记为≈590ns的时间间隔 到标记为≈600ns的时间在第二状态(例如,处于或接近0v)中操作。

150.如电压曲线792所示,跟随器电压从标记为≈590ns的时间间隔到标 记为≈600ns的时间为≈0v。

151.在标记为≈600ns的时间,电压曲线790显示电源电压vdd2从第二 状态切换到第一状态(例如,处于或接近0.675v)。如电压曲线792所 示,这导致出现在跟随器节点zn处的跟随器电压的寄生噪声电压在标记 为≈600ns的时间附近上升到≈0.16v。

152.如电压曲线790所示,电源电压vdd2在标记为≈600ns到≈660ns 的时间间隔保持在第一状态。

153.如电压曲线792所示,抗噪电路706(见图4a)使寄生噪声电压被抵 消,从而在标记为≈600ns到≈660ns的时间间隔期间从≈0.16v下降到 ≈0.131v。因此,当电源电压vdd1处于第二状态并且电源电压vdd2 处于第一状态时,抗噪电路706减少了跟随器节点zn处的寄生噪声电压 的影响。

154.图8a是根据一些实施例的电路800a的电路图。

155.电路800a包括拉低电路404和抗噪电路606。拉低电路404在上面关 于图4a进行了

描述,并且是图1中的拉低电路104的一个示例。抗噪电 路606在上面关于图6进行了描述,并且是图1中的抗噪电路106的一个 示例。如先前关于图2a所讨论的,响应于电源电压vdd2处于第一状态, 寄生电容cp导致跟随器节点zn上的跟随器电压出现寄生噪声电压。

156.图8b是根据一些实施例的半导体电路的布局图800b。

157.半导体器件中的结构由布局图中的形状(也称为图案)表示。为了讨 论的简单起见,图8b(以及本文包括的其他图)的布局图中的元素将被 视为它们本身是结构而不是图案。布局图800b表示作为图8a所示的电路 800a的示例的半导体电路。图8b所示的半导体电路也是图1中的电路 101的示例。

158.布局图800b包括拉低电路854,其是图8a中的拉低电路404的示例。 布局图800b还包括抗噪电路856。布局图800b类似于图7b中的布局图 700b,不同在于布局图800b包括pfet t3的表示,并且包括有源区域 860而不是有源区域360、762。

159.有源区域860相对于y轴具有与图7b中的有源区域360相同的高度, 但具有图7b中的有源区域360四倍的长度。有源区域860是被掺杂以具 有p型导电性的od区域。在图7b中,栅极电极765的顶部形成在有源 区域860上并高于有源区域860,并且是pfet t3的栅极gt3。

160.因此,有源区域860在栅极gt2左侧的部分是源极st3。有源区域 860在栅极gt2右侧和栅极gt3左侧的部分是pfet t2、t3两者的漏极 dt2、dt3。有源区域860在栅极gt3右侧和栅极电极766左侧的部分是 pfet t3的源极st3和电容器连接pfet 602的漏极/源极dsp1。有源区 域860在栅极电极766右侧和栅极电极767左侧的部分是电容器连接 pfet 602的漏极/源极dsp2。有源区域860在栅极电极767右侧的部分是 电容器连接pfet 602的漏极/源极dsp3。

161.不需要额外的导体,因为pfet t2、t3共享相同的漏极dt2、dt3, 并且因为栅极电极765提供pfet t3、t0的栅极gt3、gt0。如图7b所 讨论的导体770、772、774、776、779、781、783、785的连接从而提供 了形成图8a中的电路800a所需的连接。

162.图9a是根据一些实施例的电路900a的电路图。

163.电路900a包括拉低电路504和抗噪电路606。拉低电路504在上面关 于图5a进行了描述,并且是图1中的拉低电路104的一个示例。抗噪电 路606在上面关于图6进行了描述,并且是图1中的抗噪电路106的一个 示例。如先前关于图2a所讨论的,响应于电源电压vdd2处于第一状态, 寄生电容cp导致跟随器节点zn上的跟随器电压出现寄生噪声电压。

164.图9b是根据一些实施例的半导体电路的布局图900b。

165.半导体器件中的结构由布局图中的形状(也称为图案)表示。为了讨 论的简单起见,图9b(以及本文包括的其他图)的布局图中的元素将被 视为它们本身是结构而不是图案。布局图900b表示作为图9a所示的电路 900a的示例的半导体电路。图9b所示的半导体电路也是图1中的电路 101的示例。

166.布局图900b包括拉低电路954,其是图9a中的拉低电路504的示例。 布局图900b还包括抗噪电路956。布局图900b类似于图7b中的布局图 700b,不同在于布局图900b包括nfet t5的表示,并且包括有源区域 961而不是有源区域761。

167.有源区域961相对于y轴具有与图7b中的有源区域761相同的高度, 但相对于x轴具有比图7b中的有源区域761长≈1/3的长度。更具体地, 与有源区域761相比,有源区域

961相对于x轴向左延伸了该额外的≈1/3 额外长度。

168.在图9b中,栅极电极965位于栅极电极264和栅极gt2、gt1之间。 栅极电极965具有平行于y轴延伸的长轴。栅极电极965的顶部在n阱 962上并高于n阱962。栅极电极965的底部形成在有源区域961上并高 于有源区域961。栅极电极965的底部是nfet n5的栅极gt5。栅极电极 965位于多晶硅层中。

169.有源区域961在栅极gt5左侧的部分是nfet t5的源极st5。有源 区域961在栅极gt5和栅极gt1之间的部分是nfet t1和nfet t5两者 的漏极dt1、dt5。有源区域961在栅极gt1右侧和栅极gt0左侧的部 分是nfet t1、t0两者的源极st1、st0。有源区域961在栅极gt0右侧 的部分是nfet t0的漏极dt0。

170.导体970具有平行于x轴延伸的长轴。导体970在栅极电极965(即 栅极gt5)的底部之上延伸。过孔971(为清楚起见仅标记一个)将导体 970连接到栅极gt5。导体970连接到导体377。

171.导体972具有平行于y轴延伸的长轴。导体972在源极st5之上延伸。 导体972连接到导体275。过孔973(为清楚起见仅标记一个)将导体972 连接到源极st5。

172.导体970、972各自位于金属层m0中。过孔971、973各自位于 md/vd层中。在其他实施例中,导体970、972被形成并且在其他金属层 (例如,金属层m1、金属层m2、金属层m3等)中,并且导体970、972 下方的过孔层和金属层中的导电组件将导体970、972连接到布局图900b 中的适当特征。

173.图10是根据一些实施例的制造半导体器件的方法1000的流程图。

174.根据一些实施例,可以例如使用eda系统1300(图13,下面讨论) 和集成电路(ic)制造系统1400(图14,下面讨论)来实现方法1000。

175.在图10中,方法1000包括框1002-1004。在框1002,生成布局图。 在框1002生成的示例布局图包括图2b中的布局图200b、图3b中的布局 图300b、图4b中的布局图400b、图5b中的布局图500b、图6中的布 局图600、图7b中的布局图700b、图8b中的布局图800b、图9b中的 布局图900b等。

176.在框1004,基于布局图,执行下列项中的至少一项:(a)进行一次 或多次光刻曝光、或(b)制造一个或多个半导体掩模、或(c)制造半导 体器件的层中的一个或多个组件。参见以下对图14中的ic制造系统1400 的讨论。

177.图11是根据一些实施例的制造半导体电路的方法的流程图1100。

178.流程图1104是图10中的框1004的一个示例。半导体电路的示例包括 图1中的电路101、图2a中的电路200a、由图2b中的布局图200b表示 的电路、图3a中的电路300a、由图3b中的布局图300b表示的电路、图 4a中的电路400a、由图4b中的布局图400b表示的电路、图5a中的电 路500a、由图5b中的布局图500b表示的电路、图6中的电路600、图7a中的电路700a、由图7b中的布局图700b表示的电路、图8a中的电 路800a、由图8b中的布局图800b表示的电路、图9a中的电路900a、 以及由图9b中的布局图900b表示的电路。

179.在图11中,流程图1100包括框1102、1104和1106。流程开始于框 1102。在框1102,在半导体衬底中形成一个或多个有源区域。有源区域的 示例包括图2b中的有源区域260、261,图3b中的有源区域260、261、 360、361,图4b中的有源区域261、361、460,图5b中的有源区域260、 261、360、561,图7b中的有源区域360、761、762、763,图8b中的有 源区域761、

763、860,图9b中的有源区域360、762、763、961等。半 导体衬底的示例包括图1中的半导体衬底103以及图2b、图3b、图4b、 图5b、图7b、图8b、图9b中的半导体衬底等。然后流程进行到框1104。

180.在框1104,在一个或多个有源区域之上形成一个或多个栅极电极,使 得与一个或多个有源区域相应地形成场效应晶体管(fet),fet包括被 指定用于拉低电路的一个或多个第一fet以及被指定用于抗噪电路的一个 或多个第二fet。栅极电极的示例包括图2b中的栅极电极263,图3b中 的栅极gt0、gt1、gt2、gt4,图4b中的栅极gt0、gt1、gt2、gt3、 gt4,图5b中的栅极电极564和栅极gt0、gt1、gt2、gt3、gt4,图 7b中的栅极电极765、766、767和栅极gt1、gt2,图8b中的栅极电极 765、766、767和栅极gt1、gt2,以及图9b中的栅极电极765、766、 767、965和栅极gt1、gt2。第一fet的示例包括图2b中的nfet t0, 图3b和图7b中的fet t0、t1、t2,图4b和图8b中的fet t0、t1、 t2、t3,以及图5b和图9b中的fet t0、t1、t2、t5。第二fet的示 例包括图2b、图3b、图4b、图5b中的pfet t4,以及图7b、图8b和 图9b中的fet 602、604。拉低电路的示例包括图2b中的拉低电路254、 图3b中的拉低电路354、图4b中的拉低电路454、图5b中的拉低电路 554、图7b中的拉低电路754、图8b中的拉低电路854、图9b中的拉低 电路954等。抗噪电路的示例包括图2b中的抗噪电路256、图3b中的抗 噪电路356、图4b中的抗噪电路456、图5b中的抗噪电路556、图7b中 的抗噪电路756、图8b中的抗噪电路856、以及图9b中的抗噪电路956 等。然后流程进行到框1106。

181.在框1106,形成导体和过孔,这些导体和过孔连接fet而使得一个 或多个第一fet被连接以表示拉低电路并且一个或多个第二fet被连接 以表示抗噪电路,拉低电路连接到跟随器节点并被配置为接收地电压和第 一电源电压,第一电源电压被配置为至少呈现第一状态和第二状态,拉低 电路被配置为响应于第一电源电压处于第一状态而将跟随器电压拉向地电 压以及响应于第一电源电压处于第二状态而不将跟随器电压拉向地电压, 并且抗噪电路连接到跟随器节点,且抗噪电路被配置为在第一电源电压处 于第二状态时保护跟随器节点处的跟随器电压不因噪声电压而失真。导体 的示例是上面讨论的图2b、图3b、图4b、图5b、图7b、图8b、图9b 中的金属层m0中的导体,并且过孔的示例是上面讨论的形成在图2b、图 3b、图4b、图5b、图7b、图8b、图9b等中的md/vd层中的过孔。跟 随器节点的示例是图2b、图3b、图4b、图5b、图7b、图8b、图9b等 中的跟随器节点zn。地电压的示例是图2b、图3b、图4b、图5b、图 7b、图8b、图9b等中的参考电压vss。第一电源电压的示例是图2b、 图3b、图4b、图5b、图7b、图8b、图9b等中的电源电压vdd1。

182.图12是根据一些实施例的保护电路免受寄生噪声影响的方法的流程 图1200。

183.流程图1200的方法对应于图1、图2a、图3a、图4a、图5a、图6、 图7a、图8a、图9a等的电路的操作。流程图1200包括框1202-1210。

184.流程开始于框1202。在框1202,在跟随器电路处接收第一电源电压, 跟随器电路耦合到跟随器节点,第一电源电压被配置为处于第一状态或第 二状态。跟随器电路的示例是图1中的跟随器电路108。跟随器节点的示 例是图1、图2a、图2b、图3a、图3b、图4a、图4b、图5a、图5b、 图6、图7a、图7b、图8a、图8b、图9a、图9b中的跟随器节点zn。 第一电源电压的示例是电源电压vdd2。电源电压vdd2的示例在图2a、 图2b、图3a、图3b、图4a、图4b、图5a、图5b、图6、图7a、图 7b、图8a、图8b、图9a、图9b、图4c中的电压波形490、以及图7c 中的电压波形790中示出。流程进行到框1204。

185.在框1204处,在拉低电路的控制节点处接收第二电源电压,该拉低 电路耦合在跟随器节点和具有地电压的第一参考节点之间,第二电源电压 被配置为处于第一状态或第二状态。第二电源电压的示例是电源电压 vdd1。电源电压vdd1的示例在图2a、图2b、图3a、图3b、图4a、 图4b、图5a、图5b、图6、图7a、图7b、图8a、图8b、图9a、图 9b、图4c中的电压波形491、以及图7c中的电压波形791中示出。在图 4c和图7c中,电源电压vdd1被示为处于第二状态。然后流程进行到框 1206。控制节点的示例是图2a、图3a、图4a、图5a、图6、图7a、图 8a、图9a中的nfet t0的栅极。拉低电路的示例是图1中的拉低电路 104、图2a和图6中的拉低电路204、图3a和图7a中的拉低电路304、 图4a和图8a中的低电路404、图5a和图9a中的拉低电路504、图2b 中的拉低电路254、图3b中的拉低电路354、图4b中的拉低电路454、 图5b中的拉低电路554、图7b中的拉低电路754、图8b中的拉低电路 854、以及图9b中的拉低电路954。然后流程进行到框1206。

186.在框1206,当第二电源电压处于第一状态时,控制拉低电路将跟随器 节点处的电压电平拉向地电压。示例在图4c中的电压波形492和图7c中 的电压波形792中在标记为590ns的时间之前示出。然后流程进行到框 1208。

187.在框1208,当第二电源电压处于第二状态时,控制拉低电路不将跟随 器节点处的电压电平拉向地电压。示例在图4c中的电压波形492和图7c 中的电压波形792中在标记为590ns的时间之后示出。然后流程进行到框 1210。

188.在框1210,对于耦合在跟随器节点和具有第二电源电压的至少第二参 考节点之间的抗噪电路,当第二电源电压处于第二状态时,使用抗噪电路 来保护跟随器节点处的电压电平不因寄生噪声电压而失真,寄生噪声电压 对跟随器节点是电容性的,寄生噪声电压基于第一电源电压对跟随器节点 的寄生电容耦合。示例在图4c中的电压波形492和图7c中的电压波形 792中示出,寄生噪声电压在标记为590ns的时间之后下降。抗噪电路的 示例包括图1中的抗噪电路106,图2a、图3a、图4a、图5a中的抗噪 电路206,图6、图7a、图8a、图9a中的抗噪电路606,图2b中的抗 噪电路256,图3b中的抗噪电路356,图4b中的抗噪电路456,图5b中 的抗噪电路556,图7b中的抗噪电路756,图8b中的抗噪电路856,以 及图9b中的抗噪电路956。然后流程进行到框1206。

189.图13是根据一些实施例的eda系统1300的框图。

190.在一些实施例中,eda系统1300包括apr系统。根据一些实施例, 本文描述的根据一个或多个实施例的设计布局图的方法可以例如使用eda 系统1300来实施。

191.在一些实施例中,eda系统1300是通用计算设备,包括硬件处理器 1302和非暂态计算机可读存储介质1304。存储介质1304还编码有(即存 储)计算机程序代码1306,即一组可执行指令。由硬件处理器1302执行 指令1306(至少部分地)表示实施本文描述的根据一个或多个实施例的方 法(在下文中,所述过程和/或方法)的一部分或全部的eda工具。

192.处理器1302通过总线1308电耦合至计算机可读存储介质1304。处理 器1302还通过总线1308电耦合至i/o接口1310。网络接口1312也通过总 线1308电连接到处理器1302。网络接口1312连接到网络1314,以便处 理器1302和计算机可读存储介质1304能够通过网络1314连接到外部元件。 处理器1302被配置为执行编码在计算机可读存储介质1304中的计算机程 序代码1306,以使eda系统1300可用于执行所述过程和/或方法的一部 分或全部。在一个或多个实施例中,处理器1302是中央处理单元(cpu)、 多处理器、分布式处理系

统、专用集成电路(asic)、和/或合适的处理 单元。

193.在一个或多个实施例中,计算机可读存储介质1304是电、磁、光、 电磁、红外、和/或半导体系统(或装置或设备)。例如,计算机可读存储 介质1304包括半导体或固态存储器、磁带、可移动计算机磁盘、随机存 取存储器(ram)、只读存储器(rom)、刚性磁盘、和/或光盘。在使 用光盘的一个或多个实施例中,计算机可读存储介质1304包括光盘只读 存储器(cd-rom)、读/写光盘(cd-r/w)、和/或数字视频光盘 (dmd/vd)。

194.在一个或多个实施例中,存储介质1304存储计算机程序代码1306, 该计算机程序代码1306被配置为使系统1300(其中这种执行(至少部分 地)代表eda工具)可用于执行所述过程和/或方法的一部分或全部。在 一个或多个实施例中,存储介质1304还存储有助于执行所述过程和/或方 法的一部分或全部的信息。在一个或多个实施例中,存储介质1304存储 标准单元(包括本文所公开的这种标准单元)的库1307。在一个或多个实 施例中,存储介质1304存储与本文公开的一个或多个布局相对应的一个 或多个布局图1309。

195.eda系统1300包括i/o接口1310。i/o接口1310耦合到外部电路。 在一个或多个实施例中,i/o接口1310包括用于将信息和命令传送到处理 器1302的键盘、小键盘、鼠标、轨迹球、触控板、触摸屏、和/或光标方 向键。

196.eda系统1300还包括耦合到处理器1302的网络接口1312。网络接 口1312允许eda系统1300与网络1314进行通信,一个或多个其他计算 机系统连接到网络1314。网络接口1312包括:无线网络接口,例如,蓝 牙、wifi、wimax、gprs或wcdma;或有线网络接口,例如,以太 网、usb或ieee-1364。在一个或多个实施例中,在两个或更多个系统 1300中实施所述过程和/或方法的一部分或全部。

197.系统1300被配置为通过i/o接口1310接收信息。通过i/o接口1310 接收的信息包括指令、数据、设计规则、标准单元库、和/或用于由处理器 1302处理的其他参数中的一个或多个。信息经由总线1308传输到处理器 1302。eda系统1300被配置为通过i/o接口1310接收与ui相关的信息。 该信息作为用户界面(ui)1342存储在计算机可读介质1304中。

198.在一些实施例中,所述过程和/或方法的一部分或全部被实现为用于由 处理器执行的独立软件应用。在一些实施例中,所述过程和/或方法的一部 分或全部被实现为作为附加软件应用的一部分的软件应用。在一些实施例 中,所述过程和/或方法的一部分或全部被实现为软件应用的插件。在一些 实施例中,所述过程和/或方法中的至少一个被实现为作为eda工具的一 部分的软件应用。在一些实施例中,所述过程和/或方法的一部分或全部被 实现为eda系统1300所使用的软件应用。在一些实施例中,使用诸如可 从铿腾电子科技有限公司(cadence design systems,inc.)获得的 之类的工具、或另一合适的布局生成工具来生成包括标准单 元的布局图。

199.在一些实施例中,这些过程被实现为存储在非暂态计算机可读记录介 质中的程序的功能。非暂态计算机可读记录介质的示例包括但不限于外部/ 可移动和/或内部/内置存储装置或存储器单元,例如,光盘(例如, dmd/vd)、磁盘(例如,硬盘)、半导体存储器(例如,rom、 ram)、存储卡等中的一项或多项。

200.图14是根据一些实施例的ic制造系统1400的框图及与其相关联的 ic制造流程。

201.在一些实施例中,基于布局图,使用制造系统1400来制造下列项中 的至少一项:(a)一个或多个半导体掩模、或(b)半导体集成电路的层 中的至少一个组件。

202.在图14中,ic制造系统1400包括在与制造ic器件1460有关的设计、 开发、以及制造周期和/或服务中彼此交互的实体,例如,设计室1420、 掩模室1430和ic制造商/制造者(“fab”)1450。系统1400中的实体通 过通信网络连接。在一些实施例中,通信网络是单个网络。在一些实施例 中,通信网络是各种不同的网络,例如,内部网和互联网。通信网络包括 有线和/或无线通信信道。每个实体与一个或多个其他实体进行交互,并向 一个或多个其他实体提供服务和/或从一个或多个其他实体接收服务。在一 些实施例中,设计室1420、掩模室1430和ic制造商/制造者1450中的两 个或更多个由单个较大公司拥有。在一些实施例中,设计室1420、掩模室 1430和ic制造商/制造者1450中的两个或更多个在公共设施中共存并使用 公共资源。

203.设计室(或设计团队)1420生成ic设计布局图1422。ic设计布局图 1422包括为ic器件1460设计的各种几何图案。几何图案对应于组成要制 造的ic器件1460的各种组件的金属、氧化物、或半导体层的图案。各个 层进行组合以形成各种ic特征。例如,ic设计布局图1422的一部分包括 在半导体衬底(例如,硅晶圆)中形成的各种ic特征(例如,有源区域、 栅极电极、源极和漏极、层间互连的金属线或过孔、以及焊盘的开口)、 以及设置在半导体衬底上的各种材料层。设计室1420实施适当的设计过 程以形成ic设计布局图1422。设计过程包括逻辑设计、物理设计、或布 局和布线中的一个或多个。ic设计布局图1422呈现在具有几何图案信息 的一个或多个数据文件中。例如,ic设计布局图1422以gdsii文件格式 或dfii文件格式表达。

204.掩模室1430包括数据准备1432和掩模制造1444。掩模室1430使用 ic设计布局图1422来制造一个或多个掩模1445,其被用来根据ic设计布 局图1422制造ic器件1460的各个层。掩模室1430执行掩模数据准备 1432,其中,ic设计布局图1422被转换成代表性数据文件(“rdf”)。 掩模数据准备1432将rdf提供给掩模制造1444。掩模制造1444包括掩 模写入器。掩模写入器将rdf转换为衬底上的图像,例如,掩模(调制盘) 1445或半导体晶圆1453。掩模数据准备1432处理设计布局图1422,以符 合掩模写入器的特定特性和/或ic制造商/制造者1450的要求。在图14中, 掩模数据准备1432和掩模制造1444被示为单独的要素。在一些实施例中, 掩模数据准备1432和掩模制造1444被统称为掩模数据准备。

205.在一些实施例中,掩模数据准备1432包括光学接近校正(opc),其 使用光刻增强技术来补偿图像误差,例如,可能由衍射、干涉、其他工艺 影响等引起的图像误差。opc调整ic设计布局图1422。在一些实施例中, 掩模数据准备1432包括进一步的分辨率增强技术(ret),例如,离轴照 明、子分辨率辅助特征、相移掩模、其他合适的技术等、或其组合。在一 些实施例中,还使用反光刻技术(ilt),其将opc视为反成像问题。

206.在一些实施例中,掩模数据准备1432包括掩模规则检查器(mrc), 其利用一组掩模创建规则来检查已经在opc中进行过处理的ic设计布局 图1422,该组掩模创建规则包含某些几何和/或连接性限制以确保足够的 余量,以考虑半导体制造工艺中的可变性等。在一些实施例中,mrc修 改ic设计布局图1422以补偿掩模制造1444期间的限制,这可以撤消由 opc执行的部分修改以满足掩模创建规则。

207.在一些实施例中,掩模数据准备1432包括光刻工艺检查(lpc),其 模拟将由ic制造商/制造者1450实施以制造ic器件1460的工艺。lpc基 于ic设计布局图1422来模拟该工艺以创建模拟制造器件,例如,ic器件 1460。lpc模拟中的工艺参数可以包括与ic制造周期

的各个工艺相关联 的参数、与用于制造ic的工具相关联的参数、和/或制造工艺的其他方面。 lpc考虑了各种因素,例如,航空图像对比度、焦深(dof)、掩模误差 增强因素(meef)、其他合适的因素等、或其组合。在一些实施例中, 在通过lpc创建了模拟制造器件之后,如果模拟器件在形状上不够接近以 满足设计规则,则重复opc和/或mrc以进一步完善ic设计布局图1422。

208.应当理解,为了清楚起见,掩模数据准备1432的以上描述已被简化。 在一些实施例中,数据准备1432包括诸如逻辑运算(lop)之类的附加特 征,以根据制造规则来修改ic设计布局图1422。此外,可以以各种不同 的顺序执行在数据准备1432期间应用于ic设计布局图1422的处理。

209.在掩模数据准备1432之后并且在掩模制造1444期间,基于经修改的 ic设计布局图1422来制造掩模1445或一组掩模1445。在一些实施例中, 掩模制造1444包括基于ic设计布局图1422来执行一个或多个光刻曝光。 在一些实施例中,基于经修改的ic设计布局图1422,使用电子束(e

‑ꢀ

beam)或多个电子束的机制来在掩模(光掩模或调制盘)1445上形成图案。 以各种技术形成掩模1445。在一些实施例中,掩模1445是使用二进制技 术形成的。在一些实施例中,掩模图案包括不透明区域和透明区域。用于 曝光已经涂覆在晶圆上的图像敏感材料层(例如,光致抗蚀剂)的辐射束 (例如,紫外线(uv)束)被不透明区域阻挡并透射通过透明区域。在 一个示例中,掩模1445的二元掩模版本包括透明衬底(例如,熔融石英) 以及涂覆在二元掩模的不透明区域中的不透明材料(例如,铬)。在另一 示例中,使用相移技术形成掩模1445。在掩模1445的相移掩模(psm) 版本中,在相移掩模上形成的图案中的各个特征被配置为具有适当的相差 以增强分辨率和成像质量。在各个示例中,相移掩模是衰减psm或交替 psm。由掩模制造1444生成的(一个或多个)掩模被用于各个工艺中。 例如,这样的(一个或多个)掩模被用于离子注入工艺以在半导体晶圆1453中形成各种掺杂区域、被用于蚀刻工艺以在半导体晶圆1453中形成 各种蚀刻区域、和/或被用于其他合适的工艺。

210.ic制造商/制造者1450是ic制造企业,其包括一个或多个用于制造各 种不同的ic产品的制造设施。在一些实施例中,ic制造商/制造者1450是 半导体铸造厂。例如,可能存在用于多个ic产品的前端制造(前端 (feol)制造)的制造设施,而第二制造设施可以提供用于互连和封装 ic产品的后端制造(后端(beol)制造),并且第三制造设施可以为铸 造企业提供其他服务。

211.ic制造商/制造者1450包括制造工具1452,其被配置为对半导体晶圆 1453执行各种制造操作,使得根据(一个或多个)掩模(例如,掩模 1445)来制造ic器件1460。在各种实施例中,制造工具1452包括下列项 中的一项或多项:晶圆步进机、离子注入机、光致抗蚀剂涂布机、处理室 (例如,cmd/vd室或lpcmd/vd炉)、cmp系统、等离子体蚀刻系统、 晶圆清洁系统、或能够执行如本文所讨论的一个或多个合适的制造工艺的 其他制造设备。

212.ic制造商/制造者1450使用由掩模室1430制造的(一个或多个)掩模 1445来制造ic器件1460。因此,ic制造商/制造者1450至少间接地使用 ic设计布局图1422来制造ic器件1460。在一些实施例中,半导体晶圆 1453由ic制造商/制造者1450使用(一个或多个)掩模1445来制造以形 成ic器件1460。在一些实施例中,ic制造包括至少间接地基于ic设计布 局图1422来执行一次或多次光刻曝光。半导体晶圆1453包括硅衬底、或 在其上形成有材料

层的其他合适的衬底。半导体晶圆1453还包括(在随 后的制造步骤形成的)各种掺杂区域、电介质特征、多级互连等中的一个 或多个。

213.关于集成电路(ic)制造系统(例如,图14的系统1400)以及与其 相关联的ic制造流程的详细信息可以在例如2016年2月9日授权的美国 专利no.9,256,709、2015年10月1日公开的美国授权前公开no. 20150278429、2014年2月6日公开的美国授权前公开no.20140040838、 以及2007年8月21日授权的美国专利no.7,260,442中找到,它们中的每 一个通过引用整体结合于此。

214.在一些实施例中,一种修整(shape)跟随器电路的跟随器电压的电路, 该电路包括:拉低电路,连接在跟随器节点和第一参考电压之间,该拉低 电路响应第二参考电压,跟随器节点能连接到跟随器电路;以及抗噪电路, 连接在跟随器节点和第二参考电压之间,抗噪电路被配置为保护跟随器节 点处的跟随器电压不因电容耦合到跟随器节点的噪声电压而失真。

215.在一些实施例中,第一参考电压是地电压;第二参考电压是具有波动 的电平的第一电源电压;并且拉低电路还被配置为:响应于第一电源电压 的电平超过拉低电路的阈值电平而将跟随器节点下拉向地电压;以及响应 于第一电源电压的电平下降到低于拉低电路的阈值电平而基本上不影响跟 随器节点。在一些实施例中,电容耦合到跟随器节点的噪声电压包括由跟 随器电路的电源域中的第二电源电压产生的寄生电压;并且抗噪电路还被 配置为通过下列项的至少一项来保护跟随器节点:1)将跟随器节点处的 寄生电压放电,或者2)抵消跟随器节点处的寄生电压。在一些实施例中, 抗噪电路包括:电源节点,被配置为接收第一电源电压;以及二极管连接 场效应晶体管(fet),连接在电源节点和跟随器节点之间,使得二极管 连接fet被正向偏置,以便在第一电源电压的电平小于寄生电压的电平时 通过电源节点将跟随器节点放电。在一些实施例中,二极管连接fet是p 沟道fet(pfet),该pfet具有第一漏极/源极端子、第二漏极/源极端 子和栅极端子;第一漏极/源极端子连接到电源节点;栅极端子连接到第一 漏极/源极;并且第二漏极/源极端子连接到跟随器节点。在一些实施例中, 抗噪电路包括:连接到跟随器节点的电容器连接p沟道场效应晶体管 (pfet),以及连接到跟随器节点的电容器连接n沟道场效应晶体管 (nfet);并且电容器连接pfet和电容器连接nfet被配置为抵消跟随 器节点处的噪声电压。在一些实施例中,抗噪电路还包括:电源节点,被 配置为接收第一电源电压;地节点,被配置为接收地电压;电容器连接 pfet连接在跟随器节点和电源节点之间;并且电容器连接nfet连接在 跟随器节点和地节点之间。在一些实施例中,拉低电路包括:第一地节点, 被配置为接收地电压;第一n沟道场效应晶体管(nfet),具有耦合到 跟随器节点的第一漏极、耦合到地节点的第一源极、以及第一栅极,该第 一栅极响应第一电源电压而使得第一nfet被配置为执行下列项:响应于 第一电源电压关闭而关断以使跟随器节点被设置为浮置;以及响应于第一 电源电压开启而导通以使跟随器节点被设置为地电压。在一些实施例中, 第一栅极被连接以接收第一电源电压。在一些实施例中,拉低电路还包括: 第一电源节点,被配置为接收第一电源电压;第二地节点,被配置为接收 地电压;第一pfet,具有第二源极、第二漏极和第二栅极;以及第二 nfet,具有第三源极、第三漏极和第三栅极;其中:第二源极连接到第 一电源节点;第二漏极连接到第一栅极;第二栅极连接到第三漏极;第三 栅极连接到第一栅极;并且第三源极连接到第二地节点。在一些实施例中, 拉低电路还包括:第二电源节点,

被配置为接收第一电源电压;第二 pfet,具有第四源极、第四漏极和第四栅极;第四源极连接到第二电源节 点;第四漏极连接到第一栅极;并且第四栅极连接到第一栅极。在一些实 施例中,拉低电路还包括:第三地节点,被配置为接收地电压;以及第三 nfet,具有第四源极、第四漏极和第四栅极;第四源极连接到第三地节 点;第四漏极连接到第二栅极并连接到第三漏极;并且第四栅极连接到第 四漏极。

216.在一些实施例中,一种保护电路免受寄生噪声影响的方法,该方法包 括:在跟随器电路处接收第一电源电压,跟随器电路耦合到跟随器节点, 第一电源电压被配置为处于第一状态或第二状态;在拉低电路的控制节点 处接收第二电源电压,该拉低电路耦合在跟随器节点和具有地电压的第一 参考节点之间,第二电源电压被配置为处于第一状态或第二状态;当第二 电源电压处于第一状态时,控制拉低电路将跟随器节点处的电压电平拉向 地电压;当第二电源电压处于第二状态时,控制拉低电路不将跟随器节点 处的电压电平拉向地电压;以及对于耦合在跟随器节点和具有第二电源电 压的至少第二参考节点之间的抗噪电路,当第二电源电压处于第二状态时, 使用抗噪电路来保护跟随器节点处的电压电平不因寄生噪声电压而失真, 寄生噪声电压对跟随器节点是电容性的,寄生噪声电压基于第一电源电压 对跟随器节点的寄生电容耦合。

217.在一些实施例中,抗噪电路包括:二极管连接场效应晶体管(fet), 连接在第二参考节点和跟随器节点之间;并且使用抗噪电路进行保护包括: 当第二电源电压处于第一状态时,将二极管连接fet反向偏置;并且当第 二电源电压处于第二状态时,将二极管连接fet正向偏置,以通过第二参 考节点将跟随器节点放电。在一些实施例中,二极管连接fet包括p沟道 fet(pfet),该pfet具有第一漏极/源极、第二漏极/源极和栅极;第 一漏极/源极与栅极中的每一个连接到第二参考节点;并且第二漏极/源极 连接到跟随器节点。在一些实施例中,抗噪电路包括:电容器连接p沟道 场效应晶体管(pcap),耦合在第二参考节点和跟随器节点之间;并且 使用抗噪电路进行保护包括:当第二电源电压处于第一状态时,使用跟随 器节点处的寄生噪声电压对pcap进行充电,从而减少寄生噪声电压对跟 随器节点处的电压电平的贡献。在一些实施例中,抗噪电路还包括:电容 器连接n沟道场效应晶体管(ncap),耦合在跟随器节点和第一参考节 点之间;并且使用抗噪电路进行保护还包括:当第二电源电压处于第一状 态时,使用跟随器节点处的寄生噪声电压对ncap进行充电,从而进一步 减少寄生噪声电压对跟随器节点处的电压电平的贡献。

218.在一些实施例中,一种制造半导体器件的方法,该方法包括:在半导 体衬底中形成一个或多个有源区域;在一个或多个有源区域之上形成一个 或多个栅极电极,使得与一个或多个有源区域相应地形成场效应晶体管 (fet),fet包括:被指定用于拉低电路的一个或多个第一fet;以及 被指定用于抗噪电路的一个或多个第二fet;形成导体和过孔,这些导体 和过孔连接fet而使得:一个或多个第一fet被连接以表示拉低电路; 一个或多个第二fet被连接以表示抗噪电路;拉低电路连接到跟随器节点 并被配置为接收地电压和第一电源电压;第一电源电压被配置为至少呈现 第一状态和第二状态;拉低电路被配置为响应于第一电源电压处于第一状 态而将跟随器电压拉向地电压,以及响应于第一电源电压处于第二状态而 不将跟随器电压拉向地电压;以及抗噪电路连接到跟随器节点,抗噪电路 被配置为在第一电源电压处于第二状态时保护跟随器节点处的跟随电压不 因噪声电压而失真。在一些实施例中,一个或多个第二fet包括连接到跟 随器节点的二极管连接fet。在

一些实施例中,一个或多个第二fet包括: 连接到跟随器节点的电容器连接p沟道fet;以及连接到跟随器节点的电 容器连接n沟道fet。

219.以上概述了若干实施例的特征,使得本领域技术人员可以更好地理解 本公开的各方面。本领域技术人员应当理解,他们可以容易地使用本公开 作为设计或修改其他工艺和结构以实现本文介绍的实施例的相同目的和/或 实现本文介绍的实施例的相同优点的基础。本领域技术人员还应该认识到, 这样的等同构造不脱离本公开的精神和范围,并且他们可以在不脱离本公 开的精神和范围的情况下在本文中进行各种改变、替换和变更。

220.示例1.一种修整跟随器电路的跟随器电压的电路,该电路包括:

221.拉低电路,连接在跟随器节点和第一参考电压之间,所述拉低电路响 应第二参考电压,所述跟随器节点能连接到所述跟随器电路;以及

222.抗噪电路,连接在所述跟随器节点和所述第二参考电压之间,所述抗 噪电路被配置为保护所述跟随器节点处的所述跟随器电压不因电容耦合到 所述跟随器节点的噪声电压而失真。

223.示例2.根据示例1所述的电路,其中,

224.所述第一参考电压是地电压;

225.所述第二参考电压是以第一状态和第二状态操作的第一电源电压;并 且

226.所述拉低电路还被配置为:

227.响应于当所述第一电源电压处于所述第一状态时所述第一电源电 压的电平超过所述拉低电路的阈值电平,将所述跟随器节点下拉向所 述地电压;以及

228.响应于当所述第一电源电压处于所述第二状态时所述第一电源电 压的电平下降到低于所述拉低电路的阈值电平,基本上不影响所述跟 随器节点。

229.示例3.根据示例2所述的电路,其中,

230.电容耦合到所述跟随器节点的噪声电压包括由所述跟随器电路的电源 域中的第二电源电压产生的寄生电压;并且

231.所述抗噪电路还被配置为通过下列项的至少一项来保护所述跟随器节 点:1)将所述跟随器节点处的所述寄生电压放电,或者2)抵消所述跟随 器节点处的所述寄生电压。

232.示例4.根据示例2所述的电路,其中,所述抗噪电路包括:

233.电源节点,被配置为接收所述第一电源电压;以及

234.二极管连接场效应晶体管(fet),连接在所述电源节点和所述跟随 器节点之间,使得所述二极管连接fet被正向偏置,以便在所述第一电源 电压的电平小于所述寄生电压的电平时通过所述电源节点将所述跟随器节 点放电。

235.示例5.根据示例4所述的电路,其中,

236.所述二极管连接fet是p沟道fet(pfet),该pfet具有第一漏极 /源极端子、第二漏极/源极端子和栅极端子;

237.所述第一漏极/源极端子连接到所述电源节点;

238.所述栅极端子连接到所述第一漏极/源极;并且

239.所述第二漏极/源极端子连接到所述跟随器节点。

240.示例6.根据示例2所述的电路,其中,

241.所述抗噪电路包括:

242.连接到所述跟随器节点的电容器连接p沟道场效应晶体管 (pfet),以及

243.连接到所述跟随器节点的电容器连接n沟道场效应晶体管 (nfet);并且

244.所述电容器连接pfet和所述电容器连接nfet被配置为抵消所 述跟随器节点处的噪声电压。

245.示例7.根据示例6所述的电路,其中,

246.所述抗噪电路还包括:

247.电源节点,被配置为接收所述第一电源电压;以及

248.地节点,被配置为接收所述地电压;

249.所述电容器连接pfet连接在所述跟随器节点和所述电源节点之间; 并且

250.所述电容器连接nfet连接在所述跟随器节点和所述地节点之间。

251.示例8.根据示例2所述的电路,其中,所述拉低电路包括:

252.第一地节点,被配置为接收所述地电压;

253.第一n沟道场效应晶体管(nfet),具有耦合到所述跟随器节点的 第一漏极、耦合到所述地节点的第一源极、以及第一栅极,该第一栅极响 应所述第一电源电压而使得所述第一nfet被配置为执行下列项:

254.响应于所述第一电源电压处于所述第二状态而关断,以使所述跟 随器节点被设置为浮置;以及

255.响应于所述第一电源电压处于所述第一状态而导通,以使所述跟 随器节点被设置为所述地电压。

256.示例9.根据示例8所述的电路,其中,所述第一栅极被连接以接收所 述第一电源电压。

257.示例10.根据示例8所述的电路,其中,所述拉低电路还包括:

258.第一电源节点,被配置为接收所述第一电源电压;

259.第二地节点,被配置为接收所述地电压;

260.第一pfet,具有第二源极、第二漏极和第二栅极;以及

261.第二nfet,具有第三源极、第三漏极和第三栅极;

262.其中:

263.所述第二源极连接到所述第一电源节点;

264.所述第二漏极连接到所述第一栅极;

265.所述第二栅极连接到所述第三漏极;

266.所述第三栅极连接到所述第一栅极;并且

267.所述第三源极连接到所述第二地节点。

268.示例11.根据示例10所述的电路,其中,

269.所述拉低电路还包括:

270.第二电源节点,被配置为接收所述第一电源电压;

271.第二pfet,具有第四源极、第四漏极和第四栅极;

272.所述第四源极连接到所述第二电源节点;

273.所述第四漏极连接到所述第一栅极;并且

274.所述第四栅极连接到所述第一栅极。

275.示例12.根据示例10所述的电路,其中,

276.所述拉低电路还包括:

277.第三地节点,被配置为接收所述地电压;以及

278.第三nfet,具有第四源极、第四漏极和第四栅极;

279.所述第四源极连接到所述第三地节点;

280.所述第四漏极连接到所述第二栅极并连接到所述第三漏极;并且

281.所述第四栅极连接到所述第四漏极。

282.示例13.一种保护电路免受寄生噪声影响的方法,该方法包括:

283.在跟随器电路处接收第一电源电压,所述跟随器电路耦合到跟随器节 点,所述第一电源电压被配置为处于第一状态或第二状态;

284.在拉低电路的控制节点处接收第二电源电压,所述拉低电路耦合在所 述跟随器节点和具有地电压的第一参考节点之间,所述第二电源电压被配 置为处于第一状态或第二状态;

285.当所述第二电源电压处于所述第一状态时,控制所述拉低电路将所述 跟随器节点处的电压电平拉向所述地电压;

286.当所述第二电源电压处于所述第二状态时,控制所述拉低电路不将所 述跟随器节点处的电压电平拉向所述地电压;以及

287.对于耦合在所述跟随器节点和具有所述第二电源电压的至少第二参考 节点之间的抗噪电路,当所述第二电源电压处于所述第二状态时,使用所 述抗噪电路来保护所述跟随器节点处的电压电平不因寄生噪声电压而失真, 所述寄生噪声电压对所述跟随器节点是电容性的,所述寄生噪声电压基于 所述第一电源电压对所述跟随器节点的寄生电容耦合。

288.示例14.根据示例13所述的方法,其中,

289.所述抗噪电路包括:二极管连接场效应晶体管(fet),连接在所述 第二参考节点和所述跟随器节点之间;并且

290.使用所述抗噪电路进行保护包括:

291.当所述第二电源电压处于所述第一状态时,将所述二极管连接 fet反向偏置;并且

292.当所述第二电源电压处于所述第二状态时,将所述二极管连接 fet正向偏置,以通过所述第二参考节点将所述跟随器节点放电。

293.示例15.根据示例14所述的方法,其中,

294.所述二极管连接fet包括p沟道fet(pfet),该pfet具有第一漏 极/源极、第二漏极/源极和栅极;

295.所述第一漏极/源极与所述栅极中的每一个连接到所述第二参考节点; 并且

296.所述第二漏极/源极连接到所述跟随器节点。

297.示例16.根据示例13所述的方法,其中,

298.所述抗噪电路包括:电容器连接p沟道场效应晶体管(pcap),耦 合在所述第二参考节点和所述跟随器节点之间;并且

299.使用所述抗噪电路进行保护包括:

300.当所述第二电源电压处于所述第一状态时,使用所述跟随器节点 处的寄生噪声电压对所述pcap进行充电,从而减少所述寄生噪声电压对 所述跟随器节点处的电压电平的贡献。

301.示例17.根据示例16所述的方法,其中,

302.所述抗噪电路还包括:电容器连接n沟道场效应晶体管(ncap), 耦合在所述跟随器节点和所述第一参考节点之间;并且

303.使用所述抗噪电路进行保护还包括:

304.当所述第二电源电压处于所述第一状态时,使用所述跟随器节点 处的寄生噪声电压对所述ncap进行充电,从而进一步减少所述寄生噪声 电压对所述跟随器节点处的电压电平的贡献。

305.示例18.一种制造半导体器件的方法,该方法包括:

306.在半导体衬底中形成一个或多个有源区域;

307.在所述一个或多个有源区域之上形成一个或多个栅极电极,使得与所 述一个或多个有源区域相应地形成场效应晶体管(fet),所述fet包括:

308.被指定用于拉低电路的一个或多个第一fet;以及

309.被指定用于抗噪电路的一个或多个第二fet;

310.形成导体和过孔,所述导体和过孔连接所述fet而使得:

311.所述一个或多个第一fet被连接以表示所述拉低电路;

312.所述一个或多个第二fet被连接以表示所述抗噪电路;

313.所述拉低电路连接到跟随器节点并被配置为接收地电压和第一电 源电压;

314.所述第一电源电压被配置为至少呈现第一状态和第二状态;

315.所述拉低电路被配置为响应于所述第一电源电压处于所述第一状 态而将跟随器电压拉向所述地电压,以及响应于所述第一电源电压处 于所述第二状态而不将所述跟随器电压拉向所述地电压;以及

316.所述抗噪电路连接到所述跟随器节点,所述抗噪电路被配置为在 所述第一电源电压处于所述第二状态时保护所述跟随器节点处的所述 跟随电压不因噪声电压而失真。

317.示例19.根据示例18所述的方法,其中,所述一个或多个第二fet 包括连接到所述跟随器节点的二极管连接fet。

318.示例20.根据示例18所述的方法,其中,所述一个或多个第二fet 包括:

319.连接到所述跟随器节点的电容器连接p沟道fet;以及

320.连接到所述跟随器节点的电容器连接n沟道fet。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1