一种半导体结构的形成方法以及半导体结构与流程

本申请涉及半导体器件的制造领域,尤其涉及一种半导体结构的形成方法以及半导体结构。

背景技术:

1、随着mosfet器件尺寸不断缩小,特别是进入到65纳米及以下节点,mosfet器件由于极短沟道而凸显了各种不利的物理效应,如短沟道效应(short channel effect,sce)或栅极致漏(gate induced drain leakage,gidl)等,它们严重制约着器件性能的提高。其中短沟道效应决定了能采用的器件沟道长度、阈值电压等,使得器件性能和可靠性退化,限制了特征尺寸的进一步缩小。

技术实现思路

1、有鉴于此,本申请实施例提供一种半导体结构的形成方法以及半导体结构。

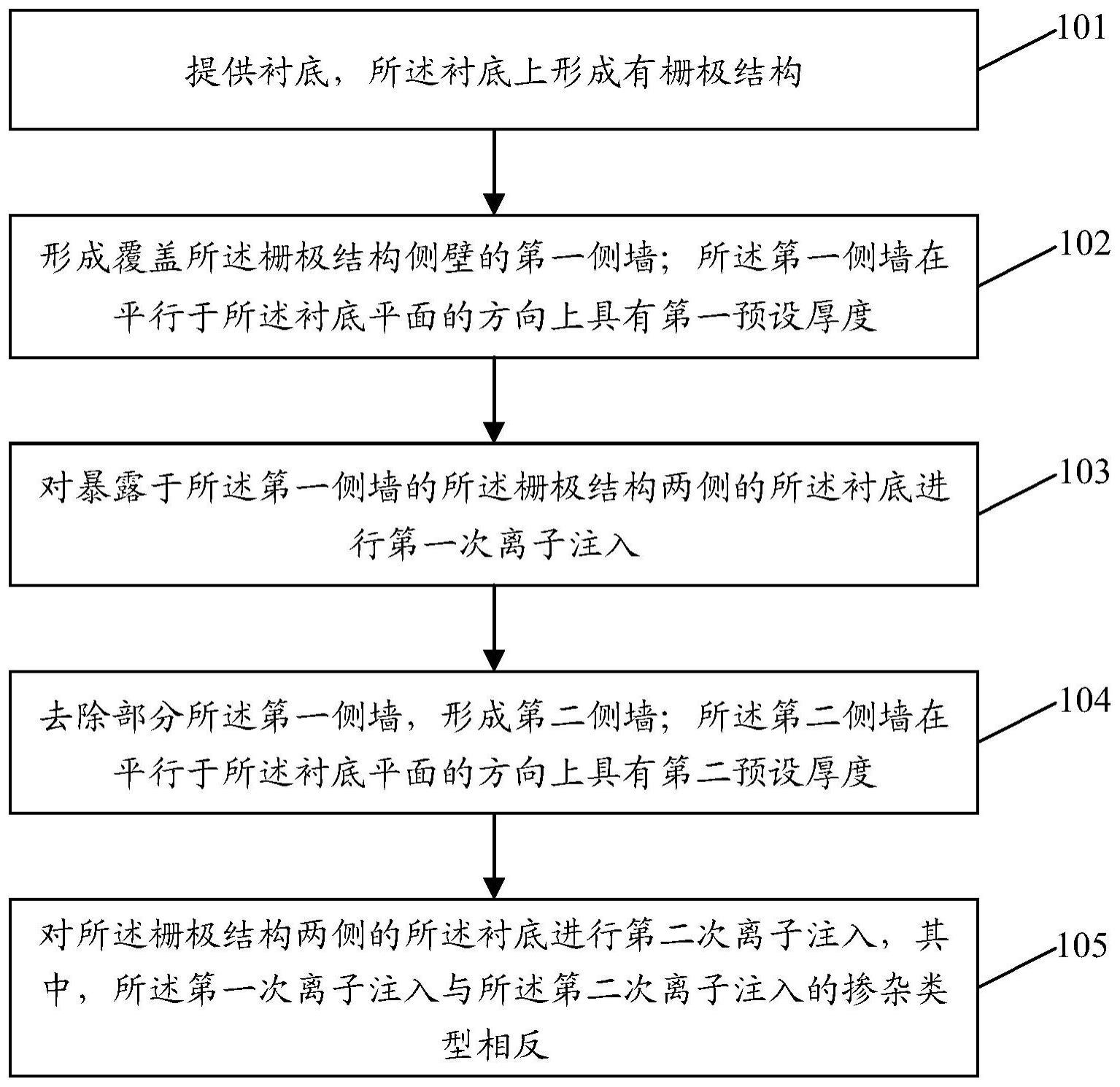

2、根据本申请实施例的第一方面,提供了一种半导体结构的形成方法,所述方法包括:

3、提供衬底,所述衬底上形成有栅极结构;

4、形成覆盖所述栅极结构侧壁的第一侧墙;所述第一侧墙在平行于所述衬底平面的方向上具有第一预设厚度;

5、对暴露于所述第一侧墙的所述栅极结构两侧的所述衬底进行第一次离子注入;

6、去除部分所述第一侧墙,形成第二侧墙;所述第二侧墙在平行于所述衬底平面的方向上具有第二预设厚度;

7、对所述栅极结构两侧的所述衬底进行第二次离子注入,其中,所述第一次离子注入与所述第二次离子注入的掺杂类型相反。

8、在一些实施例中,所述第一预设厚度的范围为5-10μm;所述第二预设厚度的范围为1-5μm。

9、在一些实施例中,所述第一次离子注入为ldd离子注入;所述第二次离子注入为halo离子注入。

10、在一些实施例中,所述对所述栅极结构两侧的所述衬底进行第一次离子注入;包括:

11、所述第一次离子注入的方向与垂直于所述衬底平面方向的夹角为第一预设夹角;

12、所述对所述栅极结构两侧的所述衬底进行第二次离子注入;包括:

13、所述第二次离子注入的方向与垂直于所述衬底平面方向的夹角为第二预设夹角;

14、其中,所述第一预设夹角小于所述第二预设夹角。

15、在一些实施例中,所述对所述栅极结构两侧的所述衬底进行第一次离子注入;包括:

16、所述第一次离子注入的剂量为第一预设剂量;

17、所述对所述栅极结构两侧的所述衬底进行第二次离子注入;包括:

18、所述第二次离子注入的剂量为第二预设剂量;

19、其中,所述第一预设剂量大于所述第二预设剂量。

20、在一些实施例中,还包括:

21、在进行第二次离子注入后,对所述栅极结构两侧的所述衬底进行热扩散,以在所述衬底内形成ldd区和halo区;其中,沿垂直于所述衬底平面方向的投影中,所述ldd区的投影与所述栅极结构的投影不重叠。

22、在一些实施例中,在形成ldd区和halo区之后,所述方法还包括:

23、以所述第二侧墙为掩膜,对所述栅极结构两侧的所述衬底进行源漏离子注入,形成源极区和漏极区。

24、根据本申请实施例的第二方面,提供了一种半导体结构的形成方法,所述方法包括:

25、提供衬底,所述衬底上形成有栅极结构;

26、形成覆盖所述栅极结构侧壁的第三侧墙;所述第三侧墙在平行于所述衬底平面的方向上具有第三预设厚度;

27、形成覆盖所述第三侧墙侧壁的第四侧墙;所述第四侧墙在平行于所述衬底平面的方向上具有第四预设厚度;所述第三侧墙与所述第四侧墙具有高刻蚀选择比;

28、对暴露于所述第三侧墙和所述第四侧墙的所述栅极结构两侧的所述衬底进行第一次离子注入;

29、去除所述第四侧墙;

30、对所述栅极结构两侧的所述衬底进行第二次离子注入;其中,所述第一次离子注入与所述第二次离子注入的掺杂类型相反。

31、在一些实施例中,所述第三预设厚度的范围为1-5μm;所述第四预设厚度的范围为4-5μm。

32、在一些实施例中,所述第一次离子注入为ldd离子注入;所述第二次离子注入为halo离子注入。

33、在一些实施例中,所述对所述栅极结构两侧的所述衬底进行第一次离子注入;包括:

34、所述第一次离子注入的方向与垂直于所述衬底平面方向的夹角为第一预设夹角;

35、所述对所述栅极结构两侧的所述衬底进行第二次离子注入;包括:

36、所述第二次离子注入的方向与垂直于所述衬底平面方向的夹角为第二预设夹角;

37、其中,所述第一预设夹角小于所述第二预设夹角。

38、在一些实施例中,所述对所述栅极结构两侧的所述衬底进行第一次离子注入;包括:

39、所述第一次离子注入的剂量为第一预设剂量;

40、所述对所述栅极结构两侧的所述衬底进行第二次离子注入;包括:

41、所述第二次离子注入的剂量为第二预设剂量;

42、其中,所述第一预设剂量大于所述第二预设剂量。

43、在一些实施例中,还包括:

44、在进行第二次离子注入后,对所述栅极结构两侧的所述衬底进行热扩散,以在所述衬底内形成ldd区和halo区;其中,沿垂直于所述衬底平面方向的投影中,所述ldd区的投影与所述栅极结构的投影不重叠。

45、在一些实施例中,在形成ldd区和halo区之后,所述方法还包括:

46、以所述第三侧墙为掩膜,对所述栅极结构两侧的所述衬底进行源漏离子注入,形成源极区和漏极区。

47、根据本申请实施例的第一方面,提供了一种半导体结构,包括:

48、衬底,

49、栅极结构,位于所述衬底上;所述栅极结构的侧壁形成有侧墙;

50、ldd区和halo区,位于所述衬底内;其中,

51、在沿垂直于所述衬底平面方向的投影中,所述ldd区的投影与所述栅极结构的投影不重叠,所述halo区的投影与所述栅极结构的投影具有重叠部分。

52、在一些实施例中,所述halo区的离子注入的剂量为1×1013原子/cm2。

53、本申请实施例中,通过先形成厚度较大的第一侧墙,以第一侧墙为掩膜,进行第一次离子注入,即ldd离子注入,可有效减少注入的离子向沟道扩散,减小了gidl电流的产生,然后刻蚀去掉部分第一侧墙,形成厚度较小的第二侧墙,进行第二次离子注入,即halo离子注入,进行沟道下方的halo离子增多,可降低sce。并且,进行halo离子注入时,作为掩膜的第二侧墙的厚度较小,进入沟道下方的halo离子增多,因此,达到相同的阈值电压的离子剂量相应的减少,从而减少了结漏电的产生。

技术特征:

1.一种半导体结构的形成方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,

3.根据权利要求1所述的方法,其特征在于,

4.根据权利要求3所述的方法,其特征在于,

5.根据权利要求3所述的方法,其特征在于,

6.根据权利要求3所述的方法,其特征在于,还包括:

7.根据权利要求6所述的方法,其特征在于,在形成ldd区和halo区之后,所述方法还包括:

8.一种半导体结构的形成方法,其特征在于,所述方法包括:

9.根据权利要求8所述的方法,其特征在于,

10.根据权利要求8所述的方法,其特征在于,

11.根据权利要求10所述的方法,其特征在于,

12.根据权利要求10所述的方法,其特征在于,

13.根据权利要求10所述的方法,其特征在于,还包括:

14.根据权利要求13所述的方法,其特征在于,在形成ldd区和halo区之后,所述方法还包括:

15.一种半导体结构,其特征在于,包括:

16.根据权利要求15所述的半导体结构,其特征在于,

技术总结

本申请实施例公开了一种半导体结构的形成方法以及半导体结构,其中,所述方法包括:提供衬底,所述衬底上形成有栅极结构;形成覆盖所述栅极结构侧壁的第一侧墙;所述第一侧墙在平行于所述衬底平面的方向上具有第一预设厚度;对暴露于所述第一侧墙的所述栅极结构两侧的所述衬底进行第一次离子注入;去除部分所述第一侧墙,形成第二侧墙;所述第二侧墙在平行于所述衬底平面的方向上具有第二预设厚度;对所述栅极结构两侧的所述衬底进行第二次离子注入,其中,所述第一次离子注入与所述第二次离子注入的掺杂类型相反。

技术研发人员:罗清

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!