接合结构及其形成方法与流程

1.本公开有关于一种接合结构及其形成方法,且特别关于一种具有银部件的接合结构及其形成方法。

背景技术:

2.现有的集成电路结构是将不同类型的芯片(例如模拟芯片、数字逻辑芯片、存储器芯片)平行排列在印刷电路板(printed circuit board,pcb)上。然而,印刷电路板上的面积有限,且各别芯片之间的距离较长,导致信号延迟的缺点。因此,随后发展出二维集成电路结构,亦即多芯片模块(multichip module,mcm)。其利用制程的优化,将不同芯片封装在同一个模块。随着晶体管数目持续上升,进一步发展出芯片或晶圆垂直堆叠的三维集成电路结构。三维集成电路结构达成系统级封装(system in chip,sip),其包括多芯片封装(multichip package,mcp)、芯片堆叠(stack die)、层叠封装(package on package,pop)、封装内封装(package in package,pip)以及晶圆对晶圆封装(wafer on wafer,wow)等。

3.三维集成电路结构的技术在于异质整合(heterogeneous integration)。异质整合是把不同种类的材料及组件变成单一系统,从而提升微光机电系统(micro-opto-electro-mechanical systems,moems)、微机电系统(micro-electro-mechanical systems,mems)以及纳米机电系统(nano-electro-mechanical systems,nems)的性能。由异质整合所衍生的三维集成电路结构使摩尔定律(moore’s law)得以延续。然而,三维集成电路仍存在一些问题,例如:微缩化时的焦耳热影响、芯片翘曲以及焊锡介金属化合物成长等,其中温度所引发的可靠度劣化是迫切的问题。因此,需要发展如何在三维集成电路制程中导入低温接合技术。

4.现有的低温接合方法包括:阳极接合、焊锡接合、表面活化接合、超音波接合以及高分子胶接合。然而,上述方法均存在一些缺点,例如:阳极接合需要施加高电压,高电压可能与芯片不相容而导致芯片毁损;焊锡接合有介金属化合物(intermetallic compound,imc)脆化的问题;表面活化接合的成本高昂且可能伤害芯片;超音波接合仅适用于小范围;以及高分子胶接合具有对位极不可重工的问题。

5.目前已知对于面心立方(face-centered cubic,fcc)晶体结构金属,其(111)结晶面为最密堆积平面,因此相较于(100)或(110)结晶面较易滑移、扩散速率较高且原子扩散速率较高(例如较高约3-4个数量级)。此外,纳米孪晶具有高密度的孪晶界,其可以提供大量的原子扩散路径。

6.中国台湾发明专利第i6865724号及中国台湾发明专利第i521104号均揭示一种在基板表面电镀铜纳米孪晶薄膜的方法,其可以于基板上形成平行分布的纳米孪晶薄膜,且具有高[111]优选结晶方位。中国台湾发明专利第i6865724号揭示一种电镀铜纳米孪晶薄膜的低温接合方法,其可以在0.8mpa至3mpa的压力及200℃至350℃的温度进行两个分别覆盖金属层的氧化物基板的接合。中国台湾发明专利第i521104号揭示一种先在基板上电镀铜晶种层再电镀镍纳米孪晶薄膜,之后将二基板低温接合的封装结构及方法;以及中国台

湾发明专利第i519681号揭示一种在半导体芯片、电路板或导电基板表面电镀金纳米孪晶薄膜,之后相互进行低温接合的结构及方法。

[0007]

然而,现有的低温接合技术虽然可以于基板上形成平行分布的纳米孪晶薄膜,但其均采用50rpm甚至1500rpm的高速旋转电镀方法,其制程及所形成的薄膜品质均不易控制,孪晶间距较大且[111]优选结晶方位低于90%。中国台湾发明专利第i432613号显示其孪晶结构的x光绕射(xrd)图中仍有明显的cu(222)结晶方位;中国台湾发明专利第i507548号显示其孪晶结构的x光绕射图中仍有明显的au(222)结晶方位,其[111]优选结晶方位甚至会低到仅50%。此外,现有技术虽利用纳米孪晶薄膜进行半导体芯片、电路板或导电基板接合,但由于纳米孪晶薄膜表面不够光滑,在接合前均须对纳米孪晶薄膜表面进行化学机械研磨(chemical mechanical polishing,cmp)以减少表面粗糙度,不仅制程繁复且会破坏纳米孪晶薄膜。

[0008]

再者,元件或接点尺寸会受到电镀制程的限制,且电镀制程产生的电镀废液亦有环保顾虑。详细而言,一般小于2微米的元件或接点无法以电镀方法制作,而使用溅镀或蒸镀则较无上述顾虑,即使是尺寸在2微米以下的元件或接点亦可容易利用溅镀或蒸镀制作完成。此外,直接电镀纳米孪晶薄膜于硅基板上,硅基板与纳米孪晶薄膜之间的接合力不足,会导致薄膜剥落从而影响薄膜整体可靠度。综合以上问题,现有的晶圆接合技术仍面临许多挑战。

技术实现要素:

[0009]

本公开的一些实施例提供一种接合结构,包括:第一基板;第二基板,与第一基板相对设置;第一接合层,于第一基板上;第二接合层,于第二基板上并与第一接合层相对设置;以及银部件,于第一接合层与第二接合层之间,其中银部件包括银纳米孪晶结构,且银纳米孪晶结构具有平行排列孪晶界,其中银纳米孪晶结构包括90%以上的[111]结晶方位。

[0010]

在一些实施例中,银部件的厚度至少为1.0微米。

[0011]

在一些实施例中,银纳米孪晶结构的厚度至少为0.5微米。

[0012]

在一些实施例中,平行排列孪晶界的间距为1纳米至100纳米。

[0013]

在一些实施例中,银部件还包括:第一过渡晶粒层,于第一接合层以及银纳米孪晶结构之间;以及第二过渡晶粒层,于第二接合层以及银纳米孪晶结构之间。

[0014]

在一些实施例中,银部件包括70%以上的[111]结晶方位。

[0015]

在一些实施例中,还包括:第一通孔,于第一基板之中并连接第一接合层;以及第二通孔,于第二基板之中并连接第二接合层。

[0016]

在一些实施例中,第一基板以及第二基板各自包括硅芯片、硅晶圆或其组合。

[0017]

在一些实施例中,第一接合层以及第二接合层各自包括铜、铝、银或其组合。

[0018]

本公开的另一些实施例提供一种形成接合结构的方法,包括:在第一基板上形成第一接合层;在第一接合层上形成第一银部件;在第二基板上形成第二接合层;在第二接合层上形成第二银部件;以及将第一银部件与第二银部件相对接合,以在第一接合层与第二接合层之间形成第三银部件,其中第三银部件包括银纳米孪晶结构,且银纳米孪晶结构具有平行排列孪晶界,其中银纳米孪晶结构具有90%以上的[111]结晶方位。

[0019]

在另一些实施例中,第三银部件的厚度至少为1.0微米、银纳米孪晶结构的厚度至

少为0.5微米以及平行排列孪晶界的间距为1纳米至100纳米。

[0020]

在另一些实施例中,形成第一银部件以及第二银部件的步骤包括溅镀或蒸镀。

[0021]

在另一些实施例中,在100℃至250℃的温度下执行第一银部件以及第二银部件的接合。

[0022]

在另一些实施例中,在1mpa至30mpa的压力下执行第一银部件以及第二银部件的接合。

[0023]

在另一些实施例中,在真空度为10-3

torr以上执行第一银部件以及第二银部件的接合。

[0024]

在另一些实施例中,第一银部件以及第二银部件的接合时间为10分钟至60分钟。

[0025]

在另一些实施例中,还包括:在第一接合层以及银纳米孪晶结构之间形成第一过渡晶粒层;以及在第二接合层以及银纳米孪晶结构之间形成第二过渡晶粒层。

[0026]

在另一些实施例中,第三银部件包括第一过渡晶粒层、第二过渡晶粒层以及银纳米孪晶结构,且第三银部件包括70%以上的[111]结晶方位。

[0027]

在另一些实施例中,还包括:于第一基板之中形成第一通孔,第一通孔连接第一接合层;以及于第二基板之中形成第二通孔,第二通孔连接第二接合层。

[0028]

在另一些实施例中,第一基板以及第二基板各自包括硅芯片、硅晶圆或其组合,且第一接合层以及第二接合层各自包括铜、铝、银或其组合。

附图说明

[0029]

以下将配合所附图示详述本公开的各面向。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制且仅用以说明例示。事实上,可能任意地放大或缩小单元的尺寸,以清楚地表现出本公开的特征。

[0030]

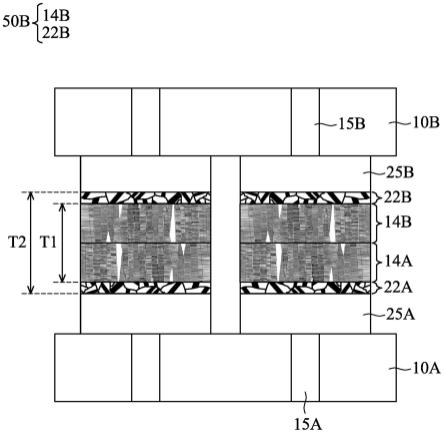

图1a至图1f根据一些实施例,绘示接合结构在不同制造阶段的剖面图。

[0031]

图2根据一些实施例,是在硅单晶上的银部件的聚焦离子束(focused ion beam,fib)图。

[0032]

图3a-图3e根据另一些实施例,系在不同温度下形成的接合结构的聚焦离子束(fib)图。

[0033]

其中,附图标记说明如下:

[0034]

10a,10b,10c:基板

[0035]

14a,14b,14c,14d:纳米孪晶结构

[0036]

15a,15b,15c:通孔

[0037]

22a,22b,22c,22d:过度晶粒层

[0038]

25a,25b,25c,25d:接合层

[0039]

50a,50b,50c,50d:银部件

[0040]

e:区域

[0041]

t1,t2,t3,t4:厚度

具体实施方式

[0042]

以下内容提供了很多不同的实施例或范例,用于实施本发明实施例的不同部件。

组件和配置的具体范例描述如下,以简化本发明实施例。当然,这些仅仅是范例,并非用以限定本发明实施例。举例来说,叙述中若提及第一部件形成于第二部件之上,可能包含第一和第二部件直接接触的实施例,也可能包含额外的部件形成于第一和第二部件之间,使得第一和第二部件不直接接触的实施例。另外,本发明实施例可能在许多范例中重复元件符号及/或字母。这些重复是为了简化和清楚的目的,其本身并非代表所讨论各种实施例及/或配置之间有特定的关系。

[0043]

以下描述实施例的一些变化。在不同图式和说明的实施例中,相似的元件符号被用来标示相似的元件。可以理解的是,在方法的前、中、后可以提供额外的步骤,且一些所叙述的步骤可在所述方法的其他实施例被取代或删除。

[0044]

此外,其中可能用到与空间相对用词,例如「在......下方」、「下方」、「较低的」、「在......上方」、「上方」等类似用词,是为了便于描述图式中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及图式中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

[0045]

此处所使用的用语「约」、「近似」等类似用语描述数字或数字范围时,该用语意欲涵盖的数值是在合理范围内包含所描述的数字,例如在所描述的数字的+/-10%之内,或本发明所属技术领域中具有通常知识者理解的其他数值。例如,用语「约5纳米」涵盖从4.5纳米至5.5纳米的尺寸范围。

[0046]

再者,说明书与权利要求中所使用的序数例如「第一」、「第二」、「第三」等的用词,以修饰权利要求的元件,其本身并不意含及代表该请求元件有任何之前的序数,也不代表某一请求元件与另一请求元件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一请求元件得以和另一具有相同命名的请求元件能作出清楚区分。

[0047]

本公开一些实施例提供一种接合结构,包括两基板之间具有银纳米孪晶结构的银部件。整体银部件具有70%以上的[111]结晶方位的平行排列孪晶界,且银部件之中的银纳米孪晶结构具有90%以上[111]结晶方位的平行排列孪晶界。除了银本身的特性,孪晶结构的特性,例如:抗氧化性、耐腐蚀性、导电性、导热性、高温稳定性等,使本公开实施例提供的接合结构在3d-ic封装,例如:低温晶圆堆叠晶圆封装(wafer on wafer)及系统整合芯片封装(chip on wafer)等具有较佳的应用优势。

[0048]

根据一些实施例,图1a至图1f绘示接合结构在不同制造阶段的剖面图。参照图1a,提供第一基板10a。第一基板10a上具有第一接合层25a,且第一基板10a中具有连接至第一接合层25a的第一通孔(via)15a。在一些实施例中,第一基板10a包括半导体晶圆、半导体芯片或其组合。例如,第一基板10a包括元素半导体,例如:硅、锗;化合物半导体,例如:碳化硅(silicon carbide)、砷化镓(gaas)、磷化镓(gap)、磷化铟(inp)、砷化铟(inas)以及/或锑化铟(insb);合金半导体,例如:硅锗(sige)、磷砷化镓(gaasp)、砷化铝铟(alinas)、砷化铝镓(algaas)、砷化镓铟(gainas)、磷化镓铟(gainp)以及/或磷砷化镓铟(gainasp);或其组合。

[0049]

在一些实施例中,第一接合层25a包括铜、铝、银或其组合。第一接合层25a的厚度可以为0.01微米至10微米,较佳为例如0.1微米至1.0微米。在一些实施例中,第一通孔15a可以为硅通孔。

[0050]

在另一些实施例中,第一基板10a上可以额外包括金属层间介电层(inter-metal dielectric,imd)(未示出)以及保护层(未示出)。金属层间介电层可以为氧化硅、氮化硅、硼硅酸盐玻璃(borosilicate glass,bsg)、磷硅酸盐玻璃(phosphoric silicate glass,psg)、硼磷硅酸盐玻璃(borophosphosilicate glass,bpsg)、低介电常数材料、其他合适的介电材料或其组成。金属层间介电层上可以设置例如内连线(interconnection)结构(未示出)、重分布层(redistribution layer,rdl)(未示出)等。保护层可以为氮化硅、聚酰亚胺(polyimide,pi)或其组合。此外,第一基板10a上可以包括各种被动及主动装置(未示出),例如:电阻、电容、电感、二极管、场效晶体管(field effect transistors,fets)、金属氧化物半导体场效晶体管(metal-oxide semiconductor fets,mosfets)、互补式金属氧化物半导体(complementary metal-oxide semiconductor,cmos)晶体管、双极性接面晶体管(bipolar junction transistors,bjts)、横向扩散mos(laterally diffused mos,ldmos)晶体管、高压晶体管、高频晶体管、其他合适的装置或其组合。应当理解,图1a所示的结构仅为示例,且第一基板10a上可以包括额外的部件。

[0051]

参照图1b,在第一接合层25a上形成第一银部件50a。在一些实施例中,第一银部件50a的厚度可以为1.0微米以上,例如约1.0微米至约10微米。第一银部件50a包括银纳米孪晶结构14a,银纳米孪晶结构14a具有平行排列孪晶界(σ3+σ9),并且孪晶界的间距可以为1纳米至100纳米,较佳为2纳米至50纳米。在一些实施例中,银纳米孪晶结构14包括平行堆叠的银纳米孪晶柱。银纳米孪晶柱的直径可以为0.1微米至10微米,较佳为0.3微米至1.0微米。

[0052]

继续参照图1b,在一些实施例中,除了银纳米孪晶结构14a之外,第一银部件50a也包括过渡晶粒层22a。最初在第一接合层25a上形成第一银部件50a时,第一银部件50a并不会立即形成具有平行排列孪晶界的银纳米孪晶结构14a,而会形成不含有平行排列孪晶界的过渡晶粒层22a。在一些实施例中,过渡晶粒层22a的厚度小于2.0微米,例如约0.1微米至约1.0微米。

[0053]

在一些实施例中,可以通过溅镀的方式将第一银部件50a形成在第一接合层25a上。在一些实施例中,溅镀采用单枪溅镀或多枪共镀。溅镀电源可以使用例如dc、dc plus、rf、高功率脉冲磁控溅镀(high-power impulse magnetron sputtering,hipims)等。第一银部件50a的溅镀功率可以为例如约100w至约500w。溅镀制程的温度为室温,但溅镀过程温度会上升约50℃至约200℃。溅镀制程的背景压力为1x10-5

torr。工作压力可以为例如约1x10-3

torr至1x10-2

torr。氩气流量约10sccm至约20sccm。载台转速可以为例如约5rpm至约20rpm。溅镀过程基板施加偏压约-100v至约-200v。第一银部件50a的沉积速率可以为例如0.5nm/s至约3nm/s。应当理解,上述溅镀制程参数可以依照实际应用适当调整,本公开并不以此为限。

[0054]

在另一些实施例,可以通过蒸镀的方式将第一银部件50a形成在第一接合层25a上。在一些实施例中,蒸镀制程的背景压力为1x10-5

torr。工作压力可以为例如约1x10-4

torr至约5x10-4

torr。氩气流量约2sccm至约10sccm。载台转速可以为例如约5rpm至约20rpm。第一银部件50a的沉积速率可以为例如约1nm/s至约5.0nm/s。额外地,在蒸镀过程期间可以对银纳米孪晶结构14a施加离子撞击,其电压约10v至约300v且电流约0.1a至约1.0a。应当理解,上述蒸镀制程参数可以依照实际应用适当调整,本公开并不以此为限。

[0055]

相较于溅镀或蒸镀,电镀制程会有元件或接点尺寸的限制。详细而言,一般小于2微米的元件或接点无法以电镀方法制造。然而,即使是尺寸在2微米以下的元件或接点可以轻易地利用溅镀或蒸镀制造。

[0056]

在一些实施例中,在第一基板10a上形成第一接合层25a以及第一银部件50a的方法可以包括:将第一接合层25a以及第一银部件50a形成在第一基板10a的全部表面上,随后进行图案化制程去除部分的第一接合层25a以及第一银部件50a以形成如图1b所示的结构。在另一些实施例中,在第一基板10a上形成第一接合层25a以及第一银部件50a的方法可以包括:在第一基板10a上设置具有开口的遮罩,并将第一接合层25a以及第一银部件50a形成在第一基板10a上,随后将遮罩移除并同时移除开口外的膜层以形成如图1b所示的结构。应当理解,上述方法仅为示例且可以依照实际应用适当调整,本公开不以此为限。

[0057]

参照图1c,提供第二基板10b。第二基板10b上具有第二接合层25b,且第二基板10b中具有连接至第二接合层25b的第二通孔15b。第二基板10b、第二接合层25b以及第二通孔15b的材料可以参考图1a所述的实施例,此处不再赘述。随后,在第二接合层25b上形成第二银部件50b,第二银部件50b包括银纳米孪晶结构14b以及过渡晶粒层22b。第二银部件50b的厚度以及形成方法可以参考图1b所述实施例的方法,此处不再赘述。应当理解,第二基板10b、第二接合层25b、第二通孔15b以及第二银部件50b可以依照实际应用适当地调整,并不限于图1a及图1b所示的实施例。

[0058]

继续参照图1c,将第一银部件50a与第二银部件50b相对接合以形成第三银部件(50a及50b)并形成接合结构。第三银部件具有银纳米孪晶结构(14a及14b)。在第三银部件的剖面金相图中,第三银部件整体包括70%以上(例如大于70%或大于75%)的[111]结晶方位,且银纳米孪晶结构包括90%以上(例如大于90%或大于95%)的[111]结晶方位。孪晶界的间距可以为1纳米至100纳米,较佳为2纳米至50纳米。在一些实施例中,银纳米孪晶结构的厚度t1至少为0.5微米,较佳为例如约0.5微米至约8微米,并且第三银部件的厚度t2至少为1.0微米,较佳为例如约1.0微米至约10微米。

[0059]

在实务上,当纳米孪晶薄膜厚度低于2微米时,在后续低温晶圆接合与3d-ic封装制程中,纳米孪晶薄膜会快速与接合材料反应殆尽。形成的界面介金属化合物与基板并无接合力而导致界面脱落,在应用上不具意义。

[0060]

在一些实施例中,可以在100℃至250℃的温度(例如约100℃至约150℃或约150℃至约250℃)、在1mpa至30mpa的压力(例如约1mpa至约3mpa或约3mpa至约30mpa)以及在真空度为10-3

torr以上执行第一银部件50a与第二银部件50b的接合。在一些实施例中,第一银部件50a与第二银部件50b的接合时间可以为10分钟至60分钟(例如约10分钟至约30分钟或约30分钟至约60分钟)。在第一银部件50a与第二银部件50b接合之后,接合结构仍具有银纳米孪晶结构14a及14b并保有纳米孪晶结构的特性。

[0061]

上述将两基板接合的实施例仅为示例。应当理解,可以将基板的数量增加至两个以上,并在多个基板的正面及反面分别形成接合层以及银部件以进行多个基板的接合,如以下图1d至图1f的示例所述。

[0062]

参照图1d,可以在第二基板10b相对于第二接合层25b的另一侧表面上形成第三接合层25c以及第四银部件50c。参照图1e,提供第三基板10c。第三基板10c上具有第四接合层25d,且第三基板10c中具有连接至第四接合层25d的第三导孔15c。可以在第四接合层25d上

形成第五银部件50d。随后将第四银部件50c以及第五银部件50d相对接合以形成接合结构。第三基板10c、第三导孔15c、第三接合层25c、第四接合层25d、第四银部件50c、第五银部件50d的材料及/或形成方法以及厚度t3、t4可以参考图1a至图1c所示的实施例,此处不再赘述。

[0063]

参照图1f,区域e可以为图1e所示的结构。应当理解,图1f仅为示例,以说明可以依实施应用调整基板的数量以形成具有不同层数的接合结构。

[0064]

本公开使用1mpa至30mpa的压力范围,不论基板或银纳米孪晶均可以保持完好无损。现有技术虽可以在0.8mpa至3mpa的低压进行接合,然而其在接合前必须先对纳米孪晶薄膜进行化学机械研磨(cmp)以减少表面粗糙度,不仅制程繁复且会破坏纳米孪晶薄膜。本公开在不损害基板及银纳米孪晶的情况下,相较于现有技术施加较大约1mpa至约30mpa的压力,使银纳米孪晶表面的凸起结构进行纳米等级的塑性变形,以达到紧密接触目标的效果。其不仅解决银纳米孪晶表面粗糙度的问题,更免除现有技术必须额外进行繁复的化学机械研磨或其他表面处理的步骤,从而可以大幅提升产能及良率。此外,现有技术的铜纳米孪晶硬度高达4gpa,约为本公开银纳米孪晶硬度的2倍。如果要利用本公开的纳米等级的凸起结构塑性变形机制解决铜纳米孪晶表面粗糙度的问题,必须施加100mpa以上的压力,将造成基板及铜纳米孪晶的损坏。

[0065]

再者,银的电阻率为1.63μω

·

cm,低于铜(1.69μω

·

cm)、金(2.2μω

·

cm)及镍(6.90μω

·

cm)的电阻率,因此银具有较佳的导电性以及导热性。银的叠差能(stacking fault energy)为25mj/m2,亦低于铜(70mj/m2)、金(45mj/m2)及镍(225mj/m2)的叠差能,因此银相较于铜、金及镍更容易形成孪晶。

[0066]

相较于现有技术(中国台湾发明专利第i432613号)使用电镀形成铜纳米孪晶薄膜,在本公开实施例的纳米孪晶制程中,银的扩散速率较铜快10倍以上(请参考:landolf-bornstein,ed.h.mehrer,diffusion in solid metals and alloys,vol.26,p.75)。此外,银的熔点较铜低约100℃,可以在较低温的环境进行后续的接合制程,使半导体装置不受接合制程高温的影响。详细而言,相较于银纳米孪晶结构,铜纳米孪晶结构需要在较高的温度(例如高于250℃)进行接合制程。其可能会损害半导体装置,并且在接合完成冷却至室温时,造成微小接点由于材料收缩而对位失败。

[0067]

银纳米孪晶硬度仅大约2gpa,较铜纳米孪晶软,在后续与其他材料接合时的表面粗糙度影响较小。尤其当微小元件或接点的高度有差异时,较不会发生共平面度的问题。

[0068]

此外,银纳米孪晶薄膜较铜纳米孪晶薄膜不易氧化,可以较铜纳米孪晶薄膜获得较佳的接合界面。相较于现有技术,上述特性均显示本公开实施例的银纳米孪晶结构在3d-ic封装,例如:低温晶圆堆叠晶圆封装(wafer on wafer)及系统整合芯片封装(chip on wafer)等具有较佳的应用优势。

[0069]

孪晶组织的形成是由于材料内部累积应变能驱动部分区域的原子均匀剪移(shear)至与其所在晶粒内部未剪移原子形成相互镜面对称的晶格位置。孪晶包括:退火孪晶(annealing twin)与机械孪晶(mechanical twin)两种。其相互对称的界面即为孪晶界(twin boundary)。

[0070]

孪晶主要发生在晶格排列最紧密的面心立方(face centered cubic,fcc)或六方最密堆排(hexagonal closed-packed,hcp)结晶材料。除了晶格排列最紧密结晶构造条件,

通常叠差能(stacking fault energy)越小的材料越容易产生孪晶。例如,铝虽为面心立方结晶构造材料,但其叠差能大约为200erg/cm2,极少出现孪晶。

[0071]

孪晶界为调谐(coherent)结晶构造,属于低能量的σ3与σ9特殊晶界。结晶方位均为{111}面。相较于一般退火再结晶所形成的高角度晶界,孪晶界的界面能约为一般高角度晶界的5%(请参考:george e.dieter,mechanical metallurgy,mcgraw-hill book company,1976,p.135-141)。

[0072]

由于孪晶界较低的界面能,可以避免成为氧化、硫化及氯离子腐蚀的路径。因此展现较佳的抗氧化性与耐腐蚀性。此外,此种孪晶的对称晶格排列对电子传输的阻碍较小。因而展现较佳的导电性与导热性。由于孪晶界对差排移动的阻挡,使材料仍可维持高强度。此兼具高强度与高导电性的特性在铜薄膜已获得证实(请参考:l.lu,y.shen,x.chen,l.qian,and k.lu,ultrahigh strength and high electrical conductivity in copper,science,vol.304,2004,p.422-426)。

[0073]

就高温稳定性而言,由于孪晶界较低的界面能,其孪晶界较一般高角度晶界稳定。孪晶界本身在高温状态不易移动,也会对其所在晶粒周围的高角度晶界产生固锁作用,使这些高角度晶界无法移动。因而整体晶粒在高温不会有明显的晶粒成长现象以维持材料的高温强度。

[0074]

就通电流的可靠性而言,由于原子经由低能量孪晶界或跨越孪晶界的扩散速率较低。在使用电子产品时,高密度电流所伴随线材内部原子移动也较为困难。如此解决线材在通电流时常发生的电迁移(electromigration)问题。在铜薄膜已有报导证实孪晶可抑制材料电迁移现象(请参考:k.c.chen,w.w.wu,c.n.liao,l.j.chen,and k.n.tu,observation of atomic diffusion at twin-modified grain boundaries in copper,science,vol.321,2008,p.1066-1069.)。

[0075]

在半导体装置中,本公开实施例具有孪晶结构的银部件可以用作电极。如以上所述,相较于其他作为接合结构(例如柱(pillar)、焊料(solder)等)的金属(例如铜、金、镍等),银具有较低的电阻率、叠差能以及熔点,其较容易形成纳米孪晶结构并且可以在低温低压的情况下进行接合制程。

[0076]

本公开实施例利用银纳米孪晶结构进行低温接合制程。其除了可以应用于三维集成电路封装产业,也可以应用于高功率元件芯片与基板的接合、对制程温度较敏感的产业、以及其他装置(例如:微机电元件(mems)、发光二极管(led)、微型发光二极管(micro-led)、迷你发光二极管(mini-led)、生物芯片、物联网(iot)系统中的感测器、执行器、以及热敏感元件等)。

[0077]

以下描述本公开一些形成接合结构的具体实施例以及检测结果。

[0078]

实施例一

[0079]

参照图2,在硅单晶的铜接合层表面溅镀银部件。使用聚焦离子束(fib)观察的金相照片显示银部件主要具有平行排列银纳米孪晶结构,且在平行排列银纳米孪晶结构与铜接合层之间具有银过渡晶粒层。使用电子背向绕射(electron backscattered diffraction,ebsd)观察银部件,平行排列银纳米孪晶界的结晶方位具有98%以上的[111]结晶方位,且具有[111]结晶方位的银纳米孪晶结构占整体银部件的85%以上。

[0080]

实施例二至六(分别对应图3a至图3e)

[0081]

在两硅芯片的铜接合层表面溅镀银部件。在压力为20mpa、真空度为10-3

torr且温度为100℃的情况下,将已溅镀银部件的两硅芯片相对接合60分钟,所得的fib金相照片如图3a所示;在压力为20mpa、真空度为10-3

torr且温度为150℃的情况下,将已溅镀银部件的两硅芯片相对接合30分钟,所得的fib金相照片如图3b所示;在压力为20mpa、真空度为10-3

torr且温度为200℃的情况下,将已溅镀银部件的两硅芯片相对接合30分钟,所得的fib金相照片如图3c所示;在压力为20mpa、真空度为10-3

torr且温度为250℃的情况下,将已溅镀银部件的两硅芯片相对接合30分钟,所得的fib金相照片如图3d所示;以及在压力为20mpa、真空度为10-3

torr且温度为250℃的情况下,将已溅镀银部件的两硅芯片相对接合10分钟,所得的fib金相照片如图3e所示。实施例二至六的金相照片均显示接合界面不具有孔洞,且铜接合层之间的接合界面仍保有平行排列纳米孪晶。随后使用电子背向绕射(ebsd)观察实施例二至六的铜接合层之间的接合界面,平行排列银纳米孪晶界的结晶方位均具有98%以上的[111]结晶方位,且具有[111]结晶方位的银纳米孪晶结构均占整体银部件的85%以上。

[0082]

本公开的实施例具有一些有利特征。在接合结构的剖面金相图中,银纳米孪晶结构具有平行排列孪晶界,平行排列孪晶界具有90%以上的[111]结晶方位。整体银部件具有70%以上的[111]结晶方位。此外,相较于其他金属(例如铜、金、镍等)银具有较低的电阻率、叠差能以及熔点,其较容易形成纳米孪晶结构并且可以在低温低压的情况下进行接合制程。

[0083]

以上概述数个实施例的特征,以使本发明所属技术领域中具有通常知识者可以更加理解本发明实施例的观点。本发明所属技术领域中具有通常知识者应理解,可轻易地以本发明实施例为基础,设计或修改其他制程和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本发明所属技术领域中具有通常知识者也应理解,此类等效的结构并无悖离本发明的精神与范围,且可在不违背本发明的精神和范围下,做各式各样的改变、取代和替换。因此,本发明的保护范围当视后附的权利要求书所界定为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1