表面黏着式功率半导体封装元件及其制法的制作方法

1.本发明关于一种封装元件,特别是指一种表面黏着式(smt)的功率半导体封装元件及其制法。

背景技术:

2.分立器件(discrete package)是指具有独立功能的电子封装元件,依其晶片功能可以分为如二极管、功率晶体管等类型的封装元件,其主要构件包含晶片、导线架(lead frame)、引线(wire)、绝缘塑封外壳等。参照美国公告第8,237,259号专利,该专利揭露其中一种传统分立器件的制法,该专利在晶粒的其中一面提供有银胶(silver paste)、烧结银(ag sintering)、锡膏等材料作为黏晶步骤(die bonding)的主要黏着介质,如同该专利的第6图的元件符号316所示,利用该黏着介质将晶粒贴在导线架上。但使用银胶/烧结银与导线架,需要昂贵的材料费用,难以降低产品制作成本,而锡膏则存在环保问题,亦不推荐使用。

技术实现要素:

3.本发明为降低产品的制作成本,故提出一种表面黏着式功率半导体封装元件及其制法。

4.为达成前述目的,本发明的「表面黏着式功率半导体封装元件」包含有:

5.一晶片,具有相对的一正面及一背面,该正面及该背面分别设有信号接点,其中该晶片为一功率半导体晶片;

6.一塑封层,包覆该晶片,且在该塑封层中形成有第一开孔及第二开孔,该第一开孔位在晶片侧边,该第二开孔对应延伸至该晶片其正面的信号接点,在该第一开孔与第二开孔内部填充一导电层,其中,该第二开孔中的导电层电性连接该晶片其正面的信号接点;

7.一导通层,设置在该晶片的背面并延伸电性连接该第一开孔中的导电层以及该晶片背面的信号接点,其中,该导通层是单一导电镀层;

8.该第一开孔及第二开孔中的导电层凸出于该塑封层的同一表面并作为该表面黏着式功率半导体封装元件的导电端子。

9.其中,在该第一开孔与第二开孔内部填充的导电层可通过电镀方式形成,将晶片正面、背面信号接点共同电性连接至封装元件的同一表面,即不需使用导线架及黏晶材料。

10.根据另一实施例,本发明的「表面黏着式功率半导体封装元件」包含有:

11.一晶片,具有相对的一正面及一背面,该正面及该背面分别设有信号接点,其中该晶片为一功率半导体晶片;

12.一导电基板,形成有一晶片容置开口,令该晶片设置在该晶片容置开口内部;

13.一塑封层,包覆该晶片与该导电基板,在该塑封层中形成有第一开孔及第二开孔,该第一开孔位在晶片侧边并延伸至该导电基板的表面,该第二开孔对应延伸至该晶片其正面的信号接点,在该第一开孔与第二开孔内部填充一导电层,其中,该第一开孔中的导电层

连接该导电基板,该第二开孔中的导电层连接该晶片其正面的信号接点;

14.一导通层,设置在该晶片的背面,且延伸连接该导电基板以及该晶片背面的信号接点;

15.该第一开孔及第二开孔中的导电层凸出于该塑封层的同一表面并作为该表面黏着式功率半导体封装元件的导电端子。

附图说明

16.图1a~图1m:本发明第一实施例的制程示意图。

17.图2a~图2l:本发明第二实施例的制程示意图。

18.图3:本发明当中的铜基板的平面示意图。

19.图4:本发明图3所示铜基板的立体示意图。

20.图5:本发明将晶片设置于铜基板中的立体示意图。

21.图6a~图6j:本发明第三实施例的制程示意图。

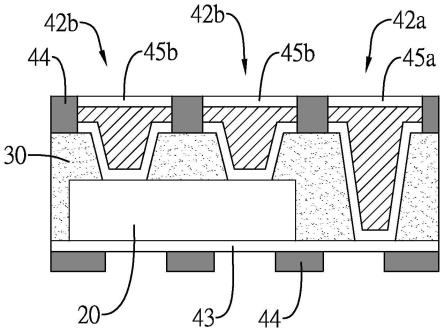

22.图7:依据本发明图1a~1m实施例制作而成的表面黏着式功率半导体封装元件剖面示意图。

23.图8:依据本发明图2a~2l实施例制作而成的表面黏着式功率半导体封装元件剖面示意图。

24.图9:依据本发明图6a~6j实施例制作而成的表面黏着式功率半导体封装元件剖面示意图。

具体实施方式

25.本发明是一种「表面黏着式功率半导体封装元件及其制法」,图1a~图1m为第一较佳实施的制程示意图,以下配合图式顺序说明本发明的制作流程。在图1a中,首先制备一载板(carrier)10,在该载板10上贴合一层黏着胶带11,该黏着胶带11的表面具有黏性。

26.参照图1b,将晶片20间隔排列在该黏着胶带11上,该晶片20为一功率半导体晶片,在其正面及背面形成有用于电性连接的信号接点(图中未示),在图1b中,将该晶片20与该黏着胶带11互相黏着的一面定义为晶片背面,其相对的另一面为晶片正面。

27.参照图1c,将各晶片20以一塑封层30包覆,该塑封层30的材料可为pp、emc等介电材质。该塑封层30成型后,进一步加入图1d所示的平坦化步骤,在该塑封层30的表面进行研磨(grinding)或清洁,使整体塑封层30的表面为平整表面。

28.参照图1e,在该塑封层30的预设位置形成第一开孔(vias)31a及第二开孔31b,该第一开孔31a、第二开孔31b的位置取决于产品所需的导电端子的位置,其中,晶片20周围的第一开孔31a可完全贯穿该塑封层30,第二开孔31b从塑封层30的表面向下延伸到该晶片20正面的信号接点。该第一开孔31a/第二开孔31b的成形方式可通过例如镭射钻孔(laser drilling)、超音波钻孔(ultrasonic drilling)、微放电加工(micro electrical discharge machining,μ-edm)、微细磨料喷射加工(micro powder blasting)或是感应耦合电浆离子蚀刻(inductively coupled plasma reactive ion etching,icp-rie)等技术,本发明并不特别限制其成形方式。本说明书中记载的第一开孔、第二开孔是指在不同位置的开孔,借此区分不同开孔的种类,而不是意指数量为第一个开孔、第二个开孔。

29.参照图1f,在各个第一开孔31a、第二开孔31b的内部壁面及塑封层30的表面形成一预电镀层40,该预电镀层40作为后续制作导电层的种子层(seed layer),该预电镀层40的制作方式可选用化学镀(electro-less plating)、溅镀(sputter)等技术完成。

30.参照图1g,图案化的一导电层42填满在各个第一开孔31a、第二开孔31b的内部以及该塑封层30的表面,其中,凸出在塑封层30表面的该导电层42通过蚀刻或其它方式而形成多个独立的导电端子。每一个第一开孔31a、第二开孔31b的位置可以构成一独立的导电端子42a,42b;或是根据晶片20功能设计,数个第一开孔31a、第二开孔31b也可以利用该导电层42彼此电性连接形成一共同接点。该导电层42的较佳材料为铜,其制作方式可通过电镀或印刷方式形成。

31.参照图1h,在完成该导电层42的制作之后,将该载板10及黏着胶带11移除而显露出该塑封层30的底面以及第一开孔31a、第二开孔31b底部。如图1i所示,若该塑封层30的底面存在有凹凸不平或脏污问题,可视需求在该塑封层30的底面进行研磨(grinding)或清洁,使该塑封层30的整体底面为平整表面。

32.参照图1j,在塑封层30的底面显露出来后,在该塑封层30的底面形成一导电镀层43,该导电镀层43电性连接该晶片20背面的信号接点至对应的导电端子42a。该导电镀层43可制作方式可选用化学镀(electro-less plating)、溅镀(sputter)等技术完成。在示意图1j中,该晶片20背面具有单一个信号接点,该信号接点通过导电镀层43电性连接到晶片20周围的其中一个导电端子42a,形成信号传输路径;但在其它实施例中,该晶片20背面具有多个个信号接点,该多个信号接点分别连接至周围的多个导电端子42a。

33.参照图1k,在该塑封层30的底面及正面分别以绝缘材形成一绝缘保护层44,具有防水气、防氧化的功能。其中,在该塑封层30正面的绝缘保护层44分布在相邻导电端子42a、42b之间作为阻焊层(solder mask),可降低相邻导电端子42a、42b在焊接过程中发生短路的机率。在形成该绝缘保护层44之后,可在各导电端子42a、42b的表面上进一步形成一接点防护层45a、45b,该接点防护层45a、45b可利用无电电镀镍浸金(enig)方式形成。

34.参照图1l所示,该塑封层30背面的绝缘保护层44可进一步进行刻印(marking)制程,例如镭射刻印或是通过黄光制程形成所需的产品标记。最后,请参照图1m示,在预定的切割位置进行切割(sawing),令每一个晶片20及其塑封层30形成独立的封装产品。

35.另请参照图2a~图2l,为本发明第二较佳实施例的制程示意图,以下配合图式顺序说明本发明的制作流程。在图2a中,首先制备一铜基板50,在该铜基板50上的底面贴合一层黏着胶带58,该黏着胶带58的表面具有黏性。其中,该铜基板50的结构如图3、图4所示,该铜基板50形成有多个晶片容置开口51,各晶片容置开口51呈矩形且在其各个角落向外延伸出一防撞缺口52(如图3所示),各防撞缺口52与晶片容置开口51相连通。在本实施中,各防撞缺口52是以该容置开口51的角落顶点作为一圆心c向外延伸出的一圆形缺口,在其它实施例中,该防撞缺口52也可以是其它形状,例如矩形、方形或多边形等,该防撞缺口52可通过机械加工(如铣刀切削)或是化学加工(如蚀刻)的方式制作而成。

36.参照图2b,在各晶片容置开口51内部分别设置一晶片60,其中,该晶片60为一功率半导体晶片,在其正面及背面形成有用于电性连接的信号接点(图中未示),在图2b中,将该晶片60与该黏着胶带50互相黏着的一面定义为晶片背面,其相对的另一面为晶片正面;在黏晶的过程中,如图5所示,因为该晶片容置开口51的四个角落均向外延伸出该防撞缺口

52,可防止晶片60的各角落直接碰撞铜基板50,避免晶片60损毁。

37.参照图2c,将晶片60以一塑封层70包覆,该塑封层70的材料可为pp、emc等介电材质。该塑封层70成型后,若有必要可在其表面进行平坦化步骤,对该塑封层70的表面进行研磨(grinding)或清洁,使整体塑封层70的表面为平整表面。

38.参照图2d,在该塑封层70的预设位置形成第一开孔(vias)71a、第二开孔71b,该第一开孔71a、第二开孔71b的位置取决于产品所需的导电端子的位置,其中,晶片60周围的第一开孔71a延伸至该铜基板50,第二开孔71b从塑封层70的表面向下延伸到该晶片60正面的信号接点。该第一开孔71a/第二开孔71b的成形方式可通过例如镭射钻孔(laser drilling)、超音波钻孔(ultrasonic drilling)、微放电加工(micro electrical discharge machining,μ-edm)、微细磨料喷射加工(micro powder blasting)或是感应耦合电浆离子蚀刻(inductively coupled plasma reactive ion etching,icp-rie)等技术,本发明并不特别限制其成形方式。

39.参照图2e,在完成该第一开孔71a/第二开孔71b的制作之后,将该黏着胶带58移除而显露出该塑封层70、该晶片60以及铜基板50的底面;根据该黏着胶带58的材料特性,可对该黏着胶带58加热或照射紫外光,使其脱离铜基板50。如图2f所示,若该塑封层70、铜基板50的底面存在有凹凸不平或脏污问题,可视需求在该塑封层70与铜基板50的底面进行研磨(grinding)或清洁。

40.参照图2g,在各个第一开孔71a/第二开孔71b的内部壁面以及该塑封层70、该晶片60以及铜基板50的底面同时形成一预电镀层80,该预电镀层80作为后续制作导电层的种子层(seed layer),该预电镀层80的制作方式可选用化学镀(electro-less plating)、溅镀(sputter)等技术完成。

41.参照图2h,图案化的一导电层82填满在各个第一开孔71a/第二开孔71b的内部以及该塑封层30的表面,其中,在塑封层30表面的该导电层82通过蚀刻或其它图案化制程形成多个独立的导电端子。每一个第一开孔71a/第二开孔71b位置可以为一独立的导电端子82a,82b;或是根据晶片60功能设计,多个第一开孔71a/第二开孔71b也可以利用该导电层82彼此电性连接形成一共同接点。该导电层82的较佳材料为铜,其制作方式可通过电镀或印刷方式形成。同时在该塑封层70、该晶片60以及铜基板50的底面形成一连接层83,该晶片60背面的信号接点通过该连接层83以铜基板50可连接至对应的导电端子82a。该连接层83可选用化学镀(electro-less plating)、溅镀(sputter)等技术完成,其较佳材料为铜。

42.在完成该导电层82以及连接层83之后,则对产品的正、反面进行后续的表面加工处理,使相邻导电端子82a、82b之间形成一阻焊层(solder mask),该表面加工处理流程包含如图2i~2k的步骤:

43.参照图2i,在连接层83的底面以及相邻导电端子82a之间分别以绝缘材形成一绝缘保护层84,该绝缘保护层84提供防水气、防氧化的功能。其中,在相邻导电端子82a、82b之间的绝缘保护层84作为阻焊层,避免相邻导电端子82a、82b在焊接过程中发生短路。

44.参照图2j所示,针对位于该连接层83背面的绝缘保护层84进行刻印(marking)制程,例如镭射刻印或是通过黄光制程形成所需的产品标记。

45.参照图2k所示,在完成刻印制程后,在各导电端子82a、82b的表面上进一步形成一接点防护层85a、85b,防止导电端子82a、82b发生氧化问题;另于该连接层83的背面亦形成

一防护层86,该防护层86不仅对该连接层83的表面提供防护作用,还可以与刻印完成后的绝缘保护层84的图案形成明显的视对对比,凸显绝缘保护层84的图案。该接点防护层85a、85b与防护层86可采用相同的制程同时制作完成,可利用无电电镀镍浸金(enig)方式同时完成。

46.前述表面加工处理流程2i~2k的制法可视需求改变顺序,举例而言,在如图2i完成绝缘保护层84之后,先在各导电端子82a、82b的表面上形成一接点防护层85a、85b,然后再针对位于该连接层83背面的绝缘保护层84进行刻印(marking)制程,如此一来,在该连接层83的背面即不需形成防护层86。

47.最后,请参照图2l所示,在预定的切割位置进行切割(sawing),令每一个晶片60及其塑封层70形成独立的封装产品。

48.上述第二实施例相较于第一实施例,该铜基板50具有一定的支撑性,能增加封装产品的结构强度。除此之外,该铜基板50在制作完成的封装产品中作为桥接导电块,可将晶片60背面的信号接点电性连接至封装产品的正面;由于桥接导电块形成在第一开孔71的下方,该第一开孔71a的深度相较于第一实施例的第一开孔深度可以降低,令导电层82更易于完整填充在第一开孔71a内部,确保较佳的电性连接。

49.关于本发明的第三较佳实施例,请参考图6a~图6i所示,在图6a中,首先制备一铜基板90,在该铜基板90上的底面贴合一层导电胶带98,该导电胶带98的表面具有黏性。其中,该铜基板90的结构与图3、图4所示的实施例相同,故不再赘述。

50.参照图6b,在各晶片容置开口91内部分别设置一晶片100,其中,该晶片100为一功率半导体晶片,在其正面及背面形成有用于电性连接的信号接点(图中未示),该晶片100与该导电胶带98互相黏着的一面定义为晶片背面,其相对的另一面为晶片正面。

51.参照图6c,将晶片100以一塑封层110包覆,该塑封层110的材料可为pp、emc等介电材质。该塑封层110成型后,若有必要可在其表面进行平坦化步骤,对该塑封层110的表面进行研磨(grinding)或清洁。

52.参照图6d,在该塑封层110的预设位置形成第一开孔(vias)111a及第二开孔111b,该第一开孔111a/第二开孔111b、的位置取决于产品所需的导电端子的位置,其中,晶片100周围的第一开孔111a延伸至该铜基板90,第二开孔111b从塑封层110的表面向下延伸到该晶片100正面的信号接点。该第一开孔111a/第二开孔111b的成形方式可通过例如镭射钻孔(laser drilling)、超音波钻孔(ultrasonic drilling)、微放电加工(micro electrical discharge machining,μ-edm)、微细磨料喷射加工(micro powder blasting)或是感应耦合电浆离子蚀刻(inductively coupled plasma reactive ion etching,icp-rie)等技术,本发明并不特别限制其成形方式。

53.参照图6e,在各个第一开孔111a/第二开孔111b的内部壁面以及该塑封层110、该晶片100的信号接点表面形成一预电镀层120,该预电镀层120作为后续制作导电层的种子层(seed layer),该预电镀层120的制作方式可选用化学镀(electro-less plating)、溅镀(sputter)等技术完成。

54.参照图6f,图案化的一导电层122填满在各个第一开孔111a/第二开孔111b的内部以及该塑封层110的表面,其中,在塑封层110表面的该导电层122通过蚀刻或其它图案化制程形成多个独立的导电端子。每一个第第一开孔111a/第二开孔111b位置可以为一独立的

导电端子122a、122b;或是根据晶片100设计多个第一开孔111a/第二开孔111b利用该导电层122彼此电性连接形成一共同接点。该导电层122的较佳材料为铜,其制作方式可通过电镀或印刷方式形成。

55.在完成该导电层122的制作之后,则对产品的正、反面进行后续的表面加工处理,使相邻导电端子122a、122b之间形成一阻焊层(solder mask),该表面加工处理流程包含如图6g~6i的步骤:

56.请参照图6g所示,在导电胶带98的底面以及相邻导电端子122a、122b之间分别以绝缘材形成一绝缘保护层124,该绝缘保护层124提供防水气、防氧化的功能。其中,在相邻导电端子122a、122b之间的绝缘保护层124作为阻焊层,避免相邻导电端子122a、122b在焊接过程中发生短路。

57.参照图6h所示,在各导电端子122a、122b的表面上进一步形成一接点防护层125a、125b,可利用无电电镀镍浸金(enig)方式形成。

58.参照图6i所示,针对位于该导电胶带98背面的绝缘保护层124进行刻印(marking)制程,例如镭射刻印或是通过黄光制程形成所需的产品标记。

59.前述表面加工处理流程6g~6i的制法可视需求改变顺序,举例而言,例如采用前述图2i~图2k所示的方式,先完成刻印步骤之后,再于产品的正、反两面利用无电电镀镍浸金(enig)方式形成防护层。

60.最后,请参照图6j所示,在预定的切割位置进行切割(sawing),令每一个晶片100及其塑封层110形成独立的封装产品。

61.依据前述三种实施例的制作方法,可分别得到如图7~图9的表面黏着式功率半导体封装元件。

62.参考图1a至图1m的制作方法以及各附图中的元件符号,可得到如图7的表面黏着式功率半导体封装元件,包含有:

63.一晶片20,其正面及背面分别具有信号接点;

64.一塑封层30,包覆该晶片20,且在该塑封层30中形成第一开孔31a及第二开孔31b,该第一开孔31a位在晶片20周围,该第二开孔31b对应延伸至晶片20正面的信号接点,在该第一开孔31a与第二开孔31b内部充满导电层42,其中,第二开孔31b中的导电层42电性连接该晶片20正面的信号接点;

65.一导通层,该第一开孔31a中的导电层42通过该导通层电性连接该晶片20背面的信号接点,该导通层由一导电镀层43构成;

66.该第一开孔31a及第二开孔31b中的导电层42凸出于该塑封层30的表面并构成该表面黏着式功率半导体封装元件的导电端子42a,42b。

67.参考图2a至图2l的制作方法以及各附图中的元件符号,可得到如图8的表面黏着式功率半导体封装元件,包含有:

68.一晶片60,其正面及背面分别具有信号接点;

69.一导电基板,形成有一晶片容置开口51,令该晶片60设置在该晶片容置开口51内部,该导电基板由一铜基板50构成;

70.一塑封层70,包覆该晶片60,且在该塑封层70中形成第一开孔71a及第二开孔71b,该第一开孔71a位在晶片60侧边并对应延伸至该导电基板的表面,该第二开孔71b对应延伸

至晶片60正面的信号接点,在各第一开孔71a与第二开孔71b内部填充导电层82,其中,第二开孔71b中的导电层82电性连接该晶片60正面的信号接点;

71.一导通层,该第一开孔71a中的导电层82通过该导电基板及该导通层电性连接该晶片80背面的信号接点,该导通层为复层结构,包含一预电镀层80及一连接层83;

72.该第一开孔71a及第二开孔71b中的导电层82凸出于该塑封层70的表面并构成该表面黏着式功率半导体封装元件的导电端子82a,82b。

73.参考图6a至图6j的制作方法以及各附图中的元件符号,可得到如图9的表面黏着式功率半导体封装元件,包含有:

74.一晶片100,其正面及背面分别具有信号接点;

75.一导电基板,形成有一晶片容置开口51,令该晶片60设置在该晶片容置开口51内部,该导电基板由一铜基板50构成;

76.一塑封层110,包覆该晶片100,且在该塑封层110中形成第一开孔111a及第二开孔111b,该第一开孔111a位在晶片100周围并延伸至该导电基板的表面,该第二开孔111b对应延伸至晶片100正面的信号接点,在各第一开孔111a与第二开孔111b内部填充导电层122,其中,第二开孔111b中的导电层122电性连接该晶片60正面的信号接点;

77.一导通层,该第一开孔111a中的导电层122通过该导电基板及该导通层电性连接该晶片100背面的信号接点,该导通层包含一黏着在该晶片100背面的导电胶带98;

78.该第一开孔111a及第二开孔111b中的导电层122凸出于该塑封层110的表面并构成该表面黏着式功率半导体封装元件的导电端子122a,122b。

79.借由上述具体实施例可以理解,本发明「表面黏着式功率半导体封装元件」产品具有以下特点:

80.一、制程中不需使用传统的导线架(lead frame)、打线(wire bonding),而且不必使用银胶或烧结银等昂贵的黏晶材料,便可以实现黏晶作业,减少制作成本。

81.二、产品厚度可以降低。

82.三、第一开孔/第二开孔内部填充的导电材,以及铜基板构成的导电块可提供良好的散热途径。

83.四、设置在晶片侧边的桥接导电件,田围绕于功率半导体晶片周围,能对该晶片产生的电磁干扰(emi)提供屏蔽作用。

84.以上所述仅是本发明的优选实施例而已,并非对本发明做任何形式上的限制,虽然本发明已以优选实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案的范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1