芯片封装结构及其制作方法与流程

本发明涉及一种封装结构,尤其涉及一种芯片封装结构及其制作方法。

背景技术:

1、目前,在次毫米发光二极管(mini led)面板或微型发光二极管(micro led)面板中,通常会将次毫米发光二极管或微型发光二极管设置于印刷电路板(或ic载板)的正表面,并将已封装的驱动ic(driver ic)配置于印刷电路板(或ic载板)的背表面或侧面。如此一来,将使得面板整体的厚度增加。

2、此外,由于印刷电路板(或ic载板)常有翘曲以及铜面平坦度不佳的问题,因此会不利于微型发光二极管的巨量转移,且增加组装失败的可能性,进而影响成品的良率。

技术实现思路

1、本发明是针对一种线路基板结构及其制造方法,具有可减薄整体厚度的技术效果或可有效地提升产品的良率。

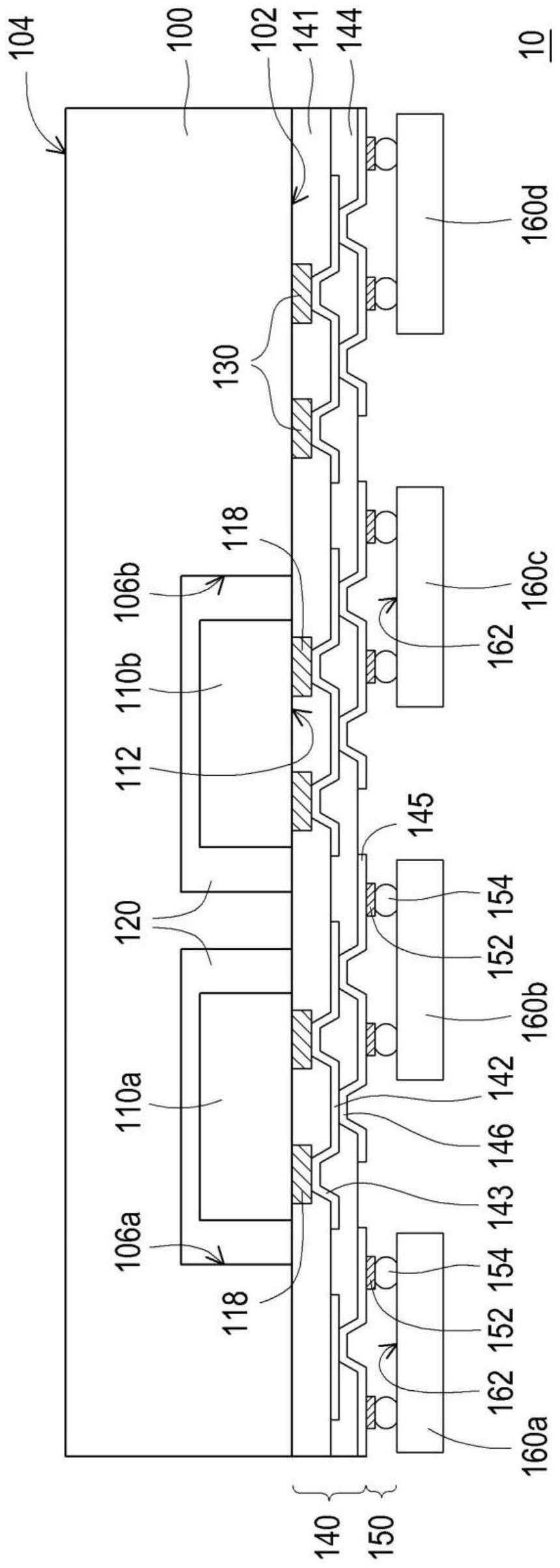

2、本发明的芯片封装结构包括基板、至少一第一芯片、黏着材料、重布线路结构以及多个第二芯片。基板具有第一表面、与第一表面相对的第二表面以及至少一凹槽。至少一第一芯片设置于凹槽中。黏着材料设置于至少一凹槽中,且位于基板与至少一第一芯片之间。重布线路结构设置于基板的第一表面上,且电性连接至至少一第一芯片。多个第二芯片设置于重布线路结构上,且电性连接至重布线路结构。

3、在本发明的一实施例中,上述的基板为玻璃基板或硅基板。

4、在本发明的一实施例中,上述的至少一第一芯片为裸晶。

5、在本发明的一实施例中,上述的多个第二芯片包括裸晶和/或封装芯片。

6、在本发明的一实施例中,上述的重布线路结构包括第一介电层、第一图案化线路层、第一导通孔、第二介电层、第二图案化线路层以及第二导通孔。第一介电层设置于基板的第一表面上。第一图案化线路层设置于第一介电层上。第一导通孔贯穿第一介电层,且第一导通孔电性连接第一图案化线路层与至少一第一芯片。第二介电层设置于第一图案化线路层上。第二图案化线路层设置于第二介电层上。第二导通孔贯穿第二介电层,且第二导通孔电性连接第二图案化线路层与第一图案化线路层。

7、在本发明的一实施例中,上述的至少一第一芯片的主动表面与基板的第一表面齐平。

8、在本发明的一实施例中,上述的芯片封装结构更包括连接件。连接件设置于重布线路结构上,其中多个第二芯片通过连接件电性连接至重布线路结构。

9、在本发明的一实施例中,上述的连接件包括接触垫以及焊接点。接触垫可连接重布线路结构。焊接点设置于接触垫上,且焊接点可电性连接至接触垫。

10、本发明的芯片封装结构的制作方法包括以下步骤:首先,提供基板,其中基板具有第一表面、与第一表面相对的第二表面以及至少一凹槽。接着,配置至少一第一芯片与黏着材料于至少一凹槽中,以使黏着材料位于基板与至少一第一芯片之间。接续,形成重布线路结构于基板的第一表面上,以电性连接至至少一第一芯片。而后,配置多个第二芯片于重布线路结构上,以电性连接至重布线路结构。

11、在本发明的一实施例中,上述形成重布线路结构于基板的第一表面上的方法包括以下步骤:首先,以平坦化制程形成第一介电层于基板的第一表面上。接着,形成第一图案化线路层于第一介电层上并形成第一导通孔于第一介电层中,其中第一导通孔贯穿第一介电层,且第一导通孔电性连接第一图案化线路层与至少一第一芯片。接续,形成第二介电层于第一图案化线路层上。而后,形成第二图案化线路层于第二介电层上并形成第二导通孔于第二介电层中,其中第二导通孔贯穿第二介电层,且电性连接第二图案化线路层与第一图案化线路层。

12、在本发明的一实施例中,上述芯片封装结构的制作方法更包括以下步骤:形成连接件于重布线路结构上,以使多个第二芯片通过连接件电性连接至重布线路结构。

13、基于上述,在本发明一实施例的芯片封装结构中,借由将第一芯片内埋于基板中,因而使得整体的厚度得以减薄。再者,由于本实施例的第一芯片可内埋于基板且为裸晶,因此,可以避免因使用封装芯片而造成基板有翘曲的问题,也可以维持基板的刚性与平坦度,进而提升产品的良率。

14、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

技术特征:

1.一种芯片封装结构,其特征在于,包括:

2.根据权利要求1所述的芯片封装结构,其特征在于,所述基板为玻璃基板或硅基板。

3.根据权利要求1所述的芯片封装结构,其特征在于,所述至少一第一芯片为裸晶。

4.根据权利要求1所述的芯片封装结构,其特征在于,所述多个第二芯片包括裸晶和/或封装芯片。

5.根据权利要求1所述的芯片封装结构,其特征在于,所述重布线路结构包括:

6.根据权利要求1所述的芯片封装结构,其特征在于,所述至少一第一芯片具有主动表面、与主动表面相对的背表面以及接垫,所述接垫设置于所述主动表面上,且所述至少一第一芯片通过所述接垫电性连接至所述重布线路结构。

7.根据权利要求6所述的芯片封装结构,其特征在于,所述至少一第一芯片的所述主动表面与所述基板的所述第一表面齐平。

8.根据权利要求1所述的芯片封装结构,其特征在于,还包括:

9.根据权利要求8所述的芯片封装结构,其特征在于,所述连接件包括:

10.一种芯片封装结构的制作方法,其特征在于,包括:

11.根据权利要求10所述的芯片封装结构的制作方法,其特征在于,形成所述重布线路结构于所述基板的所述第一表面上的步骤包括:

12.根据权利要求10所述的芯片封装结构的制作方法,其特征在于,还包括:

技术总结

本发明提供一种芯片封装结构极其制作方法,其中芯片封装结构包括基板、至少一第一芯片、黏着材料、重布线路结构以及多个第二芯片。基板具有第一表面、与第一表面相对的第二表面以及至少一凹槽。至少一第一芯片设置于凹槽中。黏着材料设置于至少一凹槽中,且位于基板与至少一第一芯片之间。重布线路结构设置于基板的第一表面上,且电性连接至至少一第一芯片。多个第二芯片设置于重布线路结构上,且电性连接至重布线路结构。本发明的芯片封装结构极其制作方法,具有可减薄整体厚度的技术效果或可有效地提升产品的良率。

技术研发人员:曾子章,刘汉诚,林溥如,柯正达

受保护的技术使用者:欣兴电子股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!