集成标准单元的设置的制作方法

1.本公开的实施方式和实施例涉及微电子领域,具体是集成电路,并且更具体是标准单元,诸如那些用于集成电路的数字逻辑电路的设计的标准单元。

背景技术:

2.在(例如,在绝缘体上硅(soi)类型衬底上生成的)集成电路中使用的晶体管之中,使用以下晶体管可能很有用:

[0003]-低电压阈值晶体管(低vt:电压阈值voltage threshold),具有例如绝对值约为0.25伏特的阈值电压,

[0004]-常规电压阈值晶体管(rvt:常规电压阈值regular voltage threshold),具有例如绝对值约为0.35伏特的阈值电压,以及

[0005]-高电压阈值(hvt)晶体管,通常具有绝对值约为0.45伏特的阈值电压。

[0006]

这些低电压阈值、常规电压阈值和高电压阈值的概念是本领域技术人员已知的并且取决于技术节点的值,并且上面指出的数值是针对小于90nm大约10%的技术节点而给出的。

[0007]

低电压阈值和常规电压阈值晶体管,特别是当它们包括sige沟道时,也就是说包括硅和锗时,特别被用于关键路径的生产,因为它们具有高速和良好的电流性能,也就是说,具有通常大于500微安/微米的处于导通状态的电流(离子电流)。

[0008]

另一方面,这样的晶体管具有显著的泄漏,也就是说,在晶体管的关断状态下具有相对高的电流ioff,通常约为1毫微安/微米到20或30毫微安/微米。

[0009]

此外,使用硅沟道高电压阈值晶体管是有趣的,因为它们具有低泄漏电流,通常约为0.05毫微安/微米。

[0010]

目前,人们可以在相同技术平台上找到仅使用sige沟道晶体管的集成电路或集成电路的部分以及仅使用硅沟道晶体管(诸如高电压阈值晶体管)的其他集成电路或相同集成电路的其他部分。

[0011]

然而,这样的布置会消耗空间。

[0012]

因此,需要能够在单个集成电路内对低电压阈值和常规电压阈值类型的硅锗沟道晶体管与高电压阈值类型的硅沟道晶体管进行组合。

技术实现要素:

[0013]

根据一个或多个实施例,提供了一种集成电路,其包括由两个第二标准单元框定的至少一个第一标准单元。

[0014]

这三个单元被彼此相邻设置,也就是说它们直接邻接或对接在一起或间接对接在一起,也就是说借助于一个或多个若干其他标准单元,例如将在下面更详细地看到的称为填充单元的单元。

[0015]

因此,两个相邻的单元例如以可以为零或小于或等于一百纳米的距离被间隔开。

[0016]

每个单元包括位于绝缘体上硅类型衬底中和上的至少一个nmos晶体管和至少一个pmos晶体管。

[0017]

所述第一标准单元的至少一个pmos晶体管具有包括硅和锗的沟道。

[0018]

所述每个第二标准单元的至少一个pmos晶体管具有硅沟道,每个第二标准单元的至少一个pmos晶体管的阈值电压与所述第一单元的至少一个pmos晶体管的阈值电压在绝对值上不同,例如大于所述第一单元的至少一个pmos晶体管的阈值电压。

[0019]

因此,表面拥挤的问题可以通过将包括硅锗沟道pmos晶体管和硅沟道pmos晶体管的标准单元彼此相邻放置来解决。因此可以混合具有不同阈值电压的晶体管,特别是将硅锗沟道低电压阈值和常规电压阈值晶体管与硅沟道高电压阈值晶体管混合。

[0020]

存在若干用于将这些标准单元彼此相邻设置的解决方案。

[0021]

发明人确实观察到,将硅锗沟道晶体管和硅沟道晶体管彼此相抵放置会导致性能下降,这在一些应用中可能是不方便的。

[0022]

此外,根据一个变型,集成电路还可以包括半导体连接区域,该半导体连接区域将所述第一标准单元(具有sige沟道的标准单元)的至少一个pmos晶体管的有源区和第二标准单元(具有硅沟道的标准单元)的pmos晶体管的有源区进行连接。

[0023]

半导体连接区域特别包括允许将两个有源区彼此绝缘的绝缘栅,但是半导体连接区域与晶体管的有源区一起形成连续的有源区,并且因此允许避免有源切割(active cut),有源切割将引起由硅锗引起的应力松弛,损害相关sige沟道晶体管的性能。

[0024]

并且,为了不过多地损害硅锗沟道pmos晶体管的性能,根据与该变型兼容的实施例,针对集成电路进行以下设置:包括被称为填充单元的至少两个标准单元,该至少两个填充单元框定第一标准单元,分别被设置在第一标准单元与两个第二标准单元之间,并且分别与第一标准单元和两个第二标准单元对接。

[0025]

每个填充单元包括:

[0026]-填充区域,具有与第一标准单元的pmos晶体管的有源区接触的包含硅和锗的第一部分和与对应的第二标准单元的pmos晶体管的有源区接触的包含硅的第二部分,以及

[0027]-两个第一多晶硅线(形成绝缘栅),分别位于填充单元与第一标准单元或第二标准单元之间的边界的上方,并且旨在以电源电压vdd进行偏置。

[0028]

这些填充区域形成所述半导体连接区域。

[0029]

添加这些填充硅锗区域的事实允许pmos晶体管的硅锗沟道中的应力不会过度松弛,并且因此限制了硅锗沟道pmos晶体管的性能损失。

[0030]

然而,为了不过度损害硅沟道晶体管的性能,特别有利的是断开这个连续的半导体区并且在硅沟道晶体管的有源区和硅锗沟道晶体管的有源区之间提供切口(cut),同时仍然使用包含硅和锗的填充单元,以免损害sige沟道pmos晶体管的性能。

[0031]

因此,根据一个实施例,集成电路包括被称为填充单元的至少两个标准单元,该至少两个填充单元框定第一标准单元,分别被设置在第一标准单元与两个第二标准单元之间,分别与第一标准单元和两个第二标准单元对接。

[0032]

每个填充单元包括包含硅和锗的填充区域以及至少一个第一多晶硅线,该包含硅和锗的填充区域与第一标准单元的pmos晶体管的有源区邻接,并且至少一个第一多晶硅线位于填充区域上方并且旨在保持电浮动。

[0033]

此外,填充区域通过绝缘区域与所述每个第二标准单元的至少一个pmos晶体管(即硅沟道pmos晶体管)的有源区分开。

[0034]

不管实施例如何,所述第一标准单元的至少一个pmos晶体管可以是低电压阈值晶体管,并且所述第二标准单元的至少一个pmos晶体管可以是高电压阈值晶体管。

[0035]

所述第一标准单元的至少一个pmos晶体管可以是常规电压阈值晶体管并且所述第二标准单元的至少一个pmos晶体管可以是高电压阈值晶体管。

[0036]

然而,由于填充单元的存在,刚刚提到的实施例在硅上占据了一定的位置。并且,在某些应用中,进一步降低这种表面拥挤可以是有利的。

[0037]

这是为什么在另一变型中计划取消这些标准填充单元并且断开有源区的连续性的原因。

[0038]

因此,根据另一变型,所述第一标准单元的至少一个nmos晶体管具有硅沟道和阈值电压,例如,常规电压阈值,该阈值电压在绝对值上等于或优选地大于(所述该第一标准单元的至少一个pmos晶体管的)阈值电压,例如,低电压阈值。

[0039]

此外,所述该第一标准单元的至少一个pmos晶体管的有源区与所述每个第二标准单元的至少一个pmos晶体管的有源区电绝缘。

[0040]

因此,在该变型中,例如,使用不包括常规电压阈值nmos晶体管和常规电压阈值pmos晶体管但使用常规电压阈值nmos晶体管和低电压阈值硅锗沟道pmos晶体管的标准单元,获得具有高电压阈值和硅沟道的晶体管与具有常规电压阈值的晶体管的混合体。

[0041]

在硅锗沟道上使用低电压阈值晶体管的事实允许补偿(特别是在泄漏电流方面)由第二单元的pmos晶体管的有源区与第一单元的pmos晶体管的有源区之间的断开引起的性能的下降。

[0042]

在这样的变型中,第一标准单元可以有利地与每个第二标准单元邻接。

[0043]

如前所述,所述第一单元的至少一个nmos晶体管可以是常规电压阈值晶体管,所述第一单元的至少一个pmos晶体管可以是低电压阈值晶体管,并且所述每个第二单元的至少一个pmos晶体管可以是高电压阈值晶体管。

[0044]

根据又一实施例,集成电路还可以包括一组三个附加标准单元,该三个附加标准单元形成在导通状态下的电流(离子电流)方面具有良好性能的组合。

[0045]

该组附加单元可以例如在集成电路中被添加到以上所定义的标准单元组合中的至少一个组合。

[0046]

因此,在本实施例中,集成电路还包括另一组第一附加标准单元,该另一组第一附加标准单元由两个第二附加标准单元框定。

[0047]

三个附加单元邻接(对接)并且每个附加单元包括具有硅沟道的至少一个nmos晶体管和具有包含硅和锗的沟道的至少一个pmos晶体管。

[0048]

所有pmos晶体管的有源区形成一个连续的半导体区。

[0049]

所述第一附加单元的至少一个pmos晶体管的阈值电压与第二附加单元的pmos晶体管的阈值电压在绝对值上不同。

[0050]

并且该集成电路还包括两个多晶硅线,该两个多晶硅线旨在以电源电压进行偏置并且分别被设置在所述第一附加单元的至少一个pmos晶体管的有源区与所述每个第二附加单元的至少一个pmos晶体管之间的边界的上方。

[0051]

所述第一附加单元的至少一个pmos晶体管可以是低电压阈值晶体管,并且第二附加单元的pmos晶体管可以是常规电压阈值晶体管。

[0052]

不管变型和实施例如何,绝缘体上硅型衬底可以是完全耗尽的绝缘体上硅(fdsoi)类型的衬底。

[0053]

根据另一实施例,提供了一种制造集成电路的方法,包括:

[0054]-在存储器中存储标准单元库,该标准单元库旨在在绝缘体上硅型衬底上生成并且包括至少一个第一标准单元和第二标准单元,每个单元包括至少一个nmos晶体管和至少一个pmos晶体管,所述第一标准单元的至少一个pmos晶体管具有包括硅和锗的沟道,所述第二标准单元的至少一个pmos晶体管具有硅沟道,并且所述第二标准单元的至少一个pmos晶体管的阈值电压与所述第一单元的至少一个pmos晶体管的阈值电压不同,例如在绝对值上大于所述第一单元的至少一个pmos晶体管的阈值电压。

[0055]-从存储器提取这些标准单元,并且放置这些单元以使得它们被彼此相邻设置,第一标准单元由两个第二标准单元框定,

[0056]-并且根据所述这些单元的放置,生成集成电路。

[0057]

根据一种实施方式,

[0058]-第一标准单元包括围绕所述至少一个nmos晶体管的有源区和所述至少一个pmos晶体管的有源区的绝缘区域,

[0059]-第二标准单元包括至少部分地围绕所述至少一个nmos晶体管的有源区和所述至少一个pmos晶体管的有源区的绝缘区域,

[0060]-第一标准单元的每个nmos晶体管具有硅沟道,第一标准单元的每个nmos晶体管的阈值电压在绝对值上等于并且优选地大于该第一标准单元的每个pmos晶体管的阈值电压,以及

[0061]-第二标准单元的每个pmos晶体管的阈值电压在绝对值上大于第一单元的每个nmos晶体管的阈值电压。

[0062]

此外,进行以下设置:第一标准单元由两个第二标准单元框定,该第一标准单元的放置使得第一标准单元的pmos晶体管的有源区与两个第二单元的pmos晶体管的有源区电绝缘。

[0063]

根据一种实施方式,所述第一单元的至少一个nmos晶体管是常规电压阈值晶体管,所述第一单元的至少一个pmos晶体管是低电压阈值晶体管并且所述第二单元的至少一个pmos晶体管是高电压阈值晶体管。

[0064]

根据一种实施方式,标准单元库还包括第一附加标准单元和第二附加标准单元,附加单元各自包括具有硅沟道的至少一个nmos晶体管和具有包含硅和锗的沟道的至少一个pmos晶体管,并且所述第一附加单元的至少一个pmos晶体管的阈值电压与所述第二附加单元的至少一个pmos晶体管的阈值电压在绝对值上不同,并且所述放置还包括设置这些附加单元以使得第一附加单元由两个第二附加单元以邻接的方式框定,所有附加单元的pmos晶体管的有源区形成连续的半导体区,第一附加单元或第二附加单元中的至少一个在其边缘上具有在对应有源区上方的多晶硅线,该多晶硅线旨在以电源电压进行偏置。

[0065]

根据一种实施方式,所述第一附加单元的至少一个pmos晶体管是低电压阈值晶体管并且所述第二附加单元的至少一个pmos晶体管是常规电压阈值晶体管。

[0066]

根据另一实施例,提供了一种标准单元,旨在在绝缘体上硅型衬底上生成并且包括:至少一个nmos晶体管,具有硅沟道;至少一个pmos晶体管,具有包括硅和锗的沟道,并且该至少一个pmos晶体管的阈值电压在绝对值上低于所述至少一个nmos晶体管的阈值电压;以及绝缘区域,围绕所述至少一个nmos晶体管的有源区和所述至少一个pmos晶体管的有源区。

[0067]

根据一个实施例,所述至少一个nmos晶体管是常规电压阈值晶体管并且所述至少一个pmos晶体管是具有低电压阈值的晶体管。

附图说明

[0068]

在查看实施例和实施方式以及附图的详细描述后,本公开的其他优势和特征将变得明显,这些实施方式和实施例绝不是限制性的,其中:

[0069]

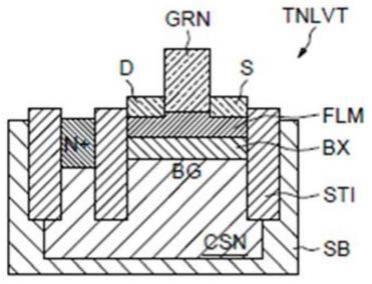

图1至图6示意性地示出了根据一个或多个实施例的在绝缘体上硅型(例如,完全耗尽的绝缘体上硅类型的)衬底上生成的具有不同阈值电压的nmos和pmos晶体管。

[0070]

图7示意性地示出了根据一个或多个实施例的包括借助于两个填充单元由两个第二标准单元框定的第一标准单元的集成电路。

[0071]

图8示意性地示出了根据一个或多个实施例的包括第一标准单元的集成电路,该第一标准单元包括具有形成其栅极的多晶硅线的两个锗硅沟道pmos晶体管。

[0072]

图9示意性地示出了根据一些实施例的包括由两个第二标准单元以对接方式框定的第一标准单元的集成电路。

[0073]

图10示意性地示出了根据一个或多个实施例的包括由两个第二附加标准单元以对接方式框定的第一附加标准单元的集成电路。

[0074]

图11示意性地示出了根据一个或多个实施例的制造集成电路的方法。

具体实施方式

[0075]

图1至图6示意性地示出了在绝缘体上硅型(例如,完全耗尽的绝缘体上硅类型的)衬底上生成的具有不同阈值电压的nmos和pmos晶体管。

[0076]

将在下面描述的标准单元中使用的nmos晶体管具有硅沟道。

[0077]

除了具有硅沟道的高电压阈值pmos晶体管之外,将在下面描述的标准单元中使用的pmos晶体管具有硅锗沟道。

[0078]

在图1中,参考tnlvt表示低电压阈值nmos晶体管,通常约为0.25伏特的低电压阈值nmos晶体管。

[0079]

该nmos晶体管在半导体膜flm中和上生成,该半导体膜flm被设置在掩埋绝缘区域bx(本领域技术人员已知的名称为box:buried oxyde)的上方。

[0080]

掩埋绝缘层bx位于在半导体衬底sb中形成的n型掺杂半导体阱csn的上方。

[0081]

位于掩埋层bx下方的阱csn的部分形成了后栅极bg,该后栅极bg这里由被设置在两个绝缘区域sti之间的n+型接触来偏置。

[0082]

晶体管tnlvt还包括源极s和漏极d的升高区域以及这里包含具有n型输出功的金属的栅极grn。

[0083]

该晶体管tnlvt具有全硅沟道。

[0084]

半导体膜flm这里是本征硅,也就是说具有小于10

11

atoms/cm3的掺杂浓度。

[0085]

图2中所示的晶体管tnrvt是常规电压阈值nmos晶体管,也就是说约为0.35伏特的常规电压阈值nmos晶体管。

[0086]

晶体管tnrvt可以通过半导体膜flm的掺杂与图1的晶体管tnlvt进行区别。

[0087]

事实上,对于晶体管tnrvt,薄膜flm的掺杂浓度约为10

18

atoms/cm3。

[0088]

该晶体管tnrvt可以是硅沟道晶体管。

[0089]

图3示出了具有高电压阈值的nmos晶体管tnhvt,通常约为0.45伏特的nmos晶体管。

[0090]

该晶体管tnhvt也可以具有硅沟道。

[0091]

它与图2中的晶体管tnrvt的区别在于,它包括包含具有p型输出功的金属的栅极grp,而晶体管tnrvt具有包含具有n型输出功的金属的grn。

[0092]

晶体管tnhvt的薄膜flm的掺杂浓度可以与图2的晶体管tnrvt的薄膜flm的掺杂浓度相同。

[0093]

图4至图6示出了具有不同阈值电压的pmos晶体管。

[0094]

图4示出了具有低电压阈值的pmos晶体管tplvt,其沟道包括硅和锗,例如si

1-x

ge

x

合金,其中x介于0.1(10%)与0.4(40%)之间,优选地等于0.2(20%)。

[0095]

它的结构类似于图1的nmos晶体管tnlvt的结构,但可以通过掺杂剂的类型进行区分。

[0096]

更具体地,对于晶体管tplvt,后栅极(rear gate)bg所在的半导体阱为p型掺杂阱csp,可以通过p+接触进行偏置。

[0097]

源区s和漏区d是p掺杂的。相比之下,栅极grn包含具有n型输出功的金属。

[0098]

由于阈值电压为低电压,因此膜flm是本征硅锗。

[0099]

图5的晶体管tprvt是常规电压阈值pmos晶体管,具有硅锗沟道,并且可以通过薄膜flm的掺杂浓度与图4的晶体管tplvt进行简单区分,该薄膜flm的掺杂浓度可以等于图2的晶体管tnrvt的薄膜flm的掺杂浓度。

[0100]

图6所示的晶体管tphvt是硅沟道高电压阈值pmos晶体管。

[0101]

该晶体管tphvt与图5的晶体管tprvt不同,一方面,通过该晶体管tphvt的栅极grp包含具有p型输出功的金属的事实,并且另一方面,通过晶体管tphvt的沟道包含本征硅而非硅锗(sige)的事实,允许将pmos晶体管的阈值电压在绝对值上增加250mv或300mv。

[0102]

在本文的其余部分,附图标记以lvt为结尾的晶体管是低电压阈值晶体管,附图标记以rvt为结尾的晶体管是常规电压阈值晶体管,并且附图标记以hvt为结尾的晶体管是高电压阈值晶体管。

[0103]

在图7中,附图标记ic表示在该示例中包括借助于两个填充单元stdfl1由两个第二标准单元std2框定的第一标准单元std1的集成电路。

[0104]

更具体地,这里的第一标准单元std1包括两个sige沟道pmos晶体管tplvt(sige)和两个si沟道nmos晶体管tnlvt(si)。

[0105]

形成这些晶体管的栅极grn的多晶硅线高出这两个晶体管tplvt(sige)的有源区za。

[0106]

这里的每个第二标准单元std2包括两个硅沟道pmos晶体管tphvt(si)和两个硅沟

道nmos晶体管tnhvt(si)。

[0107]

形成这些晶体管tphvt的栅极grp的多晶硅线也高出这些晶体管tphvt(si)的有源区za。

[0108]

每个填充单元stdfl1包括填充区域flrg1,该填充区域flrg1包括由与晶体管tplvt(sige)的有源区za接触的硅锗形成的第一部分p1和与晶体管tphvt(si)的有源区za接触的包含硅的第二部分p2,以便形成连续的半导体区。

[0109]

两个部分p1和p2形成两个缓冲区(tplvt侧的sige和tphvt侧的si)允许吸收si/sige跃迁。

[0110]

该集成电路还包括两个多晶硅线gri。

[0111]

每个线gri分别与在填充单元stdfl1和单元std1或std2之间的边界重叠。

[0112]

这些多晶硅线gri连接到电源电压vdd(例如,约为1伏特),以便形成允许将晶体管tphvt(si)与晶体管tplvt(sige)电绝缘的绝缘栅极。

[0113]

位于两个绝缘栅极之间的多晶硅线gri可以保持浮动。

[0114]

图8的实施例与图7的实施例的区别特别在于,在硅沟道晶体管tphvt(si)和硅锗沟道晶体管tplvt(sige)之间不再存在连续的半导体区。

[0115]

实际上,这种连续性在晶体管tphvt(si)的边缘处被破坏,以免降低该晶体管的性能。

[0116]

更具体地,这里的集成电路ic1包括第一标准单元std10,该第一标准单元std10再次包括两个锗硅沟道pmos晶体管tplvt(sige),形成其栅极的多晶硅线grn高出其有源区za。

[0117]

该第一标准单元std10还包括两个硅沟道nmos晶体管tnlvt(si)。

[0118]

第一标准单元std10借助于两个填充单元stdfl10由两个第二标准单元std20框定。

[0119]

这里的每个第二单元std20包括两个硅沟道pmos晶体管tphvt(si)和两个硅沟道nmos晶体管tnhvt(si)。

[0120]

形成这些pmos晶体管的栅极grp的两个多晶硅线高出pmos晶体管的有源区za。

[0121]

每个填充单元stdfl10包括填充区域flrg10,该填充区域flrg10由扩展晶体管tplvt(sige)的有源区za的硅和锗形成。

[0122]

另一方面,每个填充单元包括绝缘区域ris,该绝缘区域ris允许将填充区域flrg10与对应第二标准单元std20的晶体管tphvt(si)的有源区za绝缘。

[0123]

为了保持硅线间距,可以在不同晶体管的栅极之间插入保持浮动的硅线lpl。

[0124]

为了节省空间,可以消除填充单元,同时省去包含pmos晶体管的所有有源区的连续半导体区,也就是说破坏这种连续性。

[0125]

在这方面,可以由以下进行设置:包含nmos晶体管和具有相同阈值电压的pmos晶体管(例如常规电压阈值晶体管)的第一标准单元,该第一标准单元由具有硅沟道pmos晶体管(例如具有高电压阈值)的两个第二标准单元以对接方式框定。

[0126]

然而,在这种情况下,第一标准单元的pmos晶体管的性能下降,尤其是关于离子电流,这在一些应用中可能是不方便的。

[0127]

为了克服这种性能损失,还可以使用第一“混合”标准单元,也就是说具有nmos晶

体管和pmos晶体管,nmos晶体管和pmos晶体管具有不同的阈值电压,通常pmos晶体管在绝对值上与nmos晶体管的阈值电压相比具有更低阈值电压。

[0128]

这种配置的一个示例如图9所示。

[0129]

在该图9中,集成电路ic2包括第一标准单元std100,该第一标准单元std100由两个第二标准单元std200以对接方式框定。

[0130]

第一单元std100包括硅沟道nmos晶体管tnrvt(si)和硅锗沟道pmos晶体管tplvt(sige)。

[0131]

绝缘区域ris(例如,包括二氧化硅)围绕晶体管tnrvt和tplvt的每个有源区za。

[0132]

因此这里可以看出,与通常的标准单元不同,nmos晶体管的阈值电压与pmos晶体管的电压不同。

[0133]

更具体地说,nmos晶体管tnrvt(si)是常规电压阈值晶体管,而pmos晶体管tplvt(sige)是低电压阈值晶体管,但实际上如下所示,由于有源区的断开,其将具有常规类型电压阈值。

[0134]

这里的每个第二标准单元std200包括两个硅沟道nmos晶体管tnhvt(si)和两个硅沟道pmos晶体管tphvt(si)。

[0135]

形成这些晶体管的栅极grp的多晶硅线高出这些晶体管的有源区za。

[0136]

同样,这些晶体管的有源区za至少部分地由绝缘区域ris围绕。

[0137]

由于第一标准单元和第二标准单元的pmos晶体管之间的有源区的不连续性,晶体管tplvt的阈值电压将在绝对值上增加,并且该pmos晶体管tplvt(sige)的ion电流性能被影响并且该离子电流减小。

[0138]

因此,晶体管tplvt将像常规电压阈值晶体管一样工作,并且具有相同的阈值电压电平。

[0139]

因此,该实施例的显著之处在于,它提供了具有高电压阈值和硅沟道的晶体管与具有常规电压阈值和sige沟道的晶体管的混合,同时限制了由于没有填充单元而导致的拥挤。

[0140]

因此,存在提供具有不同阈值电压和低泄漏(低电流ioff)的晶体管的混合的标准单元的组合。

[0141]

在图10所示的集成电路中可以存在标准单元的其他组合。例如,这些其他组合可以在集成电路中被添加到图9中的单元组合。

[0142]

图10的集成电路ic3包括由两个第二附加标准单元stds2以对接方式框定的第一附加标准单元stds1。

[0143]

第一单元stds1包括硅锗沟道pmos晶体管tprvt(sige)和硅沟道nmos晶体管tnrvt(si)。

[0144]

形成这些晶体管的栅极的多晶硅线grn高出这些晶体管的有源区。

[0145]

每个第二附加单元stds2包括硅锗沟道pmos晶体管tplvt(sige)和硅沟道nmos晶体管tnlvt(si)。这里同样,形成这些晶体管的栅极的多晶硅线grn高出这些晶体管的有源区za。

[0146]

这些附加单元的pmos晶体管的有源区za彼此接触以形成连续的半导体区。

[0147]

为了将晶体管tplvt(sige)与晶体管tprvt(sige)电绝缘,以电源电压vdd进行偏

置的多晶硅线gri与在晶体管tprvt(sige)与tplvt(sige)的有源区za之间的边界重叠。

[0148]

这里,因此获得了一组标准单元,该一组标准单元提供了具有不同阈值电压和在离子电流方面高性能的晶体管的混合。

[0149]

现在更具体地参考图11来说明方法的实施方式的示例。

[0150]

标准单元的库lbr被存储在存储器mm中,该库lbr特别包括上述的单元std1、std2、std10、std20、std100、std200、stds1、stds2、stdfl1和stdfl10。

[0151]

这里应当注意,即使所有这些单元在存储器mm中表示,单元stds2、std1和std10在基本单元特性(lvt型单元)方面是相同的,并且仅它们的邻接将不同。

[0152]

对于在基本单元特性(hvt型单元)方面相同的单元std20和std200也是如此。

[0153]

然后,在步骤st110中,执行这些标准单元中的一些标准单元的提取,然后执行这些被提取的单元的放置st111,以便获得要生成的集成电路部件的期望配置,诸如,例如在图7到图10中所示的配置。

[0154]

然后,根据单元的这种放置,以本身已知的常规方式生成集成电路ic、ic1、ic2或ic3(步骤st112)。

[0155]

集成电路可以被概括为:包括至少一个第一标准单元(std100),该第一标准单元(std100)由两个第二标准单元(std200)框定,该三个单元被彼此相邻放置,每个单元包括位于绝缘体上硅型衬底中和上的至少一个nmos晶体管(tnrvt)和至少一个pmos晶体管(tplvt),所述第一标准单元(std100)的至少一个pmos晶体管(tplvt)具有包括硅和锗的沟道,所述每个第二标准单元的至少一个pmos晶体管(tphvt)具有硅沟道,每个第二标准单元的至少一个pmos晶体管(tphvt)的阈值电压与所述第一单元的至少一个pmos晶体管(tplvt)的阈值电压在绝对值上不同。

[0156]

集成电路还可以包括半导体连接区域(flrg1),该半导体连接区域(flrg1)将所述第一标准单元(std1)的至少一个pmos晶体管的有源区和第二标准单元(std2)的pmos晶体管的有源区进行连接。

[0157]

集成电路可以包括被称为填充单元的至少两个标准单元(stdfl1),该两个填充单元框定第一标准单元,分别被设置在第一标准单元(std1)与两个第二标准单元(std2)之间,分别与第一标准单元和两个第二标准单元对接,每个填充单元包括填充区域(flrg1)以及两个第一多晶硅线(gri),该填充区域具有包含硅和锗的第一部分(p1)以及包含硅的第二部分(p2),该包含硅和锗的第一部分(p1)与第一标准单元的pmos晶体管的有源区接触,并且该包含硅的第二部分(p2)与对应的第二标准单元的pmos晶体管的有源区接触,并且两个第一多晶硅线(gri)分别位于填充单元与第一标准单元(std1)或第二标准单元(std2)之间的边界的上方,并且旨在以电源电压进行偏置,填充区域形成所述半导体连接区域。

[0158]

集成电路可以包括被称为填充单元的至少两个标准单元(stdfl10),该两个填充单元框定第一标准单元(std10),分别被设置在第一标准单元(std10)与两个第二标准单元(std20)之间,分别与第一标准单元和两个第二标准单元对接,每个填充单元包括包含硅和锗的填充区域以及至少一个第一多晶硅线,该包含硅和锗的填充区域邻接于第一标准单元的pmos晶体管的有源区,并且该至少一个第一多晶硅线位于填充区域的上方并且旨在保持电浮动,填充区域通过绝缘区域(ris)与所述每个第二标准单元的至少一个pmos晶体管的有源区分开。

[0159]

所述第一标准单元的至少一个pmos晶体管可以是低电压阈值晶体管(tplvt)并且所述第二标准单元的至少一个pmos晶体管可以是高电压阈值晶体管(tphvt)。所述第一标准单元的至少一个pmos晶体管可以是常规电压阈值晶体管(tpvrt)并且所述第二标准单元的至少一个pmos晶体管可以是高电压阈值晶体管(tphvt)。所述第一标准单元(std100)的至少一个nmos晶体管可以具有硅沟道,所述第一标准单元(std100)的至少一个nmos晶体管的阈值电压在绝对值上等于或优选地大于所述该第一标准单元的至少一个pmos晶体管的阈值电压,并且所述该第一标准单元的至少一个pmos晶体管的有源区可以与所述每个第二标准单元(std200)的至少一个pmos晶体管的有源区电绝缘。第一标准单元(std100)可以邻接于每个第二标准单元(std200)。所述第一单元(std100)的至少一个nmos晶体管可以是常规电压阈值晶体管(tnrvt),所述第一单元(std100)的至少一个pmos晶体管可以是低电压阈值晶体管(tplvt)并且所述每个第二单元(std200)的至少一个pmos晶体管可以是高电压阈值晶体管(tphvt)。

[0160]

集成电路还可以包括由两个第二附加标准单元(stds2)框定的另一组第一附加标准单元(stds1),三个附加单元被邻接并且每个附加单元包括具有硅沟道的至少一个nmos晶体管和具有包含硅和锗的沟道的至少一个pmos晶体管,所有pmos晶体管的有源区形成连续的半导体区,所述第一附加单元的至少一个pmos晶体管的阈值电压与第二附加单元的pmos晶体管的阈值电压在绝对值上不同,并且集成电路还包括两个多晶硅线,该两个多晶硅线旨在以电源电压进行偏置并且分别被设置在所述第一附加单元的至少一个pmos晶体管的有源区与所述每个第二附加单元的至少一个pmos晶体管之间的边界的上方。

[0161]

所述第一附加单元(stds1)的至少一个pmos晶体管可以是低电压阈值晶体管(tplvt)并且第二附加单元(stds2)的pmos晶体管可以是常规电压阈值晶体管(tprvt)。绝缘体上硅型衬底可以是完全耗尽的绝缘体上硅型衬底。

[0162]

一种用于制造集成电路的方法可以被概括为包括:在存储器(mm)中存储标准单元库(lbr),该标准单元库(lbr)旨在在绝缘体上硅型衬底上生成并且包括至少一个第一标准单元和第二标准单元,每个单元包括至少一个nmos晶体管和至少一个pmos晶体管,所述第一标准单元的至少一个pmos晶体管具有包括硅和锗的沟道,所述第二标准单元的至少一个pmos晶体管具有硅沟道,所述第二标准单元的至少一个pmos晶体管的阈值电压与所述第一单元的至少一个pmos晶体管的阈值电压在绝对值上不同;从存储器提取(st110)这些标准单元,并且放置(st111)这些单元以使得它们被彼此相邻设置,第一标准单元由两个第二标准单元框定;以及根据所述这些单元的放置,生成(st112)集成电路。

[0163]

第一标准单元可以包括围绕所述至少一个nmos晶体管的有源区和所述至少一个pmos晶体管的有源区的绝缘区域,第二标准单元可以包括至少部分地围绕所述至少一个nmos晶体管的有源区和所述至少一个pmos晶体管的有源区的绝缘区域,第一标准单元的每个nmos晶体管可以具有硅沟道,第一标准单元的每个nmos晶体管在绝对值上大于该第一标准单元的每个pmos晶体管的阈值电压的阈值电压,并且第二标准单元的每个pmos晶体管的阈值电压在绝对值上大于第一单元的每个nmos晶体管的阈值电压,并且其中单元的放置可以包括放置第一标准单元(std100)以使得第一标准单元的pmos晶体管的有源区与两个第二单元的pmos晶体管的有源区电绝缘,该第一标准单元(std100)由两个第二标准单元(std200)以邻接的方式框定。所述第一单元的至少一个nmos晶体管可以是常规电压阈值晶

体管(tnrvt),所述第一单元的至少一个pmos晶体管可以是低电压阈值晶体管(tplvt)并且所述第二单元的至少一个pmos晶体管可以是高电压阈值晶体管(tphvt)。标准单元库还可以包括第一附加标准单元(stds1)和第二附加标准单元(stds2),附加单元各自包括具有硅沟道的至少一个nmos晶体管和具有含有硅和锗的沟道的至少一个pmos晶体管,并且所述第一附加单元的至少一个pmos晶体管的阈值电压与所述第二附加单元的至少一个pmos晶体管的阈值电压在绝对值上不同,并且所述放置还可以包括设置这些附加单元以使得第一附加单元由两个第二附加单元框定,所有附加单元的pmos晶体管的有源区形成连续的半导体区,第一附加单元或第二附加单元中的至少一个在其边缘上具有在对应有源区上方的多晶硅线,该多晶硅线旨在以电源电压进行偏置。所述第一附加单元的至少一个pmos晶体管可以是低电压阈值晶体管(tplvt)并且所述第二附加单元的至少一个pmos晶体管可以是常规电压阈值晶体管(tprvt)。

[0164]

标准单元可以被概括为:旨在绝缘体上硅型衬底上生成,并且包括:至少一个nmos晶体管(tnrvt),具有硅沟道;至少一个pmos晶体管(tplvt),具有包括硅和锗的沟道,并且该至少一个pmos晶体管(tplvt)的阈值电压在绝对值上等于或优选地低于所述至少一个nmos晶体管的阈值电压;以及绝缘区域,围绕所述至少一个nmos晶体管的有源区和所述至少一个pmos晶体管的有源区的。

[0165]

所述至少一个nmos晶体管可以是常规电压阈值晶体管(tnrvt)并且所述至少一个pmos晶体管可以是具有低电压阈值(tplvt)的晶体管。

[0166]

可以对上述各种实施例组合以提供进一步的实施例。根据以上详细描述,可以对实施例进行这些和其他改变。一般而言,在以下权利要求中,所使用的术语不应被解释为将权利要求限于说明书和权利要求中所公开的特定实施例,而应被解释为包括权利要求所要求的所有可能的实施例以及与其等效的全部范围。因此,权利要求不受本公开的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1