半导体装置的制作方法

1.本发明涉及半导体装置。

背景技术:

2.在用于移动通信、卫星通信等的电子设备中组装有将高频信号的收发功能一体化的rf前端模块。rf前端模块具备:具有高频放大功能的单片微波集成电路元件(mmic)、控制高频放大电路的控制ic、开关ic、双工器等。

3.下述的专利文献1中公开了在mmic上堆叠控制ic而小型化的高频模块。专利文献1所公开的高频模块包括搭载于模块基板上的mmic、和堆叠于mmic上的控制ic。mmic的电极、控制ic的电极以及模块基板上的电极通过引线接合而电连接。

4.专利文献1:美国专利申请公开第2015/0303971号说明书。

5.在高频放大电路中例如使用异质结双极晶体管(hbt)。hbt在动作中产生集电极损耗而发热。发热引起的hbt的温度上升作用于使集电极电流进一步增大的方向。若满足该正反馈的条件,则导致hbt热失控。为了避免hbt的热失控,限制hbt的输出功率的上限值。

6.为了实现高频放大电路的高输出化,优选提高来自包含hbt等的半导体装置的散热特性。在专利文献1所公开的高频模块中,难以满足近年来对高频放大电路的高输出化的要求。

技术实现要素:

7.本发明的目的在于提供一种能够提高散热特性的半导体装置。

8.根据本发明的一个观点,提供一种半导体装置,具备:

9.第一部件,具有第一面,在俯视上述第一面时,在上述第一面的内部配置有包含开关的至少一个开关电路;

10.第二部件,与上述第一部件的上述第一面面接触地接合,包含构成高频放大电路的化合物半导体系的多个晶体管;以及

11.第一导体突起,从上述第二部件向上述第一部件侧的相反侧突出,

12.上述第一部件包含电路元件,上述电路元件在俯视时配置于上述高频放大电路与上述至少一个开关电路之间,且不构成上述至少一个开关电路。

13.形成有从多个晶体管通过第一部件与第二部件的接合界面到达第一部件的传热路径、和从第二部件经由第一导体突起到达安装有半导体装置的模块基板的传热路径这两个路径。因此,能够提高来自晶体管的散热特性。另外,在高频放大电路与至少一个开关电路之间配置有不构成开关电路的电路元件,因此能够提高高频放大电路与开关电路之间的绝缘性。

附图说明

14.图1是包含第一实施例的半导体装置的高频模块的框图。

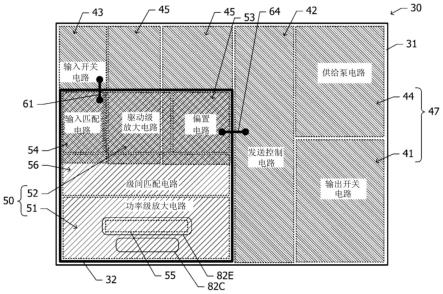

15.图2是表示包含第一实施例的半导体装置的高频模块的电路部件的俯视时的位置关系的图。

16.图3是第一实施例的半导体装置的示意剖视图。

17.图4a是构成第一实施例的半导体装置的功率级放大电路的多个单元的各个的等效电路图,图4b是构成形成于第二部件的功率级放大电路的一个单元的示意剖视图。

18.图5a是表示第一实施例的半导体装置的各构成要素的俯视时的配置的示意图,图5b是表示构成功率级放大电路的多个晶体管的俯视时的配置的图。

19.图6a和图6b是用于说明两个电路之间的区域的示意图。

20.图7a~图7f的附图是制造中途阶段的半导体装置的剖视图。

21.图8a~图8c的附图是制造中途阶段的半导体装置的剖视图,图8d是完成后的半导体装置的剖视图。

22.图9是表示第二实施例的半导体装置的各构成要素的俯视时的配置的示意图。

23.图10是第二实施例的半导体装置的示意剖视图。

24.图11是表示第三实施例的半导体装置的各构成要素的俯视时的配置的示意图。

25.图12是表示第三实施例的变形例的半导体装置的各构成要素的俯视时的配置的示意图。

26.附图标记说明

27.20

…

高频模块;21

…

模块基板;30

…

半导体装置;31

…

第一部件;31a

…

第一面;32

…

第二部件;32b

…

第三部件;41、41b

…

输出开关电路;42、42b

…

发送控制电路;43、43b

…

输入开关电路;44

…

充电泵电路;45

…

其它电路;47

…

开关电路;50、50b

…

高频放大电路;51、51b

…

功率级放大电路;52、52b

…

驱动级放大电路;53、53b

…

偏置电路;54、54b

…

输入匹配电路;55

…

多个晶体管分布的区域;56、56b

…

级间匹配电路;61、61b

…

布线;62、62b、63

…

焊盘;64、64b

…

布线;67

…

层间绝缘膜;68

…

保护膜;70

…

双工器;71

…

低噪声放大器;72

…

天线开关;73

…

频带选择开关;74

…

输出端子选择开关;75

…

接收控制电路;76

…

输出匹配电路;82、82b、82c、82e

…

导体突起;82p

…

cu柱;82s

…

焊锡层;83

…

导体突起;101

…

基底半导体层;101a

…

导电区域;101b

…

元件分离区域;102b

…

基极层;102c

…

集电极层;102e

…

发射极层;103b

…

基极电极;103c

…

集电极;103e

…

发射极电极;104b

…

基极布线;104bb

…

基极偏置布线;104c

…

集电极布线;104e

…

发射极布线;105e

…

发射极布线;105rf

…

高频信号输入布线;111、112

…

层间绝缘膜;200

…

母基板;201

…

剥离层;204

…

连结支承体;210

…

基板;311

…

基板;312

…

多层布线结构;313、313b

…

金属图案;314、314b

…

导通孔;315、316

…

布线;317

…

第一部件保护膜。

具体实施方式

28.[第一实施例]

[0029]

参照图1~图8d的附图,对第一实施例的半导体装置进行说明。以下进行说明的第一实施例的半导体装置是高频功率放大器。

[0030]

图1是包含第一实施例的半导体装置30的高频模块20的框图。该高频模块20包含第一实施例的半导体装置30、输出匹配电路76、多个双工器70、天线开关72、两个接收用的频带选择开关73、两个低噪声放大器71、接收用的输出端子选择开关74、以及接收控制电路

75。这些电路部件倒装式安装于模块基板。该高频模块20具有进行频分双工(fdd)方式的收发的功能。

[0031]

半导体装置30包含第一部件31和与第一部件31接合的第二部件32。例如,第一部件31由元素半导体系构成,第二部件32由化合物半导体构成。在第一部件31形成有输入开关电路43、发送控制电路42、以及输出开关电路41。在第二部件32形成有由功率级放大电路51及驱动级放大电路52构成的两级结构的高频放大电路50、偏置电路53、输入匹配电路54以及级间匹配电路56。驱动级放大电路52是初级的放大电路,功率级放大电路51是末级的放大电路。在图1中,在设置于第一部件31的电路上标注相对较浅的阴影线,在设置于第二部件32的电路上标注相对较深的阴影线。

[0032]

偏置电路53根据来自发送控制电路42的控制信号,向功率级放大电路51及驱动级放大电路52供给偏置电流。

[0033]

输入开关电路43的两个输入接点分别与设置于模块基板的高频信号输入端子in1、in2连接。从两个高频信号输入端子in1、in2输入高频信号。输入开关电路43从两个输入接点选择一个接点,将输入到所选择的接点的高频信号经由输入匹配电路54输入到驱动级放大电路52。

[0034]

在驱动级放大电路52被放大的高频信号经由级间匹配电路56输入到功率级放大电路51。在功率级放大电路51被放大的高频信号通过输出匹配电路76输入到输出开关电路41的一个输入接点。输出开关电路41从多个输出接点选择一个接点,将在高频放大电路50中被放大的高频信号从所选择的输出接点输出。

[0035]

输出开关电路41的多个输出接点中的两个接点分别与设置于模块基板的辅助输出端子paaux1、paaux2连接。其它的六个接点分别与按照每个频带准备的多个双工器70的发送用输入端口连接。输出开关电路41具有从按照每个频带准备的多个双工器70中选择一个双工器70的功能。

[0036]

天线开关72具有电路侧的多个接点和天线侧的两个接点。天线开关72的多个电路侧的接点中的两个接点分别与发送信号输入端子trx1、trx2连接。电路侧的其它的六个接点分别与多个双工器70的输入输出共享端口连接。天线侧的两个接点分别与天线端子ant1、ant2连接。在天线端子ant1、ant2分别连接有天线。

[0037]

天线开关72将两个天线侧的接点分别与从电路侧的多个接点中选择的两个接点连接。在使用一个频带进行通信的情况下,天线开关72将电路侧的一个接点和天线侧的一个接点连接。在高频放大电路50中被放大且通过了对应的频带用的双工器70的高频信号从与所选择的天线侧的接点连接的天线被发送。

[0038]

两个接收用的频带选择开关73的各个具有四个输入接点和一个输出接点。两个频带选择开关73的各个的四个输入接点中的三个接点分别与双工器70的接收用输出端口连接。两个频带选择开关73各自的剩余的一个接点分别与辅助输入端子lnaaux1、lnaaux2连接。

[0039]

两个接收用的频带选择开关73的输出接点分别与两个低噪声放大器71连接。两个接收用的频带选择开关73分别使通过了双工器70的接收信号输入到低噪声放大器71。

[0040]

输出端子选择开关74的两个电路侧的接点分别与两个低噪声放大器71的输出端口连接。输出端子选择开关74的三个端子侧的接点分别与接收信号输出端子lnaout1、

lnaout2、lnaout3连接。在低噪声放大器71中被放大的接收信号从由输出端子选择开关74选择的接收信号输出端子输出。

[0041]

从设置于模块基板的电源端子vcc1、vcc2分别向功率级放大电路51以及驱动级放大电路52施加电源电压。

[0042]

发送控制电路42与电源端子vio1、控制信号端子sdata1、以及时钟端子sclk1连接。发送控制电路42基于提供给控制信号端子sdata1的控制信号来控制偏置电路53、输入开关电路43以及输出开关电路41。

[0043]

接收控制电路75与电源端子vio2、控制信号端子sdata2以及时钟端子sclk2连接。接收控制电路75基于提供给控制信号端子sdata2的控制信号来控制低噪声放大器71、接收用的频带选择开关73以及输出端子选择开关74。

[0044]

在模块基板还设置有电源端子vbat以及漏极电压端子vdd2。从电源端子vbat向偏置电路53以及发送控制电路42供给电源。从漏极电压端子vdd2向低噪声放大器71施加电源电压。

[0045]

图2是表示包含第一实施例的半导体装置的高频模块20的电路部件的俯视时的位置关系的图。在模块基板21安装有半导体装置30、多个双工器70、低噪声放大器71、天线开关72、以及其它的表面安装型的多个无源部件。半导体装置30的第一部件31在俯视时比第二部件32大,且包含第二部件32。

[0046]

输出匹配电路76由配置于模块基板内的电感器等的无源元件和表面安装于模块基板的电容器等构成。构成输出匹配电路76的电感器配置在俯视时与半导体装置30重叠的位置。此外,也可以由集成型无源部件构成输出匹配电路76。

[0047]

图3是第一实施例的半导体装置30的示意剖视图。第一部件31包括基板311、配置于其上的多层布线结构312、以及覆盖多层布线结构312的表面的第一部件保护膜317。基板311包含元素半导体系的半导体部分。作为基板311,例如使用硅基板或者绝缘体上硅(soi)基板。输出开关电路41(图1)、发送控制电路42(图1)以及输入开关电路43(图1)由形成于基板311的表层部的半导体元件以及多层布线结构312内的布线构成。在图3中,用虚线包围形成有输入开关电路43的区域并示出。将第一部件31的最表面称为第一面31a。在第一部件保护膜317的一部分设置有开口,在开口填充有金属膜318。第一部件保护膜317及金属膜318的上表面相当于第一面31a。

[0048]

第二部件32与第一部件31的第一面31a面接触地接合。另外,在俯视时,第二部件32的至少一部分与金属膜318的至少一部分重叠,第二部件32与金属膜318面接触。在第二部件32形成有图1所示的功率级放大电路51、驱动级放大电路52、偏置电路53、输入匹配电路54以及级间匹配电路56。在图3中,用虚线包围配置有输入匹配电路54的区域并示出。

[0049]

以覆盖第二部件32的方式,在第一面31a上配置有层间绝缘膜67。在层间绝缘膜67的规定位置设置有多个开口。在层间绝缘膜67上配置有焊盘62、63、以及布线61。配置有焊盘62、63、以及布线61的布线层有时被称为再布线层。再布线层内的布线61有时被称为再布线。

[0050]

布线61通过设置于层间绝缘膜67的开口,将形成于第二部件32的电路和形成于第一部件31的电路连接。例如,布线61通过设置于层间绝缘膜67的开口,经由多层布线结构312内的布线315与输入开关电路43连接,并且通过设置于层间绝缘膜67的另一开口与输入

匹配电路54连接。在再布线层内除了布线61以外还配置有其它的多个布线。再布线层内的布线例如用于图1所示的发送控制电路42和偏置电路53的连接。

[0051]

焊盘62在俯视时包含于第二部件32,并与形成于第二部件32的电路连接。另一焊盘63在俯视时配置于第二部件32的外侧,经由多层布线结构312内的布线316与形成于第一部件31的输入开关电路43连接。

[0052]

在层间绝缘膜67上配置有保护膜68以覆盖再布线层。在保护膜68设置有使焊盘62、63的各自的上表面的一部分区域露出的开口。在焊盘62、63上分别配置有导体突起82、83。导体突起82包括与焊盘62连接的cu柱82p、和配置于cu柱82p的上表面的焊锡层82s。这样的结构的导体突起82被称为cu柱状凸块。

[0053]

此外,为了提高密接性,也可以在cu柱82p的底面配置凸块下金属层。另一导体突起83也具有与导体突起82相同的层叠结构。此外,代替cu柱状凸块,也可以在导体突起82、83等中使用au凸块、焊锡球凸块、竖立在焊盘上的导体柱等。如au凸块那样,不载置焊锡层的凸块也被称为柱。竖立在焊盘上的导体柱也被称为接线柱。

[0054]

导体突起82例如用于图1所示的电源端子vcc1和功率级放大电路51的连接、电源端子vcc2和驱动级放大电路52的连接、功率级放大电路51和输出匹配电路76的连接。并且,导体突起82用于第二部件32内的接地导体和模块基板的接地导体的连接。

[0055]

导体突起83例如用于图1所示的输入开关电路43和高频信号输入端子in1、in2的连接、发送控制电路42和电源端子vio1、控制信号端子sdata1、以及时钟端子sclk1的连接、输出开关电路41和输出匹配电路76、多个双工器70等的连接。

[0056]

在多层布线结构312内配置有至少一层的金属图案313、以及多个导通孔314。多个导通孔314在厚度方向上连接金属图案313彼此、或者金属膜318和金属图案313。多个金属图案313在俯视时与第二部件32的一部分区域重叠。配置于最下方的布线层的金属图案313经由多个导通孔314与基板311连接。金属图案313不与第一部件31的任一电路电连接。金属膜318、金属图案313以及导通孔314作为从第二部件32到达基板311的传热路径发挥功能。另外,导体突起82除了作为电流路径的功能之外,还具有作为从第二部件32到达模块基板的传热路径的功能。

[0057]

图4a是构成第一实施例的半导体装置30的功率级放大电路51(图1)的多个单元的各个的等效电路图。功率级放大电路51由相互并联连接的多个单元构成。此外,驱动级放大电路52(图1)也具有与功率级放大电路51同样的电路结构。但是,构成驱动级放大电路52的单元的个数比构成功率级放大电路51的单元的个数少。

[0058]

各单元包括晶体管q、输入电容器cin以及镇流电阻元件rb。晶体管q的基极经由输入电容器cin与高频信号输入布线105rf连接。并且,晶体管q的基极经由镇流电阻元件rb与基极偏置布线104bb连接。晶体管q的发射极接地。晶体管q的集电极与集电极布线104c连接。经由集电极布线104c向晶体管q的集电极施加电源电压,并且从集电极输出被放大后的高频信号。

[0059]

图4b是构成形成于第二部件32的功率级放大电路51(图1)的一个单元的示意剖视图。第二部件32包括基底半导体层101。基底半导体层101与第一部件31面接触,从而第二部件32与第一部件31接合。基底半导体层101被划分为导电区域101a和元件分离区域101b。在基底半导体层101中例如使用gaas。导电区域101a由n型gaas形成,元件分离区域101b通过

将绝缘杂质离子注入到n型gaas层而形成。

[0060]

在导电区域101a上配置有晶体管q。晶体管q包括从导电区域101a起依次层叠的集电极层102c、基极层102b、以及发射极层102e。发射极层102e配置于基极层102b的一部分区域上。作为一个例子,集电极层102c由n型gaas形成,基极层102b由p型gaas形成,发射极层102e由n型ingap形成。即,晶体管q是异质结双极晶体管。作为晶体管q,也可以使用其它的化合物半导体系的半导体元件。

[0061]

在基极层102b上配置有基极电极103b,基极电极103b与基极层102b电连接。在发射极层102e上配置有发射极电极103e,发射极电极103e与发射极层102e电连接。在导电区域101a上配置有集电极103c。集电极103c经由导电区域101a与集电极层102c电连接。

[0062]

在基底半导体层101上配置有第一层的层间绝缘膜111以覆盖晶体管q、集电极103c、基极电极103b、以及发射极电极103e。第一层的层间绝缘膜111例如由sin等无机绝缘材料形成。在层间绝缘膜111的规定的多个位置分别设置有开口。

[0063]

在层间绝缘膜111上配置有第一层的发射极布线104e、基极布线104b、集电极布线104c、基极偏置布线104bb。并且,在层间绝缘膜111上配置有镇流电阻元件rb。发射极布线104e通过设置于层间绝缘膜111的开口与发射极电极103e连接。基极布线104b通过设置于层间绝缘膜111的其它开口与基极电极103b连接。集电极布线104c通过设置于层间绝缘膜111的其它开口与集电极103c连接。

[0064]

基极布线104b延伸至未配置有晶体管q的区域,其前端与镇流电阻元件rb的一个端部重叠。在重叠部分,基极布线104b和镇流电阻元件rb电连接。镇流电阻元件rb的另一个端部与基极偏置布线104bb重叠。在重叠部分,镇流电阻元件rb和基极偏置布线104bb电连接。

[0065]

在层间绝缘膜111上配置有第二层的层间绝缘膜112以覆盖第一层的发射极布线104e、基极布线104b、基极偏置布线104bb、以及镇流电阻元件rb。第二层的层间绝缘膜112也由sin等无机绝缘材料形成。

[0066]

在层间绝缘膜112上配置有第二层的发射极布线105e以及高频信号输入布线105rf。第二层的发射极布线105e通过设置于层间绝缘膜112的开口与第一层的发射极布线104e连接。高频信号输入布线105rf的一部分在俯视时与第一层的基极布线104b重叠。在两者的重叠区域形成有输入电容器cin。

[0067]

配置有第三层的层间绝缘膜67以覆盖第二层的发射极布线105e以及高频信号输入布线105rf。第三层的层间绝缘膜67例如由聚酰亚胺等有机绝缘材料形成。此外,第三层的层间绝缘膜67如图3所示那样扩展至第一部件31上。

[0068]

在第三层的层间绝缘膜67上配置有焊盘62。焊盘62通过设置于层间绝缘膜67的开口与第二层的发射极布线105e连接。

[0069]

图5a是表示第一实施例的半导体装置30的各构成要素的俯视时的配置的示意图。在俯视时,第二部件32包含于第一部件31。

[0070]

在俯视第一部件31的第一面31a(图3)时,在第一面31a的内部配置有输入开关电路43、发送控制电路42、输出开关电路41、充电泵电路44、其它的电路45。在其它的电路45中例如包括静电保护电路、熔断器电路、温度补偿电路等。在图5a中,在第一部件31的配置有这些电路的区域标注相对较深的向右下方倾斜的阴影线。此外,“配置有电路的区域”意味

着在俯视时包含构成电路的有源元件、无源元件等多个电路元件、以及将这些电路元件彼此连接的布线的一个区域。

[0071]

在第二部件32配置有驱动级放大电路52和功率级放大电路51的两级结构的高频放大电路50、偏置电路53、输入匹配电路54、以及级间匹配电路56。在图5a中,在第二部件32的配置有这些电路的区域标注相对较浅的向右上方倾斜的阴影线。

[0072]

输入开关电路43和输入匹配电路54通过再布线层的布线61(图3)相互连接。发送控制电路42和偏置电路53通过再布线层的其它的布线64相互连接。

[0073]

充电泵电路44通过周期性的时钟信号反复开关的接通断开,从而使施加到电容器的电压的极性反转并使输入电压升压。如图1所示,输出开关电路41是在一个输入接点与多个输出接点之间进行高频信号的接通断开的开关。这样,将包含进行接通断开动作的开关的充电泵电路44以及输出开关电路41统称为开关电路47。充电泵电路44和输出开关电路41相互邻接而配置。

[0074]

在俯视时,充电泵电路44和输出开关电路41与第二部件32隔开间隔而配置。输入开关电路43、其它的电路45在俯视时与第二部件32重叠。

[0075]

在俯视时,在形成于第二部件32的高频放大电路50与配置于第一部件31的开关电路47之间的区域配置有发送控制电路42。即,在第一部件31中的高频放大电路50与开关电路47之间的区域配置有不构成开关电路47的至少一个电路元件。不构成开关电路47的电路元件例如包括形成于第一部件31的有源元件、无源元件、熔断器等。

[0076]

图5b是表示构成功率级放大电路51的多个晶体管q(图4a、图4b)的俯视时的配置的图。多个晶体管q的各个包括集电极层102c以及基极层102b。在俯视时,集电极层102c的外周线和基极层102b的外周线大致一致。发射极层102e(图4b)在俯视时包含于基极层102b。晶体管q的各个在俯视时在一个方向(在图5b中上下方向)上具有长的形状。多个晶体管q的各个的长边方向平行,多个晶体管q在与长边方向正交的方向(在图5b中左右方向)上排列而配置。

[0077]

多个晶体管q在区域55内分布。多个晶体管q分布的区域55被定义为例如在俯视时包含多个晶体管q的最小的凸多边形。

[0078]

也可以将由多个晶体管q构成的晶体管列在与晶体管q排列的方向正交的方向上配置有多列。在这种情况下,将包含多个晶体管列所包含的全部的晶体管q的最小的凸多边形定义为多个晶体管q分布的区域55即可。

[0079]

如图5a所示,在功率级放大电路51内配置有多个晶体管q分布的区域55。导体突起82e、82c分别与多个晶体管q的发射极以及集电极连接。在俯视时,发射极用的导体突起82e包含多个晶体管q分布的区域55。在构成功率级放大电路的电路块内还配置有图4a及图4b所示的输入电容器cin以及镇流电阻元件rb。

[0080]

接下来,参照图6a和图6b,对“两个电路之间的区域”进行说明。

[0081]

图6a和图6b是用于说明两个电路之间的区域的示意图。在使连接第一电路a1所包含的多个电路要素和第二电路a2所包含的多个电路要素的线段中长度最短的线段lmin向与线段lmin正交的方向移动时,将线段lmin通过的区域标记为lpass。图6a表示存在多个线段lmin的例子,图6b表示仅存在一个线段lmin的例子。

[0082]

将区域lpass中的在与线段lmin正交的方向上配置有第一电路a1及第二电路a2的

至少一方的范围定义为第一电路a1与第二电路a2之间的区域ab(在图6a、图6b中标注阴影线的区域)。在第一电路a1及第二电路a2分别配置在多个分离的区域的情况下,对于分离的区域分别定义“两个电路之间的区域”。

[0083]

接下来,参照图7a~图8d的附图,对第一实施例的半导体装置30的制作方法进行说明。图7a~图8c的附图是制造中途阶段的半导体装置30的剖视图,图8d是完成后的半导体装置30的剖视图。

[0084]

如图7a所示,在gaas等化合物半导体的单晶的母基板200上使剥离层201外延生长,在剥离层201上形成元件形成层202。在元件形成层202形成有图4b所示的第二部件32的晶体管q、第一层的布线层、第二层的布线层等。这些电路元件以及布线层由一般的半导体工艺形成。在图7a中,对于形成于元件形成层202的元件结构省略记载。在该阶段,元件形成层202未被分离成各个第二部件32。

[0085]

接下来,如图7b所示,将抗蚀剂图案(未图示)作为蚀刻掩模,图案形成元件形成层202(图5a)以及剥离层201。在该阶段,元件形成层202(图5a)被分离成每个第二部件32。

[0086]

接下来,如图7c所示,在分离后的第二部件32上粘贴连结支承体204。由此,多个第二部件32经由连结支承体204相互连结。此外,也可以在图7b的图案形成工序中残留作为蚀刻掩模使用的抗蚀剂图案,使抗蚀剂图案介于第二部件32与连结支承体204之间。

[0087]

接下来,如图7d所示,对母基板200以及第二部件32选择性地蚀刻剥离层201。由此,第二部件32以及连结支承体204从母基板200剥离。为了选择性地蚀刻剥离层201,作为剥离层201,使用蚀刻耐性与母基板200及第二部件32的任一个均不同的化合物半导体。

[0088]

如图7e所示,准备形成有设置于第一部件31(图3)的输入开关电路43以及多层布线结构312(图3)等的基板210。在该阶段,基板210未被分离成各个第一部件31。

[0089]

如图7f所示,将第二部件32与基板210接合。第二部件32与基板210的接合由范德瓦耳斯键或者氢键形成。除此之外,也可以通过静电、共价键合、共晶合金键合等将第二部件32与基板210接合。例如,在基板210的表面的一部分由au形成的情况下,也可以使第二部件32与au区域密接并进行加压,从而将两者接合。

[0090]

接下来,如图8a所示,从第二部件32剥离连结支承体204。在剥离了连结支承体204之后,如图8b所示,在基板210以及第二部件32上形成层间绝缘膜67以及再布线层。再布线层包含布线61、焊盘62、63(图3)等。

[0091]

接下来,如图8c所示,在再布线层上形成保护膜68,在保护膜68的规定位置形成开口。然后,在开口内以及保护膜68上形成导体突起82。形成导体突起82的同时,也形成其它的导体突起83(图3)等。

[0092]

最后,如图8d所示,切割基板210。由此,得到半导体装置30。

[0093]

接下来,对第一实施例的优异的效果进行说明。

[0094]

在第一实施例中,如图3所示,形成有从第二部件32朝向第一部件31的传热路径。第二部件32与第一部件31面接触,因此第二部件32和第一部件31通过低的热电阻热耦合。并且,在第二部件32的正下方的多层布线结构312内配置有金属图案313以及导通孔314,因此与第二部件32的正下方的多层布线结构312的整个区域由绝缘材料形成的结构相比,从第二部件32到基板311的传热路径的热电阻变低。此外,金属图案313不与第一部件31的任一电路块电连接,因此作为传热路径发挥功能的金属图案313对第一部件31的电路块的动

作不产生影响。此外,也可以将金属图案313与第一部件31内的接地导体电连接。

[0095]

从第二部件32传导到第一部件31的热量在第一部件31内扩散。在第一部件31内扩散的热量从第一部件31的表面向外部放射。在半导体装置30以安装于模块基板的状态被模制树脂覆盖的情况下,从第一部件31向模制树脂传导热量。

[0096]

并且,导体突起82作为从第二部件32到模块基板的传热路径发挥功能。这样,通过从第二部件32朝向模块基板的传热路径、和从第二部件32朝向第一部件31的传热路径这两个路径进行散热。因此,能够提高来自第二部件32的散热特性。为了得到提高散热特性的充分的效果,优选在第一部件31的基板311的半导体部分使用热导率比形成在第二部件32形成的半导体元件的化合物半导体高的半导体、例如si、ge等元素半导体。另外,作为形成于第二部件32的半导体元件,为了放大高频信号,优选使用电子迁移率比第一部件31的基板311的半导体部分高的化合物半导体系的半导体元件。

[0097]

在第二部件32中的构成功率级放大电路51的多个晶体管q分布的区域55(图5a)特别容易产生发热。为了减少从多个晶体管q分布的区域55到第一部件31的基板311(图3)的传热路径的热电阻,优选以多个晶体管q分布的区域55在俯视时包含于金属图案313(图3)的方式配置金属图案313。并且,优选以多个晶体管q分布的区域55在俯视时包含于金属膜318(图3)的方式配置金属膜318。

[0098]

另外,在第一实施例中,第二部件32(图5a)与第一部件31的输入开关电路43、以及其它的电路45重叠。因此,与第二部件32不与第一部件31的任一电路重叠的情况相比,能够减小半导体装置30的俯视时的尺寸。

[0099]

并且,在第一实施例中,开关电路47与高频放大电路50在面内方向隔开间隔而配置,因此能够提高高频放大电路50与开关电路47的绝缘性。例如,能够抑制在输出开关电路41以及充电泵电路44中产生的杂波混入在高频放大电路50中被放大的或者放大后的高频信号中。另外,能够抑制由功率级放大电路51放大后的高频信号的高次谐波直接耦合到输出开关电路41而不被输出匹配电路76(图1)过滤的情况。

[0100]

此外,输入开关电路43和驱动级放大电路52相互接近而配置,但由于以下的理由,不易产生使开关电路47和高频放大电路50接近的情况下的问题。通过输入开关电路43和输入匹配电路54,实现驱动级放大电路52的输入侧的阻抗匹配。因此,在输入开关电路43与驱动级放大电路52之间不需要高的绝缘性。另外,通过输入开关电路43的信号的电平比通过输出开关电路41的信号的电平足够低。因此,在输入开关电路43中,也存在不使用由充电泵电路44产生的负电压的情况。在这种情况下,输入开关电路43与输出开关电路41相比,提高与其它电路的绝缘性的必要性较低。

[0101]

将高频放大电路50和开关电路47相互隔开间隔而配置,并在两者之间配置发送控制电路42,因此即使将高频放大电路50和开关电路47相互隔开间隔而配置,也不会导致半导体装置30的大型化。

[0102]

并且,在第一实施例中,将充电泵电路44和输出开关电路41邻接而配置。通过在充电泵电路44中产生的负电压,使输出开关电路41动作。将产生使输出开关电路41动作的负电压的充电泵电路44配置在输出开关电路的附近,因此能够抑制开关的误动作。另外,将两者连接的布线变短,因此能够抑制从周围的电路向输出开关电路41的经由布线的杂波的混入。

[0103]

接下来,对第一实施例的变形例进行说明。

[0104]

在第一实施例(图3)中,由第一部件31的金属膜318、多层布线结构312内的多个金属图案313以及多个导通孔314(图3)构成的传热路径与第二部件32以及基板311接触,但由金属膜318、金属图案313以及多个导通孔314构成的传热路径未必需要与第二部件32以及基板311接触。例如,由多个金属图案313以及多个导通孔314构成的传热路径也可以经由绝缘膜与第二部件32以及基板311热耦合。在这种情况下,绝缘膜作为从第二部件32到基板311的传热路径的一部分发挥功能。另外,也可以不配置金属膜318,将第一面31a的整个区域设为第一部件保护膜317。在这种情况下,第一部件保护膜317中的与第二部件32接触的部分主要作为传热路径发挥功能。

[0105]

另外,在不配置金属图案313以及导通孔314的情况下,从第二部件32到基板311的传热路径的热电阻变高,但在能够确保功率级放大电路51的充分的输出的情况下,也可以未必配置金属图案313以及导通孔314。在这种情况下,多层布线结构312所包含的绝缘膜作为传热路径发挥功能。

[0106]

在第一实施例(图5a)中,在高频放大电路50与开关电路47之间配置发送控制电路42,但也可以配置不构成开关电路47的其它电路的电路元件。优选配置于高频放大电路50与开关电路47之间的电路为与充电泵电路44以及输出开关电路41相比不易产生杂波的电路。或者,可以将在高频放大电路50的动作中不进行动作的电路配置于高频放大电路50与开关电路47之间。作为这样的电路,列举出静电保护电路、温度补偿电路、熔断器电路等。

[0107]

在第一实施例中,将半导体装置30搭载于频分双工(fdd)方式的高频模块20(图1)中,但也能够搭载于时分双工(tdd)方式的高频模块中。

[0108]

在将半导体装置30搭载于tdd方式的高频模块的情况下,使用收发切换开关作为输出开关电路41(图1)。收发切换开关具有两个接点和一个共有端子。两个接点中的一个接点经由输出匹配电路76(图1)与功率级放大电路51连接,另一个接点与用于放大接收信号的低噪声放大器71(图1)连接,或者经由接收用的频带选择开关73(图1)与低噪声放大器71连接。共有端子经由滤波器与天线端子连接。在使用收发切换开关作为输出开关电路41的情况下,也与第一实施例同样,在输出开关电路41(图5a)与高频放大电路50之间配置发送控制电路42。

[0109]

[第二实施例]

[0110]

接下来,参照图9和图10对第二实施例的半导体装置进行说明。以下,对于与参照图1~图8d的附图进行说明的第一实施例的半导体装置相同的结构省略说明。

[0111]

图9是表示第二实施例的半导体装置30的各构成要素的俯视时的配置的示意图。在图9中与图5a同样,在第一部件31的配置有各电路的区域标注相对较深的向右下方倾斜的阴影线,在第二部件32的配置有各电路的区域标注相对较浅的向右上方倾斜的阴影线。

[0112]

在第一实施例的半导体装置30(图5a)中,在第一部件31接合有一个第二部件32,但在第二实施例的半导体装置30中,在第一部件31除了第二部件32之外还接合有第三部件32b。第二部件32的结构与第一实施例的半导体装置30的第二部件32的结构相同。第三部件32b与第二部件32同样,包括:包含功率级放大电路51b及驱动级放大电路52b的两级结构的高频放大电路50b、偏置电路53b、输入匹配电路54b、以及级间匹配电路56b。

[0113]

与第一实施例的半导体装置30的第一部件31同样,在第一部件31配置有第二部件

32用的输入开关电路43、发送控制电路42、以及输出开关电路41。还配置有第三部件32b用的输入开关电路43b、发送控制电路42b、以及输出开关电路41b。还配置有第二部件32和第三部件32b共享的充电泵电路44。另外,与第一实施例同样,在第一部件31配置有其它的电路45。

[0114]

在俯视时,在第二部件32的高频放大电路50与第二部件32用的输出开关电路41之间配置有第三部件32b用的输出开关电路41b。第二部件32用的输出开关电路41配置于第三部件32b的高频放大电路50b与第三部件32b用的输出开关电路41b之间。

[0115]

在充电泵电路44与第二部件32的高频放大电路50之间配置有其它的电路45以及第三部件32b用的输出开关电路41b。在充电泵电路44与第三部件32b的高频放大电路50b之间配置有其它的电路45以及第二部件32用的输出开关电路41。

[0116]

即,第二部件32的高频放大电路50和第二部件32用的输出开关电路41相互隔开间隔而配置。同样地,第三部件32b的高频放大电路50b和第三部件32b用的输出开关电路41b也相互隔开间隔而配置。

[0117]

第三部件32b的输入匹配电路54b和第三部件32b用的输入开关电路43b通过再布线层的布线61b相互连接。第三部件32b的偏置电路53b和第三部件32b用的发送控制电路42b通过再布线层内的布线64b相互连接。

[0118]

第二部件32的高频放大电路50和第三部件32b的高频放大电路50b以相互不同的频带动作。一个高频放大电路50和另一个高频放大电路50b选择性地进行动作,两者不同时动作。

[0119]

图10是第二实施例的半导体装置30的示意剖视图。除了第二部件32之外,第三部件32b也与第一部件31的第一面31a面接触而接合。对于第三部件32b也与第二部件32同样,配置有焊盘62b、导体突起82b、布线61b、金属膜318b、至少一层的金属图案313b、以及多个导通孔314b。导体突起82b从第三部件32b突出。金属膜318b、多层布线结构312内的金属图案313b以及多个导通孔314b在俯视时与第三部件32b重叠。再布线层内的布线61b将第三部件32b的输入匹配电路54b和形成于第一部件31的第三部件32b用的输入开关电路43b相互连接。

[0120]

接下来,对第二实施例的优异的效果进行说明。

[0121]

在第二实施例中也与第一实施例同样,第二部件32的高频放大电路50和第二部件32用的输出开关电路41相互隔开间隔而配置,因此能够提高两者之间的绝缘性。同样地,能够提高第三部件32b的高频放大电路50b和第三部件32b用的输出开关电路41b之间的绝缘性。

[0122]

在第二实施例中,在第二部件32的高频放大电路50的附近配置有第三部件32b用的输出开关电路41b,在第三部件32b的高频放大电路50b的附近配置有第二部件32用的输出开关电路41。但是,高频放大电路50和高频放大电路50b不同时动作。因此,即使在相互接近而配置的高频放大电路50与输出开关电路41b之间、以及高频放大电路50b与输出开关电路41之间产生电磁耦合,高频放大电路50以及高频放大电路50b的动作实质上也不会受到这些电磁耦合的影响。

[0123]

并且,第三部件32b与第一部件31面接触,并且相对于第三部件32b也设置有导体突起82b,因此能够提高来自第三部件32b的散热特性。

[0124]

[第三实施例]

[0125]

接下来,参照图11对第三实施例的半导体装置进行说明。以下,对于与参照图9和图10进行说明的第二实施例的半导体装置相同的结构省略说明。

[0126]

图11是表示第三实施例的半导体装置30的各构成要素的俯视时的配置的示意图。在图11中与图9同样,在第一部件31的配置有各电路的区域标注相对较深的向右下方倾斜的阴影线,在第二部件32的配置有各电路的区域标注相对较浅的向右上方倾斜的阴影线。

[0127]

在第三实施例中也与第二实施例同样,第二部件32和第三部件32b与第一部件31面接触而接合。第二部件32和第三部件32b的结构与第二实施例的半导体装置30(图9、图10)的第二部件32和第三部件32b的结构相同。

[0128]

在第一部件31配置有第二部件32用的发送控制电路42及输出开关电路41、第三部件32b用的发送控制电路42b及输出开关电路41b。配置于第一部件31的输入开关电路43被第二部件32和第三部件32b共享。

[0129]

再布线层的布线61、64与第二实施例同样,连接第二部件32的电路和第一部件31的电路,布线61b、64b连接第三部件32b的电路和第一部件31的电路。

[0130]

在第三实施例中,在第二部件32的高频放大电路50与第二部件32用的输出开关电路41之间配置有第二部件32用的发送控制电路42。该位置关系与第一实施例的半导体装置30(图5a)的位置关系同样。另外,在第三部件32b的高频放大电路50b与第三部件32b用的输出开关电路41b之间配置有第三部件32b用的发送控制电路42b。

[0131]

在充电泵电路44与第二部件32的高频放大电路50之间配置有第二部件32用的发送控制电路42和第三部件32b用的发送控制电路42b。在充电泵电路44与第三部件32b的高频放大电路50b之间也配置有第二部件32用的发送控制电路42和第三部件32b用的发送控制电路42b。

[0132]

并且,在第二部件32的高频放大电路50与第三部件32b用的输出开关电路41b之间、以及第三部件32b的高频放大电路50b与第二部件32用的输出开关电路41之间的任一个均配置有第二部件32用的发送控制电路42和第三部件32b用的发送控制电路42b。

[0133]

接下来,对第三实施例的优异的效果进行说明。

[0134]

在第三实施例中也与第二实施例同样,将第二部件32的高频放大电路50和第二部件32用的输出开关电路41相互隔开间隔而配置,因此能够提高两者之间的绝缘性。同样地,能够提高第三部件32b的高频放大电路50b与第三部件32b用的输出开关电路41b之间的绝缘性。

[0135]

在第二实施例(图9)中,第二部件32的高频放大电路50和第三部件32b用的输出开关电路41b接近而配置。与此相对,在第三实施例中,第二部件32的高频放大电路50和第三部件32b用的输出开关电路41b隔开间隔而配置。因此,能够提高高频放大电路50与输出开关电路41b之间的绝缘性。同样地,能够提高高频放大电路50b与输出开关电路41之间的绝缘性。因此,能够得到即便使第二部件32的高频放大电路50和第三部件32b的高频放大电路50b同时动作,也不易产生两者之间的电磁干扰的优异的效果。

[0136]

接下来,参照图12对第三实施例的变形例进行说明。

[0137]

图12是表示第三实施例的变形例的半导体装置30的各构成要素的俯视时的配置的示意图。在图12中与图11同样,在第一部件31的配置有各电路的区域标注相对较深的向

右下方倾斜的阴影线,在第二部件32的配置有各电路的区域标注相对较浅的向右上方倾斜的阴影线。

[0138]

在第三实施例中,在第一部件31接合有第二部件32和第三部件32b,在第二部件32和第三部件32b分别形成有驱动级放大电路52、52b、功率级放大电路51、51b等。与此相对,在本变形例中,在第一部件31接合有一个第二部件32,在一个第二部件形成有两个驱动级放大电路52、52b、两个功率级放大电路51、51b、两个输入匹配电路54、54b、以及两个偏置电路53、53b。

[0139]

形成于第一部件31的输入开关电路43的至少一部分在俯视时配置于第二部件32的外侧。再布线层内的布线61、61b在俯视时在第二部件32的外侧与输入开关电路43连接。如本变形例那样,也可以在一个第二部件32形成双系统的放大电路。

[0140]

不言而喻上述的各实施例是例示,能够进行不同的实施例所示的结构的部分置换或者组合。对于由多个实施例的同样的结构引起的同样的作用效果,按每个实施例没有依次提及。并且,本发明并不限制于上述的实施例。例如,能够进行各种变更、改进、组合等对于本领域技术人员来说是显而易见的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1