三维存储器及其制备方法与流程

1.本发明涉及半导体器件技术领域,特别涉及一种三维存储器及其制备方法。

背景技术:

2.随着三维存储器的堆叠层数的增加,在去除底部的氧化层-氮化层-氧化层(ono)形成开口的过程中,开口未打开或未完全打开,这样底部的外延结构与沟道层就可能不能连接或者连接的面积较小,从而影响三维存储器的电性能。

技术实现要素:

3.本发明的目的在于提供一种三维存储器及其制备方法,以解决三维存储器的电性能较差技术问题。

4.本发明提供一种三维存储器,包括:堆叠的源极层和堆叠结构以及第一半导体层,所述第一半导体层包括第一部分以及与所述第一部分连接的第二部分,所述堆叠结构包括交替堆叠的栅极层和层间绝缘层;沟道结构,所述沟道结构穿过所述堆叠结构并延伸至所述源极层;所述第一部分位于所述源极层与所述堆叠结构之间,且与所述沟道结构的沟道层连接,所述第二部分设于所述源极层背离所述堆叠结构的一侧,以及贯穿在所述源极层内。

5.其中,所述三维存储器包括依次设置的第一氧化层、氮化层、第二氧化层,所述第一氧化层、所述氮化层以及所述第二氧化层位于所述源极层与所述堆叠结构之间,且所述第一氧化层与所述源极层层叠,所述第二氧化层与所述堆叠结构层叠;所述第一氧化层、所述氮化层以及所述第二氧化层的端面与所述第一部分的端面连接。

6.其中,所述三维存储器还包括连接层,所述连接层连接在所述堆叠结构与所述源极层之间,所述沟道结构贯穿所述连接层,所述第一半导体层的第一部分与所述连接层连接。

7.其中,所述第一部分为空心结构或实心结构;和/或,所述第二部分的贯穿所述源极层的结构为空心结构或实心结构。

8.其中,所述第一部分内设有多个间隔设置的缝隙;和/或,所述第二部分的贯穿所述源极层的结构内设有多个间隔设置的缝隙。

9.其中,所述三维存储器还包括:第一绝缘层,位于所述第一半导体层背离所述源极层的一侧,且所述第一绝缘层填充所述第一部分的空心结构与所述第二部分的空心结构。

10.其中,所述三维存储器还包括:覆盖所述堆叠结构及所述源极层的第二绝缘层;第一触点,穿过所述第二绝缘层与所述堆叠结构的栅极层连接;互连结构,位于所述堆叠结构背离所述源极层的一侧,所述互连结构与所述沟道结构电连接;外围电路,位于所述互连结构背离堆叠结构的一侧,并与所述互连结构电连接;所述外围电路包括:外围衬底、设于所述外围衬底上的外围器件以及覆盖所述外围器件与所述外围衬底的介质层。

11.其中,所述三维存储器还包括:第二触点,穿过所述第二绝缘层伸入在所述源极层

内;第一引出触点,穿过所述第一绝缘层以及穿过所述第一半导体层延伸在所述源极层内,其中,所述第二触点与所述第一引出触点连接;源极触点,穿过所述第一绝缘层以及穿过所述第一半导体层延伸在所述源极层内,并与所述源极层连接;第一桥阶层,位于所述第一绝缘层背离所述第一半导体层的一侧,且连接所述第一引出触点与所述源极触点。

12.其中,所述三维存储器还包括:连接触点,穿过所述第二绝缘层伸入在所述连接层内与所述连接层连接。

13.其中,所述三维存储器还包括:第三触点,穿过所述第二绝缘层伸入在所述源极层内;第二引出触点,穿过所述第一绝缘层以及穿过所述第一半导体层延伸在所述源极层内,其中,所述第三触点与所述第二引出触点分别连接。

14.其中,所述三维存储器还包括:第四触点,穿过所述介质层伸入在所述外围衬底内;第三引出触点,伸入在所述外围衬底内,且与所述第四触点连接。

15.其中,所述源极层为n型掺杂的半导体层,所述第一半导体层为n型掺杂的半导体层。本发明提供一种三维存储器的制备方法,包括:提供堆叠的源极层、牺牲层和堆叠结构,其中,所述牺牲层位于所述源极层和所述堆叠结构之间,所述堆叠结构包括交替堆叠的栅极层和层间绝缘层;形成若干穿过所述堆叠结构以及穿过所述牺牲层且延伸至所述源极层的沟道结构;形成贯穿所述源极层与所述牺牲层的过孔,其中,所述过孔露出所述沟道结构的沟道层;在所述过孔的孔壁与所述源极层背离所述堆叠结构的一侧形成第一半导体层,其中,所述第一半导体层与所述沟道结构的沟道层连接。

16.其中,所述过孔包括第一子孔以及与所述第一子孔连通的第二子孔;所述第一子孔由所述源极层与所述堆叠结构围成;或者,所述第一子孔由所述堆叠结构、所述源极层以及刻蚀后的所述牺牲层围成;所述第二子孔位于所述源极层内。

17.其中,所述牺牲层包括依次设置的第一氧化层、氮化层、第二氧化层,所述第一氧化层、所述氮化层以及所述第二氧化层位于所述源极层与所述堆叠结构之间,且所述第一氧化层与所述源极层层叠堆叠,所述第二氧化层与所述堆叠结构层叠。

18.其中,“提供堆叠的源极层、牺牲层和堆叠结构,其中,所述牺牲层位于所述源极层和所述堆叠结构之间”包括:提供堆叠的源极层、牺牲层、连接层和堆叠结构,其中,所述连接层位于所述牺牲层与所述堆叠结构之间。

19.其中,“形成贯穿所述源极层与所述牺牲层的过孔,其中,所述过孔露出所述沟道结构的沟道层”包括:在所述源极层与所述牺牲层上形成第一初始过孔,其中,所述第一初始过孔露出所述氮化层;选择性刻蚀所述氮化层,以将所述第一初始过孔扩大为第二初始过孔,其中,所述第二初始过孔露出所述沟道结构的存储器膜层;刻蚀所述第二初始过孔露出的所述存储器膜层,以露出所述沟道结构的沟道层。

20.其中,“刻蚀所述第二初始过孔露出的所述存储器膜层”包括:刻蚀所述存储器膜层时,刻蚀所述第一氧化层与所述第二氧化层,以将所述第二初始过孔扩大为所述过孔。

21.其中,在刻蚀所述存储器膜层之后,所述制备方法还包括:刻蚀所述第一氧化层与所述第二氧化层,以将所述第二初始过孔扩大为所述过孔。

22.其中,“刻蚀所述第二氧化层”包括:刻蚀所述第二氧化层,以使得所述过孔露出所述连接层;“在所述过孔的孔壁上形成第一半导体层”包括:在形成所述第一半导体层时,所述第一半导体层与所述连接层连接。

23.其中,在形成所述第一半导体层之后,所述制备方法还包括:在所述第一半导体层背离所述源极层的一侧形成第一绝缘层,且使得所述第一绝缘层填充所述第一半导体层的空心结构。

24.其中,在形成所述堆叠结构之后,所述制备方法还包括:形成覆盖所述堆叠结构、所述牺牲层及所述源极层的第二绝缘层;在所述第二绝缘层上形成穿过所述第二绝缘层的第一触点,其中,所述第一触点与所述堆叠结构的栅极层连接;在所述堆叠结构背离所述源极层的一侧形成互连结构,其中,所述互连结构与所述沟道结构电连接;在所述互连结构背离堆叠结构的一侧形成外围电路,其中,所述外围电路与所述互连结构电连接;所述外围电路包括:外围源极层、设于所述外围源极层上的外围器件以及覆盖所述外围器件与所述外围源极层的介质层。

25.其中,在形成所述外围电路之后,所述制备方法还包括:在所述第二绝缘层上形成伸入在所述源极层内的第二触点;在所述第一绝缘层与所述第一半导体层上形成第一引出触点,其中,所述第一引出触点延伸在所述源极层内,且与所述第二触点连接;以及在所述第一绝缘层与所述第一半导体层上形成源极触点,其中,所述源极触点与所述源极层连接;在所述第一绝缘层背离所述第一半导体层的一侧形成第一桥阶层,其中,所述第一桥阶层连接所述第一引出触点与所述源极触点。

26.其中,“在所述第二绝缘层上形成穿过所述第二绝缘层的第一触点”包括:

27.在形成所述第一触点时,形成连接触点,其中,所述连接触点穿过所述第二绝缘层伸入在所述连接层内与所述连接层连接。

28.其中,所述制备方法还包括:在所述第二绝缘层上形成第三触点,其中,所述第三触点伸入在所述源极层内;在所述第一绝缘层以及穿过所述第一半导体层上形成第二引出触点,其中,所述第二引出触点伸入在所述源极层内,且与所述第三触点连接。

29.其中,所述制备方法还包括:在所述介质层上形成第四触点,其中,所述第四触点伸入在所述外围源极层内;在所述外围源极层上形成第三引出触点,其中,所述第三引出触点与所述第四触点连接。

30.综上所述,通过从源极层背向堆叠结构的一侧设置第一半导体层连接层,且使得第一半导体层的第一部分与沟道结构的沟道层连接,第一半导体层连接层将沟道结构的沟道层连接至源极层,无需在三维存储器内形成将沟道层连接至源极层的外延结构,三维存储器的电性能较好。本技术的第一半导体层的形成方式简单,工艺操作窗口较大,而且不受堆叠结构层数的限制。

附图说明

31.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

32.图1是在衬底上形成第一牺牲氧化层、第一牺牲氮化层、第二牺牲氧化层以及源极层的结构示意图。

33.图2是在源极层上形成第一氧化层、氮化层以及第二氧化层的结构示意图。

34.图3是在第二氧化层上形成连接层的结构示意图。

35.图4是形成连接层上形成堆叠结构,以及在堆叠结构上形成延伸至源极层的沟道结构的结构示意图。

36.图5是形成台阶结构以及形成第二绝缘层的结构示意图。

37.图6是在沟道结构之间形成栅极沟槽的结构示意图。

38.图7是以栅极沟槽为入口去除栅极牺牲层的结构示意图。

39.图8是在对应栅极牺牲层的位置形成栅极层的结构示意图。

40.图9是填充栅极沟槽的结构示意图。

41.图10是形成第一触点、第二触点的结构示意图。

42.图11是形成互连结构的结构示意图。

43.图12是互连结构与外围电路连接的结构示意图。

44.图13是去除衬底、第一牺牲氧化层、第一牺牲氮化层以及第二牺牲氧化层的结构示意图。

45.图14是形成第一初始过孔的结构示意图。

46.图15是形成第二初始过孔的结构示意图。

47.图16是形成过孔的结构示意图。

48.图17是形成第一半导体层的结构示意图。

49.图18是形成第一绝缘层的结构示意图。

50.图19是形成引出孔的结构示意图。

51.图20是形成初始间隔层的结构示意图。

52.图21是形成间隔层的结构示意图。

53.图22是形成引出触点层的结构示意图。

54.图23是形成第一引出触点与第二引出触点的结构示意图。

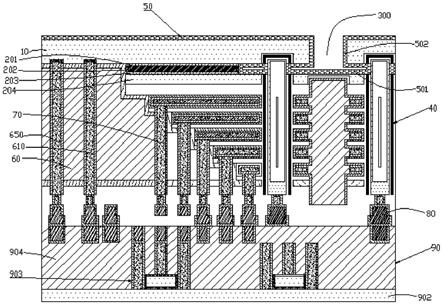

55.图24是本技术的第一种三维存储器的结构示意图。

56.图25是本技术的第二种三维存储器的结构示意图。

57.图26是本技术的第三种三维存储器的结构示意图。

58.图27是本技术的第四种三维存储器的结构示意图。

59.图28是本技术的第五种三维存储器的结构示意图。

60.图29是本技术的第六种三维存储器的结构示意图。

具体实施方式

61.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

62.请参阅图17,本发明提供一种三维存储器,包括:

63.堆叠的源极层10和堆叠结构30以及第一半导体层50,第一半导体层50包括第一部分501以及与第一部分501连接的第二部分502,堆叠结构30包括交替堆叠的栅极层和层间绝缘层。可选地,源极层10为n型掺杂的半导体层,源极层10的材质可以为多晶硅。第一半导

体层50为n型掺杂的半导体层,第一半导体层50的材质可以为多晶硅。

64.沟道结构40,沟道结构40穿过堆叠结构30并延伸至源极层10。可以理解的是,沟道结构40的形成方法为:在堆叠结构30上形成延伸至源极层10的沟道孔;从沟道孔的孔壁到孔中心的方向上,在沟道孔的孔壁上形成存储器膜层与沟道层。存储器膜层包括沿沟道孔的孔壁向孔中心的阻挡绝缘层、电荷捕获层和隧穿绝缘层。阻挡绝缘层和隧穿绝缘层的示例性材料为氧化硅,电荷捕获层的示例性材料为氮化硅,存储器膜层形成了氧化硅-氮化硅-氧化硅(ono)的叠层结构。沟道层的示例性材料为硅(si)。阻挡绝缘层、电荷捕获层以及隧穿绝缘层可以选择其他材料,在此不做限定。

65.第一部分501位于源极层10与堆叠结构30之间,且与沟道结构40的沟道层连接,第二部分502设于源极层10背离堆叠结构30的一侧,以及贯穿在源极层10内。

66.本技术中,通过从源极层10背向堆叠结构30的一侧设置第一半导体层50连接层204,且使得第一半导体层50的第一部分501与沟道结构40的沟道层连接,第一半导体层50连接层204将沟道结构40的沟道层连接至源极层10,无需在三维存储器内形成将沟道层连接至源极层10的外延结构,三维存储器的电性能较好。本技术的第一半导体层50的形成方式简单,工艺操作窗口较大,而且不受堆叠结构30层数的限制。

67.在一个具体的实施例中,第一部分501为空心结构或实心结构。

68.可以理解的是,在形成第一半导体层50之前,源极层10内形成有过孔300;若第一部分501贴合过孔300的孔壁,未完全填充过孔300,第一部分501为空心结构(图24);若第一部分501完全填充过孔300,第一部分501为实心结构(图26)。

69.在一个具体的实施例中,第一部分501的空心结构具体表现为:第一部分501内设有多个缝隙570,多个缝隙570间隔设置(图25);或者,多个缝隙570连通形成一个较大空间(图24)。可以理解的是,第一部分501内设置的缝隙570可以抵抗由于温度变化所引起的热胀冷缩。

70.在一个具体的实施例中,第二部分502的贯穿源极层10的结构为空心结构或实心结构。

71.可以理解的是,若第二部分502的贯穿源极层10的结构贴合在源极层10内的过孔300的孔壁,未完全填充源极层10内的过孔300,第二部分502为空心结构;若第二部分502的贯穿源极层10的结构完全填充源极层10内的过孔300,第二部分502为实心结构。

72.第二部分502的贯穿源极层10的结构为空心结构具体表现为:第二部分502的贯穿源极层10的结构内设有多个缝隙570,多个缝隙570间隔设置,或者多个缝隙570连通形成一个较大空间。可以理解的是,可以理解的是,第二部分502内设置的缝隙570可以抵抗由于温度变化所引起的热胀冷缩。

73.在一个具体的实施例中,三维存储器包括依次设置的第一氧化层201、氮化层202、第二氧化层203,第一氧化层201、氮化层202以及第二氧化层203位于源极层10与堆叠结构30之间,且第一氧化层201与源极层10层叠,第二氧化层203与堆叠结构30层叠;第一氧化层201、氮化层202以及第二氧化层203的端面与第一部分501的端面连接。

74.可以理解的是,过孔300延伸在第一氧化层201、氮化层202、第二氧化层203内,第一氧化层201、氮化层202、第二氧化层203的端面裸露,在连接孔60内形成第一半导体层50时,第一半导体层50的第一部分501连接第一氧化层201、氮化层202、第二氧化层203的端

面。第一氧化层201、氮化层202、第二氧化层203可以支撑第一半导体层50,使得第一半导体层50连接的更加稳固。

75.在一个具体的实施例中,三维存储器还包括连接层204,连接层204连接在堆叠结构30与源极层10之间,沟道结构40贯穿连接层204,第一半导体层50的第一部分501与连接层204连接。可选地,连接层204位于堆叠结构30与第二氧化层203之间。可以理解的是,在形成过孔300时,过孔300使得连接层204的至少部分表面裸露,在过孔300内形成第一半导体层50时,第一半导体层50的第一部分501与连接层204连接。连接层204的设置可以连接导通第一半导体层50与三维存储器的内部结构。

76.在一个具体的实施例中,三维存储器还包括:

77.请参阅图18,第一绝缘层340,位于连接层204第一半导体层50背离源极层10的一侧,且第一绝缘层340填充第一部分501的空心结构与第二部分502的空心结构。可以理解的是,若第一部分501为空心结构,第二部分502为空心结构,则在形成第一绝缘层340时,第一绝缘层340将填充第一部分501的空心结构和第二部分502的空心结构;若第一部分501为实心结构,第二部分502为空心结构,则第一绝缘层340将填充第二部分502的空心结构。

78.在一个具体的实施例中,三维存储器还包括:

79.覆盖堆叠结构30及源极层10的第二绝缘层60;

80.第一触点70,穿过第二绝缘层60与堆叠结构30的栅极层301连接。

81.本技术中,通过设置第一触点70,可以使得栅极层301通过第一触点70与其他结构连接。

82.在一个具体的实施例中,三维存储器还包括:

83.互连结构80,位于堆叠结构30背离源极层10的一侧,互连结构80与沟道结构40电连接。可以理解的是,互连结构80也形成在第二绝缘层60内。互连结构80包括依次连接的焊盘、导电通道以及布线。焊盘与沟道结构40连接,布线与三维存储器的其他结构电连接,如与下文的外围电路90的连接。

84.在一个具体的实施例中,三维存储器还包括:

85.外围电路90,位于互连结构80背离堆叠结构30的一侧,并与互连结构80电连接;

86.外围电路90包括:外围衬底902、设于外围衬底902上的外围器件903以及覆盖外围器件903的介质层904。本技术中,外围电路90通过互连结构80为沟道结构40供电。

87.如下将介绍三维存储器的具体四种结构。

88.第一种:

89.请参阅图24-图26,三维存储器还包括:

90.第二触点610,穿过第二绝缘层60伸入在源极层10内;第二触点610的材质可以为银(ag)。

91.第一引出触点620,穿过第一绝缘层340以及穿过第一半导体层50延伸在源极层10内,其中,第二触点610与第一引出触点620连接;第一引出触点620的材质可以为银(ag)。

92.源极触点630,穿过第一绝缘层以及穿过第一半导体层50延伸在源极层10内,并与源极层10连接;源极触点630的材质可以为银(ag)。

93.第一桥接层640,位于第一绝缘层340背离第一半导体层50的一侧,且连接第一引出触点620与源极触点630。第一桥接层640的材质可以为银(ag)。

94.可以理解的是,源极触点630、第一桥接层640、第一引出触点620以及第二触点610形成连接通路。第一桥接层640主要用于将给到源极层10的电位通过第一桥接层640、第一引出触点620和第二触点610以及与源极层10搭接的源极触点630传递到源级层10。

95.本方式中,三维存储器还包括:

96.第三触点650,穿过第二绝缘层60伸入在源极层10内;

97.第二引出触点660,穿过第一绝缘层以及穿过第一半导体层50延伸在源极层10内,其中,第三触点650与第二引出触点660分别连接。

98.本方式中,还包括第一引出层130,位于第一绝缘层340背离第一半导体层50的一侧,且通过第二引出触点660与第三触点650连接。

99.如此,第一引出层130可以将三维存储器引出,第一桥接层640可以将三维存储器的内部结构连通。

100.第二种:

101.请参阅图27,三维存储器还包括:

102.连接触点710,穿过第二绝缘层60伸入在连接层204内与连接层204连接。连接触点710的材质可以为银(ag)。

103.可以理解的是,第一半导体层50、连接层204、连接触点710形成连接通路。

104.本方式中,三维存储器还包括:

105.第三触点650,穿过第二绝缘层60伸入在源极层10内;

106.第二引出触点660,穿过第一绝缘层以及穿过第一半导体层50延伸在源极层10内,其中,第三触点650与第二引出触点660分别连接。

107.本方式中,还包括第一引出层130,位于第一绝缘层340背离第一半导体层50的一侧,且通过第二引出触点660与第三触点650连接。

108.如此,第一引出层130可以将三维存储器引出,连接触点710可以将三维存储器的内部结构连通。

109.第三种:与第一种不同的是:

110.请参阅图28,本方式的三维存储器包括:

111.第四触点670,穿过介质层904伸入在外围衬底902内;

112.第三引出触点680,伸入在外围衬底902内,且与第四触点670连接。

113.还包括第二引出层690,位于外围衬底902背离外围器件903的一侧,且通过第三引出触点680与第四触点670连接。

114.如此,第二引出层690可以将三维存储器引出,第一桥接层640可以将三维存储器的内部结构连通。

115.第四种:与第二种结构不同的是:

116.请参阅图29,本方式的三维存储器包括:

117.第四触点670,穿过介质层904伸入在外围衬底902内;

118.第三引出触点680,伸入在外围衬底902内,且与第四触点670连接。

119.还包括第二引出层690,位于外围衬底902背离外围器件903的一侧,且通过第三引出触点680与第四触点670连接。

120.如此,第二引出层690可以将三维存储器引出,连接触点710可以将三维存储器的

内部结构连通。

121.除了上述的三维存储器,本技术还提供一种三维存储器的制备方法。

122.三维存储器的制备方法包括:

123.s1,请参阅图13,提供堆叠的源极层10、牺牲层20和堆叠结构30,其中,牺牲层20位于源极层10和堆叠结构30之间,堆叠结构30包括交替堆叠的栅极层和层间绝缘层;

124.s2,形成若干穿过堆叠结构30以及穿过牺牲层20且延伸至源极层10的沟道结构40;

125.s3,请参阅图16,形成贯穿源极层10与牺牲层20的过孔300,其中,过孔300露出沟道结构40的沟道层;

126.s4,请参阅图17,在过孔300的孔壁与源极层10背离堆叠结构30的一侧形成第一半导体层50,其中,第一半导体层50与沟道结构40的沟道层连接。

127.本技术中,通过从源极层10背向堆叠结构30的一侧形成过孔300,在过孔300的孔壁上形成第一半导体层50,且使得第一半导体层50与沟道结构40的沟道层连接,第一半导体层50将沟道结构40的沟道层连接至源极层10,无需在三维存储器内形成将沟道层连接至源极层10的外延结构,三维存储器的电性能较好。本技术的第一半导体层50的形成方式简单,工艺操作窗口较大,而且不受堆叠结构30层数的限制。

128.在一个具体的实施例中,过孔300包括第一子孔以及与第一子孔连通的第二子孔;

129.第一子孔由源极层10与堆叠结构30围成;或者,第一子孔由堆叠结构30、源极层10以及刻蚀后的牺牲层20围成;

130.第二子孔位于源极层10内。

131.可以理解的是,在形成过孔300的过程中,若是牺牲层20被完全刻蚀掉,则第一子孔由源极层10与堆叠结构30围成;若是牺牲层20被部分刻蚀掉,第一子孔由堆叠结构30、源极层10以及刻蚀后的牺牲层20围成。

132.本技术中,通过牺牲层20的设置,方便于在去除牺牲层20时,形成过孔300,以方便于在过孔300内形成第一半导体层50。

133.在一个具体的实施例中,牺牲层20包括依次设置的第一氧化层201、氮化层202、第二氧化层203,第一氧化层201、氮化层202以及第二氧化层203位于源极层10与堆叠结构30之间,且第一氧化层201与源极层10层叠,第二氧化层203与堆叠结构30层叠。可以理解的是,第一氧化层201与第二氧化层203的示例性材料为氧化硅,氮化层202的示例性材料为氮化硅。第一氧化层201、氮化层202、第二氧化层203形成了氧化硅-氮化硅-氧化硅(ono)的叠层结构。可以理解的是,过孔300可以贯穿第一氧化层201、氮化层202、第二氧化层203,第一氧化层201、氮化层202、第二氧化层203的端面裸露,在过孔300内形成第一半导体层50时,第一半导体层50连接第一氧化层201、氮化层202、第二氧化层203的端面。第一氧化层201、氮化层202以及第二氧化层203可以支撑第一半导体层50,使得第一半导体层50连接的更加稳固。

134.本技术中,通过设置牺牲层20包括依次设置的第一氧化层201、氮化层202、第二氧化层203,牺牲层20方便形成,也方便刻蚀去除。

135.在一个具体的实施例中,“提供堆叠的源极层10、牺牲层20和堆叠结构30,其中,牺牲层20位于源极层10和堆叠结构30之间”包括:

136.提供堆叠的源极层10、牺牲层20、连接层204和堆叠结构30,其中,连接层204位于牺牲层20与堆叠结构30之间。可选地,连接层204位于堆叠结构30与第二氧化层203之间。可以理解的是,在形成过孔300时,过孔300使得连接层204的至少部分表面裸露,在过孔300内形成第一半导体层50时,第一半导体层50的第一部分501与连接层204连接。连接层204的设置可以导通连接第一半导体层50与三维存储器的内部结构。

137.请参阅图14,在一个具体的实施例中,“形成贯穿源极层10与牺牲层20的过孔300,其中,过孔300露出沟道结构40的沟道层”包括:

138.请参阅图15,在源极层10与牺牲层20上形成第一初始过孔440,其中,第一初始过孔440露出氮化层202;

139.选择性刻蚀氮化层202,以将第一初始过孔440扩大为第二初始过孔450,其中,第二初始过孔450露出沟道结构40的存储器膜层;

140.刻蚀第二初始过孔300露出的存储器膜层,以露出沟道结构40的沟道层。可以理解的是,源极层10、第一氧化层201、氮化层202的材质不同,刻蚀比不同。

141.本技术中,首先形成第一初始过孔440,然后将第一初始过孔440扩大为第二初始过孔450,最后再刻蚀第二初始过孔450露出的存储器膜层,可以根据刻蚀的需求选择相应的刻蚀剂,以提高刻蚀效率。

142.在一个具体的实施例中,“刻蚀第二初始过孔450露出的存储器膜层”包括:

143.刻蚀存储器膜层时,刻蚀第一氧化层201与第二氧化层203,以将第二初始过孔450扩大为过孔300。

144.可以理解的是,第一氧化层201、第二氧化层203与存储器膜层的刻蚀比相近,本技术在刻蚀存储器膜层时,同步刻蚀第一氧化层201、第二氧化层203,如此第二初始过孔450扩大形成的过孔300的体积较大,第一半导体层50的形成面积较大,第一半导体层50与沟道层的连接面积较大,提高了三维存储器的电性能。

145.在一个具体的实施例中,在刻蚀存储器膜层之后,制备方法还包括:

146.刻蚀第一氧化层201与第二氧化层203,以将第二初始过孔450扩大为过孔300。

147.可以理解的是,第一氧化层201、第二氧化层203与存储器膜层的刻蚀比不同,本技术在刻蚀存储器膜层时,不刻蚀第一氧化层201、第二氧化层203,在完成刻蚀存储器膜层后,刻蚀第一氧化层201、第二氧化层203,如此,存储器膜层与第一氧化层201以及第二氧化层203的刻蚀过程彼此不影响,可以较好地控制过孔300的尺寸大小,可以按需设置第一半导体层50。

148.请参阅图16,在一个具体的实施例中,“刻蚀第二氧化层203”包括:

149.刻蚀第二氧化层203,以使得过孔300露出连接层204;

[0150]“在过孔300的孔壁上形成第一半导体层50”包括:

[0151]

在形成第一半导体层50时,第一半导体层50与连接层204连接。

[0152]

可以理解的是,在第二氧化层203刻蚀的过程中,需要将第二氧化层203朝向连接层204的结构刻蚀去除,以露出连接层204,方便于后续的连接层204与第一半导体层50连接。

[0153]

可以理解的是,堆叠的源极层10、牺牲层20、连接层204和堆叠结构30的形成方法包括:

[0154]

提供衬底280;

[0155]

请参阅图1,在衬底280上依次形成第一牺牲氧化层290、第一牺牲氮化层310、第二牺牲氧化层320以及源极层10;

[0156]

请参阅图2,在源极层10上形成第一氧化层201、氮化层202以及第二氧化层203;

[0157]

请参阅图3,在第二氧化层202上形成连接层204;

[0158]

请参阅图4,在连接层204上形成堆叠结构30,以及在堆叠结构30上形成延伸至源极层10的沟道结构40;堆叠结构30包括交替堆叠的层间绝缘层与栅极牺牲层20;

[0159]

请参阅图5,刻蚀堆叠结构30的端部以形成台阶结构,并在刻蚀后的堆叠结构30、牺牲层20与源极层10上形成第二绝缘层60;

[0160]

请参阅图6,在沟道结构40之间形成栅极沟槽330;

[0161]

请参阅图7,以栅极沟槽330为入口去除栅极牺牲层20;

[0162]

请参阅图8,在对应栅极牺牲层20的位置形成栅极层301;

[0163]

请参阅图9,填充栅极沟槽330;

[0164]

请参阅图10,在第二绝缘层60上形成穿过第二绝缘层60的第一触点70,第一触点70与栅极层301连接,以及在第二绝缘层60上形成伸入在源极层10内的第二触点610;

[0165]

请参阅图11,在堆叠结构30背离源极层10的一侧形成互连结构80,其中,互连结构80与沟道结构40电连接。

[0166]

请参阅图12,在互连结构80背离堆叠结构30的一侧形成外围电路90,其中,外围电路90与互连结构80电连接;外围电路90包括:外围衬底902、设于外围衬底902上的外围器件903以及覆盖外围器件903与外围衬底902的介质层904。

[0167]

请参阅图13,去除衬底280、第一牺牲氧化层290、第一牺牲氮化层310以及第二牺牲氧化层320。

[0168]

请参阅图18,在一个具体的实施例中,在形成第一半导体层50之后,制备方法还包括:

[0169]

在第一半导体层50背离源极层10的一侧形成第一绝缘层340,且使得第一绝缘层340填充第一半导体层50的空心结构。可以理解的是,第一绝缘层340填充第一半导体层50的空心结构,可以使得三维存储器结构平坦。

[0170]

本技术中,通过设置第一触点770,可以使得栅极层301通过第一触点70与其他结构连接。外围电路90通过互连结构80为沟道结构40供电。

[0171]

如下,将介绍三维存储器的具体形成方法。

[0172]

第一种:

[0173]

在一个具体的实施例中,在形成外围电路90之后,制备方法还包括:

[0174]

在第一绝缘层340与第一半导体层50上形成第一引出触点620,其中,第一引出触点620延伸在源极层10内,且与第二触点610连接;以及

[0175]

在第一绝缘层340与第一半导体层50上形成源极触点630,其中,源极触点630与源极层10连接;

[0176]

在第一绝缘层340背离第一半导体层50的一侧形成第一桥接层640,其中,第一桥接层640连接第一引出触点620与源极触点630。

[0177]

可以理解的是,源极触点630、第一桥接层640、第一引出触点620以及第二触点610

形成连接通路。第一桥接层640主要用于将给到源级层的电位通过第一桥接层640、第一引出触点620和第二触点610以及与源级搭接的源极触点630传递到源级层10。

[0178]

本方式中,三维存储器的制备方法还包括:

[0179]

在第二绝缘层60上形成第三触点650,其中,第三触点650伸入在源极层10内;

[0180]

在第一绝缘层340以及穿过第一半导体层50上形成第二引出触点660,其中,第二引出触点660伸入在源极层10内,且与第三触点650连接。

[0181]

本方式中,制备方法还包括:在第一绝缘层340340背离第一半导体层50的一侧第一引出层130,第一引出层130通过第二引出触点660与第三触点650连接。

[0182]

如此,第一引出层130可以将三维存储器引出,第一桥接层640可以将三维存储器的内部结构连通。

[0183]

第二种:

[0184]

在三维存储器的制备方法中,

[0185]“在第二绝缘层60上形成穿过第二绝缘层60的第一触点70”包括:

[0186]

在形成第一触点70时,形成连接触点710,其中,连接触点710穿过第二绝缘层60伸入在连接层204内与连接层204连接。

[0187]

本方式中,三维存储器的制备方法还包括:

[0188]

在第二绝缘层60上形成第三触点650,其中,第三触点650伸入在源极层10内;

[0189]

在第一绝缘层340以及穿过第一半导体层50上形成第二引出触点660,其中,第二引出触点660伸入在源极层10内,且与第三触点650连接。

[0190]

本方式中,制备方法还包括:在第一绝缘层340340背离第一半导体层50的一侧第一引出层130,第一引出层130通过第二引出触点660与第三触点650连接。

[0191]

如此,第一引出层130可以将三维存储器引出,连接触点710可以将三维存储器的内部结构连通。

[0192]

第三种:与第一种不同的是:

[0193]

本方式的三维存储器的制备方法包括:

[0194]

在介质层904上形成第四触点670,其中,第四触点670伸入在外围衬底902内;

[0195]

在外围衬底902上形成第三引出触点680,其中,第三引出触点680与第四触点670连接。

[0196]

本方式中,三维存储器的制备方法还包括:

[0197]

在外围衬底背离外围器件的一侧形成第二引出层690,第二引出层690通过第三引出触点680与第四触点670连接。

[0198]

如此,第二引出层690可以将三维存储器引出,第一桥接层640可以将三维存储器的内部结构连通。

[0199]

第四种:与第二种制备方法不同的是:

[0200]

本方式的三维存储器的制备方法包括:

[0201]

在介质层904上形成第四触点670,其中,第四触点670伸入在外围衬底902内;

[0202]

在外围衬底902上形成第三引出触点680,其中,第三引出触点680与第四触点670连接。

[0203]

本方式中,三维存储器的制备方法还包括:

[0204]

在外围衬底902背离外围器件903的一侧形成第二引出层690,第二引出层690通过第三引出触点680与第四触点670连接。

[0205]

如此,第二引出层690可以将三维存储器引出,连接触点710可以将三维存储器的内部结构连通。

[0206]

可以理解的是,在形成上述引出触点(第一引出触点620、第二引出触点660、第三引出触点680)之前,先在形成引出触点的引出孔510的侧壁上形成间隔层540,如可以在第一绝缘层340、第一半导体层50以及源极层10上形成引出孔510(图19),引出孔510露出对应的触点,在引出孔510与第一绝缘层340上形成初始间隔层530(图20);刻蚀初始间隔层530以形成引出孔510侧壁上的间隔层540(图21)。

[0207]

可以理解的是,在形成引出触点时,可以在第一绝缘层340上形成整层的引出触点层520(图22),引出触点层520与引出触点连接,然后去除第一绝缘层340上的引出触点层520(图23)。

[0208]

以上所揭露的仅为本发明较佳实施例而已,当然不能以此来限定本发明之权利范围,本领域普通技术人员可以理解实现上述实施例的全部或部分流程,并依本发明权利要求所作的等同变化,仍属于发明所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1