一种封装装片结构设计方法与流程

1.本发明属于半导体封装技术领域,具体是涉及一种封装装片结构设计方法。

背景技术:

2.目前半导体产品的发展趋势就是小型化,密集化,在尽可能小的区域内安装尽可能多的芯片,减少空间占用,提高空间利用率。目前ssop24封装芯片尺寸较大,并且芯片功能较少,不能满足复杂的电路控制要求。

技术实现要素:

3.本发明的目的在于针对上述问题,提供一种封装装片结构设计方法,采用两层堆叠封装方式,且第二层平封两颗芯片,精简了封装面积,并能满足复杂的电路控制要求。

4.本发明的技术方案是这样实现的。

5.一种封装装片结构设计方法,其特征在于,包括以下步骤:(1)在框架基材上采用ssop24框架正常装片,使用装片胶粘接下层芯片,形成芯片叠装方式的第一层;(2)在下层芯片上采用daf进行装片,分别使用装片胶粘接两颗上层芯片,形成芯片叠装方式的第二层,两颗上层芯片属于同一层,均不超出下层芯片的芯片外围且留有芯片间的焊线空间;(3)两颗上层芯片采用一次性贴片,贴片后烘烤;(4)使用焊线将基材焊盘与下层芯片焊接,然后两颗上层芯片与下层芯片采用bsob线弧焊接方式,焊接bsob统一使用下层芯片作bsob焊线点的方式;(5)塑封,完成整个产品封装。

6.进一步地,步骤(1)中下层芯片的装片参数为点胶压力30-50n,吸片压力70-90n,贴片压力70-90n,吸片延时60-90ms,挤压延时20-40ms,贴片延时30-50 ms。

7.进一步地,所述步骤(1)中下层芯片安装斜度小于8um。

8.进一步地,所述步骤(2)中两颗上层芯片的装片参数为吸片压力50-60n,贴片压力50-60n,吸片延时20-40ms,贴片延时15-30ms。

9.进一步地,所述步骤(2)中两颗上层芯片的厚度不同,以便兼容更多组合方式。

10.进一步地,所述步骤(4)中线弧的控制以芯片表面为基准,管控范围为100-250um,以防漏丝。

11.进一步地,步骤(4)替换为基材焊盘与下层芯片之间、下层芯片与两颗上层芯片之间均采用bsob连接,且为连续焊线,焊线顺序为两颗上层芯片

→

下层芯片

→

基材焊盘。

12.进一步地,所述步骤(1)中基岛尺寸95*140mil。

13.本发明的有益效果是:(1)本发明适用于ssop24封装,在第二层平封两颗芯片,带来了更多组合的可能,平封芯片的尺寸、厚度和贴片位置都可以进行微调,在原有ssop24基础上再次精简了封装面积,拥有更高的性价比。(2)本发明方法封装结构因为第二层超两颗

芯片,焊线连接方式可以实现更为复杂的电路连接,不仅线长变短,线弧更为稳定;在复杂的电路控制中也可以配合芯片设计制造出更为精巧的控制。(3)鉴于传统ssop24广泛应用于蓝牙耳机、液晶显示控制等智能电子设备,本发明方法形成的ssop24封装可以在同厚度基础上实现更加多元化的控制,同时组合完成更为复杂的功能,也可作为mcu进行独立控制,运用于智能开关、控制器及驱动器等场景。

附图说明

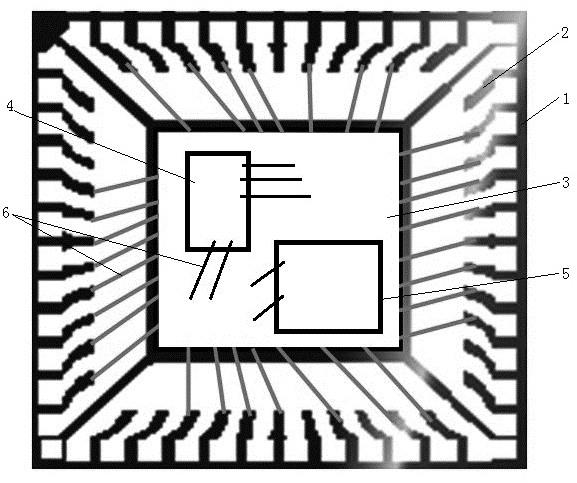

14.图1为本发明装片结构的俯视图。

15.在图中,1、框架基材,2、基材焊盘,3、下层芯片,4、上层芯片ⅰ,5、上层芯片ⅱ,6、焊线。

具体实施方式

16.下面通过实施例以及说明书附图对本发明的技术方案做进一步地详细说明。

17.实施例1:如图1所示,本发明的一种封装装片结构设计方法,包括以下步骤:(1)在框架基材1上采用ssop24框架正常装片,使用装片胶粘接下层芯片3,基岛尺寸为80*80mil,形成芯片叠装方式的第一层,下层芯片3的装片参数为点胶压力 30n,吸片压力70n,贴片压力70n,吸片延时60ms,挤压延时20ms,贴片延时30ms。下层芯片3安装斜度小于8um。

18.(2)在下层芯片3上采用daf进行装片,分别使用装片胶粘接两颗厚度相同的上层芯片:上层芯片ⅰ4、上层芯片ⅱ5,形成芯片叠装方式的第二层,上层芯片ⅰ4、上层芯片ⅱ5属于同一层,均不超出下层芯片3的芯片外围且留有芯片间的焊线空间;上层芯片ⅰ4、上层芯片ⅱ5的装片参数为吸片压力50n,贴片压力50n,吸片延时20ms,贴片延时15ms。

19.(3)上层芯片ⅰ4、上层芯片ⅱ5采用一次性贴片,贴片后烘烤;(4)使用焊线6将基材焊盘2与下层芯片3焊接,然后两颗上层芯片(上层芯片ⅰ4、上层芯片ⅱ5)与下层芯片3采用bsob线弧焊接方式,焊接bsob统一使用下层芯片3作bsob焊线点的方式;线弧的控制以芯片表面为基准,管控范围为100-250um,以防漏丝。

20.(5) 塑封,完成整个产品封装。

21.实施例2:如图1所示,本发明的另一种封装装片结构设计方法,包括以下步骤:(1)在框架基材1上采用ssop24框架正常装片,使用装片胶粘接下层芯片3,基岛尺寸95*140mil,形成芯片叠装方式的第一层,下层芯片3的装片参数为点胶压力50n,吸片压力90n,贴片压力90 n,吸片延时90ms,挤压延时40ms,贴片延时50ms。下层芯片3安装斜度小于8um。

22.(2)在下层芯片3上采用daf进行装片,分别使用装片胶粘接两颗厚度不同的上层芯片:上层芯片ⅰ4、上层芯片ⅱ5,形成芯片叠装方式的第二层,上层芯片ⅰ4、上层芯片ⅱ5属于同一层,均不超出下层芯片3的芯片外围且留有芯片间的焊线空间;上层芯片ⅰ4、上层芯片ⅱ5的装片参数为吸片压力60n,贴片压力60n,吸片延时40ms,贴片延时30 ms。

23.(3)上层芯片ⅰ4、上层芯片ⅱ5采用一次性贴片,贴片后烘烤;(4) 基材焊盘2与下层芯片3之间、下层芯片3与上层芯片ⅰ4、上层芯片ⅱ5之间均采用bsob连接,且为连续焊线,焊线顺序为上层芯片ⅰ4、上层芯片ⅱ5

→

下层芯片3

→

基材焊

盘2;线弧的控制以芯片表面为基准,管控范围为100-250um,以防漏丝。

24.(5) 塑封,完成整个产品封装。

25.以上所述是本发明的优选实施例,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

技术特征:

1.一种封装装片结构设计方法,其特征在于,包括以下步骤:(1)在框架基材上采用ssop24框架正常装片,使用装片胶粘接下层芯片,形成芯片叠装方式的第一层;(2)在下层芯片上采用daf进行装片,分别使用装片胶粘接两颗上层芯片,形成芯片叠装方式的第二层,两颗上层芯片属于同一层,均不超出下层芯片的芯片外围且留有芯片间的焊线空间;(3)两颗上层芯片采用一次性贴片,贴片后烘烤;(4)使用焊线将基材焊盘与下层芯片焊接,然后两颗上层芯片与下层芯片采用bsob线弧焊接方式,焊接bsob统一使用下层芯片作bsob焊线点的方式;(5)塑封,完成整个产品封装。2. 根据权利要求1所述的封装装片结构设计方法,其特征在于:步骤(1)中下层芯片的装片参数为点胶压力30-50n,吸片压力70-90n,贴片压力70-90 n,吸片延时60-90ms,挤压延时20-40ms,贴片延时30-50ms。3.根据权利要求1所述的封装装片结构设计方法,其特征在于:所述步骤(1)中下层芯片安装斜度小于8um。4.根据权利要求1所述的封装装片结构设计方法,其特征在于:所述步骤(2)中两颗上层芯片的装片参数为吸片压力50-60n,贴片压力50-60n,吸片延时20-40ms,贴片延时15-30ms。5.根据权利要求1所述的封装装片结构设计方法,其特征在于:所述步骤(2)中两颗上层芯片的厚度不同,以便兼容更多组合方式。6.根据权利要求1所述的封装装片结构设计方法,其特征在于:所述步骤(4)中线弧的控制以芯片表面为基准,管控范围为100-250um。7.根据权利要求1所述的封装装片结构设计方法,其特征在于:步骤(4)替换为基材焊盘与下层芯片之间、下层芯片与两颗上层芯片之间均采用bsob连接,且为连续焊线,焊线顺序为两颗上层芯片

→

下层芯片

→

基材焊盘。8.根据权利要求1所述的封装装片结构设计方法,其特征在于:所述步骤(1)中基岛尺寸95*140mil。

技术总结

本发明公开了一种封装装片结构设计方法,包括以下步骤:(1)在框架基材上采用SSOP24框架正常装片,使用装片胶粘接下层芯片,形成芯片叠装方式的第一层;(2)在下层芯片上采用DAF进行装片,分别使用装片胶粘接两颗上层芯片,形成芯片叠装方式的第二层;(3)两颗上层芯片采用一次性贴片,贴片后烘烤;(4)使用焊线将基材焊盘与下层芯片焊接,然后两颗上层芯片与下层芯片采用BSOB线弧焊接方式;(5)塑封,完成整个产品封装。本发明适用于SSOP24封装,在第二层平封两颗芯片,带来了更多组合的可能,平封芯片的尺寸、厚度和贴片位置都可以进行微调,在原有SSOP24基础上再次精简了封装面积,拥有更高的性价比。更高的性价比。更高的性价比。

技术研发人员:艾育林 盛天金

受保护的技术使用者:江西万年芯微电子有限公司

技术研发日:2021.12.30

技术公布日:2022/4/29

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1