半导体器件及引线框架的制作方法

1.本技术涉及半导封装领域,特别涉及一种半导体器件及用于构建所述半导体器件的引线框架。

背景技术:

2.封装产品通常是将芯片贴装于引线框架上,以焊线导电连接芯片与引线框架,最后以封装材料封装而获得。

3.在焊线图设计中,经常会遇到地线位置不足的情况,导致基岛需要额外镀银区。或者,会发生焊线位置尴尬的情况,如果不在连筋上焊接焊线,则会发生焊线交叉、超长焊线等问题而导致无法进行焊线作业,从而使得实际工艺中不得不在连筋上进行焊线的情况。

4.然而,通常在框架制作中,连筋会产生压痕、不平整等问题,使得发生连筋上焊线时会造成质量问题。

5.此外,本领域技术人员知晓的,连筋在与基岛连接部分需要做相应的向下冲压处理。因此,当不得不在连筋上进行焊线时,除了连筋表面的压痕及不平整等问题之外,还会发生当焊线必须焊接在连筋向下冲压的位置的情况。在这种情况中,由于焊线的焊点位置十分低,容易导致线弧及线长均不理想,同时也由于基岛是封装体中最容易发生分层的位置,容易因为基岛面与封装材料的分层而导致线脱的问题。

6.因此,有必要提供一种新的引线框架,以克服上述缺陷。

技术实现要素:

7.本技术的目的在于提供一种引线框架和利用该引线框架的半导体器件,通过所述连筋的分支部分,从而解决焊线在连筋时会产生的质量问题。

8.为了达到上述目的,根据本技术的一方面,提供一种半导体器件,包括至少一半导体芯片,贴附至一基岛在一第一平面内的表面;其中,一连筋连接至所述基岛,并具有倾斜地连接至所述基岛的一第一部分;所述连筋具有一第二部分,所述第二部分具有一在一第二平面内的表面;所述第二平面平行于所述第一平面,且与所述第一平面属于不同平面;所述连筋具有一从所述第二部分分出的分支部分,所述分支部分在所述第二平面内具有一用于接收一连接所述半导体芯片的引线的表面;并且,所述分支部分具有一与所述基岛的第一边缘相距一第一距离的边缘。

9.在一些实施例中,所述半导体器件还包括复数个引线指,每一引线指具有一在所述第二平面内的表面,每一引线指的该表面用于接收一连接所述半导体芯片的引线,并且,每一引线指具有一与所述基岛的第一边缘相距所述第一距离的边缘。

10.在一些实施例中,所述半导体芯片具有一靠近所述第二平面的顶面。

11.在一些实施例中,所述半导体器件还包括一引线,所述引线连接所述半导体芯片与所述连筋的所述分支部分。

12.在一些实施例中,所述半导体器件还包括一引线,所述引线连接所述半导体芯片

与所述引线指。

13.在一些实施例中,所述半导体器件还包括一第二连筋,所述第二连筋在所述基岛的相对侧处连接至所述基岛。

14.在一些实施例中,所述第二连筋具有一从所述第二连筋分出的分支部分,该分支部分具有一在所述第二平面内的表面以接收一连接所述半导体芯片的引线,并且,所述第二连筋的该分支部分具有一与所述基岛的第二边缘相距一第二距离的边缘。

15.在一些实施例中,所述半导体器件还包括在所述基岛的四个角处连接到所述基岛的一第二连筋、一第三连筋和一第四连筋。

16.在一些实施例中,所述第二连筋、第三连筋和第四连筋均具有从相应的连筋分出的分支部分,该些分支部分均具有一在所述第二平面内的表面以接收一连接所述半导体芯片的引线。

17.在一些实施例中,所述半导体器件还包括一与所述分支部分相邻的引线指,该引线指与相邻的分支部分具有面向所述基岛的一边缘的共线边缘。

18.根据本技术的另一方面,提供一种引线框架,用于一半导体器件;所述引线框架包括:至少一基岛,具有在一第一平面内的表面,以接收一半导体芯片;一连筋连接至所述基岛,并具有倾斜地连接至所述基岛的一第一部分;所述连筋具有一第二部分,所述第二部分具有一在一第二平面内的表面;所述第二平面平行于所述第一平面,且与所述第一平面属于不同平面;以及,复数个引线指,与所述连筋相邻;其中,所述连筋具有一从所述第二部分分出的分支部分,所述分支部分在所述第二平面内具有一用于接收一连接所述半导体芯片的引线的表面;并且,所述分支部分未直接连接至相邻的引线指。

19.在一些实施例中,所述分支部分具有一与所述基岛的第一边缘相距一第一距离的边缘。

20.在一些实施例中,每一引线指具有一在所述第二平面内的表面,每一引线指的该表面用于接收一连接所述半导体芯片的引线,并且,每一引线指具有一与所述基岛的第一边缘相距所述第一距离的边缘。

21.在一些实施例中,所述半导体芯片具有一靠近所述第二平面的顶面。

22.在一些实施例中,所述半导体器件还包括一第二连筋,所述第二连筋在所述基岛的相对侧处连接至所述基岛。

23.在一些实施例中,所述第二连筋具有一从所述第二连筋分出的分支部分,该分支部分具有一在所述第二平面内的表面以接收一连接所述半导体芯片的引线,并且,所述第二连筋的分支部分未直接连接至相邻的引线指。

24.在一些实施例中,所述第二连筋的分支部分具有一与所述基岛的第二边缘相距一第二距离的边缘。

25.在一些实施例中,所述半导体器件还包括在所述基岛的四个角处连接到所述基岛的一第二连筋、一第三连筋和一第四连筋。

26.在一些实施例中,所述第二连筋、第三连筋和第四连筋均具有从相应的连筋分出的分支部分,该些分支部分均具有一在所述第二平面内的表面以接收一连接所述半导体芯片的引线;并且,所述第二连筋的分支部分、所述第三连筋的分支部分、所述第四连筋的分支部分均未直接连接至相邻的引线指。

27.在一些实施例中,所述第二连筋的分支部分、所述第三连筋的分支部分、所述第四连筋的分支部分分别具有一与所述基岛的第二边缘相距一第二距离的边缘。

28.在一些实施例中,所述引线指与相邻的所述分支部分具有面向所述基岛的一边缘的共线边缘。

29.在本技术中,所述连筋(和/或所述第二连筋、第三连筋及第四连筋)通过从第二部分分出所述分支部分,以在连筋中(和/或所述第二连筋、第三连筋及第四连筋)区分出用于焊接引线的区域,而所述连筋(和/或所述第二连筋、第三连筋及第四连筋)的其他所述第二部分以及所述倾斜地连接至所述基岛的第一部分主要充当常规连筋所起到的连接基岛的作用。因而,在焊接引线工艺中,在对引线指进行常规焊线前滚平处理时,由于所述连筋(和/或所述第二连筋、第三连筋及第四连筋)的所述第二部分的表面、所述分支部分的表面,以及所述引线指的表面均处于同一平面内(第二平面),使得所述连筋(和/或所述第二连筋、第三连筋及第四连筋)的所述第二部分及所述分支部分也同样受到滚平处理,以具备能够焊接引线的表面质量。由此,解决了现有半导体器件及包含其中的引线框架中,因连筋的压痕和/或不平整等问题,使得在连筋上焊接引线时会造成的质量问题。

30.此外,由于所述连筋(和/或所述第二连筋、第三连筋及第四连筋)的所述第二部分的表面处于与其他引线指的表面处于同一平面内,因此也避免了引线的焊点位置低的情况,从而解决了线弧及线长均不理想及因基岛面与封装材料的易分层而导致的易线脱问题。

附图说明

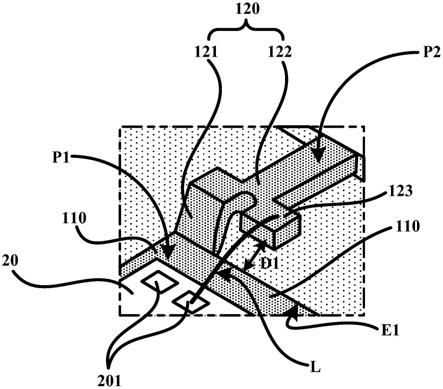

31.图1a是根据本技术一实施例的半导体器件1的结构示意图;

32.图1b是图1中1b区域的局部放大图;

33.图1c是集成到图1a所示半导体器件1中的半导体芯片、基岛、连筋、引线指及引线的俯视图;

34.图2a是根据本技术另一实施例的半导体器件2的结构示意图;

35.图2b是集成到图2a所示半导体器件2中的半导体芯片、基岛、连筋、引线指及引线的俯视图;

36.图3a是根据本技术再一实施例的半导体器件3的结构示意图;

37.图3b是集成到图3a所示半导体器件3中的半导体芯片、基岛、连筋、第二连筋、引线指及引线的俯视图;

38.图4a是根据本技术再一实施例的半导体器件4的结构示意图;

39.图4b是集成到图4a所示半导体器件4中的半导体芯片、基岛、连筋、第二连筋、第三连筋、第四连筋、引线指及引线的俯视图;

40.图4c是图4a所示半导体器件4中连筋、第二连筋、第三连筋及第四连筋的不同设置位置的俯视图;

41.图5a是根据本技术再一实施例的半导体器件5的结构示意图;

42.图5b是图5a所示半导体器件5中连筋不同设置位置的俯视图;

43.图6a是根据本技术再一实施例的半导体器件6的结构示意图;

44.图6b是集成到图6a所示半导体器件6中的半导体芯片、基岛、连筋、第二连筋、引线

指及引线的俯视图;

45.图7a是根据本技术一实施例的引线框架1000的结构示意图;

46.图7b是图7a中7b区域的局部放大图;

47.图8a是根据本技术一实施例的引线框架2000的框架单元的结构示意图;

48.图8b是根据本技术另一实施例的引线框架3000的框架单元的结构示意图;

49.图8c是图8b所示框架单元的的不同设置位置的结构示意图。

具体实施方式

50.以下,结合具体实施方式,对本技术的技术进行详细描述。应当知道的是,以下具体实施方式仅用于帮助本领域技术人员理解本技术,而非对本技术的限制。

51.在本实施例中,提供一种半导体器件1。如图1a所示,所述半导体器件1包括半导体芯片20,以及用于塑封所述半导体芯片20以形成器件的封装材料em。如图1a所示,所述半导体器件1设有基岛110,与所述基岛110连接的连筋120,以及围绕所述基岛110设置的复数个引线指130。所述芯片20具有复数个焊盘201,每一焊盘201通过一引线l与一引线指130电性连接。

52.定义所述基岛110用于贴设所述半导体芯片20的表面(即,图1a中所述基岛110的上表面)所在的平面为第一平面p1。同时,定义引线指130用于接收所述引线l的表面(即,图1a中所述引线指130的上表面)所在的平面为第二平面p2,也就是说,每一引线指130用于接收所述引线l的表面均位于所述第二平面p2内。如图1a所示,所述第二平面p2平行于所述第一平面p1,并且,所述第二平面p2与所述第一平面p1属于不同平面。

53.以下,结合图1b和图1c详细描述所述连筋120的结构。

54.如图1b和图1c所示,所述连筋120具有第一部分121和第二部分122,其中,所述第一部分121为所述连筋120倾斜地连接至所述基岛110的部分,而所述第二部分122的一表面(即图1b中所述第二部分122的上表面)位于所述第二平面p2内。

55.如图1b和图1c所示,一分支部分123从所述第二部分122分出,用于接收一连接至所述芯片20的焊盘201的引线l。具体地,所述引线l连接至所述分支部分123的表面(即图1b中所述分支部分123的上表面),而该表面如图1b所示位于所述第二平面p2内。并且,所述分支部分123的边缘与所述基岛110的第一边缘e1相距一第一距离d1,如图1c所示。

56.由此,如图1a至图1c所示的,在本实施例中,所述连筋120通过从所述第二部分122分出所述分支部分123,以在连筋120中区分出用于接收引线的区域,而所述连筋120的其他所述第二部分122以及所述倾斜地连接至所述基岛110的第一部分121主要充当常规连筋在半导体器件中所起到的连接基岛的作用。

57.基于上述本技术的半导体器件1的结构,本领域技术人员可以根据实际需要,而具体设置引线指及连筋的位置。以下列举几个包含于本技术范围内的半导体器件,本领域技术人员可以理解的是,下述图2a至图8c所示的半导体器件及用于构建半导体器件的引线框架仅为更好地说明本技术,而非限制之用。

58.图2a和图2b是根据本技术另一实施例构建的半导体器件2。

59.如图2a所示,本实施例所述半导体器件2的大致结构与图1a所示半导体器件1相似。所述半导体器件2包括半导体芯片20,以及用于塑封所述半导体芯片20以形成器件的封

装材料em。如图2a所示,所述半导体器件2设有基岛210,与所述基岛210连接的连筋220,以及围绕所述基岛210设置的复数个引线指230。所述芯片20具有复数个焊盘201,每一焊盘201通过一引线l与一引线指230电性连接。

60.与图1a至图1c所示的所述半导体器件1中的连筋120相似地,如图2a和图2b所示,所述连筋220具有第一部分221和第二部分222;其中,所述第一部分221为所述连筋220倾斜地连接至所述基岛210的部分,而所述第二部分222的一表面(即图2a中所述第二部分222的上表面)位于所述第二平面p2内。

61.与图1a至图1c所示的所述半导体器件1中的连筋120相似地,如图2a和图2b所示,一分支部分223从所述连筋220的第二部分222分出,用于接收一连接至所述芯片20的焊盘201的引线l。具体地,所述引线l连接至所述分支部分223的表面(即图2a中所述分支部分123的上表面),而该表面如图2a所示位于所述第二平面p2内。此外,如图2b所示,所述分支部分223的边缘与所述基岛210的第一边缘e1相距一第一距离d1。

62.与图1a至图1c所示的所述半导体器件1不同的是,本实施例的所述半导体器件2中,一引线指230与所述连筋220相邻设置,如图2a和图2b所示。具体地,如图2b所示,与所述连筋220相邻的引线指230未直接连接至相邻的所述连筋220的分支部分223,并且,该引线指230的边缘与所述基岛210的第一边缘e1相距所述第一距离d1。

63.图3a和图3b是根据本技术另一实施例构建的半导体器件3。

64.如图3a所示,本实施例所述半导体器件3的大致结构与图2a所示半导体器件2相似。所述半导体器件3包括半导体芯片20,以及用于塑封所述半导体芯片20以形成器件的封装材料em。如图3a所示,所述半导体器件3设有基岛310、与所述基岛310连接的连筋320,以及围绕所述基岛310设置且与所述连筋320相邻的复数个引线指330。所述芯片20具有复数个焊盘201,每一焊盘201通过一引线l与一引线指330电性连接。

65.与图2a和图2b所示的所述半导体器件2中的连筋220相似地,如图3a和图3b所示,一分支部分323从所述连筋320的第二部分322分出,用于接收一连接至所述芯片20的焊盘201的引线l。具体地,所述引线l连接至所述分支部分323的表面(即图3a中所述分支部分323的上表面),而该表面如图3a所示位于所述第二平面p2内。此外,如图3b所示,所述分支部分323的边缘与所述基岛310的第一边缘e1相距一第一距离d1。

66.与图2a和图2b所示的所述半导体器件2不同的是,本实施例的所述半导体器件3设有第二连筋340,尤其是在与所述基岛310的所述第一边缘e1相对的第二边缘e2处设置第二连筋340,如图3a和图3b所示。

67.所述第二连筋340的结构优选地与连筋320相同。具体地,如图3a和图3b所示,所述第二连筋340同样具有倾斜地连接至所述基岛310的第一部分341、表面位于所述第二平面p2内的第二部分342,以及,从该第二部分分出的分支部分343。并且,如图3b所示,所述第二连筋340的分支部分342与所述基岛310的第二边缘e2之间相距一第二距离d2。该第二距离d2等于所述第一距离d1,也可以根据实际工艺需要而设定具体数值。如图3a和图3b所示,所述第二连筋340的所述分支部分343同样用于接收一引线。

68.图4a和图4b是根据本技术另一实施例构建的半导体器件4。

69.如图4a所示,本实施例所述半导体器件4的大致结构与图3a所示半导体器件3相似。所述半导体器件4包括半导体芯片20,以及用于塑封所述半导体芯片20以形成器件的封

装材料em。如图4a所示,所述半导体器件4设有基岛410、与所述基岛410连接的连筋420,以及围绕所述基岛410设置且与所述连筋420相邻的复数个引线指330。所述芯片20具有复数个焊盘201,每一焊盘201通过一引线l与一引线指430电性连接。

70.与图3a和图3b所示的所述半导体器件3中的连筋320相似地,如图4a和图4b所示,一分支部分423从所述连筋420的第二部分422分出,用于接收一连接至所述芯片20的焊盘201的引线l。具体地,所述引线l连接至所述分支部分423的表面(即图4a中所述分支部分423的上表面),而该表面如图4a所示位于所述第二平面p2内。此外,如图4b所示,所述分支部分423的边缘与所述基岛410的第一边缘e1相距一第一距离d1。

71.与图3a和图3b所示的所述半导体器件3相似地,如图4a和图4b所示,本实施例的所述半导体器件4在与所述基岛410的所述第一边缘e1相对的第二边缘e2处设置第二连筋440。具体地,如图4a和图4b所示,所述第二连筋440同样具有倾斜地连接至所述基岛410的第一部分441、表面位于所述第二平面p2内的第二部分442,以及,从该第二部分分出的分支部分443。并且,如图4b所示,所述第二连筋440的分支部分442与所述基岛410的第二边缘e2之间相距一第二距离d2。该第二距离d2等于所述第一距离d1,也可以根据实际工艺需要而设定具体数值。如图4a和图4b所示,所述第二连筋440的所述分支部分443同样用于接收一引线。

72.与图3a和图3b所示的所述半导体器件3不同的是,本实施例的所述半导体器件4中设有第三连筋450和第四连筋460,所述第三连筋450和第四连筋460分别设置于所述基岛410的侧边,并且,所述第三连筋450和第四连筋460的结构与所述第二连筋440相似。具体地,如图4a和图4b所示,所述第三连筋450具有倾斜地连接至所述基岛410的第一部分451、表面位于所述第二平面p2内的第二部分452,以及,从该第二部分分出的分支部分453;所述第四连筋460具有倾斜地连接至所述基岛410的第一部分461、表面位于所述第二平面p2内的第二部分462,以及,从该第二部分分出的分支部分463。如图4a所示,所述第三连筋450的分支部分453、所述第四连筋460的分支部分463位于所述第二平面p2内的表面,用于接收引线。

73.此外,如图4b所示,所述第三连筋450和所述第四连筋460分别相邻地设有一引线指430。所述第三连筋450的分支部分453及所述第四连筋460的分支部分463分别未直接连接至相邻的引线指430。尤其优选地,如图4b所示,所述第三连筋450的分支部分453面向所述基岛410的边缘4531与相邻的引线指430的边缘431共线。相似地,所述第四连筋460的分支部分463面向所述基岛410的边缘4631与相邻的引线指430的边缘431共线。

74.图4c所示的是本实施例的所述半导体器件4中所述连筋420、所述第二连筋440、所述第三连筋450和所述第四连筋460的另一设置位置。如图4c所示,本实施例的所述半导体器件4中,所述连筋420、所述第二连筋440、所述第三连筋450和所述第四连筋460可以分别设置于所述基岛410的四个角处。也就是说,如图4c所示,作为一种可选的实施方式,所述连筋420的所述第一部分421、所述第二连筋440的第一部分441、所述第三连筋450的第一部分451和所述第四连筋460的第一部分461分别可以倾斜地连接至所述基岛410的四个角。同时,所述连筋420的分支部分423、所述第三连筋450的分支部分453及所述第四连筋460的分支部分463分别未直接连接至相邻的引线指430。此外,如图4c所示,与图4b所示的结构相似地,所述第二连筋440的分支部分443、所述第三连筋450的分支部分453及所述第四连筋463

面向所述基岛410的边缘也同样分别与相邻的引线指430的边缘共线。

75.图5a是根据本技术另一实施例构建的半导体器件5。

76.如图5a所示,本实施例所述半导体器件5的大致结构与图1a所示半导体器件1相似。所述半导体器件5包括半导体芯片20,以及用于塑封所述半导体芯片20以形成器件的封装材料em。如图5a所示,所述半导体器件5设有基岛510,与所述基岛510连接的连筋520,以及围绕所述基岛510设置的复数个引线指530。所述芯片20具有复数个焊盘201,每一焊盘201通过一引线l与一引线指530电性连接。

77.与图1a至图1c所示的所述半导体器件1中的连筋120相似地,如图5a所示,所述连筋520具有第一部分521和第二部分222;其中,所述第一部分521为所述连筋520倾斜地连接至所述基岛510的部分,而所述第二部分522的一表面(即图5a中所述第二部分522的上表面)位于所述第二平面p2内。

78.与图1a至图1c所示的所述半导体器件1中的连筋120相似地,如图5a所示,一分支部分523从所述连筋520的第二部分522分出,用于接收一连接至所述芯片20的焊盘201的引线l。具体地,所述引线l连接至所述分支部分523的表面(即图5a中所述分支部分523的上表面),而该表面如图5a所示位于所述第二平面p2内。

79.与图1a至图1c所示的所述半导体器件1不同的是,本实施例的所述半导体器件5中设有一第二连筋540,所述第二连筋540连接至所述基岛510,如图5a所示。与所述连筋520不同的是,所述第二连筋540仅用于连接至所述基岛510而不用于接收一引线。

80.图5b所示的是图5a所示本实施例的半导体器件5中所述连筋520及第二连筋540的另一种设置位置。

81.如图5b所示,在本实施例的所述半导体器件5中,可以设置一连筋520和复数个第二连筋540,并将所述连筋520及复数个第二连筋540设置于所述基岛510的四个角处。也就是说,如图5b所示,作为一个可选的实施方式,所述连筋520的所述第一部分521可以倾斜地连接至所述基岛510的一角,并且,所述连筋520的分支部分523同样未直接连接至相邻的引线指530。而在所述基岛510的其他三个角处分别设置一第二连筋540,使得一条第二连筋540连接至所述基岛510的一角。如上文所述的,与所述连筋520不同的是,所述第二连筋540仅用于连接至所述基岛510而不用于接收一引线。

82.图6a和图6b是根据本技术另一实施例构建的半导体器件6。

83.如图6a所示,本实施例所述半导体器件6中包含两个半导体芯片20,以及用于塑封所述半导体芯片20以形成器件的封装材料em。因此,如图6a和图6b所示,每一半导体芯片20对应一个基岛。

84.具体地,如图6a和图6b所示,所述半导体器件6包括两个芯片20,所述半导体器件6设有两个基岛610、与每一基岛610对应设置一连筋620、与每一基岛610对应设置一第二连筋630,以及围绕所述基岛610设置的复数个引线指640。所述每一芯片20具有复数个焊盘201,每一焊盘201通过一引线l与一引线指640电性连接。

85.与图1a至图1c所示的所述半导体器件1中的连筋120相似地,如图6a和图6b所示,每一连筋620具有第一部分621和第二部分622;其中,所述第一部分621为所述连筋620倾斜地连接至一基岛610的部分,而所述第二部分622的一表面(即图6a中所述第二部分622的上表面)位于所述第二平面p2内。

86.与图1a至图1c所示的所述半导体器件1中的连筋120相似地,如图6a和图6b所示,一分支部分623从一连筋620的第二部分622分出,用于接收一连接至一芯片20的焊盘201的引线l。具体地,所述引线l连接至所述分支部分623的表面(即图6a中所述分支部分623的上表面),而该表面如图6a所示位于所述第二平面p2内。

87.在本实施例中,如图6a和图6b所示,每一基岛610对应设置一第二连筋640,所述第二连筋640连接至一基岛610。与所述连筋520不同的是,所述第二连筋640仅用于连接至一基岛610而不用于接收一引线。

88.本领域技术人员可以理解的是,本技术同时还提供引线框架,所述引线框架在切割后能够获得如图1a至图6b中任意一个所示的基岛、连筋、第二连筋、第三连筋、第四连筋及引线指的结构。也就是说,本技术上述半导体器件1、半导体器件2、半导体器件3、半导体器件4、半导体器件5和半导体器件6分别可以对应至少一种引线框架,以最终获得如图1a至图6b中任意一个所示的基岛、连筋、第二连筋、第三连筋、第四连筋及引线指的设置位置及结构。

89.作为一个具体实施例,如图7a所示,本技术提供一种引线框架1000,所述引线框架1000包括至少一个以切割线w为边界定义的框架单元,每一框架单元在切割后可以用于构建成封装体(半导体器件)。以下,以一个框架单元的结构作为范例进行说明。

90.如图7a所示,在一个框架单元中,所述引线框架1000包括:基岛1110、与所述基岛1110连接的连筋1120、围绕所述基岛1110设置的复数个引线指1130,以及用于连接所述基岛1110、连筋1120及复数个引线指1130的外框1001。本领域技术人员可以理解的时,所述基岛1110用于贴设一芯片。该芯片进一步可以通过引线与所述连筋1120及引线指1130电性连接。

91.如图7a所示,所述连筋1120具有第一部分1121和第二部分1122,一分支部分123从所述第二部分122分出,用于接收一连接至一芯片的引线。

92.如图7a和图7b所示,所述第一部分1121为所述连筋1120倾斜地连接至所述基岛110的部分。因而,如图7b所示,定义所述基岛1110用于贴设一半导体芯片的表面(即,图7b中所述基岛1110的上表面)所在的平面为第一平面p1;同时,所述连接1120的第二部分1122的表面所在的平面为第二平面p2。如图7b所示,所述第二平面p2平行于所述第一平面p1,并且,所述第二平面p2与所述第一平面p1属于不同平面。

93.如图7b所示,所述分支部分1123用于接收一引线的表面(即图7b中所述分支部分1123的上表面)位于所述第二平面p2内。此外,如图7a所示,所述分支部分1123的边缘与所述基岛1110的第一边缘e1相距一第一距离d1。

94.图8a至图8c所示的,是本技术中所述引线框架可以具有的其他结构。在图8a至图8c中,以切割线w所定义的框架单元作为示例进行描述。

95.如图8a所示,在本技术另一实施例中提供的引线框架2000的框架单元中,包括一基岛2210、与所述基岛2210连接的连筋2220,以及围绕所述基岛2210设置的复数个引线指2230。

96.在本实施例中,所述基岛2210、所述连筋2220和所述引线指2230的结构布置均与图7a和图7b所述的引线框架1000相同。具体地,如图8a所示,所述连筋2220具有第一部分2221和第二部分2222;其中,所述第一部分2221为所述连筋2220倾斜地连接至所述基岛

2210的部分。分支部分2223从所述连筋2220的第二部分2222分出,用于接收一连接芯片的引线。所述基岛2210、所述第二部分2221及所述分支部分2223的表面位置与图7b中引线框架1000的位置相同,在此不再赘述。

97.与框架1000不同的是,在引线框架2000中,在与所述基岛2210的所述第一边缘e1相对的第二边缘e2处设置第二连筋2240,所述第二连筋2240同样具有倾斜地连接至所述基岛2210的第一部分2241、第二部分2242,以及从第二部分2242分出的分支部分2243,如图8a所示。此外,所述连筋2220的分支部分2223的边缘与所述基岛2210的第一边缘e1相距一第一距离d1,而所述第二连筋2240的分支部分2242与所述基岛2210的第二边缘e2之间相距一第二距离d2。该第二距离d2等于所述第一距离d1,也可以根据实际工艺需要而设定具体数值。

98.如图8b所示,在本技术另一实施例中提供的引线框架3000的框架单元中,包括一基岛3410、与所述基岛3410连接的连筋3420,以及围绕所述基岛3410设置的复数个引线指3430、第二连筋3440、第三连筋3450和第四连筋3460。所述第三连筋3450和所述第四连筋3460的结构与图7a及图7b中所述连筋2220的结构相同。

99.如图8c所示的是图8b所示的引线框架3000的所述连筋3420、第二连筋3440、第三连筋3450和第四连筋3460的另一种位置设置。如图8c所示,所述连筋3420、第二连筋3440、第三连筋3450和第四连筋3460分别设置于所述基岛3410的四个角。

100.如图8c所示,本实施例的所述引线框架3000中,所述连筋3420、所述第二连筋3440、所述第三连筋3450和所述第四连筋3460可以分别设置于所述基岛3410的四个角处。也就是说,如图8c所示,作为一种可选的实施方式,所述连筋3420的所述第一部分3421、所述第二连筋3440的第一部分3441、所述第三连筋3450的第一部分3451和所述第四连筋3460的第一部分3461分别可以倾斜地连接至所述基岛3410的四个角。同时,所述连筋3420的分支部分3423、所述第三连筋3450的分支部分3453及所述第四连筋3460的分支部分3463分别未直接连接至相邻的引线指3430。此外,如图8c所示,所述第二连筋3440的分支部分3443、所述第三连筋3450的分支部分3453及所述第四连筋3463面向所述基岛3410的边缘也同样分别与相邻的引线指3430的边缘共线。

101.在本技术中,所述连筋(和/或所述第二连筋和/或第三连筋和/或第四连筋)通过从第二部分分出所述分支部分,以在连筋中区分出用于焊接引线的区域,而所述连筋的其他所述第二部分以及所述倾斜地连接至所述基岛的第一部分主要充当常规连筋在引线框架中所起到的连接基岛的作用。因而,在后续的焊接引线工艺中,在对引线指进行常规焊线前滚平处理时,由于所述连筋的所述第二部分的表面、所述分支部分的表面,以及所述引线指的表面均处于同一平面内(第二平面),使得,所述连筋的所述第二部分及所述分支部分也同样受到滚平处理,以具备能够焊接引线的表面质量。由此,解决了现有引线框架中,因连筋的压痕和/或不平整等问题,使得在连筋上焊接引线时会造成的质量问题。

102.此外,由于所述连筋的所述第二部分的表面处于与其他引线指的表面处于同一平面内,因此也避免了引线的焊点位置低的情况,从而解决了线弧及线长均不理想及因基岛面与封装材料的易分层而导致的易线脱问题。

103.本技术已由上述相关实施例加以描述,然而上述实施例仅为实施本技术的范例。必需指出的是,已公开的实施例并未限制本技术的范围。相反地,包含于权利要求书的精神

及范围的修改及均等设置均包括于本技术的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1