半导体存储装置的制作方法

1.本实用新型涉及一种半导体装置,尤其是涉及一种半导体存储装置。

背景技术:

2.随着各种电子产品朝小型化发展之趋势,动态随机存储器(dynamic randomaccess memory,dram)单元的设计也必须符合高集成度及高密度之要求。对于一具备凹入式闸极结构之dram单元而言,由于其可以在相同的半导体基底内获得更长的载流子通道长度,以减少电容结构之漏电情形产生,因此在目前主流发展趋势下,其已逐渐取代仅具备平面闸极结构之dram单元。

3.一般来说,具备凹入式闸极结构之dram单元会包含一晶体管组件与一电荷贮存装置,以接收来自于位线及字线的电压信号。然而,受限于工艺技术之故,现有具备凹入式闸极结构之dram单元仍存在有许多缺陷,还待进一步改良并有效提升相关存储器组件之效能及可靠度。

技术实现要素:

4.本实用新型公开了一种半导体存储装置,其特征在于包含一基底,定义有一存储区以及一围绕存储区的一边缘区;多个有源区,位于基底表面且位于存储区内,并且各有源区沿着一斜向方向排列,边缘区内包含有一虚设有源区图案,虚设有源区图案包含有一第一边缘主轴图案,以及多条第一长分支与多条短分支连接边缘主轴图案;多个存储节点接触,接触虚设有源区图案的第一长分支,但不接触虚设有源区图案的短分支。

5.本实用新型的特征在于,有别于公知技术中通常仅将存储节点接触(storagenode contact,简称sc)设置在存储区内的有源区(active area,aa)两端,而不设置在边缘区中,本实用新型除了将存储节点接触设置在有源区上,也同时将一部分的存储节点接触设置在边缘区中的虚设有源区图案上,其中虚设有源区图案虽然并未当作组件使用,但是将一部分的存储节点接触设置在边缘区中的虚设有源区图案上,可以降低制程的难度,且周围的存储节点接触可以充当保护结构以保护中间存储区组件,防止组件受到物理或是电性上的影响。

附图说明

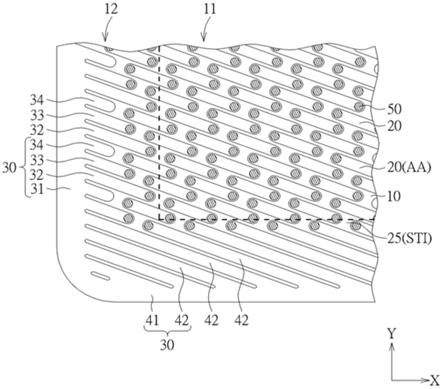

6.图1绘示本实用新型一存储区内的有源区以及边缘区内的虚设有源区图案的部分上视示意图。

7.图2绘示根据本实用新型一实施例,形成存储节点接触(sc)在有源区以及虚设有源区图案上的示意图。

8.图3绘示根据本实用新型另一实施例,形成存储节点接触(sc)在有源区以及虚设有源区图案上的示意图。

9.其中,附图标记说明如下:

10.10:基底

11.11:存储区

12.12:边缘区

13.20(aa):有源区

14.25(sti):浅沟渠隔离

15.30:虚设有源区图案

16.31:第一边缘主轴图案

17.32:第一长分支

18.33:第二长分支

19.34:短分支

20.41:第二边缘主轴图案

21.42:第二边缘分支

22.50:存储节点接触

具体实施方式

23.为使熟悉本实用新型所属技术领域的一般技术者能更进一步了解本实用新型,下文特列举本实用新型的数个优选实施例,并配合所附的附图,详细说明本实用新型的构成内容及所欲达成的功效。

24.如图1所示,本实用新型提供一半导体装置1,其包含有一基底10,基底上定一有一存储区(memory cell region)11以及围绕该存储区的一边缘区(periphery region)12。其中,半导体存储装置例如是包含一凹入式闸极的随机动态处理存储器(dynamic random access memory,dram),其包含有至少一晶体管组件(未绘示)以及至少一电容结构(未绘示),以作为dram阵列中的最小组成单元并接收来自于字线(word line,wl)及位线(bit line,bl)的电压信号。本实施例中,为了简化图式,并未绘出字线以及位线的位置。

25.具体来说,该半导体存储装置包含一基底10,例如是一硅基底、含硅基底(如sic、sige)或硅覆绝缘(silicon

‑

on

‑

insulator,soi)基底等,基底10的存储区11内定义有多个有源区(active area,aa)20,有源区20相互平行且相互间隔地沿着一斜向方向d1延伸,而呈一矩阵排列。有源区20的制作方法例如为先形成多条沿着斜向方向d1平行排列的条状图案,接着再利用蚀刻等图案化步骤将该条状结构截断成多段,接下来再形成一浅沟渠隔离(shallow trench isolation,sti)25覆盖于基底10上,其中被浅沟渠隔离(sti)25所曝露的区域就定义为有源区20。上述有源区20的制作方法属于本领域的公知技术,其余细节不多加赘述。

26.此外,在边缘区12内包含有虚设有源区图案30,其中虚设有源区图案30来自在上述有源区20的制作过程中,一些未被完全截断的边缘图案留在基底10上的边缘区12内,因此而形成了虚设有源区图案30。这些虚设有源区图案30可能不像有源区20会彼此分离,而是彼此连接而构成一连续性结构,因此在实际制程中通常无法当作组件使用。在公知技术中,也通常不会在虚设有源区图案30上继续形成组件。

27.本实施例包含有虚设有源区图案30,位于边缘区12的其中一个边界(例如为左侧边界),且虚设有源区图案30包含有边缘主轴图案还有复数个长分支与短分支与边缘主轴

图案相连。举例来说,第一边缘主轴图案31沿着一第一方向(例如为y方向)排列,复数个第一长分支32、复数个第二长分支33与复数个短分支34连接第一边缘主轴图案31。其中第一长分支32的长度大于第二长分支33,而第二长分支33的长度又大于短分支34。沿着第一方向由上至下来看,各分支依照短分支34、第二长分支33以及第一长分支32的顺序循环排列。此外,上述第一长分支32、第二长分支33与短分支34皆沿着斜向方向d1排列,也就是与有源区20的排列方向相同。

28.另外,除了上述第一边缘主轴图案31以及其分支位于边缘区12的其中一边,边缘区12的其他边界可能也包含有虚设有源区图案。举例来说,如图1所示,虚设有源区图案30的另一部分位于边缘区12的下方边界,虚设有源区图案30的下方边界部分可能如上述虚设有源区图案30的左侧边界部分一样,包含有长分支与短分支交错排列,或着是仅包含有相同长度的分支。以本实施例为例,虚设有源区图案30的下方边界部分包含有第二边缘主轴图案41沿着一第二方向(例如为x方向)排列,且多个第二边缘分支42连接第二边缘主轴图案41并沿着斜向方向d1排列,其中各个第二边缘分支42的长度彼此相同。

29.可理解的是,图1中仅画出边缘区12的两个边界,分别是第一边缘主轴图案31与第二边缘主轴图案41。但是实际上边缘区12可能包含有更多边界,例如上方边界与右侧边界,为了图式简洁本实施例并未画出。

30.图2绘示根据本实用新型一实施例,形成存储节点接触(sc)在有源区以及虚设有源区图案上的示意图。如图2所示,形成多个存储节点接触50。这里所述的存储节点接触50例如是连接基底(有源区20)与电容结构(图未示)的接触组件。一般来说,因为只有存储区11内的有源区20当作组件使用,因此公知技术中仅会在存储区11内的每一个有源区20的两端形成存储节点接触50。而本实用新型与公知技术不同之处在于,除了在存储区11内的有源区20上形成存储节点接触50以外,存储节点接触50也会一并形成在边缘区12内一部分的虚设有源区图案上,例如形成在虚设有源区图案30上。

31.以本实施例为例,一部分的存储节点接触50形成在虚设有源区图案30上,其中存储节点接触50可形成在较为靠近存储区11的第一长分支32以及第二长分支33的末端,然而却不形成在短分支34上。这种配置方式的优点在于,在形成存储节点接触50时,将存储节点接触50的分布范围稍微扩大至边缘区12内,因为不需要过度着重边界细节,因此在制作上难度可以降低。除此之外,形成在边缘区12内的存储节点接触50虽然并没有当作电子组件使用,但是其排列在存储区11的周围,也可以达到保护有源区内组件的功效,避免有源区内的组件受到物理上或电性的影响。

32.在本实用新型的其他实施例中,存储节点接触50也可以形成于另一边的虚设有源区图案上,例如形成在虚设有源区图案30的各第二边缘分支42的末端。或是如图3所示,图3绘示根据本实用新型另一实施例,形成存储节点接触(sc)在有源区以及虚设有源区图案上的示意图。在本实施例中,存储节点接触50也可以不只形成在各第二边缘分支42的末端,也可形成在例如第二边缘分支42的中段(原先位于第二边缘分支42的末端的存储节点接触50可以选择性地存在或不存在),也属于本实用新型的涵盖范围。

33.值得注意的是,在形成上述存储节点接触50之前,还形成有一些其他的组件,例如字线、位线、位线接触等。而在形成上述存储节点接触50之后,还可能包含形成例如电容结构以连接存储节点接触与有源区。这些组件属于本领域的公知技术,本实用新型中为了图

式简洁并未画出这些组件,但是这些组件理应存在于半导体存储装置中。

34.综合以上说明书与图式,本实用新型提供一种半导体存储装置,其特征在于包含一基底10,定义有一存储区11以及一围绕存储区11的一边缘区12;多个有源区20,位于基底10表面且位于存储区11内,并且各有源区20沿着一斜向方向d1排列,边缘区12内包含有一虚设有源区图案30,虚设有源区图案30包含有一第一边缘主轴图案31,以及多条第一长分支32与多条短分支34连接边缘主轴图案31;多个存储节点接触50,接触虚设有源区图案30的第一长分支32,但不接触虚设有源区图案30的短分支34。

35.在一些实施例中,其中多个存储节点接触50,更接触存储区11内的多个有源区20的两端点。

36.在一些实施例中,其中虚设有源区图案30的第一边缘主轴图案31沿着一第一方向(y方向)排列,其中第一方向不同于斜向方向d1。

37.在一些实施例中,其中沿着第一方向,第一长分支32与短分支34交互排列。

38.在一些实施例中,其中虚设有源区图案30更包含有一第二边缘主轴图案41,其中第二边缘主轴图案41沿着一第二方向(x方向)排列,其中第二方向与第一方向互相垂直。

39.在一些实施例中,其中第二边缘主轴图案41包含有多个第二边缘分支42,连接第二边缘主轴图案41,且各第二边缘分支42沿着斜向方向d1排列。

40.在一些实施例中,其中一部分的存储节点接触50位于第二边缘分支42的末段。

41.在一些实施例中,其中有一部分的存储节点接触50位于第二边缘分支42的中段。

42.在一些实施例中,其中虚设有源区图案30的第一长分支32与短分支34皆沿着斜向方向d1排列。

43.在一些实施例中,其中第一长分支32的一末端呈现椭圆形,另一末端与边缘主轴图案连接。

44.在一些实施例中,其中虚设有源区图案30更包含有多条第二长分支33,沿着斜向方向d1排列,且连接第一边缘主轴图案31。

45.在一些实施例中,其中至少有一存储节点接触50接触第二长分支33。

46.在一些实施例中,其中各存储区11内的有源区20不接触边缘区12内的虚设有源区图案30。

47.在一些实施例中,其中更包含有一浅沟渠隔离25,位于基底10上,其中各有源区20以及虚设有源区图案30被浅沟渠隔离25暴露出。

48.在一些实施例中,其中有源区20的材质包含有硅,且虚设有源区图案30的材质也包含硅。

49.综上所述,本实用新型的特征在于,有别于公知技术中通常仅将存储节点接触(storage node contact,简称sc)设置在存储区内的有源区(active area,aa)两端,而不设置在边缘区中,本实用新型除了将存储节点接触设置在有源区上,也同时将一部分的存储节点接触设置在边缘区中的虚设有源区图案上,其中虚设有源区图案虽然并未当作组件使用,但是将一部分的存储节点接触设置在边缘区中的虚设有源区图案上,可以降低制程的难度,且周围的存储节点接触可以充当保护结构以保护中间存储区组件,防止组件受到物理或是电性上的影响。

50.以上所述仅为本实用新型的优选实施例而已,并不用于限制本实用新型,对于本

领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1