一种半导体芯片集成用三维堆叠封装结构的制作方法

1.本实用新型涉及半导体芯片封装的技术领域,特别是涉及一种半导体芯片集成用三维堆叠封装结构。

背景技术:

2.目前半导体芯片封装工艺主要为芯片在基板的两端做堆叠,并通过焊线的方式,实现芯片到芯片、芯片到基板的电气连接,然后在进行塑封保护,由于封装元件是基板、芯片、粘合剂以及塑封材料等多种材料的组合,在工作过程中,材料的热膨胀系数不匹配,使得塑封后容易出现翘曲的情况,影响产品的正常使用,导致使用局限性较高。

技术实现要素:

3.为解决上述技术问题,本实用新型提供一种能够有效避免出现翘曲的情况,确保产品的正常使用,降低使用局限性的半导体芯片集成用三维堆叠封装结构。

4.本实用新型的一种半导体芯片集成用三维堆叠封装结构,包括基板、两组半导体芯片、上塑封层、下塑封层、上压盖、下压盖、四组固定螺栓和两组顶紧压板,两组半导体芯片的底端均涂装设置有粘合剂,两组半导体芯片通过粘合剂固定粘贴在基板的顶端和底端,两组半导体芯片的左右两端均焊接设置有焊接线,并且每组半导体芯片通过两组焊接线与基板电连接,上塑封层和下塑封层分别盖装在两组半导体芯片的上,上压盖和下压盖上均设置有两组连接板,上压盖和下压盖通过连接板与固定螺栓的配合分别固定安装在基板的顶端和底端,上压盖和下压盖的内部均设置有多组弹簧,两组顶紧压板通过与弹簧的连接分别固定安装在上压盖和下压盖内,并且一组顶紧压板的底端与上塑封层的顶端贴紧,另一组顶紧压板的顶端与下塑封层的底端贴紧。

5.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述两组顶紧压板上均设置有多组透气孔,所述上压盖和下压盖的左右两端均设置有多组散热口。

6.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述四组焊接线的两端均焊接设置有焊线锥台。

7.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述上压盖和下压盖的前端均设置有观察窗。

8.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述四组固定螺栓上均套装设置有紧固垫圈。

9.本实用新型的一种半导体芯片集成用三维堆叠封装结构,还包括四组防滑胶圈,基板上设置有四组沉槽,四组防滑胶圈通过与固定螺栓的配合分别固定安装在四组沉槽内。

10.本实用新型的一种半导体芯片集成用三维堆叠封装结构,还包括两组把手,两组把手分别固定安装在上压盖和下压盖的右端。

11.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述两组把手的圆周外

壁上均设置有防滑网纹。

12.与现有技术相比本实用新型的有益效果为:首先在组装时,半导体芯片通过粘合剂粘合在基板的两端面,并通过焊接线完成与基板的电连接,然后通过上塑封层和下塑封层完成塑封保护,最后再将上压盖和下压盖安装牢靠,使顶紧压板与上塑封层和下塑封层紧密接触,若温度变化时,由于材料的膨胀系数不匹配,产生翘曲时,会使弹簧产生一个指向上塑封层和下塑封层的顶紧力,从而使得顶紧压板紧紧压住上塑封层和下塑封层,防止结构两端出现翘曲,从而能够有效避免出现翘曲的情况,确保产品的正常使用,降低使用局限性。

附图说明

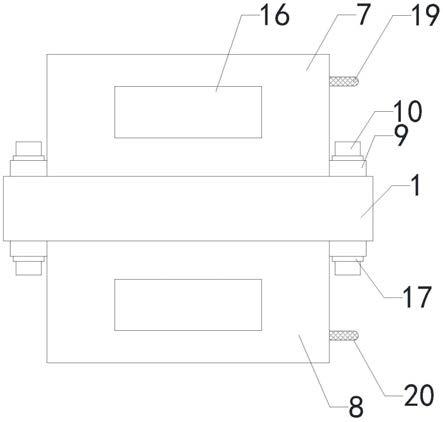

13.图1是本实用新型的前侧结构示意图;

14.图2是本实用新型的前侧剖面结构示意图;

15.图3是本实用新型中上压盖的上侧结构示意图;

16.图4是本实用新型中上压盖的右侧结构示意图;

17.图5是本实用新型中压板的上侧结构示意图;

18.附图中标记:1、基板;2、半导体芯片;3、粘合剂;4、焊接线;5、上塑封层;6、下塑封层;7、上压盖;8、下压盖;9、连接板;10、固定螺栓;11、弹簧;12、顶紧压板;13、透气孔;14、散热口;15、焊线锥台;16、观察窗;17、紧固垫圈;18、防滑胶圈;19、把手;20、防滑网纹。

具体实施方式

19.下面结合附图和实施例,对本实用新型的具体实施方式作进一步详细描述。以下实施例用于说明本实用新型,但不用来限制本实用新型的范围。

20.如图1至图5所示,本实用新型的一种半导体芯片集成用三维堆叠封装结构,包括基板1、两组半导体芯片2、上塑封层5、下塑封层6、上压盖7、下压盖8、四组固定螺栓10和两组顶紧压板12,两组半导体芯片2的底端均涂装设置有粘合剂3,两组半导体芯片2通过粘合剂3固定粘贴在基板1的顶端和底端,两组半导体芯片2的左右两端均焊接设置有焊接线4,并且每组半导体芯片2通过两组焊接线4与基板1电连接,上塑封层5和下塑封层6分别盖装在两组半导体芯片2的上,上压盖7和下压盖8上均设置有两组连接板9,上压盖7和下压盖8通过连接板9与固定螺栓10的配合分别固定安装在基板1的顶端和底端,上压盖7和下压盖8的内部均设置有多组弹簧11,两组顶紧压板12通过与弹簧11的连接分别固定安装在上压盖7和下压盖8内,并且一组顶紧压板12的底端与上塑封层5的顶端贴紧,另一组顶紧压板12的顶端与下塑封层6的底端贴紧;首先在组装时,半导体芯片2通过粘合剂3粘合在基板1的两端面,并通过焊接线4完成与基板1的电连接,然后通过上塑封层5和下塑封层6完成塑封保护,最后再将上压盖7和下压盖8安装牢靠,使顶紧压板12与上塑封层5和下塑封层6紧密接触,若温度变化时,由于材料的膨胀系数不匹配,产生翘曲时,会使弹簧11产生一个指向上塑封层5和下塑封层6的顶紧力,从而使得顶紧压板12紧紧压住上塑封层5和下塑封层6,防止结构两端出现翘曲,从而能够有效避免出现翘曲的情况,确保产品的正常使用,降低使用局限性。

21.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述两组顶紧压板12上

均设置有多组透气孔13,所述上压盖7和下压盖8的左右两端均设置有多组散热口14;通过设置透气孔13和散热口14,能够确保结构内部空气的流通,从而能够具有良好的散热效果,提高使用可靠性。

22.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述四组焊接线4的两端均焊接设置有焊线锥台15;通过设置焊线锥台15,能够使得焊接线4与基板1和半导体芯片2的连接更加的牢固,防止出现断开的情况,提高使用可靠性。

23.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述上压盖7和下压盖8的前端均设置有观察窗16;通过设置观察窗16,能够便于观察内部的使用情况,便于及时进行调整,降低使用局限性。

24.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述四组固定螺栓10上均套装设置有紧固垫圈17;通过设置紧固垫圈17,能够有效防止固定螺栓10出现松动的情况,提高使用可靠性。

25.本实用新型的一种半导体芯片集成用三维堆叠封装结构,还包括四组防滑胶圈18,基板1上设置有四组沉槽,四组防滑胶圈18通过与固定螺栓10的配合分别固定安装在四组沉槽内;通过设置防滑胶圈18,能够使连接板9与基板1连接的更加紧密,防止出现打滑的情况,提高使用可靠性。

26.本实用新型的一种半导体芯片集成用三维堆叠封装结构,还包括两组把手19,两组把手19分别固定安装在上压盖7和下压盖8的右端;通过设置把手19,能够使上压盖7和下压盖8的取放更加的便捷,降低使用局限性。

27.本实用新型的一种半导体芯片集成用三维堆叠封装结构,所述两组把手19的圆周外壁上均设置有防滑网纹20;通过设置防滑网纹20,能够有效防止在取放时出现打滑脱手的情况,提高使用可靠性。

28.本实用新型的一种半导体芯片集成用三维堆叠封装结构,其在工作时,首先在组装时,半导体芯片2通过粘合剂3粘合在基板1的两端面,并通过焊接线4完成与基板1的电连接,然后通过上塑封层5和下塑封层6完成塑封保护,最后再将上压盖7和下压盖8安装牢靠,使顶紧压板12与上塑封层5和下塑封层6紧密接触,若温度变化时,由于材料的膨胀系数不匹配,产生翘曲时,会使弹簧11产生一个指向上塑封层5和下塑封层6的顶紧力,从而使得顶紧压板12紧紧压住上塑封层5和下塑封层6,防止结构两端出现翘曲。

29.本实用新型的一种半导体芯片集成用三维堆叠封装结构,其安装方式、连接方式或设置方式均为常见机械方式,只要能够达成其有益效果的均可进行实施;本行业内技术人员只需按照其附带的使用说明书进行安装和操作即可。

30.以上所述仅是本实用新型的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型技术原理的前提下,还可以做出若干改进和变型,这些改进和变型也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1