多层式压敏电阻的制作方法

1.本实用新型涉及一种压敏电阻,特别是涉及一种多层式压敏电阻。

背景技术:

2.压敏电阻(varistor)是一种电子组件,也称为voltage dependent resistor(vdr),其电阻会随着施加的电压而变化,它具有类似于二极管的非线性特性(非奥姆电流-电压特性)。然而,与二极管相反,它在两个横向电流方向上具有相同的特性。传统上,压敏电阻实际上是通过连接两个整流器(例如反并联配置的氧化铜或者氧化锗整流器)来构造的。在低电压下,压敏电阻具有较高的电阻,该电阻会随着电压的升高而减小。现代的压敏电阻主要基于烧结的陶瓷金属氧化物材料,这些材料仅在微观尺度上表现出方向性。这种类型通常称为金属氧化物压敏电阻(mov)。另外,压敏电阻可以用作电路中的控制或者补偿组件,以提供最佳工作条件或者防止过大的瞬态电压。当压敏电阻用来做为保护设备时,它们在触发时会将过高电压所产生的电流与敏感组件分流。

技术实现要素:

3.本实用新型所要解决的技术问题在于,针对现有技术的不足提供一种多层式压敏电阻。

4.为了解决上述的技术问题,本实用新型所采用的其中一技术方案是提供一种多层式压敏电阻,其包括:一多层式堆栈结构,该多层式堆栈结构包括一绝缘载体、设置在绝缘载体内的多个第一内导电层以及设置在绝缘载体内的多个第二内导电层,且多个第一内导电层与多个第二内导电层交替排列;以及一外电极结构,该外电极结构部分地包覆多层式堆栈结构,外电极结构包括电性接触多个第一内导电层的一第一外电极层以及电性接触多个第二内导电层的一第二外电极层,且第一外电极层以及第二外电极层分别包覆多层式堆栈结构的一第一侧端部以及一第二侧端部。

5.根据本实用新型的一技术方案的一方面,绝缘载体包括一绝缘上盖、一绝缘下盖以及连接于绝缘上盖与绝缘下盖之间的一绝缘本体,该绝缘本体的周围具有一第一外表面、一第二外表面、一第三外表面以及一第四外表面,且多个第一内导电层以及多个第二内导电层交替排列在绝缘本体内。

6.根据本实用新型的一技术方案的一方面,每一第一内导电层具有从绝缘本体的第一外表面裸露的一第一前裸露端、面向绝缘本体的第二外表面的一第一后内埋端、面向绝缘本体的第三外表面的一第一左内埋端以及面向绝缘本体的第四外表面的一第一右内埋端。

7.根据本实用新型的一技术方案的一方面,第一前裸露端电性接触第一外电极层,第一后内埋端对应于第一前裸露端且被包覆在绝缘本体内,第一左内埋端连接于第一前裸露端与第一后内埋端之间且被包覆在绝缘本体内,且第一右内埋端连接于第一前裸露端与第一后内埋端之间且被包覆在绝缘本体内。

8.根据本实用新型的一技术方案的一方面,第二内导电层具有从绝缘本体的第二外表面裸露的一第二前裸露端、面向绝缘本体的第一外表面的一第二后内埋端、面向绝缘本体的第四外表面的一第二左内埋端以及面向绝缘本体的第三外表面的一第二右内埋端。

9.根据本实用新型的一技术方案的一方面,第二前裸露端电性接触第二外电极层,第二后内埋端对应于第二前裸露端且被包覆在绝缘本体内,第二左内埋端连接于第二前裸露端与第二后内埋端之间且被包覆在绝缘本体内,且第二右内埋端连接于第二前裸露端与第二后内埋端之间且被包覆在绝缘本体内。

10.根据本实用新型的一技术方案的一方面,所述绝缘载体符合下列的条件:g与t1的比值为1:0.3~1.0,g与t2的比值为1:0.3~1.0,d11与g的比值为1:0.3~1.0,d12与g的比值为1:0.3~1.0,d21与g的比值为1:0.3~1.0,且d22与g的比值为1:0.3~1.0;其中,t1为绝缘上盖的厚度,t2为绝缘下盖的厚度,g为彼此相邻的第一内导电层与第二内导电层之间的距离,d11为第一内导电层的第一左内埋端与绝缘本体的第三外表面之间的距离,d12为第一内导电层的第一右内埋端与绝缘本体的第四外表面之间的距离,d21为第二内导电层的第二左内埋端与绝缘本体的第四外表面之间的距离,d22为第二内导电层的第二右内埋端与绝缘本体的第三外表面之间的距离。

11.为了解决上述的技术问题,本实用新型所采用的另外一技术方案是提供一种多层式压敏电阻,其包括:一多层式堆栈结构,该多层式堆栈结构包括一绝缘载体、设置在绝缘载体内的多个第一内导电层以及设置在绝缘载体内的多个第二内导电层,且多个第一内导电层与多个第二内导电层交替排列;以及一外电极结构,该外电极结构部分地包覆多层式堆栈结构,外电极结构包括电性接触多个第一内导电层的一第一外电极层以及电性接触多个第二内导电层的一第二外电极层,且第一外电极层以及第二外电极层分别包覆多层式堆栈结构的一第一侧端部以及一第二侧端部;其中,绝缘载体包括一绝缘上盖、一绝缘下盖以及连接于绝缘上盖与绝缘下盖之间的一绝缘本体,且绝缘本体的周围具有一第一外表面、一第二外表面、一第三外表面以及一第四外表面;其中,绝缘载体符合下列的条件:g与t1的比值为1:0.3~1.0,g与t2的比值为1:0.3~1.0,d11与g的比值为1:0.3~1.0,d12与g的比值为1:0.3~1.0,d21与g的比值为1:0.3~1.0,且d22与g的比值为1:0.3~1.0;其中,t1为绝缘上盖的厚度,t2为绝缘下盖的厚度,g为彼此相邻的第一内导电层与第二内导电层之间的距离,d11为第一内导电层的一第一左内埋端与绝缘本体的第三外表面之间的距离,d12为第一内导电层的一第一右内埋端与绝缘本体的第四外表面之间的距离,d21为第二内导电层的一第二左内埋端与绝缘本体的第四外表面之间的距离,d22为第二内导电层的一第二右内埋端与绝缘本体的第三外表面之间的距离。

12.本实用新型的其中一有益效果在于,本实用新型所提供的一种多层式压敏电阻,其能通过“多层式堆栈结构包括一绝缘载体、设置在绝缘载体内的多个第一内导电层以及设置在绝缘载体内的多个第二内导电层,且多个第一内导电层与多个第二内导电层交替排列”以及“外电极结构部分地包覆多层式堆栈结构,外电极结构包括电性接触多个第一内导电层的一第一外电极层以及电性接触多个第二内导电层的一第二外电极层,且第一外电极层以及第二外电极层分别包覆多层式堆栈结构的一第一侧端部以及一第二侧端部”的技术方案,以得到多层式压敏电阻的产品。

13.本实用新型的另外一有益效果在于,本实用新型所提供的一种多层式压敏电阻,

其能通过“g与t1的比值为1:0.3~1.0”、“g与t2的比值为1:0.3~1.0”、“d11与g的比值为1:0.3~1.0”、“d12与g的比值为1:0.3~1.0”、“d21与g的比值为1:0.3~1.0”以及“d22与g的比值为1:0.3~1.0”的技术方案,以降低漏电流(leakage current)并且提升通流容量(即最大峰值电流值(maximum peak current))。

14.为使能进一步了解本实用新型的特征及技术内容,请参阅以下有关本实用新型的详细说明与附图,然而所提供的附图仅用于提供参考与说明,并非用来对本实用新型加以限制。

附图说明

15.图1为本实用新型第一实施例所提供的多层式压敏电阻的制作方法的流程图。

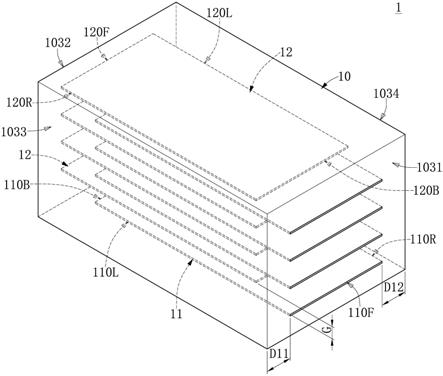

16.图2为本实用新型第二实施例所提供的多层式堆栈结构的其中一观看角度的立体示意图。

17.图3为本实用新型第二实施例所提供的多层式堆栈结构的另外一观看角度的立体示意图。

18.图4为本实用新型第二实施例所提供的多层式堆栈结构的剖面示意图。

19.图5为本实用新型第二实施例所提供的多层式压敏电阻的其中一观看角度的立体示意图。

20.图6为本实用新型第二实施例所提供的多层式压敏电阻的另外一观看角度的立体示意图。

21.图7为本实用新型第二实施例所提供的多层式压敏电阻的剖面示意图。

具体实施方式

22.以下是通过特定的具体实施例来说明本实用新型所公开有关“多层式压敏电阻”的实施方式,本领域技术人员可由本说明书所公开的内容了解本实用新型的优点与效果。本实用新型可通过其他不同的具体实施例加以实行或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本实用新型的构思下进行各种修改与变更。另外,本实用新型的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本实用新型的相关技术内容,但所公开的内容并非用以限制本实用新型的保护范围。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

23.[第一实施例]

[0024]

参阅图1至图7所示,本实用新型第一实施例提供一种多层式压敏电阻的制作方法,其包括:首先,如图1所示,提供一初始的多层式结构(步骤s100);接着,如图1所示,对初始的多层式结构进行烧结,以形成一经烧结的多层式结构(步骤s102);然后,配合图1以及图2至图4所示,将经烧结的多层式结构制作成一多层式堆栈结构1,多层式堆栈结构1包括一绝缘载体10、设置在绝缘载体10内的多个第一内导电层11以及设置在绝缘载体10内的多个第二内导电层12(步骤s104);接下来,配合图1以及图5至图7所示,形成一外电极结构2以部分地包覆多层式堆栈结构1,外电极结构2包括电性接触多个第一内导电层11的一第一外电极层21以及电性接触多个第二内导电层12的一第二外电极层22(步骤s106)。值得注意的

是,多个第一内导电层11与多个第二内导电层12交替排列(如图2至图4所示),并且第一外电极层21以及第二外电极层22分别包覆多层式堆栈结构1的一第一侧端部1001以及一第二侧端部1002(如图5至图7所示)。举例来说,初始的多层式结构可以是多层式压敏电阻生胚,其整体外形以及内部构造会与图2至图4所显示的多层式堆栈结构1近似。另外,经烧结的多层式结构可以是多层式压敏电阻熟胚,其整体外形以及内部构造会与图2至图4所显示的多层式堆栈结构1近似。然而,本实用新型不以上述所举的例子为限。

[0025]

进一步来说,如图1所示,将经烧结的多层式结构制作成多层式堆栈结构1的步骤s104还包括步骤(a)或者步骤(b)。其中,步骤(a)包括:首先,将经烧结的多层式结构浸泡在含有“0.1%~4.9%浓度的碱金属(lino3)”的一第一种溶液(金属离子溶液)中,浸泡时间介于30秒至120秒之间(步骤s1040(a));接着,将经烧结的多层式结构从第一种溶液中取出后进行烤干步骤,以形成一经烤干的多层式结构(步骤s1042(a));然后,在600℃~800℃的温度下,对经烤干的多层式结构进行金属离子扩散步骤(步骤s1044(a))。另外,步骤(b)包括:首先,将经烧结的多层式结构浸泡在包括含有“0.1%~4.9%浓度的含碱金属离子之混合树脂胶”的一第二种溶液(金属离子溶液)中(步骤s1040(b));接着,将经烧结的多层式结构从第二种溶液中取出后进行烤干步骤,以形成一经烤干的多层式结构(步骤s1042(b));然后,在600℃~800℃的温度下,对经烤干的多层式结构进行金属离子扩散步骤(步骤s1044(b))。

[0026]

举例来说,如图1所示,在对初始的多层式结构进行烧结的步骤s102之前,制作方法还包括:预先对初始的多层式结构进行加热(步骤s101)。另外,在预先对初始的多层式结构进行加热的步骤s101中,初始的多层式结构是在400℃~600℃的温度下进行加热。此外,在对初始的多层式结构进行烧结的步骤s102中,初始的多层式结构是在800℃~1000℃的温度下进行烧结。然而,本实用新型不以上述所举的例子为限。

[0027]

[第二实施例]

[0028]

参阅图2至图7所示,本实用新型第二实施例提供一种多层式压敏电阻v,多层式压敏电阻v是使用第一实施例所提供的制作方法所制成,并且多层式压敏电阻v包括一多层式堆栈结构1以及一外电极结构2。进一步来说,多层式堆栈结构1包括一绝缘载体10、设置在绝缘载体10内的多个第一内导电层11以及设置在绝缘载体10内的多个第二内导电层12,并且多个第一内导电层11与多个第二内导电层12交替排列。另外,外电极结构2包括电性接触多个第一内导电层11的一第一外电极层21以及电性接触多个第二内导电层12的一第二外电极层22,并且第一外电极层21以及第二外电极层22分别包覆多层式堆栈结构1的一第一侧端部1001以及一第二侧端部1002。

[0029]

进一步来说,配合图2至图4所示,绝缘载体10包括一绝缘上盖101、一绝缘下盖102以及连接于绝缘上盖101与绝缘下盖102之间的一绝缘本体103。另外,绝缘本体103的周围具有一第一外表面1031、一第二外表面1032、一第三外表面1033以及一第四外表面1034,并且多个第一内导电层11以及多个第二内导电层12交替排列在绝缘本体103内。

[0030]

进一步来说,配合图2与图4所示,每一第一内导电层11具有从绝缘本体103的第一外表面1031裸露的一第一前裸露端110f、面向绝缘本体103的第二外表面1032的一第一后内埋端110b、面向绝缘本体103的第三外表面1033的一第一左内埋端110l以及面向绝缘本体103的第四外表面1034的一第一右内埋端110r。再者,配合图2、图4、图5与图7所示,第一

前裸露端110f电性接触第一外电极层21,第一后内埋端110b相对应于第一前裸露端110f且被包覆在绝缘本体103内,第一左内埋端110l连接于第一前裸露端110f与第一后内埋端110b之间且被包覆在绝缘本体103内,并且第一右内埋端110r连接于第一前裸露端110f与第一后内埋端110b之间且被包覆在绝缘本体103内。

[0031]

进一步来说,配合图3与图4所示,第二内导电层12具有从绝缘本体103的第二外表面1032裸露的一第二前裸露端120f、面向绝缘本体103的第一外表面1031的一第二后内埋端120b、面向绝缘本体103的第四外表面1034的一第二左内埋端120l以及面向绝缘本体103的第三外表面1033的一第二右内埋端120r。再者,配合图3、图4、图6与图7所示,第二前裸露端120f电性接触第二外电极层22,第二后内埋端120b相对应于第二前裸露端120f且被包覆在绝缘本体103内,第二左内埋端120l连接于第二前裸露端120f与第二后内埋端120b之间且被包覆在绝缘本体103内,并且第二右内埋端120r连接于第二前裸露端120f与第二后内埋端120b之间且被包覆在绝缘本体103内。

[0032]

值得注意的是,配合图2至图4所示,绝缘载体10符合下列的条件:g与t1的比值为1:0.3~1.0,g与t2的比值为1:0.3~1.0,d11与g的比值为1:0.3~1.0,d12与g的比值为1:0.3~1.0,d21与g的比值为1:0.3~1.0,并且d22与g的比值为1:0.3~1.0。其中,如图4所示,t1为绝缘上盖101的厚度,t2为绝缘下盖102的厚度,并且g为彼此相邻的第一内导电层11与第二内导电层12之间的间距。如图2所示,d11为第一内导电层11的第一左内埋端110l与绝缘本体103的第三外表面1033之间的距离,并且d12为第一内导电层11的第一右内埋端110r与绝缘本体103的第四外表面1034之间的距离。如图3所示,d21为第二内导电层12的第二左内埋端120l与绝缘本体103的第四外表面1034之间的距离,并且d22为第二内导电层12的第二右内埋端120r与绝缘本体103的第三外表面1033之间的距离。

[0033]

请参考下列的表一,本实用新型以具有一预定的长(2.2

±

0.2mm)、宽(1.7

±

0.2mm)、厚(1.7

±

0.2mm)的绝缘载体10以及包括多个第一内导电层11与多个第二内导电层12的总层数采用8层来进行实验,其实验结果如下所示:

[0034]

表一

[0035]

[0036]

[实施例的有益效果]

[0037]

本实用新型的其中一有益效果在于,本实用新型所提供的一种多层式压敏电阻的制作方法,其能通过“将经烧结的多层式结构浸泡在含有0.1%~4.9%浓度的碱金属的一第一种溶液中,浸泡时间介于30秒至120秒之间;将经烧结的多层式结构从第一种溶液中取出后进行烤干步骤,以形成一经烤干的多层式结构;以及在600℃~800℃的温度下,对经烤干的多层式结构进行金属离子扩散步骤”或者“将经烧结的多层式结构浸泡在包括含有0.1%~4.9%浓度的含碱金属离子之混合树脂胶的一第二种溶液中;将经烧结的多层式结构从第二种溶液中取出后进行烤干步骤,以形成一经烤干的多层式结构;以及在600℃~800℃的温度下,对经烤干的多层式结构进行金属离子扩散步骤”的技术方案,以降低漏电流(leakage current)并且提升通流容量(即最大峰值电流值(maximum peak current))。

[0038]

本实用新型的另外一有益效果在于,本实用新型所提供的一种多层式压敏电阻v,其能通过“多层式堆栈结构1包括一绝缘载体10、设置在绝缘载体10内的多个第一内导电层11以及设置在绝缘载体10内的多个第二内导电层12,并且多个第一内导电层11与多个第二内导电层12交替排列”以及“外电极结构2包括电性接触多个第一内导电层11的一第一外电极层21以及电性接触多个第二内导电层12的一第二外电极层22,并且第一外电极层21以及第二外电极层22分别包覆多层式堆栈结构1的一第一侧端部1001以及一第二侧端部1002”的技术方案,以得到多层式压敏电阻v的产品。

[0039]

本实用新型的另外一有益效果在于,本实用新型所提供的一种多层式压敏电阻v,其能通过“g与t1的比值为1:0.3~1.0”、“g与t2的比值为1:0.3~1.0”、“d11与g的比值为1:0.3~1.0”、“d12与g的比值为1:0.3~1.0”、“d21与g的比值为1:0.3~1.0”以及“d22与g的比值为1:0.3~1.0”的技术方案,以降低漏电流(leakage current)并且提升通流容量(即最大峰值电流值(maximum peak current))。

[0040]

以上所公开的内容仅为本实用新型的优选可行实施例,并非因此局限本实用新型的权利要求书的保护范围,所以凡是运用本实用新型说明书及附图内容所做的等效技术变化,均包含于本实用新型的权利要求书的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1