一种用于集成电路八边形低寄生电容的MOS器件的制作方法

一种用于集成电路八边形低寄生电容的mos器件

技术领域

1.本实用新型涉及半导体器件技术领域,特别是涉及一种用于集成电路八边形低寄生电容的mos器件。

背景技术:

2.传统的mos管如图1所示,包含mos器件所在的阱,mos器件的栅极(g)、漏极(d)、源极(s)和衬底接触。传统的mos器件中s端的面积等于d端的面积,d端的寄生电容偏大,用作大功率的mos驱动管时,mos管的宽度会较大,为了不违反相关的闩锁效应规则,mos管不能只画成一个多finger的形式,需要多个mos多finger的面积,中间插入多条衬底,如图2所示,这样就会导致芯片的面积变大。

技术实现要素:

3.本实用新型所要解决的技术问题是,克服现有技术的缺点,提供一种用于集成电路八边形低寄生电容的mos器件。

4.为了解决以上技术问题,本实用新型的技术方案如下:

5.一种用于集成电路八边形低寄生电容的mos器件,包括,

6.衬底;

7.漏端,设置在所述衬底上;

8.源端,设置在所述衬底上,所述源端设置有若干个,均匀布设在所述漏端的四周,且所述源端与所述漏端之间的间距相等,相邻两个所述源端之间留有间隙;

9.栅极,设置在所述衬底上,且位于所述源端与所述漏端的间隙以及相邻所述源端之间的间隙内;以及,

10.衬底接触端,设置在所述源端内,且与所述衬底连接。

11.作为本实用新型所述用于集成电路八边形低寄生电容的mos器件的一种优选方案,其中:所述漏端的截面呈多边形,且任一内角均大于90

°

。

12.作为本实用新型所述用于集成电路八边形低寄生电容的mos器件的一种优选方案,其中:所述漏端的截面呈正八边形。

13.作为本实用新型所述用于集成电路八边形低寄生电容的mos器件的一种优选方案,其中:所述源端设置有四个,均匀布设在所述漏端的四周。

14.作为本实用新型所述用于集成电路八边形低寄生电容的mos器件的一种优选方案,其中:所述源端的截面均呈等腰梯形,且其上底朝向所述漏端。

15.本实用新型还公开了一种用作大功率的mos驱动器件,包括若干个上述任一方案所述的用于集成电路八边形低寄生电容的mos器件,若干个所述mos器件呈阵列式排列,若干个所述mos器件设置在同一衬底上,若干个所述mos器件的栅极互相连接,且相邻两个所述mos器件上相邻的所述源端互相连接。

16.本实用新型的有益效果是:

17.(1)本实用新型将源端设置在漏端的四周,将栅极设置在源端与漏端之间的间隙以及相邻源端之间的间隙内,并将衬底接触端设置在源端内,不用添加额外的衬底接触,极大地减少了mos器件的整体面积,也使mos器件各个点的背栅电阻更为均匀,同时,在保证mos器件的宽度和长度不变的情况下,可调节漏端与栅极的交叠面积,减少漏端的寄生电容。

18.(2)本实用新型中将漏端设置为正八边形,使漏端的内角大于90

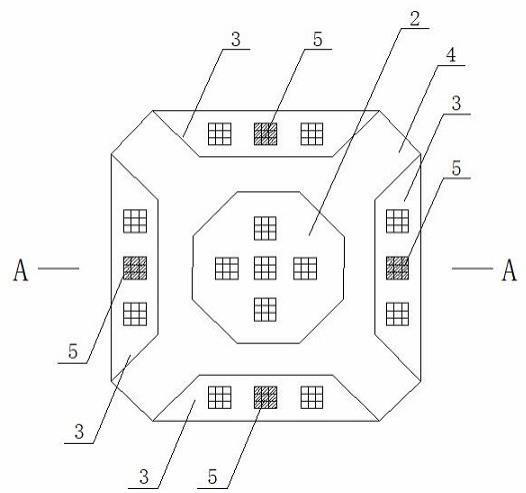

°

,避免产生尖角放电的现象。

19.(3)本实用新型中还可将若干个mos器件呈阵列式排列,用作大功率的mos驱动管,若干个mos器件中栅极自动连接在一起,相邻mos器件的源端也互相连接,不用另外添加衬底接触,极大地减少了芯片的面积。

附图说明

20.为了更清楚地说明本实用新型实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其它的附图。

21.图1为传统的mos管的结构示意图;

22.图2为传统的mos管用作大功率mos驱动管的结构示意图;

23.图3为第一个实施例提供的用于集成电路八边形低寄生电容的mos器件的结构示意图;

24.图4为图3中a-a的截面示意图;

25.图5为本实用新型提供的用作大功率的mos驱动器件的结构示意图;

26.图6为第二个实施例提供的用于集成电路八边形低寄生电容的mos器件的结构示意图;

27.图7为图6中b-b的截面示意图;

28.其中:1、衬底;2、漏端;3、源端;4、栅极;5、衬底接触端。

具体实施方式

29.为使本实用新型的内容更容易被清楚地理解,下面根据具体实施方式并结合附图,对本实用新型作出进一步详细的说明。

30.实施例1:

31.本实施例提供了一种用于集成电路八边形低寄生电容的mos器件,为nmos器件,包括p型衬底1,在p型衬底1上形成五个高掺杂的n+区,其中一个高掺杂的n+区为漏端2,其余四个高掺杂的n+区为源端3,分别均匀排布在漏端2的四周,如图1所示。在漏端2和源端3上引出的电极分别为漏极和源极。在p型衬底1的表面覆盖一层二氧化硅作为绝缘层,并在绝缘层上覆盖一层金属或多晶硅,其上引出的电极为栅极4。在本实施例中,栅极4位于漏端2与源端3之间的间隙以及相邻源端3之间的间隙内。

32.其中,漏端2的横截面呈多边形,且该多边形的任一内角均大于90

°

,这样可有效避免产生尖角放电的现象。在本实施例中,漏端2的横截面呈正八边形。

33.每个源端3的横截面均呈等腰梯形,四个源端3分别位于漏端2的前端、后端、左侧和右侧。每个源端3横截面的上底边均朝向漏端2,且与漏端2之间的间距均相等。相邻两个源端3之间均留有等宽的间隙。栅极4位于漏端2与源端3之间间隙以及相邻两个源端3之间的间隙内。源端3横截面的下底边与栅极4的边部围成八边形,如图1所示。

34.在每个源端3均设置有衬底接触端5,该衬底接触端5与p型衬底1连接。在衬底1接触端上引出的电极为衬底1电极。

35.上述的用于集成电路八边形低寄生电容的mos器件,中间为漏端2,漏端2四周为源端3,在漏端2与源端3之间的区域内为mos器件的栅极4,衬底1接触端设置在源端3内,不用添加额外的衬底接触,这样极大地减少了mos器件的整体面积,也让mos器件个点的背栅电阻更为均匀,同时,在保证mos器件的宽度和长度不变的情况下,可调节漏端2与栅极4之间的交叠面积,减少漏端2的寄生电容。

36.另外,本实施例还提供了一种用作大功率的mos驱动器件,包括若干个按照阵列式排布的上述mos器件,如图3所示。若干个mos器件设置在同一衬底1上,且相邻两个mos器件上相邻源端3互相连接,若干个mos器件的栅极4自动连接在一起,不用另外添加衬底接触,极大地减少了芯片的面积。

37.实施例2:

38.本实施例提供了一种用于集成电路八边形低寄生电容的mos器件,与实施例1的不同之处在于:本实施例中的mos器件为pmos器件,包括n型衬底1,在n型衬底1上形成五个高掺杂的p+区,其中一个高掺杂的p+区为漏端2,其余四个高掺杂的p+区为源端3,分别均匀排布在漏端2的四周,如图4所示。在漏端2和源端3上引出的电极分别为漏极和源极。在n型衬底1的表面覆盖一层二氧化硅作为绝缘层,并在绝缘层上覆盖一层金属或多晶硅,其上引出的电极为栅极4。在本实施例中,栅极4位于漏端2与源端3之间的间隙以及相邻源端3之间的间隙内。

39.本实施例中未进行说明的部分与实施例1中相同,在此不重复说明。

40.除上述实施例外,本实用新型还可以有其他实施方式;凡采用等同替换或等效变换形成的技术方案,均落在本实用新型要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1