半导体集成电路装置的制作方法

1.本公开涉及一种包括纳米片(纳米线)fet(field effect transistor,场效应晶体管)的半导体集成电路装置。

背景技术:

2.作为在半导体基板上形成半导体集成电路的方法,已知有标准单元方式。标准单元方式是指:通过事先将具有特定逻辑功能的基本单元(例如反相器、锁存器、触发器、全加器等)作为标准单元准备好,将多个标准单元布置在半导体基板上,用布线将这些标准单元连接起来,由此来设计lsi(大规模集成电路)芯片。

3.lsi的基本构成要素即晶体管通过缩小栅极长度(scaling:按比例缩小)而实现了集成度的提升、工作电压的降低以及工作速度的提升。然而,近年来,出现的问题是过度地按比例缩小会引起截止电流,截止电流又会引起功耗显著增大。为解决该问题,人们已开始积极对立体构造晶体管进行研究,即让晶体管构造从现有的平面型变为立体型。纳米片(纳米线)fet作为其中之一而备受瞩目。

4.在非专利文献1、2中,公开了使用将栅极电极设为叉形的纳米片fet的sram存储单元和标准单元的布局。

5.非专利文献1:p.weckx et al.,“stacked nanosheet fork architecture for sram design and device co-optimization toward 3nm”,2017 ieee internationa]electron devices meeting(iedm),december 2017,iedm17-505~508

6.非专利文献2:p.weckx et a1.,

″

novel forksheet device architecture as ultimate logic scaling device towards 2nm

″

,2019 ieee internationa]electron devices meeting(iedm),december 2019,iedm19-871~874

技术实现要素:

[0007]-发明要解决的技术问题-[0008]

在本说明书中,按照非专利文献1的记载,将栅极电极呈叉形的纳米片fet称为叉片(fork sheet)fet。

[0009]

近年来,半导体集成电路的微细化和高集成化的发展显著,相伴于此,工作电压的低电压化以及工作频率的高速化正在加速。然而,伴随着工作频率的高速化,噪声增加,并且,伴随着工作电压的低电压化,抗噪性降低,因此,就近年来的半导体集成电路而言,存在容易发生由噪声引起电路误动作的问题。作为防止由噪声引起电路误动作的方法,存在在电路的电源间设置去耦电容的方法。将形成有这样的去耦电容的单元称为电容单元。

[0010]

但是,迄今为止,还没有对采用了叉片fet的电容单元进行研究。

[0011]

本公开的目的在于提供一种电容单元的布局构造,该电容单元使用了叉片fet。

[0012]-用以解决技术问题的技术方案-[0013]

在本公开的第一方面为一种半导体集成电路装置,其包括作为电容单元的标准单

元,在所述半导体集成电路装置中,在所述标准单元中,形成有p型晶体管的p型区域和形成有n型晶体管的n型区域在第一方向上相邻地形成,所述标准单元包括:第一纳米片部、第二纳米片部、第一栅极布线、第一焊盘对、第二栅极布线、第二焊盘对,在所述p型区域,所述第一纳米片部由沿与所述第一方向垂直的第二方向延伸的一个纳米片或沿所述第一方向排列的两个以上的纳米片构成,在所述n型区域,所述第二纳米片部由沿所述第二方向延伸的一个纳米片或沿所述第一方向排列的两个以上的纳米片构成,所述第一栅极布线沿所述第一方向延伸,且以包围所述第一纳米片部所具有的纳米片的所述第一方向以及第三方向上的外周的方式形成,所述第三方向垂直于所述第一方向和所述第二方向,所述第一焊盘对分别与所述第一纳米片部所具有的纳米片的所述第二方向上的两个端部连接,所述第二栅极布线沿所述第一方向延伸,且以包围所述第二纳米片部所具有的纳米片的所述第一方向和所述第三方向上的外周的方式形成,所述第二焊盘对分别与所述第二纳米片部所具有的纳米片的所述第二方向上的两个端部连接,所述第一焊盘对和所述第二栅极布线被供给第一电源电压,所述第二焊盘对和所述第一栅极布线被供给比所述第一电源电压低的第二电源电压,所述第一纳米片部与所述第二纳米片部在所述第一方向上对置,并且,所述第一纳米片部所具有的纳米片中的最接近所述第二纳米片部的纳米片的所述第一方向上的靠所述第二纳米片部侧的面从所述第一栅极布线露出,所述第二纳米片部所具有的纳米片中的最接近所述第一纳米片部的纳米片的所述第一方向上的靠所述第一纳米片部侧的面从所述第二栅极布线露出。

[0014]

根据该方面,由于第一焊盘对和第二栅极布线被供给第一电源电压,第二焊盘对和第一栅极布线被供给第二电源电压,因此在第一纳米片部与第一栅极布线之间、以及第二纳米片部与第二栅极布线之间产生电容。此外,在第一栅极布线与第二栅极布线之间、以及第一焊盘对与第二焊盘对之间也产生电容。并且,第一纳米片部所具有的纳米片中最接近第二纳米片部的纳米片的靠第二纳米片部侧的面从第一栅极布线露出,第二纳米片部所具有的纳米片中最接近第一纳米片部的纳米片的靠第一纳米片侧的面从第二栅极布线露出。由此,能够缩小第一纳米片部与第二纳米片部之间的间隔,因此能够进一步减小电容单元的面积。能够在第一栅极布线与第二栅极布线之间、以及第一焊盘对与第二焊盘对之间实现更大的电容。

[0015]

在本公开的第二方面为一种半导体集成电路装置,其包括作为电容单元的标准单元,在所述半导体集成电路装置中,在所述标准单元中,形成有第一导电型晶体管的第一区域和形成有第二导电型晶体管的第二区域在第一方向上相邻地形成,所述标准单元包括:第一纳米片部、第二纳米片部、第一栅极布线、第一焊盘对、第二栅极布线、第二焊盘对,在所述第一区域,所述第一纳米片部由沿与所述第一方向垂直的第二方向延伸的一个纳米片或沿所述第一方向排列的两个以上的纳米片构成,在所述第二区域,所述第二纳米片部由沿所述第二方向延伸的一个纳米片或沿所述第一方向排列的两个以上的纳米片构成,所述第一栅极布线沿所述第一方向延伸,且以包围所述第一纳米片部所具有的纳米片的所述第一方向以及第三方向上的外周的方式形成,所述第三方向垂直于所述第一方向和所述第二方向,所述第一焊盘对分别与所述第一纳米片部所具有的纳米片的所述第二方向上的两个端部连接,所述第二栅极布线沿所述第一方向延伸,且以包围所述第二纳米片部所具有的纳米片的所述第一方向和所述第三方向上的外周的方式形成,所述第二焊盘对分别与所述

第二纳米片部所具有的纳米片的所述第二方向上的两个端部连接,所述第一栅极布线和所述第二栅极布线被供给第一电源电压,所述第一焊盘对和所述第二焊盘对被供给与所述第一电源电压不同的第二电源电压,所述第一纳米片部与所述第二纳米片部在所述第一方向上对置,并且,所述第一纳米片部所具有的纳米片中的最接近所述第二纳米片部的纳米片的所述第一方向上的靠所述第二纳米片部侧的面从所述第一栅极布线露出,所述第二纳米片部所具有的纳米片中的最接近所述第一纳米片部的纳米片的所述第一方向上的靠所述第一纳米片部侧的面从所述第二栅极布线露出。

[0016]

根据该方面,由于第一栅极布线和第二栅极布线被供给第一电源电压,第一焊盘对和第二焊盘对被供给第二电源电压,因此在第一纳米片部与第一栅极布线之间、或者第二纳米片部与第二栅极布线之间产生电容。并且,第一纳米片部所具有的纳米片中最接近第二纳米片部的纳米片的靠第二纳米片部侧的面从第一栅极布线露出,第二纳米片部所具有的纳米片中最接近第一纳米片部的纳米片的靠第一纳米片部侧的面从第二栅极布线露出。由此,能够缩小第一纳米片部与第二纳米片部之间的间隔,因此能够进一步减小电容单元的面积。

[0017]-发明的效果-[0018]

根据本公开,能够实现一种使用了叉片fet的大容量电容单元的布局构造。

附图说明

[0019]

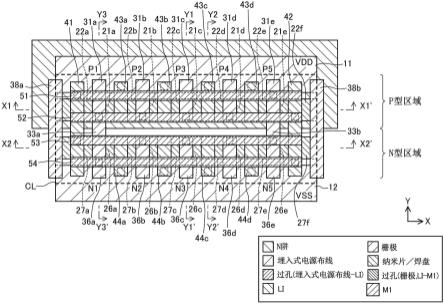

图1是俯视图,其示出第一实施方式所涉及的电容单元的布局构造的例子;

[0020]

图2的(a)、(b)是图1的布局构造的俯视时沿横向剖开的剖视图;

[0021]

图3的(a)~(c)是图1的布局构造的俯视时沿纵向剖开的剖视图;

[0022]

图4是图1~图3所示的电容单元的电路图;

[0023]

图5的(a)、(b)是剖视图,示出第一实施方式的变形例所涉及的电容单元的布局构造;

[0024]

图6是俯视图,其示出第二实施方式所涉及的电容单元的布局构造的例子;

[0025]

图7的(a)、(b)是图6的布局构造的俯视时沿纵向剖开的剖视图;

[0026]

图8是图6和图7所示的电容单元的电路图;

[0027]

图9是俯视图,其示出第二实施方式的变形例1所涉及的电容单元的布局构造;

[0028]

图10是图9所示的电容单元的电路图;

[0029]

图11是俯视图,其示出第二实施方式的变形例2所涉及的电容单元的布局构造;

[0030]

图12是图11所示的电容单元的电路图;

[0031]

图13是示出叉片fet的基本构造的图,(a)是俯视图,(b)是剖视图。

具体实施方式

[0032]

以下,参照附图对实施方式做详细的说明。在以下实施方式中,半导体集成电路装置包括多个标准单元(在本说明书中,有时简称为单元),上述多个标准单元中至少一部分标准单元包括纳米片fet(field effect transistor)。纳米片fet是使用了供电流流动的薄片(纳米片)而形成的fet。纳米片例如由硅形成。在半导体集成电路装置中,纳米片fet的一部分是栅极电极呈叉形的叉片fet。

[0033]

在本公开中,将形成在纳米片的两端且构成成为纳米片fet的源极或漏极的端子的半导体层部称为“焊盘”。

[0034]

首先,对叉片fet的基本构造进行说明。

[0035]

图13是示出叉片fet的基本构造的图,(a)是俯视图,(b)是沿(a)中的线y-y’剖开的剖视图。在图13的基本构造中,两个晶体管tr1、tr2在y方向上隔开间隔s地排列着布置。成为晶体管tr1的栅极的栅极布线531和成为晶体管tr2的栅极的栅极布线532都沿y方向延伸,并且在x方向上布置在相同的位置处。

[0036]

成为晶体管tr1的沟道区域的沟道部521和成为晶体管tr2的沟道区域的沟道部526由纳米片构成。在图13中,沟道部521、526分别由纳米片构成,该纳米片由俯视时重叠的三张片状构造形成。在沟道部521的x方向上的两侧形成有成为晶体管tr1的源极区域或漏极区域的焊盘522a、522b。在沟道部526的x方向上的两侧形成有成为晶体管tr2的源极区域或漏极区域的焊盘527a、527b。焊盘522a、522b是构成沟道部521的纳米片进行外延生长而形成的。焊盘527a、527b是构成沟道部526的纳米片进行外延生长而形成的。

[0037]

栅极布线531隔着栅极绝缘膜(未图示)包围由纳米片构成的沟道部521的在y方向及z方向上的外周。不过,构成沟道部521的纳米片的在y方向上的靠晶体管tr2侧的面未被栅极布线531覆盖,而是从栅极布线531露出。也就是说,在图13的(b)的剖视图中,栅极布线531未覆盖构成沟道部521的纳米片的附图中的右侧,而是覆盖附图中的上侧、左侧以及下侧。栅极布线531相对于构成沟道部521的纳米片,向y方向上的与晶体管tr2相反的一侧伸出,伸出的量为长度ol。

[0038]

栅极布线532隔着栅极绝缘膜(未图示)包围由纳米片构成的沟道部526的在y方向及z方向上的外周。不过,构成沟道部526的纳米片的在y方向上的靠晶体管tr1侧的面未被栅极布线532覆盖,而是从栅极布线532露出。也就是说,在图13的(b)的剖视图中,栅极布线532未覆盖构成沟道部526的纳米片的附图中的左侧,而是覆盖附图中的上侧、右侧以及下侧。栅极布线532相对于构成沟道部526的纳米片,向y方向上的与晶体管tr1相反的一侧伸出,伸出的量为长度ol。

[0039]

如果将各纳米片的宽度(y方向上的尺寸)设为w、高度(z方向上的尺寸)设为h,栅极有效宽度weff则为:weff=2

×

w+h。

[0040]

由于晶体管tr1的沟道部521、晶体管tr2的沟道部526均由三张纳米片构成,因此晶体管tr1、tr2的栅极有效宽度为:3

×

(2

×

w+h)。

[0041]

根据图13的结构,栅极布线531相对于构成沟道部521的纳米片,没有向y方向上的晶体管tr2侧伸出。栅极布线532相对于构成沟道部526的纳米片,没有向y方向上的晶体管tr1侧伸出。这样一来,就能够使晶体管tr1、tr2更接近,从而能够实现小面积化。

[0042]

需要说明的是,构成晶体管的沟道部的纳米片的张数不限于三张。也就是说,纳米片可以由一张片状构造形成,也可以由俯视时重叠的多张片状构造形成。在图13的(b)中,示出纳米片的剖面形状为长方形,但不限于此,纳米片的剖面形状例如也可以是正方形、圆形、椭圆形等。

[0043]

叉片fet和纳米片fet可以混着存在于半导体集成电路装置内,该纳米片fet的纳米片的整个周围被栅极布线包围。

[0044]

在本说明书中,“vdd”和“vss”是指电源电压或电源本身。在本说明书中,像“同一

布线宽度”等意为宽度等相等的表述包含制造上的偏差范围。

[0045]

(第一实施方式)

[0046]

图1~图3是示出第一实施方式所涉及的电容单元的布局构造的例子的图,图1是俯视图,图2的(a)、(b)是俯视时沿横向剖开的剖视图,图3的(a)~(c)是俯视时沿纵向剖开的剖视图。图2的(a)是沿线x1-x1’剖开的剖面,图2的(b)是沿线x2-x2’剖开的剖面。图3的(a)是沿线y1一y1’剖开的剖面,图3的(b)是沿线y2-y2’剖开的剖面,图3的(c)是沿线y3-y3’剖开的剖面。

[0047]

需要说明的是,在以下说明中,在图1等俯视图中,将附图中的横向设为x方向(相当于第二方向),将附图中的纵向设为y方向(相当于第一方向),将垂直于基板面的方向设为z方向(相当于第三方向)。

[0048]

图4是图1~图3所示的电容单元的电路图。如图4所示,图1~图3所示的电容单元具有p型晶体管p1、p2、p3、p4、p5以及n型晶体管n1、n2、n3、n4、n5。晶体管p2~p4以及晶体管n2~n4作为电容元件发挥功能。晶体管p1和晶体管n5构成固定值输出部5。固定值输出部5向节点x1输出低固定值(vss),向节点x2输出高固定值(vdd)。晶体管p1的源极与vdd连接,漏极与晶体管n5的栅极连接,栅极与晶体管n5的漏极连接。晶体管n5的源极与vss连接,漏极与晶体管p1的栅极连接。晶体管p1的栅极相当于节点x1,晶体管n5的栅极相当于节点x2。

[0049]

需要说明的是,晶体管p5和晶体管n1为截止状态的晶体管。作为电容单元的电路结构,也可以没有晶体管p5和晶体管n1,但如果有晶体管p5和晶体管n1,则电容单元的布局的规则性提升,因此装置的制造容易度提升,成品率提升,制造偏差得到抑制。

[0050]

晶体管p2~p4的源极和漏极与vdd连接,栅极与节点x1连接。由于vss从固定值输出部5输出到节点x1,所以晶体管p2~p4作为电容元件发挥功能。晶体管n2~n4的源极和漏极与vss连接,栅极与节点x2连接。由于vdd从固定值输出部5输出到节点x2,所以晶体管n2~n4作为电容元件发挥功能。

[0051]

图1~图3的电容单元与其他标准单元以单元框cl相邻的方式沿x方向排列布置,从而构成单元列。多个单元列以单元框cl相邻的方式沿y方向排列布置。多个单元列中的每一列相比前一列上下反转。

[0052]

如图1所示,在电容单元的y方向上的两端,分别设有沿x方向延伸的电源布线11、12。电源布线11、12均为形成于埋入式布线层的埋入式电源布线(bpr:buried power rail)。电源布线11供给电源电压vdd,电源布线12供给电源电压vss。电源布线11、12在包括电容单元的单元列中被与其他单元所共有,成为沿x方向延伸的电源布线。电源布线11、12构成被布置于在y方向上相邻的单元列彼此之间的电源布线。

[0053]

在n阱上的p型区域形成有p型晶体管p1、p2、p3、p4、p5。在p型基板上的n型区域形成有n型晶体管n1、n2、n3、n4、n5。p型区域和n型区域在y方向上相邻地形成。在x方向上,晶体管p1、p2、p3、p4、p5的布置位置分别与晶体管n1、n2、n3、n4、n5的布置位置相同。即,晶体管p1、n1在y方向上排成一列。晶体管p2、n2在y方向上排成一列。晶体管p3、n3在y方向上排成一列。晶体管p4、n4在y方向上排成一列。晶体管p5、n5在y方向上排成一列。

[0054]

晶体管p1、p2、p3、p4、p5分别具有由俯视时重叠的三张片状构造形成的纳米片21a、21b、21c、21d、21e作为沟道部。也就是说,晶体管p1、p2、p3、p4、p5为纳米片fet。

[0055]

如图1所示,在纳米片21a的附图中左侧形成有焊盘22a、在纳米片21a和纳米片21b

之间形成有焊盘22b、在纳米片21b和纳米片21c之间形成有焊盘22c、在纳米片21c和纳米片21d之间形成有焊盘22d、在纳米片21d和纳米片21e之间形成有焊盘22e以及在纳米片21e的附图中右侧形成有焊盘22f,上述焊盘22a、22b、22c、22d、22e、22f由与三张片状构造连接的一体构造的半导体层形成。焊盘22a、22b成为晶体管p1的源极区域和漏极区域。焊盘22b、22c成为晶体管p2的源极区域和漏极区域。焊盘22c、22d成为晶体管p3的源极区域和漏极区域。焊盘22d、22e成为晶体管p4的源极区域和漏极区域。焊盘22e、22f成为晶体管p5的源极区域和漏极区域。

[0056]

晶体管n1、n2、n3、n4、n5分别具有由俯视时重叠的三张片状构造形成的纳米片26a、26b、26c、26d、26e作为沟道部。也就是说,晶体管n1、n2、n3、n4、n5为纳米片fet。

[0057]

如图1所示,在纳米片26a的附图中左侧形成有焊盘27a、在纳米片26a和纳米片26b之间形成有焊盘27b、在纳米片26b和纳米片26c之间形成有焊盘27c、在纳米片26c和纳米片26d之间形成有焊盘27d、在纳米片26d和纳米片26e之间形成有焊盘27e以及在纳米片26e的附图中右侧形成有焊盘27f,上述焊盘27a、27b、27c、27d、27e、27f由与三张片状构造连接的一体构造的半导体层形成。焊盘27a、27b成为晶体管n1的源极区域和漏极区域。焊盘27b、27c成为晶体管n2的源极区域和漏极区域。焊盘27c、27d成为晶体管n3的源极区域和漏极区域。焊盘27d、27e成为晶体管n4的源极区域和漏极区域。焊盘27e、27f成为晶体管n5的源极区域和漏极区域。

[0058]

在p型区域形成有沿y方向并列延伸的栅极布线31a、31b、31c、31d、31e。栅极布线31a、31b、31c、31d、31e以相等的宽度形成,且以相等的间距布置。在n型区域形成有沿y方向并列延伸的栅极布线36a、36b、36c、36d、36e。栅极布线36a、36b、36c、36d、36e以相等的宽度形成,且以相等的间距布置。在x方向上,栅极布线31a、31b、31c、31d、31e的布置位置分别与栅极布线36a、36b、36c、36d、36e的布置位置相同。即,栅极布线31a、36a在y方向上排成一列。栅极布线31b、36b在y方向上排成一列。栅极布线31c、36c在y方向上排成一列。栅极布线31d、36d在y方向上排成一列。栅极布线31e、36e在y方向上排成一列。在x方向的两侧的单元框cl上形成有虚设栅极布线38a、38b。

[0059]

栅极布线31a隔着栅极绝缘膜(未图示)包围晶体管p1的纳米片21a的在y方向和z方向上的外周。栅极布线31a成为晶体管p1的栅极。同样地,栅极布线31b、31c、31d、31e分别隔着栅极绝缘膜(未图示)包围晶体管p2、p3、p4、p5的纳米片21b、21c、21d、21e的在y方向和z方向上的外周。栅极布线31b、31c、31d、31e分别成为晶体管p2、p3、p4、p5的栅极。

[0060]

栅极布线36a隔着栅极绝缘膜(未图示)包围晶体管n1的纳米片26a的在y方向和z方向上的外周。栅极布线36a成为晶体管n1的栅极。同样地,栅极布线36b、36c、36d、36e分别隔着栅极绝缘膜(未图示)包围晶体管n2、n3、n4、n5的纳米片26b、26c、26d、26e的在y方向和z方向上的外周。栅极布线36b、36c、36d、36e分别成为晶体管n2、n3、n4、n5的栅极。

[0061]

在y方向上排列的栅极布线31a、栅极布线36a经由形成在栅极布线31a与栅极布线36a之间的桥部33a连接。在y方向上排列的栅极布线31e、栅极布线36e经由形成在栅极布线31e与栅极布线36e之间的桥部33b连接。

[0062]

在局部布线层形成有沿y方向延伸的局部布线41、42、43a、43b、43c、43d、44a、44b、44c、44d。局部布线41与焊盘22a、27a相连接。局部布线42与焊盘22f、27f相连接。局部布线43a、43b、43c、43d分别与焊盘22b、22c、22d、22e连接,并且经由过孔(via)与电源布线11连

接。局部布线44a、44b、44c、44d分别与焊盘27b、27c、27d、27e连接,并且经由过孔与电源布线12连接。

[0063]

在m1布线层中,形成有沿x方向延伸的金属布线51、52、53、54。金属布线52、金属布线54对应于电路的节点x1,金属布线51、金属布线53对应于电路的节点x2。金属布线51经由过孔与栅极布线31c连接,并且经由过孔与局部布线41连接。金属布线52经由过孔与栅极布线31a、31b、31c、31d连接,并且经由过孔与局部布线42连接。金属布线53经由过孔与栅极布线36b、36c、36d、36e连接,并且经由过孔与局部布线41连接。金属布线54与栅极布线36a连接,并且金属布线54经由过孔与局部布线42连接。金属布线51、52、53、54形成布线间电容。

[0064]

此处,纳米片21a和纳米片26a在y方向上对置。纳米片21a的y方向上的靠纳米片26a侧的面未被栅极布线31a覆盖,而是从栅极布线31a露出。纳米片26a的y方向上的靠纳米片21a侧的面未被栅极布线36a覆盖,而是从栅极布线36a露出。

[0065]

同样地,纳米片21b与纳米片26b在y方向上对置,纳米片21c与纳米片26c在y方向上对置,纳米片21d与纳米片26d在y方向上对置,纳米片21e与纳米片26e在y方向上对置。纳米片21b、21c、21d、21e各自的y方向上的靠纳米片26b、26c、26d、26e侧的面未被栅极布线31b、31c、31d、31e覆盖,而是从栅极布线31b、31c、31d、31e露出。纳米片26b、26c、26d、26e的y方向上的靠纳米片21b、21c、21d、21e侧的面未被栅极布线36b、36c、36d、36e覆盖,而是从栅极布线36b、36c、36d、36e露出。

[0066]

此处,着眼于作为电容元件发挥功能的晶体管p3。在晶体管p3中,vss从节点x1被供向成为栅极的栅极布线31c,vdd经由局部布线43b、43c被供向成为源极/漏极的焊盘22c、22d。因此,产生夹着晶体管p3的栅极氧化膜的电容。除此之外,还在如下的部位产生电容。

[0067]

1)焊盘22c、22d与栅极布线31c之间(参照图2的(a))

[0068]

2)局部布线43b、43c与栅极布线31c之间(参照图2的(a))

[0069]

3)栅极布线31c与晶体管n3的栅极布线36c之间(参照图3的(a))。从节点x2向栅极布线36c供给vdd。

[0070]

4)焊盘22c、22d与晶体管n3的焊盘27c、27d之间(参照图3的(b))。经由局部布线44b、44c向焊盘27c、27d供给vss。

[0071]

5)局部布线43b、43c与栅极布线44b、44之间(参照图3的(b))。

[0072]

而且,在本实施方式中,晶体管p3的纳米片21c的靠晶体管n3的纳米片26c侧的面未被栅极布线31c覆盖,并且,晶体管n3的纳米片26c的靠晶体管p3的纳米片21c侧的面未被栅极布线36c覆盖。由此,晶体管p3和晶体管n3的距离缩短。因此,上述3)、4)的电容变得更大。

[0073]

如上所述,根据本实施方式,对于晶体管p2、p3、p4,在纳米片21b、21c、21d与栅极布线31b、31c、31d之间产生电容。对于晶体管n2、n3、n4,在纳米片26b、26c、26d与栅极布线36b、36c、36d之间产生电容。并且,纳米片21b、21c、21d的靠纳米片26b、26c、26d侧的面从栅极布线31b、31c、31d露出,纳米片26b、26c、26d的靠纳米片21b、21c、21d侧的面从栅极布线36b、36c、36d露出。由此,能够使纳米片21b、21c、21d与纳米片26b、26c、26d之间的间隔变窄,因此能够进一步减小电容单元的面积。此外,例如在晶体管p3、n3中,在栅极布线31c与栅极布线36c之间、以及焊盘对22c、22d与焊盘对27c、27d之间也能够实现更大的电容。

[0074]

需要说明的是,在上述实施方式中,也可以省略固定值输出部。在这种情况下,例

如只要将电容单元构成为向晶体管p2、p3、p4的栅极直接供给vss、并且向晶体管n2、n3、n4的栅极直接供给vdd即可。

[0075]

在上述实施方式中,作为构成电容的晶体管,分别设了三个p型晶体管和三个n型晶体管,但是构成电容的晶体管的数量不限于此。

[0076]

(变形例)

[0077]

在上述的实施方式中,在各晶体管中,在y方向上各布置有一个纳米片,但也可以在y方向上布置有两个以上的纳米片。在该情况下,只要在p型区域和n型区域的边界部分,对置的纳米片从栅极布线露出即可。即,在将p型晶体管所具有的纳米片作为第一纳米片部,将n型晶体管所具有的纳米片作为第二纳米片部时,第一纳米片部所具有的纳米片中最接近第二纳米片部的纳米片的y方向上的靠第二纳米片部侧的面从栅极布线露出,第二纳米片部所具有的纳米片中最接近第一纳米片部的纳米片的y方向上的靠第一纳米片侧的面从栅极布线露出即可。由此,能够得到与上述实施方式同样的作用和效果。

[0078]

图5的(a)、(b)是表示本变形例的构造的俯视时沿纵向剖开的剖视图。在图5的构造中,晶体管p3具有沿y方向排列的两个纳米片21c、23c,晶体管n3具有沿y方向排列的两个纳米片26c、28c。在纳米片21c、23c、26c、28c的x方向上的一侧分别形成有焊盘24d、22d、27d、29d。

[0079]

纳米片21c的y方向上的靠纳米片26a侧的面未被栅极布线31c覆盖,而是从栅极布线31c露出。纳米片26a的y方向上的靠纳米片21c侧的面未被栅极布线36c覆盖,而是从栅极布线36c露出。

[0080]

即,在将纳米片21c、23c作为第一纳米片部24,将纳米片26c、28c作为第二纳米片部25时,第一纳米片部24所具有的纳米片中最接近第二纳米片部25的纳米片21c的y方向上的靠第二纳米片部25侧的面从栅极布线31c露出,第二纳米片部25所具有的纳米片中最接近第一纳米片部24的纳米片26c的靠y方向上的第一纳米片部24侧的面从栅极布线36c露出。

[0081]

(第二实施方式)

[0082]

图6和图7是示出第二实施方式所涉及的电容单元的布局构造的例子的图,图6是俯视图,图7是俯视时沿纵向剖开的剖视图。图7的(a)是沿线y4一y4’剖开的剖面,图7的(b)是沿线y5-y5’剖开的剖面。需要说明的是,图6和图7所示的布局构造与图1~图3所示的布局构造类似,例如电源布线、以及晶体管的纳米片和焊盘的布置相同。在以下的说明中,对与第一实施方式相同的构成,有时省略说明。

[0083]

图8是图6和图7所示的电容单元的电路图。如图8所示,图6和图7所示的单元具有p型晶体管p1、p2、p3、p4、p5以及n型晶体管n1、n2、n3、n4、n5。晶体管n2~n4作为电容元件发挥功能。晶体管p5和晶体管n1构成固定值输出部5。固定值输出部5向节点x1输出高固定值(vdd),向节点x2输出低固定值(vss)。晶体管p5的源极与vdd连接,漏极与晶体管n1的栅极连接,栅极与晶体管n1的漏极连接。晶体管n1的源极与vss连接,漏极与晶体管p5的栅极连接。晶体管n1的栅极相当于节点x1,晶体管p5的栅极相当于节点x2。

[0084]

需要说明的是,晶体管p1~p4和晶体管n5为截止状态的晶体管。作为电容单元的电路结构,也可以没有晶体管p1~p4和晶体管n5,但如果有晶体管p1~p4和晶体管n5,则电容单元的布局的规则性提升,因此装置的制造容易度提升,成品率提升,制造偏差得到抑

制。

[0085]

晶体管n2~n4的源极和漏极与vss连接,栅极与节点x1连接。由于vdd从固定值输出部5输出到节点x1,所以晶体管n2~n4作为电容元件发挥功能。

[0086]

如图6和图7所示,在p型区域形成有沿y方向并列延伸的栅极布线131a、131b、131c、131d、131e。栅极布线131a、131b、131c、131d、131e以相等的宽度形成,且以相等的间距布置。在n型区域形成有沿y方向并列延伸的栅极布线136a、136b、136c、136d、136e。栅极布线136a、136b、136c、136d、136e以相等的宽度形成,且以相等的间距布置。在x方向上,栅极布线131a、131b、131c、131d、131e的布置位置分别与栅极布线136a、136b、136c、136d、136e的布置位置相同。即,栅极布线131a、136a在y方向上排成一列。栅极布线131b、136b在y方向上排成一列。栅极布线131c、136c在y方向上排成一列。栅极布线131d、136d在y方向上排成一列。栅极布线131e、136e在y方向上排成一列。

[0087]

栅极布线131a隔着栅极绝缘膜(未图示)包围晶体管p1的纳米片21a的在y方向和z方向上的外周。栅极布线131a成为晶体管p1的栅极。同样地,栅极布线131b、131c、131d、131e隔着栅极绝缘膜(未图示)分别包围晶体管p2、p3、p4、p5的纳米片21b、21c、21d、21e的在y方向和z方向上的外周。栅极布线131b、131c、131d、131e分别成为晶体管p2、p3、p4、p5的栅极。

[0088]

栅极布线136a隔着栅极绝缘膜(未图示)包围晶体管n1的纳米片26a的在y方向和z方向上的外周。栅极布线136a成为晶体管n1的栅极。同样地,栅极布线136b、136c、136d、136e隔着栅极绝缘膜(未图示)分别包围晶体管n2、n3、n4、n5的纳米片26b、26c、26d、26e的在y方向和z方向上的外周。栅极布线136b、136c、136d、136e分别成为晶体管n2、n3、n4、n5的栅极。

[0089]

在y方向上排列的栅极布线131a和栅极布线136a经由形成在栅极布线131a与栅极布线136a之间的桥部133a连接。在y方向上排列的栅极布线131b和栅极布线136b经由形成在栅极布线131b与栅极布线136b之间的桥部133b连接。在y方向上排列的栅极布线131c和栅极布线136c经由形成在栅极布线131c与栅极布线136c之间的桥部133c连接。在y方向上排列的栅极布线131d和栅极布线136d经由形成在栅极布线131d与栅极布线136d之间的桥部133d连接。在y方向上排列的栅极布线131e和栅极布线136e经由形成在栅极布线131e与栅极布线136e之间的桥部133e连接。

[0090]

在局部布线层形成有沿y方向延伸的局部布线141、142、143、144、145、146、147、148。局部布线141与焊盘22a、27a连接。局部布线142与焊盘22b、27b连接,并且局部布线142经由过孔与电源布线12连接。局部布线143与焊盘22c、27c连接,并且局部布线143经由过孔与电源布线12连接。局部布线144与焊盘22d、27d连接,并且局部布线144经由过孔与电源布线12连接。局部布线145与焊盘22e连接。局部布线146与焊盘22f连接,并且局部布线146经由过孔与电源布线11连接。局部布线147与焊盘27e连接,并且局部布线147与电源布线12连接。局部布线148与焊盘27f连接。

[0091]

在m1布线层,形成有沿x方向延伸的金属布线151、152、153、154。金属布线152、154对应于电路的节点x1,金属布线151、153对应于电路的节点x2。金属布线151经由过孔与栅极布线131e连接,并且金属布线151经由过孔与局部布线141连接。金属布线152经由过孔与栅极布线131a、131b、131c、131d连接,并且金属布线152经由过孔与局部布线145连接。金属

布线153经由过孔与栅极布线136e连接,并且金属布线153经由过孔与局部布线141连接。金属布线154经由过孔与栅极布线136a、136b、136c、136d连接,并且金属布线154经由过孔与局部布线148连接。

[0092]

此处,与第一实施方式同样地,纳米片21a和纳米片26a在y方向上对置。纳米片21a的y方向上的靠纳米片26a侧的面未被栅极布线131a覆盖,而是从栅极布线131a露出。纳米片26a的y方向上的靠纳米片21a侧的面未被栅极布线136a覆盖,而是从栅极布线136a露出。

[0093]

同样地,纳米片21b和纳米片26b在y方向上对置。纳米片21c和纳米片26c在y方向上对置。纳米片21d和纳米片26d在y方向上对置。纳米片21e和纳米片26e在y方向上对置。纳米片21b、21c、21d、21e各自的y方向上的靠纳米片26b、26c、26d、26e侧的面未被栅极布线131b、131c、131d、131e覆盖,而是从栅极布线131b、131c、131d、131e露出。纳米片26b、26c、26d、26e的y方向上的靠纳米片21b、21c、21d、21e侧的面未被栅极布线136b、136c、136d、136e覆盖,而是从栅极布线136b、136c、136d、136e露出。

[0094]

从p型区域至n型区域,形成有被供给vdd的栅极布线和被供给vss的局部布线,在该栅极布线和局部布线之间形成电容。例如,若着眼于晶体管p3、n3,则栅极布线131c、136c通过桥部133c连接,并且经由金属布线152向栅极布线131c、136c供给vdd。从电源布线12向局部布线143、144供给vss。因此,在栅极布线131c、136c以及桥部133c与局部布线143、144之间形成电容。

[0095]

如上所述,根据本实施方式,对于晶体管n2、n3、n4,在纳米片26b、26c、26d与栅极布线136b、136c、136d之间产生电容。并且,纳米片21b、21c、21d的靠纳米片26b、26c、26d侧的面从栅极布线131b、131c、131d露出,纳米片26b、26c、26d的靠纳米片21b、21c、21d侧的面从栅极布线136b、136c、136d露出。由此,能够使纳米片21b、21c、21d与纳米片26b、26c、26d之间的间隔变窄,因此能够进一步减小电容单元的面积。此外,例如在晶体管p3、n3中,能够在栅极布线131c、栅极布线136c以及桥部133c与局部布线143、局部布线144之间实现大的电容。

[0096]

需要说明的是,在上述实施方式中,也可以省略固定值输出部。在该情况下,例如只要将电容单元构成为向晶体管n2、n3、n4的栅极直接供给vdd即可。

[0097]

在上述实施方式中,作为构成电容的晶体管,设了三个n型晶体管,但是构成电容的晶体管的数量不限于此。

[0098]

与第一实施方式的变形例同样地,在各晶体管中,纳米片也可以在y方向上布置有两个以上。

[0099]

(变形例1)

[0100]

也可以替换晶体管的导电型而构成上述实施方式所涉及的电容单元。

[0101]

图9是俯视图,其示出第二实施方式的变形例1所涉及的电容单元的布局构造。图9所示的布局构造相当于将图6中的布局构造上下翻转,将p型和n型互换,并且将vdd和vss互换的布局构造。在图9的布局构造中,电源布线、晶体管、栅极布线、局部布线以及m1布线的布置方式与图6的布局构造相同。不过,与图6中的布局构造不同之处在于:m1布线与局部布线以及栅极布线之间的连接关系、以及局部布线与电源布线之间的连接关系。

[0102]

图10是图9所示的电容单元的电路图。图10中的电路相当于将图8中的电路上下翻转,将p型和n型互换,并且将vdd和vss互换的电路。

[0103]

如图10所示,图9所示的单元具有p型晶体管p1、p2、p3、p4、p5以及n型晶体管n1、n2、n3、n4、n5。晶体管p2~p4作为电容元件发挥功能。晶体管p1和晶体管n5构成固定值输出部5。固定值输出部5向节点x1输出低固定值(vss),向节点x2输出高固定值(vdd)。晶体管p1的源极与vdd连接,漏极与晶体管n5的栅极连接,栅极与晶体管n5的漏极连接。晶体管n5的源极与vss连接,漏极与晶体管p1的栅极连接。晶体管p1的栅极相当于节点x1,晶体管n5的栅极相当于节点x2。

[0104]

晶体管p2~p4的源极和漏极与vdd连接,栅极与节点x1连接。由于vss从固定值输出部5输出到节点x1,所以晶体管p2~p4作为电容元件发挥功能。晶体管n1~n4和晶体管p5为截止状态的晶体管。

[0105]

在图9中,局部布线142、143、144、145经由过孔与电源布线11连接。局部布线148经由过孔与电源布线12连接。金属布线151经由过孔与栅极布线131a、131b、131c、131d连接,并且经由过孔与局部布线146连接。金属布线152经由过孔与栅极布线131e连接,并且经由过孔与局部布线141连接。金属布线153经由过孔与栅极布线136a、136b、136c、136d连接,并且经由过孔与局部布线147连接。金属布线154经由过孔与栅极布线136e连接,并且经由过孔与局部布线141连接。

[0106]

在本变形例中,也能够得到与上述实施方式相同的作用和效果。

[0107]

(变形例2)

[0108]

图11是俯视图,其示出第二实施方式的变形例2所涉及的电容单元的布局构造。在图11的布局构造中,电源布线、晶体管、栅极布线的布置方式与图6的布局构造相同。不过,局部布线的布置方式有一部分不同,并且m1布线与局部布线以及栅极布线之间的连接关系、以及局部布线与电源布线之间的连接关系不同。

[0109]

图12是图11所示的电容单元的电路图。图12的电路相当于将在图8的电路中直接连接到vss上的晶体管p1~p4、n2~n4的源极和漏极连接到节点x2的电路,固定值输出部5向该节点x2输出低固定值(vss)。

[0110]

如图12所示,图11所示的单元具有p型晶体管p1、p2、p3、p4、p5以及n型晶体管n1、n2、n3、n4、n5。晶体管n2~n4作为电容元件发挥功能。晶体管p5和晶体管n1构成固定值输出部5。固定值输出部5向节点x1输出高固定值(vdd),向节点x2输出低固定值(vss)。晶体管p5的源极与vdd连接,漏极与晶体管n1的栅极连接,栅极与晶体管n1的漏极连接。晶体管n1的源极与vss连接,漏极与晶体管p5的栅极连接。晶体管n1的栅极相当于节点x1,晶体管p5的栅极相当于节点x2。

[0111]

晶体管n2~n4的源极和漏极与节点x2连接,栅极与节点x1连接。由于vdd从固定值输出部5输出到节点x1,vss从固定值输出部5输出到节点x2,所以晶体管n2~n4作为电容元件发挥功能。

[0112]

需要说明的是,晶体管p1~p4和晶体管n5为截止状态的晶体管。作为电容单元的电路结构,也可以没有晶体管p1~p4和晶体管n5,但如果有晶体管p1~p4和晶体管n5,则电容单元的布局的规则性提升,因此装置的制造容易度提升,成品率提升,制造偏差得到抑制。

[0113]

在局部布线层形成有沿y方向延伸的局部布线241、242、243、244、245、246、247、248。局部布线241与焊盘22a连接。局部布线242与焊盘27a连接,并且局部布线242经由过孔

与电源布线12连接。局部布线243与焊盘22b、27b连接。局部布线244与焊盘22c、27c连接。局部布线245与焊盘22d、27d连接。局部布线246与焊盘22e连接,并且局部布线246经由过孔与电源布线11连接。局部布线247与焊盘27e连接。局部布线248与焊盘22f、27f连接。

[0114]

在m1布线层,形成有沿x方向延伸的金属布线251、252、253、254。金属布线252、金属布线254对应于电路的节点x1,金属布线251、金属布线253对应于电路的节点x2。金属布线251经由过孔与局部布线241、243、244、245连接,并且经由过孔与栅极布线131e连接。金属布线252经由过孔与栅极布线131a、131b、131c、131d连接,并且经由过孔与局部布线248连接。金属布线253经由过孔与局部布线243、244、245、247连接。金属布线254经由过孔与栅极布线136a、136b、136c、136d连接,并且经由过孔与局部布线248连接。

[0115]

根据本变形例,也能够得到与上述实施方式相同的作用和效果。而且,在本变形例中,构成固定值输出部的晶体管n1以外的晶体管的源极和漏极不直接与vss连接,因此能够抑制由esd(electro static discharge:静电放电)引起的装置损坏。

[0116]

需要说明的是,与第二实施方式的变形例1同样,也能够在本变形例中替换晶体管的导电型。

[0117]

需要说明的是,在上述的各实施方式以及变形例中,供给vdd以及vss的电源布线是bpr,但是不限于此,例如也可以是m1布线等。

[0118]

在上述各实施方式和变形例中,形成有沿x方向延伸的四条m1布线,但也可以省略一部分m1布线。

[0119]-产业实用性-[0120]

在本公开中,能够实现使用了叉片fet的大容量的电容单元的布局构造,因此对于例如提升半导体芯片的小型化和集成度方面是有用的。

[0121]-符号说明-[0122]5ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

固定值输出部

[0123]

11、12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电源布线

[0124]

21b、21c、21d、23c、26b、26c、26d、28c

ꢀꢀꢀꢀ

纳米片

[0125]

22b、22c、22d、22e、27b、27c、27d、27e

ꢀꢀ

焊盘

[0126]

24、25

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

纳米片部

[0127]

31b、31c、31d、36b、36c、36d

ꢀꢀ

栅极布线

[0128]

131b、131c、131d、136b、136c、136d

ꢀꢀꢀꢀꢀꢀ

栅极布线

[0129]

133b、133c、133d

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

桥部

[0130]

142、143、144、145

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

局部布线

[0131]

p1、p2、p3、p4、p5

ꢀꢀꢀꢀꢀꢀ

p型晶体管

[0132]

n1、n2、n3、n4、n5

ꢀꢀꢀꢀꢀꢀ

n型晶体管

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1