光接收元件和测距系统的制作方法

1.本技术涉及光接收元件和测距系统,并且更具体地,涉及能够在防止边缘破裂的同时实现高pde的光接收元件和测距系统。

背景技术:

2.近年来,通过飞行时间(tof)方法测量距离的测距传感器受到关注。测距传感器的示例包括使用单光子雪崩二极管(spad)作为光接收像素的测距传感器。在spad中,当施加大于击穿电压的电压(在后文中被称为过度偏压(excess bias))的状态中,当一个光子进入高电场的pn结区域时,雪崩放大发生。通过检测此时电流瞬时流动的时刻,可以高精度地测量距离。

3.例如,专利文献1公开了一种像素结构,其中,包括n型半导体区和p型半导体区的倍增区中的该p型半导体区的面积形成为小于该n型半导体区,以便减小在倍增区的发生雪崩放大的端部处的强电场(边缘断开)。

4.现有技术文献

5.专利文献

6.专利文献1:wo 2018/074530

技术实现要素:

7.本发明要解决的问题

8.然而,专利文献1的像素结构具有高内阻,需要大的过量偏压,并且具有改进的空间。

9.鉴于这种情况做出本技术,并且其目标是使得可以实现高光子检测效率(pde)同时防止边缘断裂。

10.问题的解决方案

11.根据本技术的第一方面的光接收元件包括像素,在像素中,在第一导电类型的第一半导体区和与第一半导体区相对的第二导电类型的第二半导体区接合的区域中形成倍增区,并且形成在比第一半导体区更靠近光接收表面的位置处的第二半导体区的平面区域更大。

12.根据本技术的第二方面的测距系统包括:照明装置,发射照射光;以及光接收元件,接收通过由被摄体反射照射光而获得的反射光;其中,光接收元件包括像素,在像素中,在第一导电类型的第一半导体区和与第一半导体区相对的第二导电类型的第二半导体区接合的区域中形成倍增区,并且形成在比第一半导体区更靠近光接收表面的位置处的第二半导体区的平面区域更大。

13.在本技术的第一方面和第二方面,在第一导电类型的第一半导体区和与第一半导体区相对的第二导电类型的第二半导体区接合的区域中形成倍增区,并且形成在比第一半导体区更靠近光接收表面的位置处的第二半导体区的平面区域更大。

14.光接收元件和测距系统可以是独立的装置,或者可以是结合在其他装置中的模块。

附图说明

15.图1是示出使用spad的像素的电路配置示例的图。

16.图2是示出图1中的像素的操作的曲线图。

17.图3是示出使用spad的像素的第一像素结构的视图。

18.图4是示出第一像素结构的操作和效果的图。

19.图5是示出第一像素结构的操作和效果的视图。

20.图6是示出根据第一像素结构的像素的第一变形例的截面图。

21.图7是示出根据第一像素结构的像素的第二变形例的截面图。

22.图8是根据第一像素结构的像素的平面图。

23.图9是示出根据第一像素结构的像素的第三变形例的平面图。

24.图10是示出使用spad的像素的第二像素结构的截面图。

25.图11是示出根据第二像素结构的像素的变形例的截面图。

26.图12是示出使用spad的像素的第三像素结构的截面图。

27.图13是示出使用spad的像素的第四像素结构的截面图。

28.图14是示出使用spad的像素的第五像素结构的截面图。

29.图15是示出使用spad的像素的第六像素结构的截面图。

30.图16是示出使用spad的像素的第七像素结构的图。

31.图17是示出半导体区中的电子流动的视图。

32.图18是图17中的阴极接触外周区的放大图。

33.图19是示出分离层和低浓度n型半导体区在基板厚度方向上的深度的视图。

34.图20是示出根据第七像素结构的像素的变形例的平面图。

35.图21是示出根据第七像素结构的像素分离层的制造方法的视图。

36.图22是示出根据第七像素结构的像素分离层的制造方法的视图。

37.图23是示出根据第七像素结构的像素的第一变形例的视图。

38.图24是示出根据第七像素结构的像素的第二变形例和第三变形例的截面图。

39.图25是示出根据第七像素结构的像素的效果的视图。

40.图26是示出使用spad的像素的第八像素结构的视图。

41.图27是示出使用spad的像素的第九像素结构的图。

42.图28是示出使用spad的像素的第十像素结构的视图。

43.图29是示出堆叠结构的像素结构示例的截面图。

44.图30是示出执行有源消光的像素的电路配置示例的图。

45.图31是示出应用本技术的光接收元件的配置示例的框图。

46.图32是示出应用本技术的测距系统的配置示例的框图。

47.图33是示出作为应用本技术的电子装置的智能电话的配置示例的框图。

48.图34是示出车辆控制系统的示意性配置的示例的框图。

49.图35是表示车外信息检测部和摄像部的安装位置的例子的说明图。

具体实施方式

50.在下文中,将参考附图描述用于执行本技术的模式(在下文中,称之为实施方式)。注意,在描述和附图中,具有基本上相同的功能和配置的部件由相同的附图标记表示,并且省略多余的描述。将按照以下顺序进行描述。

51.1.使用spad的像素电路

52.2.像素的第一像素结构

53.3.像素的第一像素结构的变形例

54.4.像素的第二像素结构

55.5.像素的第三像素结构

56.6.像素的第四像素结构

57.7.像素的第五像素结构

58.8.像素的第六像素结构

59.9.像素的第七像素结构

60.10.第七像素结构的制造方法

61.11.像素的第七像素结构的变形例

62.12.像素的第八像素结构

63.13.像素的第九像素结构

64.14.像素的第十像素结构

65.15.堆叠结构的配置示例

66.16.执行有源消光的像素电路

67.17.光接收元件的配置示例

68.18.测距系统的配置示例

69.19.电子设备的应用示例

70.20.移动体的应用示例

71.注意,在以下描述中参考的附图中,相同或相似的部分由相同或相似的参考标号表示。然而,附图是示意性的,并且厚度和平面尺寸之间的关系、各层的厚度比率等与实际不同。此外,附图可以包括具有不同尺寸关系和比率的部分。

72.此外,在以下描述中的方向的定义(诸如,上下方向)仅是为了便于描述的定义,并且不限制本公开的技术构思。例如,当通过将对象旋转90

°

观察对象时,通过转换为左侧和右侧读取上侧和下侧,并且当通过将对象旋转180

°

观察对象时,通过反转读取上侧和下侧。

73.《1.使用spad的像素电路》

74.图1示出使用单光子雪崩二极管(spad)的像素电路,该spad可应用于通过飞行时间(tof)方法测量距离的测距传感器的光接收元件。

75.图1中的像素10包括spad 21、恒流源22、晶体管23和反相器24。

76.spad 21的阴极连接至恒流源22,并且连接至反相器24的输入端子和晶体管23的漏极。spad 21的阳极连接至电源vspad。

77.spad 21是光电二极管(单光子雪崩光电二极管),该光电二极管对产生的电子执行雪崩放大并且当入射光入射时输出阴极电压vs的信号。例如,供应至spad 21的阳极的电源vspad是具有与spad 21的击穿电压vbd相同的电压的负偏压(负电位)。

78.例如,恒流源22包括在饱和区域中操作的p型mos晶体管,并且通过用作淬灭电阻器来执行无源淬灭。电源电压ve(ve》0)被供应至恒流源22。注意,对于恒流源22,还可以使用上拉电阻器等代替p型mos晶体管。

79.为了以足够的效率检测光(光子),将大于spad 21的击穿电压vbd的电压(在下文中称为过量偏压(excess bias))施加至spad 21。

80.晶体管23的漏极连接至spad 21的阴极、反相器24的输入端子、以及恒流源22,并且晶体管23的源极连接至地(gnd)。栅极控制信号vg从驱动像素的像素驱动部提供给晶体管23的栅极。

81.在像素10是有源像素的情况下,低(lo)栅极控制信号vg从像素驱动部供应至晶体管23的栅极。另一方面,在像素10是非有源像素的情况下,高(hi)栅极控制信号vg从像素驱动部供应至晶体管23的栅极。

82.反相器24在作为输入信号的阴极电压vs为低时输出高pfout信号,并且在阴极电压vs为高时输出低pfout信号。

83.接下来,将参考图2描述在像素10设定为有源像素的情况下的操作。图2是示出spad 21响应于光子入射的阴极电压vs和检测信号pfout的变化的曲线图。

84.首先,在像素10是有源像素的情况下,晶体管23通过低栅极控制信号vg被设置为截止。

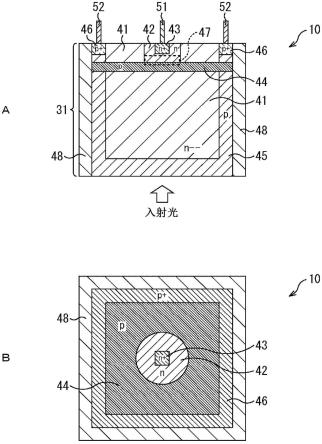

85.在图2中的时间t0之前的时间,因为电源电压ve被供应至spad 21的阴极并且电源vspad被供应至阳极,所以大于击穿电压vbd的反向电压被施加至spad 211,从而将spad 21设置为盖革(geiger)模式。在这种状态下,spad 21的阴极电压vs与电源电压ve相同。

86.当光子入射在设置在盖革模式中的spad 21上时,雪崩倍增发生,并且电流流过spad 21。

87.当在时间t0出现雪崩倍增并且电流流过spad 21时,在时间t0之后,通过流过spad 21的电流,电流也流过作为恒流源22的p型mos晶体管,并且由于mos晶体管的电阻部件而出现电压降。

88.当spad 21的阴极电压vs在时间t2变得低于0v时,电压变得低于击穿电压vbd,使得雪崩放大停止。在此,淬火操作使得由雪崩放大生成的电流流过恒流源22以生成电压降,并且阴极电压vs随着生成的电压降而变得低于击穿电压vbd,从而停止雪崩放大。

89.当雪崩放大停止时,流过恒流源22(p型mos晶体管)的电流逐渐减小,并且在时间t4,阴极电压vs再次返回至原始电源电压ve,使得其能够检测下新的光子(再充电操作)。

90.反相器24在作为输入电压的阴极电压vs等于或高于预定阈值电压vth(=ve/2)时输出lo(低)pfout信号,并且在阴极电压vs低于预定阈值电压vth时输出高pfout信号。在图4的示例中,在从时间t1到时间t3的时间段内输出hi(高)pfout信号。

91.注意,在像素10是非有源像素的情况下,高栅极控制信号vg从像素驱动部提供到晶体管23的栅极,并且晶体管23接通。因此,spad 21的阴极电压vs变为0v(gnd),并且spad 21的阳极-阴极电压变为等于或低于击穿电压vbd,并且因此即使光子进入spad 21也没有反应发生。

92.《2.像素的第一像素结构》

93.图3是示出使用上述spad 21的像素10的第一像素结构的视图。

94.图3示出与形成在包括硅等的半导体基板31上的多个像素中的一个像素对应的部分的像素结构,并且图3的a是像素10的截面图。

95.在图3的a中示出的像素10的截面图中,仅示出半导体基板31的结构,并且图3的a的下侧是半导体基板31的背面侧,该背面侧是在其上形成片上透镜等的入射面侧,并且从物体反射的反射光入射。

96.另一方面,图3的a的上侧是半导体基板31的前表面侧,并且虽然未示出,但是形成包括用于驱动像素等的电路的布线层。

97.图3的b是从半导体基板31的前表面侧观看的图3的a的像素10的平面图。

98.如图3的a所示,像素10包括n阱41、n型半导体区42、高浓度n型半导体区43、p型半导体区44、空穴蓄积区45和高浓度p型半导体区46。然后,雪崩倍增区47由耗尽层形成,该耗尽层形成在n型半导体区42和p型半导体区44接合的区域中。

99.n阱41通过控制到其中半导体基板31的杂质浓度薄的n型(n

‑‑

)而形成,并且形成将通过像素10中的光电转换产生的电子转移到雪崩倍增区47的电场。注意,代替n阱41,可以形成其中将半导体基板31的杂质浓度控制为p型的p阱。

100.如图3的b所示,n型半导体区42是厚的n型(第一导电类型)半导体区(第一半导体区),在像素区域的中心部中形成在距半导体基板31的前表面侧的预定深度处。然后,在n型半导体区42中,具体地,控制中心部的表面附近以具有高浓度(n+)的杂质以形成高浓度n型半导体区43。高浓度n型半导体区43是接触部(第一接触部),接触部连接至作为用于提供负电压的阴极的接触电极51以形成雪崩倍增区47。从接触电极51向高浓度n型半导体区43施加电源电压ve。

101.p型半导体区44是在具有预定厚度(深度)的像素区域的整个表面上从与半导体基板31中的n型半导体区42的底表面接触的深度位置形成的厚的p型(第二导电类型)半导体区(第二半导体区)。

102.在此,将n阱41的杂质浓度设置为例如1e+14/cm3或更小的低浓度,并且期望将形成雪崩倍增区47的n型半导体区42和p型半导体区44中的每一个的杂质浓度控制为具有1e+16/cm3或更大的高浓度。

103.空穴蓄积区45是以围绕n阱41的侧表面和底表面的方式形成的p型半导体区(p),并且蓄积由光电转换生成的空穴。此外,空穴蓄积区45俘获在与像素分离部48的交界处产生的电子,并且还具有抑制暗计数比(dcr)的效果。特别将空穴蓄积区45的基板表面侧附近的区域控制为杂质浓度(p+)高,形成高浓度p型半导体区46。高浓度p型半导体区46是连接至作为spad 21的阳极的接触电极52的接触部(第二接触部)。从接触电极52向高浓度p型半导体区46施加电源vspad。空穴蓄积区45可以通过离子注入形成,并且可以通过固相扩散形成。

104.将像素彼此分离的像素分离部48形成在像素10的像素边界部处,该像素边界部是与相邻像素的边界。例如,像素分离部48可仅包括诸如氧化硅膜的绝缘层,或者可具有双重结构,使得诸如钨的金属层的外侧(n阱41侧)覆盖有诸如氧化硅膜的绝缘层。

105.如上所述,在根据第一像素结构的像素10中,关于其中形成雪崩倍增区47的n型半导体区42和p型半导体区44的平面区域,p型半导体区44的平面区域形成为大于n型半导体区42的平面区域。此外,关于n型半导体区42和p型半导体区44距基板前表面的深度位置,p

型半导体区44形成在比n型半导体区42的深度位置更深的位置处。换言之,p型半导体区44形成在比n型半导体区42更靠近光接收表面的位置处。

106.要注意的是,在从半导体基板31的前表面侧观看像素10的图3的b中所示的平面图中,在n型半导体区42与高浓度p型半导体区46之间的区域恰好是n阱41,但是p型半导体区44低于所示的n阱41,以便示出在n型半导体区42与p型半导体区44之间的区域尺寸的差异。

107.图3中的第一像素结构是其中读取电子作为信号电荷(载流子)的结构的示例,但是可以使用其中读取空穴的结构。在这种情况下,具有小平面尺寸的n型半导体区42变成p型半导体区,并且高浓度n型半导体区43变成高浓度p型半导体区。具有大平面尺寸的p型半导体区44变成n型半导体区,并且高浓度p型半导体区46变成高浓度n型半导体区。从接触电极51向从高浓度n型半导体区43改变到高浓度p型半导体区的接触部施加电源vspad,并且从接触电极52向从高浓度p型半导体区46改变到高浓度n型半导体区的接触部施加电源电压ve。

108.《第一像素结构的操作和效果》

109.将参考图4和图5描述其中p型半导体区44的平面区域形成为大于其中形成雪崩倍增区47的n型半导体区42的平面区域的结构的效果。

110.在图4的描述中,给出了与图3中的参考标号相同的参考标号以便于理解。

111.通常,如在图4的a中所示,可以想象一种结构,其中,形成雪崩倍增区47的n型半导体区42和p型半导体区44在同一平面区域中形成,使得连接区重叠。

112.在这种情况下,如在图4的a的下侧上的电场曲线图中所示,雪崩倍增区47的端部变成强电场,并且发生边缘击穿。

113.因此,如在图4的b中所示,通过减小其中形成雪崩倍增区47的n型半导体区42和p型半导体区44的平面尺寸,可以说,仅使用仅在图4的a中的端部处的强电场部并且具有强且均匀的电场来形成雪崩倍增区47。为了形成具有均匀电场的这种雪崩倍增区47,例如,n型半导体区42的直径优选为2μm或更小,并且n型半导体区42与p型半导体区44之间的深度方向上的相对距离优选为1000nm或更小。

114.因此,通过减小雪崩倍增区47的平面尺寸,可以使电场均匀并且可以防止边缘击穿,但是在图3的第一像素结构中,p型半导体区44延伸到像素外周部中的空穴蓄积区45。

115.将参考图5描述延伸到像素外周部中的空穴蓄积区45的p型半导体区44的效果。

116.雪崩放大所产生的空穴经由p型半导体区44移动到空穴蓄积区45。作为p型半导体区44的在平面方向上在n型半导体区42外部的区域的外周区61形成空穴电流路径并且具有改善内阻(降低空穴电阻)的效果。

117.此外,由于p型半导体区44在平面方向上形成在雪崩倍增区47的外周区61中,所以由于入射光的入射而在n阱41中生成的电子移动至外周区61内部的雪崩倍增区47。即,外周区61的p型半导体区44具有屏蔽效应,并且n阱41的电子以无障碍(barrier)方式移动至雪崩倍增区47。从n阱41到雪崩倍增区47的无障碍结构实现了高电荷收集效率。

118.因此,利用图3所示的像素10的第一像素结构,能够实现高pde,同时防止边缘断裂。高pde的实现还允许低的过偏压。

119.《3.像素的第一像素结构的变形例》

120.图6是示出根据第一像素结构的像素10的第一变形例的截面图。

121.注意,在图6和随后的附图中,对应于图3中所示的第一像素结构的那些的部分由相同的附图标记表示,并且将适当地省略其描述。

122.在图6的第一变形例中,在图3中示出的第一像素结构中形成雪崩倍增区47的p型半导体区44变成p型半导体区44’。

123.在图3所示的第一像素结构中,在像素周边部分中,p型半导体区44的平面区域延伸直到到达空穴蓄积区45,但是图6的第一变形例的p型半导体区44’不延伸直到到达空穴蓄积区45,并且在p型半导体区44’与空穴蓄积区45之间形成n阱41(第四半导体区)。然而,p型半导体区44’的平面区域形成为大于n型半导体区42的平面区域。

124.如上所述,即使在p型半导体区44’没有形成得足够大以与空穴蓄积区45接触的情况下,由于p型半导体区44’形成为至少大于n型半导体区42,所以p型半导体区44在平面方向上在n型半导体区42之外的区域(图5中的外周区61)形成空穴电流路径,并且因此获得改善内阻(降低空穴电阻)的效果。

125.图7为示出根据第一像素结构的像素10的第二变形例的截面图。

126.在图3所示的第一像素结构中,在像素10的像素边界部处形成将像素彼此分离的像素分离部48,并且在像素分离部48的像素中心侧上的侧表面(像素边界部附近)上形成空穴蓄积区45。

127.另一方面,在图7的第二变形例中,图3的像素分离部48被省略。因此,与图3中的第一像素结构相比,空穴蓄积区45被设置在外周部中以便与相邻像素的边界部接触,并且n阱41的区域形成为比图3中的第一像素结构更宽。

128.这样,可以省略像素分离部48。

129.图8的a示出四个像素区域的平面图,其中,从半导体基板31的前表面侧观察,根据图3中所示的第一像素结构的像素10排列成2

×

2。

130.图8的b示出从半导体基板31的前表面侧观看时四个像素区域的平面图,其中,根据图7中所示的第二变形例的像素10排列成2

×

2。

131.在图8的a和b中,虚线表示像素10的边界。

132.在像素分离部48形成在像素10的边界部处的情况下,如图8的a所示,像素分离部48布置在像素10周围,并且在多个像素的阵列中,像素分离部48布置成格子图案。

133.另一方面,在像素10的边界部不形成像素分离部48的情况下,如图8的b所示,空穴蓄积区45布置在像素10周围,并且在多个像素的阵列中,空穴蓄积区45布置成格子图案。

134.图9是根据第一像素结构的像素10的第三变形例,并且示出n型半导体区42的平面形状的变形例。除n型半导体区42之外的结构类似于图3中所示的第一像素结构。

135.在图3所示的第一像素结构中,n型半导体区42的平面形状为圆形,但是n型半导体区42的平面形状不限于圆形,并且可以是四边形、五边形或其他多边形形状。

136.图9的a示出n型半导体区42的平面形状为四边形的示例。

137.图9的b示出n型半导体区42的平面形状为五边形形状的示例。

138.《4.像素的第二像素结构》

139.图10是示出使用spad 21的像素10的第二像素结构的截面图。注意,从半导体基板31的前表面侧观看的根据第二像素结构的像素10的平面图类似于在第一像素结构中的图3的b,并且因此被省略。

140.当根据图10的第二像素结构的像素10与根据图3中所示的第一像素结构的像素10进行比较时,杂质浓度高于n阱41的杂质浓度的n型(n-)的n型半导体区81(第四半导体区)形成在比形成雪崩倍增区47的n型半导体区42和p型半导体区44更深(更靠近光接收表面)的区域中。

141.换言之,在根据图3所示的第一像素结构的像素10中,由具有低杂质浓度的n阱41和杂质浓度高于n阱41的杂质浓度的n型半导体区81代替由p型半导体区44和空穴蓄积区45围绕的n阱41,并且n型半导体区81布置在n阱41和p型半导体区44之间。

142.因此,形成电位梯度,使得在n阱41中生成的载流子(电子)容易朝向雪崩倍增区47漂移。

143.要注意的是,根据电位梯度的设计,如图11中所示,可以使用并非具有与n阱41相同的导电类型的n型半导体区81,而是具有与n阱41的导电类型不同的导电类型和比p型半导体区44更低的杂质浓度的p型半导体区81’(第四半导体区)。

144.可以通过离子注入形成n型半导体区81和p型半导体区81’,其中,注入n型或p型离子。

145.《5.像素的第三像素结构》

146.图12是示出使用spad 21的像素10的第三像素结构的截面图。

147.当根据图12中的第三像素结构的像素10与根据图3中所示的第一像素结构的像素10进行比较时,在像素边界部处形成的像素分离部48由从前表面侧穿透半导体基板31至后表面侧的像素间沟槽部101和绝缘层102取代。像素间沟槽部101例如由诸如钨(w)、铝(al)、钛(ti)或氮化钛(tin)的金属材料或者诸如多晶硅的导电材料形成,并且从形成有布线层的半导体基板31的前表面侧施加比spad 21的阳极电极(接触电极52)的负电压大的负电压。绝缘层102由例如sio2形成。

148.像素间沟槽部101和绝缘层102的平面布置具有类似于图8的a中示出的像素分离部48的晶格形状的晶格形状。

149.通过形成这种像素间沟槽部101和绝缘层102,可以进一步减小相邻像素的影响,并且可以进一步减小串扰。另外,通过形成横向电场,容易回收高电场区域的载流子,能够提高pde。

150.《6.像素的第四像素结构》

151.图13是示出使用spad 21的像素10的第四像素结构的截面图。

152.当根据图13中的第四像素结构的像素10与根据图3中所示的第一像素结构的像素10进行比较时,在像素分离部48与在像素边界部处形成的空穴蓄积区45之间形成固定电荷膜121。除了像素分离部48与空穴蓄积区45之间的侧表面之外,固定电荷膜121还形成在半导体基板31的背面侧上的空穴蓄积区45的外部。

153.固定电荷膜121是负固定电荷膜。通过固定电荷膜121诱导空穴而在固定电荷膜121的内部形成空穴蓄积区。通过组合由固定电荷膜121形成的空穴蓄积区和形成于该空穴蓄积区内部的空穴蓄积区45,能够抑制暗电流,能够抑制dcr。此外,通过减少串扰和形成横向电场,可以容易地收集高电场区域中的载流子,并且可以改善pde。

154.《7.像素的第五像素结构》

155.图14的a是示出使用spad 21的像素10的第五像素结构的截面图,并且图14的b是

从半导体基板31的前表面侧观看的图14的a中的像素10的平面图。

156.当根据图14中的第五像素结构的像素10与根据图3中所示的第一像素结构的像素10进行比较时,新增加了由浅沟槽分离(sti)形成的绝缘层141。

157.如图14的b所示,绝缘层141形成在在平面方向上连接至作为spad21的阴极的接触电极51的n型半导体区42和高浓度n型半导体区43的外周上,并且将spad 21的阳极和阴极彼此电分离。

158.应注意,因为其用于将spad 21的阳极和阴极电分离的目的,绝缘层141不总是必须布置在与n型半导体区42相邻的外周,并且仅需要布置在电连接至接触电极51的n型半导体区42与高浓度n型半导体区43之间以及电连接至接触电极52的高浓度p型半导体区46之间。例如,绝缘层141可形成在靠近基板前表面的高浓度p型半导体区46的内周侧上。

159.在图14的b中,在n型半导体区42与高浓度p型半导体区46之间的区域恰好是n阱41,但是示出的低于n阱41的p型半导体区44的点类似于图3的b。

160.《8.像素的第六像素结构》

161.图15的a是示出使用spad 21的像素10的第六像素结构的截面图,并且图15的b是从半导体基板31的前表面侧观看的图15的a中的像素10的平面图。

162.根据图14中所示的第五像素结构的像素10具有spad 21的阳极和阴极使用绝缘层141在平面方向上分离的配置,但是根据图15中所示的第六像素结构的像素10具有spad 21的阳极和阴极通过将spad 21的阳极和阴极布置在半导体基板31的不同深度位置而分离的配置。

163.具体地,当根据图15中的第六像素结构的像素10与根据图3中所示的第一像素结构的像素10进行比较时,像素10的像素边界部处的像素分离部48由穿透半导体基板31的与背面侧或前面侧的相对侧上的基板表面的导电构件161和形成在其两个外侧(像素内部)上的绝缘膜162代替。导电性部件161例如由多晶硅或钨(w)等金属材料形成,绝缘膜162例如由sio2形成。

164.此外,作为spad 21的阳极的接触部的高浓度p型半导体区46被嵌入和布置在半导体基板31中。在图15的a的示例中,高浓度p型半导体区46在深度方向上的位置形成在与p型半导体区44相同的位置处,但是高浓度p型半导体区46和p型半导体区44在深度方向上的位置不必相同。阳极侧上的高浓度p型半导体区46和阴极侧上的n型半导体区42和高浓度n型半导体区43仅需要被布置在不同的深度位置处。

165.导电构件161连接至半导体基板31的前表面的上表面上的接触电极52,并且连接至半导体基板31中的高浓度p型半导体区46,并且高浓度p型半导体区46经由导电构件161电连接至接触电极52。导电构件161的外周部,除了与高浓度p型半导体区46连接的连接区域以外,被绝缘膜162覆盖,与n阱41和空穴蓄积区45电分离。

166.如上所述,在像素尺寸减小的情况下,spad 21的阳极和阴极布置在半导体基板31的深度方向上的不同位置处并且分离的配置是有效的。即,当spad 21的阳极和阴极被布置在同一平面上时,在像素尺寸被小型化的情况下存在限制。此外,因为spad 21的阳极和阴极彼此靠近,所以电气分离是困难的。通过将像素配置成沿深度方向移位,与像素布置在相同平面上的情况相比,能够进一步减小像素尺寸。

167.《9.像素的第七像素结构》

168.图16的a是示出使用spad 21的像素10的第七像素结构的截面图,并且图16的b是沿着图16的a中的线x-x’截取的像素10的平面图。

169.在下面要参考的图16至图28中,相同的参考标号被给予与上述第一像素结构相同的部分,并且将适当地省略对这些部分的描述。

170.在根据第七像素结构的像素10中,雪崩倍增区47通过在连接到作为阴极的接触电极51的高浓度n型半导体区43与在其下方形成的p型半导体区44之间的接合区域中形成的耗尽层形成,类似于上述第一至第六像素结构。

171.在图16的a的截面图中,示出在上述第一至第六像素结构中省略的片上透镜816。片上透镜816形成在半导体基板31的后表面侧(其是图16的a的下侧)上。作为阴极的接触电极51、作为阳极的接触电极52等形成在半导体基板31的前表面上。

172.在基板平面方向(图16中的横向方向)上,在连接至作为阴极的接触电极51的高浓度n型半导体区43与连接至作为阳极的接触电极52的高浓度p型半导体区46之间形成物理分离和电分离它们的分离层801。该分离层801由例如氧化硅膜(sio2)形成,并且具有与根据图14中所示的第五像素结构的像素10的绝缘层141的功能相似的功能。即,通过分离层801将spad 21的阳极和阴极电分离,可以抑制阳极和阴极之间在平面方向上的边缘击穿。具体地,即使在像素10的像素尺寸减小并且阳极和阴极之间的距离缩短的情况下,也可以可靠地抑制边缘击穿。

173.在分离层801与高浓度n型半导体区43之间形成低浓度n型半导体区802(第六半导体区),该低浓度n型半导体区802具有与高浓度n型半导体区43相同的导电类型(n型)并且杂质浓度低于高浓度n型半导体区43。此外,在分离层801和高浓度p型半导体区46之间形成具有与高浓度n型半导体区43的导电类型相反的导电类型(p型)并且杂质浓度高于p型半导体区44的杂质浓度的高浓度p型半导体区803(第五半导体区)。应注意,在示出上述第一至第六像素结构的附图(例如,图14等)中,高浓度p型半导体区46的杂质浓度由“p+”表示,并且在图16中,对于高浓度p型半导体区803,杂质浓度也由“p+”表示。然而,高浓度p型半导体区46具有比高浓度p型半导体区803的杂质浓度高的杂质浓度。与高浓度p型半导体区803相比,高浓度p型半导体区46的杂质浓度可以表示为“p++”。

174.图16的a中的单点划线表示像素10在半导体基板31的平面方向上的边界,并且像素分离部811形成在像素10的像素边界部处。像素分离部811包括使用钨等的金属dti 812以及形成在金属dti内部(n阱41侧)的氧化硅膜(绝缘层)813。像素分离部811是另一种形式的像素分离部48,例如,根据在图3中示出的第一像素结构的像素10。而且,金属dti 812和氧化硅膜813也可以说是图12所示的第三像素结构的像素间沟槽部101和绝缘层102的其他形式。负电压可以被施加到金属dti 812,如在图12中所示的第三像素结构中。在半导体基板31的光入射面侧的像素边界部处,使用与金属dti 812相同的材料形成像素间遮光膜814。在半导体基板31的背面侧的界面,形成与构成像素分离部811的氧化硅膜813同时形成的氧化硅膜815。

175.如图16的b所示,高浓度n型半导体区43、低浓度n型半导体区802和分离层801的平面形状是圆形的。低浓度n型半导体区802形成为围绕形成为圆形的高浓度n型半导体区43的外周边,并且分离层801进一步形成为围绕低浓度n型半导体区802的外周边。高浓度p型半导体区803形成在分离层801与像素分离部811之间的区域中,像素分离部811形成在像素

边界部处并且包括金属dti 812和氧化硅膜813。分离层801在平面方向上将高浓度n型半导体区43和低浓度n型半导体区802的n型半导体区与高浓度p型半导体区803和高浓度p型半导体区46的p型半导体区物理和电分离。

176.根据如上所述配置的第七像素结构的像素10与图14中所示的第五像素结构的不同之处在于,在截面图中位于p型半导体区44之上(基板前表面侧)并且在平面图中位于分离层801之外的区域,换言之,在分离层801与高浓度p型半导体区46之间的区域从n阱41变成高浓度p型半导体区803。

177.在此,在图17的b中示出在图17的a中由点划线表示的线y-y

’‑

y”上的电位。假设点y是起点并且点y”是终点,则线y-y

’‑

y”依次穿过高浓度p型半导体区803、p型半导体区44、n阱41、p型半导体区44和高浓度n型半导体区43,并且形成电位梯度,其中电位从点y经由点y’朝向点y”减小,如图17的b所示。雪崩倍增区47的p型半导体区44被耗尽。

178.即,因为高浓度p型半导体区803形成在p型半导体区44上方的靠近基板前表面的区域中,所以形成电位梯度,其中电位从点y经由点y’朝向点y”减小。由此,在半导体基板31的形成有高浓度p型半导体区803的前表面附近的区域中光电转换的电子能够被移动到雪崩倍增区47而不逸出到像素的外部,使得能够改进pde。

179.注意,高浓度p型半导体区803的杂质浓度高于p型半导体区44的杂质浓度,但低于连接到阳极(接触电极52)的高浓度p型半导体区46的杂质浓度。换言之,高浓度p型半导体区803的能级低于费米能级(fermi level),并且高浓度p型半导体区803的杂质浓度是光电转换的电子和空穴不会再结合的浓度值。杂质浓度超过费米能级的区域仅是与阳极(接触电极52)连接的高浓度p型半导体区46。

180.将描述在图17的a的截面图中包括被示出为区域831的分离层801的阴极接触周围的结构。

181.图18的a是图17的a中的阴极接触点周围的区域831的放大图。

182.分离层801在平面方向上的内壁表面(内周壁表面)上与低浓度n型半导体区802接触,并且在平面方向上的外壁表面(外周壁表面)上与高浓度p型半导体区803接触,并且物理分离低浓度n型半导体区802和高浓度p型半导体区803。由此,如上所述,能够抑制阳极和阴极之间在平面方向上的边缘击穿,并且能够将在半导体基板31的前表面附近的区域中光电转换的电子移动到雪崩倍增区47,使得能够改进pde。

183.与分离层801的内周壁表面接触的区域是杂质浓度低于形成雪崩倍增区47的高浓度n型半导体区43的杂质浓度的低浓度n型半导体区802。由此,可以释放分离层801的内周壁表面上的电场。

184.此外,分离层801还具有防止在雪崩倍增区47中生成的辐射光在平面方向上向外扩散并且进入相邻像素10的功能。因此,可以减少由在雪崩倍增区47中生成的辐射光引起的串扰。

185.注意,在以上描述中,分离层801由氧化硅膜形成,但是分离层801可以由其他材料形成。例如,分离层801可以由具有低介电常数的低k膜形成。作为低k膜的具体材料,可以提及氟化硅酸盐玻璃、聚对二甲苯、sioc、特氟隆(注册商标)、silk、聚酰亚胺、氟化无定形碳、多孔二氧化硅等。

186.图18的b和c是示出分离层801的另一个构造示例的区域831的放大图。

187.图18的b示出分离层801由气隙配置的示例。

188.图18的c示出分离层801具有由多种材料而不是单一材料形成的双重结构的示例。图18的c中的分离层801具有双重结构,其中,内部是空气间隙841,外部是氧化硅膜842。氧化硅膜842在平面方向上的内壁表面(内周壁表面)上与低浓度n型半导体区802接触,在平面方向上的外壁表面(外周壁表面)上与高浓度p型半导体区803接触,并且在向下方向上的底面上与p型半导体区44接触。

189.接下来,将参考图19描述在基板厚度方向上的分离层801和低浓度n型半导体区802的深度。

190.在上述示例中,分离层801和低浓度n型半导体区802距基板前表面的深度被设置为与其中形成雪崩倍增区47的高浓度n型半导体区43和p型半导体区44的pn结表面相同的深度,例如,如图18的a所示。

191.然而,分离层801的深度可以被设置为比图19的a中所示的pn结表面更深的位置。低浓度n型半导体区802的深度也可以形成在与分离层801相同的深度处。

192.注意,低浓度n型半导体区802的深度不需要形成在与分离层801相同的深度处,换言之,在分离层801的整个内周壁表面上,并且可以比分离层801浅,如图19的b所示。低浓度n型半导体区802的深度仅需要是在内部的高浓度n型半导体区43的深度和外部的分离层801的深度之间的深度。即使在分离层801被形成为具有在该范围内的深度的情况下,也可以获得与上述效果类似的效果。例如,其可以有助于抑制由于在平面方向上n型半导体区和p型半导体区之间的物理分离引起的边缘击穿、减少由雪崩倍增区47中生成的辐射光引起的串扰等。

193.图20是根据第七像素结构的像素10的变形例,并且示出高浓度n型半导体区43等的平面形状的另一示例。

194.在图16中所示的第七像素结构的示例中,高浓度n型半导体区43、低浓度n型半导体区802以及分离层801的平面形状是圆形,但不限于圆形,并且可以是四边形、五边形或其他多边形形状。

195.图20的a示出高浓度n型半导体区43、低浓度n型半导体区802和分离层801的相应平面形状为四边形的示例。

196.图20的b示出高浓度n型半导体区43、低浓度n型半导体区802和分离层801的相应平面形状是五边形形状的示例。

197.《10.第七像素结构的制造方法》

198.接下来,将描述根据第七像素结构的像素10的分离层801的制造方法。

199.《通过氧化膜形成分离层的情况下的制造方法》

200.首先,将参考图21描述在分离层801由氧化硅膜形成的情况下的制造方法。注意,图21仅示出对应于图17的a中所示的阴极接触点周围的区域831的部分。

201.首先,如图21的a所示,在半导体基板31的前表面侧的上表面上形成氧化硅膜871作为离子注入透过膜。此后,执行离子注入以在半导体基板31的前表面侧附近的区域中形成高浓度n型半导体区43、低浓度n型半导体区802和高浓度p型半导体区803。

202.接着,如图21的b所示,在氧化硅膜871上形成氮化硅膜872。通过使用氮化硅膜872作为硬掩模在作为分离层801的位置处蚀刻高浓度p型半导体区803,在分离层801的形成位

置处形成开口873,如图21的c所示。

203.接着,如图21的d所示,例如,通过热氧化法在开口873的底面及侧壁表面的半导体区形成氧化硅膜871。

204.接着,如图21的e所示,例如,通过使用高密度等离子体的化学气相沉积(cvd)在开口873中嵌入氧化硅膜874。此时,氧化硅膜874也形成在氮化硅膜872的上表面上。

205.然后,如图21的f所示,通过化学机械研磨(cmp)使氧化硅膜874平坦化,除去形成在氮化硅膜872的上表面的氧化硅膜874。嵌入在开口873中的氧化硅膜874和氧化硅膜871对应于分离层801。

206.通过上述步骤,高浓度n型半导体区43、低浓度n型半导体区802、分离层801和高浓度p型半导体区803在接近半导体基板31的前表面侧的区域中完成。

207.《分离层通过气隙和氧化膜的双重结构形成的情况下的制造方法》

208.接下来,将参考图22描述在分离层801具有气隙841和氧化硅膜842的双重结构的情况下的制造方法。注意,在图22中,仅示出对应于图17的a中所示的阴极接触点周围的区域831的部分。

209.首先,如图22的a所示,在半导体基板31的前表面侧的上表面上形成氧化硅膜891作为离子注入透过膜。此后,执行离子注入以在半导体基板31的前表面侧附近的区域中形成高浓度n型半导体区43、低浓度n型半导体区802和高浓度p型半导体区803。

210.接下来,如图22的b所示,执行干法蚀刻以在分离层801的形成位置处形成开口892。该步骤与图21的c类似,但是处于去除了诸如氮化硅膜的硬掩模的状态。

211.接着,如图22的c所示,例如通过cvd在开口892的底面和侧壁上形成氧化硅膜891a。此时,通过调整气体流量,能够以阶梯覆盖率不均匀的方式沉积氧化硅膜891a,并且通过增加在开口892的上拐角处的沉积量,如图22的d所示,氧化硅膜891b闭合并且形成空腔893。因此,空洞893对应于图18c中的空气间隙841,氧化硅膜891b对应于图18c中的氧化硅膜842。

212.通过上述步骤,高浓度n型半导体区43、低浓度n型半导体区802、分离层801和高浓度p型半导体区803在接近半导体基板31的前表面侧的区域中完成。

213.《11.像素的第七像素结构的变形例》

214.图23示出根据第七像素结构的像素10的第一变形例。

215.图23的a是示出第七像素结构的第一变形例的截面图,并且图23的b是沿着图23的a中的线x-x’截取的像素10的平面图。

216.当将图23中所示的第一变形例与根据图16中所示的第七像素结构的像素10进行比较时,高浓度p型半导体区803的形成区域不同,并且其他点是共同的。

217.即,在图16所示的第七像素结构中,高浓度p型半导体区803形成在从分离层801的外周壁表面到到达高浓度p型半导体区46的平面方向上的整个区域中。另一方面,在图23的第一变形例中,高浓度p型半导体区803被减少到从分离层801的外周壁表面到到达高浓度p型半导体区46之前的区域,并且n阱41形成在高浓度p型半导体区803和高浓度p型半导体区46之间。

218.如上所述,形成在相对于p型半导体区44的基板前表面侧上的高浓度p型半导体区803不需要形成在分离层801与高浓度p型半导体区46之间的平面方向上的整个区域中。然

而,为了防止在n阱41中光电转换的电子逸出到基板前表面侧,p型半导体区44需要形成在像素分离部811(的氧化硅膜813)内部的整个平面区域中。

219.图24的a是示出根据第七像素结构的像素10的第二变形例的截面图。

220.图24的a中所示的第二变形例与图23中所示的第一变形例相同之处在于,高浓度p型半导体区803形成在从分离层801的外周壁表面到到达高浓度p型半导体区46之前的区域中,并且n阱41形成在高浓度p型半导体区803与高浓度p型半导体区46之间。

221.另一方面,在图23所示的第一变形例中,高浓度p型半导体区803从基板前表面侧上的界面形成至p型半导体区44的深度,而在图24的a所示的第二变形例中,高浓度p型半导体区803不与基板前表面侧上的界面接触。在第二变形例中,高浓度p型半导体区803是从从基板前表面侧上的界面到p型半导体区44的深度的预定深度位置形成的。n阱41形成在从基板前表面侧上的界面到形成高浓度p型半导体区803的区域中。其他点与图23中示出的第一变形例的那些相似。

222.如上所述,高浓度p型半导体区803不必形成为与基板前表面侧上的界面接触。换言之,高浓度p型半导体区803可以形成在从基板前表面侧上的界面掩埋预定量的区域中。

223.图24的b是示出根据第七像素结构的像素10的第三变形例的截面图。

224.在图24的b所示的第三变形例中,高浓度p型半导体区803与图16所示的第七像素结构的高浓度p型半导体区803类似。即,高浓度p型半导体区803形成在从分离层801的外周壁表面到到达高浓度p型半导体区46的平面方向上的整个区域中。

225.另一方面,在图24的b中的第三变形例中,p型半导体区44的平面区域是从形成雪崩倍增区47的高浓度n型半导体区43下方到分离层801下方的区域,并且不在像素分离部811内部的整个平面区域中形成。其他点与图16中所示的第七像素结构的点相似。

226.如上所述,在高浓度p型半导体区803形成在与基板前表面侧上的界面接触的整个区域中的情况下,p型半导体区44可以不形成在整个平面区域中,并且可以是围绕以雪崩倍增区47为中心的分离层801的下侧的平面区域。

227.如上所述,如果高浓度p型半导体区803和p型半导体区44中的一个形成在像素10的像素分离部811内部的整个平面区域中,则另一个不需要形成在整个平面区域中。

228.如果高浓度p型半导体区803和p型半导体区44两者没有形成在整个平面区域中,如图25所示,在n阱41中光电转换的电子穿过既不形成高浓度p型半导体区803也不形成p型半导体区44的区域并且逸出到基板前表面侧。因此,通过在整个平面区域中形成高浓度p型半导体区803和p型半导体区44中的至少一个,可以将在n阱41中光电转换的电子移动至雪崩倍增区47,并且可以实现高pde。

229.《12.像素的第八像素结构》

230.图26的a是示出使用spad 21的像素10的第八像素结构的截面图,并且图26的b是沿着图26的a中的线x-x’截取的像素10的平面图。

231.在图26中,与图16中示出的第七像素结构相同的部分被给予相同的附图标记,并且将适当地省略对这些部分的描述。

232.根据图26中所示的第八像素结构的像素10与图16中所示的第七像素结构的不同之处在于还包括在形成在p型半导体区44的基板前表面侧上的高浓度p型半导体区803中的反射结构,并且在其他点上与图16中所示的第七像素结构相同。

233.例如,如图26所示,形成在高浓度p型半导体区803中的反射结构通过以预定间隔以栅格形状布置具有预定深度的多个支柱921来配置,所描述的多个支柱921不从基板前表面的界面到达p型半导体区44。在图26的b的平面图中,支柱921规则地布置,并且省略支柱921的一部分的图。另外,支柱921不必须规则地配置,也可以随机地配置。支柱921可以由与高浓度p型半导体区803不同的材料形成,例如,氧化硅膜。

234.根据第八像素结构,形成一种结构,其中,高浓度p型半导体区803和由氧化硅膜形成的支柱921的具有不同折射率的两个层在基板前表面侧上的界面处混合,并且从片上透镜816入射在n阱41上并且试图穿过到达基板前表面侧的光可以二次衍射并且限制在像素中。由此,可以进一步增加半导体基板31中的光电转换的入射光量,并且可以提高量子效率(qe)。

235.《13.像素的第九像素结构》

236.图27是示出使用spad 21的像素10的第九像素结构的截面图。图27示出两个相邻像素的截面图,并且点划线表示如图16等中的像素边界。

237.此外,在图27中,对与图16中所示的第七像素结构相同的部分给予相同的附图标记,并且将适当地省略对这些部分的描述。

238.根据图27中所示的第九像素结构的像素10与第七像素结构的不同之处在于省略了形成在图16中所示的第七像素结构中的像素边界部处的像素分离部811,并且在其他点上与图16中所示的第七像素结构相同。

239.图27中示出的像素10包括在形成雪崩倍增区47的高浓度n型半导体区43的外周上的分离层801,使得可以抑制在雪崩倍增区47中生成的辐射光的影响。因此,如在第九像素结构中,可以省略在像素边界部处的像素分离部811。由于省略了像素分离部811,因此能够消除构成像素分离部811的金属dti 812对入射光的吸收,从而能够进一步提高pde。

240.《14.像素的第十像素结构》

241.图28的a是示出使用spad 21的像素10的第十像素结构的截面图,并且图28的b是沿着图28的a中的线x-x’截取的像素10的平面图。此外,在图28中,点划线表示像素边界。

242.此外,在图28中,与图16中示出的第七像素结构相同的部分被给予相同的附图标记,并且将适当地省略对这些部分的描述。

243.根据图28中所示的第十像素结构的像素10具有其中根据图16中所示的第七像素结构的像素10的极性反转的结构。换言之,根据图16中所示的第七像素结构的像素10是读取电子作为信号电荷(载流子)的结构的示例,但是根据图28中所示的第十像素结构的像素10是读取空穴作为信号电荷的结构的示例。在这种情况下,连接至作为阴极的接触电极51的半导体区和连接至作为阳极的接触电极52的半导体区的导电类型相反。

244.更具体地,在接触电极51中形成高浓度p型半导体区1043代替高浓度n型半导体区43作为阴极,并且在接触电极52中形成高浓度n型半导体区1046代替高浓度p型半导体区46作为阳极。

245.在图28的b的平面图中,杂质浓度低于高浓度p型半导体区1043的杂质浓度的低浓度p型半导体区1802形成在高浓度p型半导体区1043的外周上。分离层801形成在低浓度p型半导体区1802的外周上。在分离层801的另一外周上,形成高浓度n型半导体区1803代替高浓度p型半导体区803。

246.如图28的a所示,n型半导体区1044在高浓度p型半导体区1043、低浓度p型半导体区1802、分离层801和高浓度n型半导体区1803的形成区域下方的整个平面区域中以预定厚度形成,并且雪崩倍增区47由形成在高浓度p型半导体区1043与形成在其下方的n型半导体区1044之间的结区中的耗尽层形成。

247.此外,从作为阴极的接触电极51施加到高浓度p型半导体区1043的电压和从作为阳极的接触电极52施加到高浓度n型半导体区1046的电压也是相反的。即,从作为阴极的接触电极51向高浓度p型半导体区1043施加电源vspad,从作为阳极的接触电极52向高浓度n型半导体区1046施加电源电压ve。

248.根据图28中的第十像素结构的像素10的其他配置与根据图16中所示的第七像素结构的像素10的配置类似,因此将省略其描述。

249.根据图28中的第十像素结构的像素10的效果与在图16中示出的第七像素结构中描述的效果相似。

250.如上所述,在图3中示出的第一像素结构的描述中,已经描述了信号电荷(载流子)可以是电子或空穴,但是这不限于第一像素结构,并且电子或空穴可以是上述第二至第九像素结构中的任一个中的信号电荷。

251.《15.堆叠结构的配置示例》

252.使用spad 21的多个像素10形成在其中的光接收元件可以使用一个半导体基板形成或者可以通过堆叠多个半导体基板形成。

253.图29是示出在通过堆叠两个半导体基板形成光接收元件的情况下的堆叠结构的示例的截面图。

254.图29中的像素10通过粘合第一基板201和第二基板202形成。第一基板201包括由硅等形成的半导体基板31和配线层212。另一方面,第二基板202包括由硅等形成的半导体基板311和布线层312。第一基板201和第二基板202之间的接合表面由单点划线表示。

255.在下文中,布线层212将被称为传感器侧布线层212,以便容易地与在第二基板202侧上的布线层312区分开。第二基板202侧上的配线层312将被称为逻辑侧配线层312。传感器侧布线层212相对于半导体基板31形成在其上的表面是前表面,并且在附图中,传感器侧布线层212未形成在其上的下表面是半导体基板31的后表面并且是入射光入射在其上的光接收表面。由于半导体基板31的结构类似于图3中所示的第一像素结构,因此将省略其描述。

256.传感器侧布线层212包括接触电极51、接触电极52、金属焊盘331、金属焊盘332和层间绝缘膜333。金属焊盘331通过诸如cu-cu的金属接合而电和物理地连接至逻辑侧布线层312的金属焊盘351。金属焊盘332通过诸如cu-cu的金属接合而电和物理地连接至逻辑侧布线层312的金属焊盘352。

257.在附图中,多个mos晶体管tr(tr1、tr2等)和逻辑侧配线层312形成在作为下侧的半导体基板311的前表面侧上。逻辑侧布线层312包括金属焊盘351、金属焊盘352和层间绝缘膜353。

258.金属焊盘351通过cu-cu等的金属接合而电连接并物理连接到传感器侧布线层212的金属焊盘331。金属焊盘352通过cu-cu等的金属接合而与传感器侧布线层212的金属焊盘332电连接、物理连接。

259.在第二基板202上,形成在半导体基板311上的多个mos晶体管tr和多个金属布线(未示出)层形成例如控制像素10的信号读取的读取控制电路(诸如恒流源22、晶体管23和反相器24(图1))以及对应于像素驱动部511、mux 513、时间测量部514(图31)的逻辑电路等。

260.利用这种配线结构,例如,供应至像素10的spad 21的阳极的电源vspad经由逻辑侧配线层312的金属焊盘352、传感器侧配线层212的金属焊盘332以及接触电极52被供应至高浓度p型半导体区46。此外,供应至像素10的spad 21的阴极的电源电压ve经由逻辑侧布线层312的金属焊盘351、传感器侧布线层212的金属焊盘331以及接触电极51被供应至高浓度n型半导体区43。

261.在图29的示例中,已经描述了采用图3所示的第一像素结构具有堆叠结构的示例,但不用说,其他第二像素结构至第十像素结构可以类似地具有堆叠结构。

262.《16.执行有源消光的像素电路》

263.图1中示出的像素10的电路配置是执行无源消光的无源电路的配置,但是也可采用执行有源消光、有源充电以及截止的有源电路的配置。

264.图30示出像素10的电路配置作为有源电路,该有源电路执行有源消光、有源充电以及抑制。

265.除了与图1中的那些相似的spad 21、恒流源22、晶体管23、以及反相器24之外,图30中的像素10还包括反相器401、可变反相器402、nor电路403、反相器404、以及p型mos晶体管405。

266.从反相器24输出的检测信号pfout也被输入至反相器401和可变反相器402。反相器401反转并输出检测信号pfout,并且在预定时间过去之后,可变反相器402反转并输出检测信号pfout。

267.nor电路403执行反相器401和可变反相器402的或非(nor)操作,并且将执行结果输出到反相器404和晶体管23的栅极。反相器404使nor电路403的输出反相,并将反相的输出输出到p型mos晶体管的栅极。

268.在图30的像素10中,雪崩倍增发生,并且在自输出高(hi)检测信号pfout起已经过去由可变反相器402确定的预定时间之后,从nor电路403输出的保持脉冲(hold_pulse)变成高。通过高的保持脉冲,晶体管23被导通并且连接到gnd以执行有源淬灭,并且p型mos晶体管405被导通以将阴极电压vs维持(保持)在0v(gnd)。

269.当在高的保持脉冲被保持预定时间之后由保持控制电路(未示出)将高的保持脉冲控制为低(lo)时,晶体管23和p型mos晶体管405截止,使得阴极电压vs再次返回至原始电源电压ve,使得其能够检测下新的光子(主动再充电操作)。

270.如在图1的无源电路的情况下,通过控制保持脉冲以开启和关闭晶体管23的保持控制电路(未示出)执行将像素10设定为有源像素或无源像素的控制。

271.用于执行有源消光和有源充电的反相器401、可变反相器402、nor电路403、反相器404和p型mos晶体管405是控制像素10的信号读取的读取控制电路的一部分。

272.《17.光接收元件的配置示例》

273.根据上述第一至第十像素结构的像素10可以应用于例如图31中示出的光接收元件的像素。

274.图31是包括上述像素10的光接收元件的框图。

275.图31中的光接收元件501包括像素驱动部511、像素阵列512、多路复用器(mux)513、时间测量部514以及输入输出部515。

276.像素阵列512具有这样的配置,其中,检测光子的入射并输出指示检测结果的检测信号pfout的像素521在行方向和列方向上以矩阵二维布置。此处,行方向是指像素行中的像素521的排列方向,即,水平方向,并且列方向是指像素列中的像素521的排列方向,即,垂直方向。在图31中,由于纸表面限制,以10行和12列的像素阵列配置示出像素阵列512,但是像素阵列512的行数和列数不限于此,并且是任意的。

277.像素驱动线522相对于像素阵列512的矩阵状像素阵列沿着每个像素行的水平方向布线。像素驱动线522传输用于驱动像素521的驱动信号。像素驱动部511通过经由像素驱动线522将预定驱动信号提供给每个像素521来驱动每个像素521。具体地,像素驱动部511进行控制,使得在与经由输入输出部515从外部提供的发光定时信号对应的预定定时,二维地布置成矩阵形式的多个像素521中的一部分像素521被设置为有效像素并且其余像素521被设置为非有源像素。有源像素是检测光子的入射的像素,而无源像素是不检测光子的入射的像素。作为像素521的配置,可以采用上述像素10的第一至第十像素结构中的任一个。

278.应注意,在图31中,像素驱动线522被示出为一条配线,但可包括多条配线。像素驱动线522的一端连接至与像素驱动部511的每个像素行对应的输出端子。

279.mux 513根据像素阵列512中的有效像素和非有源像素之间的切换来选择来自有效像素的输出。然后,mux 513将从所选择的有效像素输入的像素信号输出到时间测量部514。

280.基于从mux 513提供的有源像素的像素信号和表示发光源(图32中的光源632)的发光定时的发光定时信号,时间测量部514生成对应于从发光源发光时到有源像素接收光时的时间的计数值。经由输入输出部515从外部(图32中的成像装置622的控制部642)提供发光定时信号。

281.输入输出部515将从时间测量部514提供的有源像素的计数值作为像素信号输出到外部(图32中的信号处理电路653)。此外,输入输出部515将从外部提供的发光定时信号提供给像素驱动部511和时间测量部514。

282.《18.测距系统的配置示例》

283.图32是示出包含图31的光接收元件501的测距系统的实施方式的配置示例的框图。

284.测距系统611例如是使用tof方法捕获距离图像的系统。这里,距离图像是由距离像素信号形成的图像,该距离像素信号基于通过针对每个像素检测深度方向上从测距系统611到对象的距离而检测的距离。

285.测距系统611包括照明装置621和成像装置622。

286.照明装置621包括照明控制部631和光源632。

287.照明控制部631在成像装置622的控制部642的控制下控制光源632发光的图案。具体地,照明控制部631根据从控制部642提供的照射信号中包括的照射代码控制光源632发射光的图案。例如,照射代码具有1(高)和0(低)两个值,并且当照射代码的值是1时,照明控制部631打开光源632,并且当照射代码的值是0时,关闭光源632。

288.光源632在点亮控制部631的控制下发射预定波长区域内的光。光源632包括例如红外激光二极管。注意,光源632的类型和照射光的波长范围可以根据测距系统611的应用等任意设置。

289.成像装置622是通过反射由被摄体612、被摄体613等从照明装置621发射的光(照射光)而获得的反射光的装置。成像装置622包括成像部641、控制部642、显示部643以及存储部644。

290.成像部641包括透镜651、光接收元件652和信号处理电路653。

291.透镜651在光接收元件652的光接收表面上形成入射光的图像。应注意,透镜651的配置是任意的,并且例如,透镜651可由多个透镜组配置。

292.例如,光接收元件652包括使用每个像素的spad的传感器。在控制部642的控制下,光接收元件652接收来自被摄体612、被摄体613等的反射光,并且将所获得的像素信号作为结果提供给信号处理电路653。该像素信号表示通过对从照明装置621发射照射光的时间到光接收元件652接收照射光的时间进行计数而获得的数字计数值。指示光源632发光的定时的发光定时信号也从控制部642提供到光接收元件652。作为光接收元件652的配置,采用包括上述像素10的图31中的光接收元件501。

293.信号处理电路653在控制部642的控制下处理从光接收元件652提供的像素信号。例如,信号处理电路653基于从光接收元件652提供的像素信号检测每个像素到对象的距离,并且生成指示每个像素到对象的距离的距离图像。具体而言,信号处理电路653按每个像素获取从光源632发光到光接收元件652的每个像素接收光多次(例如,几千到几万次)的时间(计数值)。信号处理电路653生成与所获取的时间对应的直方图。然后,通过检测直方图的峰值,信号处理电路653确定直到从光源632发射的光被被摄体612或被摄体613反射并返回的时间。此外,信号处理电路653基于所确定的时间和光速执行算术运算以获得到物体的距离。信号处理电路653将生成的距离图像提供至控制部642。

294.例如,控制部642包括诸如现场可编程门阵列(fpga)或数字信号处理器(dsp)的控制电路、处理器等。控制部642控制照明控制部631和光接收元件652。具体地,控制部642将照射信号提供至照明控制部631并且将发光定时信号提供至光接收元件652。光源632根据照射信号发射照射光。发光定时信号可以是提供给照明控制部631的照射信号。此外,控制部642将从成像部641获取的距离图像提供至显示部643并且使显示部643显示距离图像。此外,控制部642将从成像部641获取的距离图像存储在存储部644中。此外,控制部642将从成像部641获取的距离图像输出到外部。

295.显示部643包括例如面板型显示装置,诸如液晶显示装置或有机电致发光(el)显示装置。

296.存储部644可以包括任意存储装置、存储介质等,并且存储距离图像等。

297.通过采用如上所述的光接收元件501和测距系统611中的像素10的上述结构,可以在防止边缘破裂的同时生成并输出实现高pde(光子检测效率)的距离图像。

298.《19.电子装置的应用例》

299.例如,上述测距系统611可安装在电子设备上,诸如,智能电话、平板终端、移动电话、个人电脑、游戏机、电视接收器、可佩戴终端、数码照相机、以及数码摄像机。

300.图33是示出作为配备有测距系统611的电子设备的智能电话的配置示例的框图。

301.如图33所示,通过经由总线711连接测距模块702、成像装置703、显示器704、扬声器705、麦克风706、通信模块707、传感器单元708、触摸面板709以及控制单元710来配置智能电话701。此外,控制单元710具有通过cpu执行程序而作为应用处理部721和操作系统处理部722的功能。

302.图32中的测距系统611应用于测距模块702。例如,测距模块702布置在智能电话701的前面,并为智能电话701的用户执行测距,从而可输出用户的面部、手、手指等的表面形状的深度值作为测距结果。

303.成像装置703布置在智能电话701的前方并且以智能电话701的用户为对象执行成像,从而获取其中捕获用户的图像。注意,虽然未示出,但是成像装置703也可布置在智能电话701的后表面上。

304.显示器704显示用于执行应用处理部721和操作系统处理部722的处理的操作画面、由成像装置703捕获的图像等。例如,当使用智能电话701进行呼叫时,扬声器705和麦克风706输出另一方的语音并收集用户语音。

305.通信模块707经由通信网络执行通信。传感器单元708感测速度、加速度、接近等,并且触摸面板709获取用户在显示器704上显示的操作屏幕上的触摸操作。

306.应用处理部721执行用于通过智能电话701提供各种服务的处理。例如,应用处理部721可以执行以下处理:基于从测距模块702提供的深度图,通过计算机图形创建虚拟再现用户的表情的面部,并且在显示器704上显示该面部。此外,应用处理部721例如能够基于从测距模块702提供的深度图来进行生成任意的三维物体的三维形状数据的处理。

307.操作系统处理部722进行用于实现智能电话701的基本功能和操作的处理。例如,操作系统处理部722可基于从测距模块702提供的深度图执行认证用户脸部和解锁智能电话701的处理。此外,操作系统处理部722可执行例如基于从测距模块702提供的深度图识别用户手势的处理和根据手势输入各种操作的处理。

308.在如上所述配置的智能电话701中,例如,可以通过应用上述测距系统1以高精确度和高速度生成深度图。因此,智能电话701可更准确地检测测距信息。

309.《20.移动体的应用例》

310.根据本公开的技术(本技术)可应用于各种产品。例如,根据本公开的技术可实现为安装在任何类型的移动对象(诸如汽车、电动车辆、混合电动车辆、摩托车、自行车、个人移动性、飞机、无人机、船舶、机器人等)上的装置。

311.图34是示出作为可以应用根据本公开内容的技术的移动体控制系统的示例的车辆控制系统的示意性配置示例的框图。

312.车辆控制系统12000包括经由通信网络12001连接的多个电子控制单元。在图34所示的示例中,车辆控制系统12000包括驱动系统控制单元12010、车身系统控制单元12020、车外信息检测单元12030、车内信息检测单元12040和集成控制单元12050。此外,作为集成控制单元12050的功能配置,示出微计算机12051、声音图像输出部12052和车载网络接口(i/f)12053。

313.驱动系统控制单元12010根据各种程序控制与车辆的驱动系统相关的装置的操作。例如,驱动系统控制单元12010用作用于产生车辆的驱动力的驱动力产生装置(诸如内燃机、驱动马达等)、用于将驱动力传递到车轮的驱动力传递机构、用于调节车辆的转向角

的转向机构、用于产生车辆的制动力的制动装置等的控制装置。

314.车身系统控制单元12020根据各种程序来控制安装在车身上的各种装置的操作。例如,车身系统控制单元12020用作用于无钥匙进入系统、智能钥匙系统、电动车窗装置或诸如前照灯、后备灯、制动灯、转向信号、雾灯等的各种灯的控制装置。在这种情况下,从作为按键的替代物的移动装置发送的无线电波或各种开关的信号可以被输入到车身系统控制单元12020。车身系统控制单元12020接收这些输入的无线电波或信号,并且控制车辆的门锁装置、电动车窗装置、灯等。

315.车外信息检测单元12030检测包含车辆控制系统12000的车外的信息。例如,在车外信息检测单元12030上连接有成像部12031。车外信息检测单元12030使成像部12031拍摄车外的图像,并接收所拍摄的图像。另外,车外信息检测单元12030也可以基于接收到的图像,进行检测人、车辆、障碍物、标志、路面上的文字等对象物的处理、或者检测其距离的处理等。

316.成像部12031是接收光并且输出对应于接收到的光的光量的电信号的光学传感器。成像部12031可以输出电信号作为图像,或者可以输出电信号作为关于测量距离的信息。此外,成像部12031接收的光可以是可见光,或者可以是诸如红外线等不可见光。

317.车内信息检测单元12040检测关于车辆内部的信息。车内信息检测单元12040例如与检测驾驶员的状态的驾驶员状态检测部12041连接。驾驶员状态检测部12041例如包括拍摄驾驶员的相机。基于从驾驶员状态检测部12041输入的检测信息,车内信息检测单元12040可以计算驾驶员的疲劳度或驾驶员的集中度,或者可以确定驾驶员是否打瞌睡。

318.微计算机12051可以基于由车外信息检测单元12030或车内信息检测单元12040获得的关于车辆内部或外部的信息来计算驱动力生成装置、转向机构或制动装置的控制目标值,并且向驱动系统控制单元12010输出控制命令。例如,在基于车间距离、车速维持行驶、车辆碰撞警告或车道偏离警告等行驶之后,为了实现包括车辆碰撞避免或冲击减轻的高级驾驶员辅助系统(adas)的功能,微计算机12051可以执行协作控制。

319.另外,微计算机12051基于由车外信息检测单元12030或车内信息检测单元12040取得的车外信息或车内信息,通过控制驱动力产生装置、转向机构、制动装置等,能够进行不依赖于驾驶员的操作等而自主行驶的自动驾驶用的协调控制。

320.另外,微计算机12051可以基于由车外信息检测单元12030获得的关于车外的信息,将控制命令输出到车身系统控制单元12020。例如,微计算机12051可以根据车外信息检测单元12030检测到的前方车辆或对面车辆的位置,进行用于防眩光的协作控制,例如控制前照灯以从远光改变到近光。

321.声音图像输出部12052向能够视觉或听觉地向车辆的乘员或车辆外部通知信息的输出装置发送声音和图像中的至少一者的输出信号。在图34的示例中,音频扬声器12061、显示部12062和仪表板12063被示为输出设备。例如,显示部12062可包括板上显示器或平视显示器中的至少一个。

322.图35为示出成像部12031的安装位置的一个示例的图。

323.在图35中,车辆12100包括成像部12101、12102、12103、12104和12105作为成像部12031。

324.成像部12101、12102、12103、12104和12105例如设置在车辆12100的车厢中的诸如

前鼻、侧视镜、后保险杠、后门、以及挡风玻璃的上部的位置处。设置在车辆内部内的前鼻部的成像部12101和设置在挡风玻璃的上部的成像部12105主要获得车辆12100的前方的图像。设置在侧视镜中的成像部12102和12103主要获得车辆12100的侧面的图像。设置到后保险杠或后门的成像部12104主要获得车辆12100的后部的图像。通过成像部12101和12105获得的前方图像主要用于检测前方车辆、行人、障碍物、交通灯、交通标志、车道等。

325.顺便提及,图35示出成像部12101至12104的拍摄范围的示例。成像范围12111表示设置在前鼻部上的成像部12101的成像范围,成像范围12112和12113分别表示设置在侧视镜上的成像部12102和12103的成像范围,并且成像范围12114表示设置在后保险杠或后门中的成像部12104的成像范围。例如,通过重叠由成像部12101至12104捕获的图像数据,可获得从上方观看的车辆12100的俯视图像。

326.成像部12101至12104中的至少一个可具有获得距离信息的功能。例如,成像部12101至12104中的至少一个可以是由多个成像元件构成的立体相机,或者可以是具有用于相位差检测的像素的成像元件。

327.例如,微计算机12051可以基于从成像部12101至12104获得的距离信息确定在成像范围12111至12114内到每个三维物体的距离以及该距离的时间变化(相对于车辆12100的相对速度),由此,抽出存在于车辆12100的行驶路径上、以与车辆12100大致相同的方向以规定的速度(例如0km/小时以上)行驶的最近的三维物体来作为前方车辆。另外,微计算机12051可以预先设定跟随距离以保持在前行车辆的前方,并且执行自动制动控制(包括跟随停止控制)、自动加速控制(包括跟随起动控制)等。由此,能够进行不依赖于驾驶员的操作等而自主行驶的自动驾驶用的协调控制。

328.例如,微计算机12051可以基于从成像部12101至12104获得的距离信息,将关于三维物体的三维物体数据分类为二轮车、标准车辆、大型车辆、行人、电线杆和其他三维物体的三维物体数据等,提取分类的三维物体数据,并且将所提取的三维物体数据用于自动躲避障碍物。例如,微计算机12051将车辆12100周围的障碍物识别为车辆12100的驾驶员可以视觉识别的障碍物和车辆12100的驾驶员难以视觉识别的障碍物。然后,微计算机12051确定表示与每个障碍物碰撞的风险的碰撞风险,并且当碰撞风险等于或高于设定值并且有可能碰撞时,微计算机12051可以经由音频扬声器12061和显示部12062向驾驶员输出警报,或经由驾驶系统控制单元12010执行强制减速或躲避转向,从而对用于防碰撞的驾驶进行辅助。

329.成像部12101至12104中的至少一个可以是检测红外线的红外相机。微计算机12051例如可以通过确定在成像部12101至12104的拍摄图像中是否存在行人来识别行人。行人的这种识别例如通过提取作为红外照相机的成像部12101至12104的成像图像中的特征点的过程以及通过对表示对象的轮廓的一系列特征点执行图案匹配处理来确定是否是行人的过程来执行。当微计算机12051确定在成像部12101到12104的成像图像中存在行人并因此识别出行人时,声音图像输出部12052控制显示部12062,使得用于强调的正方形轮廓线被显示为叠加在识别出的行人上。声音图像输出部12052还可控制显示部12062,使得在期望位置处显示表示行人的图标等。

330.上面已经描述了可以应用根据本公开的技术的车辆控制系统的示例。根据本公开的技术可以应用于上述配置之中的车外信息检测单元12030和车内信息检测单元12040。具

体而言,通过作为车外信息检测单元12030和车内信息检测单元12040使用测距系统1的测距,能够执行识别驾驶员的手势的处理,根据该手势执行各种操作(例如,音频系统、导航系统和空调系统),并且更精确地检测驾驶员的状态。另外,能够利用测距系统1的测距来识别路面的凹凸,并且将该凹凸反映在悬架的控制中。

331.本技术的实施方式不限于上述实施方式,并且在不背离本技术的主旨的情况下,各种修改是可能的。

332.在本说明书中已经描述的多种本技术可以各自独立地实现为单个单元,只要不发生矛盾。当然,还可以组合地使用和实施任何多种本技术。此外,上述任何技术的部分或全部可通过与上面未描述的另一技术一起使用来实现。

333.此外,例如,描述为一个装置(或处理单元)的配置可以被划分和配置为多个装置(或处理单元)。相反,上述作为多个装置(或处理单元)的配置可被组合和配置为一个装置(或处理单元)。此外,除了上述配置之外的配置当然可以被添加到每个装置(或每个处理单元)的配置。此外,如果整个系统的配置和操作基本相同,则特定装置(或处理单元)的配置的一部分可包括在另一装置(或另一处理单元)的配置中。

334.此外,在本说明书中,系统意味着一组多个部件(装置、模块(零件)等),并且所有部件是否在同一壳体中无关紧要。因此,容纳在分开的壳体中并且经由网络连接的多个装置和其中多个模块容纳在一个壳体中的单个装置都是系统。

335.应注意,在本说明书中描述的效果仅是示例并且不受限制,并且可以提供除了在本说明书中描述的那些效果之外的效果。

336.应注意,本技术可具有以下配置。

337.(1)

338.一种光接收元件,包括:

339.像素,在所述像素中,在第一导电类型的第一半导体区和与所述第一半导体区相对的第二导电类型的第二半导体区接合的区域中形成倍增区,并且形成在比所述第一半导体区更靠近光接收表面的位置处的所述第二半导体区的平面区域更大。

340.(2)

341.根据以上(1)所述的光接收元件,其中,

342.所述像素还包括位于所述光接收表面和所述像素的边界部附近的侧表面上的所述第二导电类型的第三半导体区。

343.(3)

344.根据以上(2)所述的光接收元件,其中,

345.所述第二半导体区形成为直到形成在所述像素的所述边界部附近的所述侧表面上的所述第三半导体区。

346.(4)

347.根据以上(2)或(3)所述的光接收元件,还包括

348.所述第一导电类型的第四半导体区,设置在所述第二半导体区与形成在所述像素的所述边界部附近的所述侧表面上的所述第三半导体区之间。

349.(5)

350.根据以上(2)至(4)中任一项所述的光接收元件,其中

351.所述像素还包括固定电荷膜,所述固定电荷膜在所述第三半导体区外部的表面上具有固定电荷。

352.(6)

353.根据以上(2)至(5)中任一项所述的光接收元件,其中

354.所述像素还包括像素分离部,所述像素分离部在所述第三半导体区外部的所述像素边界部处将所述像素彼此分离。

355.(7)

356.根据以上(6)所述的光接收元件,其中,

357.将预定电压施加至所述像素分离部。

358.(8)

359.根据以上(2)至(7)中任一项所述的光接收元件,还包括

360.分离层,在所述第一半导体区的第一接触部与所述第三半导体区的第二接触部之间,电分离第一接触部与第二接触部,所述第一接触部连接至阳极和阴极中的一电极,并且所述第二接触部连接至另一电极。

361.(9)

362.根据以上(8)所述的光接收元件,还包括

363.所述第二导电类型的第五半导体区,设置在所述分离层与所述第三半导体区之间。

364.(10)

365.根据以上(8)或(9)所述的光接收元件,还包括

366.第六半导体区,在所述第一半导体区与所述分离层之间,具有与所述第一半导体区相同的导电类型,并且具有比所述第一半导体区更低的杂质浓度。

367.(11)

368.根据以上(9)所述的光接收元件,还包括

369.反射结构,在所述第五半导体区的区域中由与所述第五半导体区的材料不同的材料形成。

370.(12)

371.根据以上(2)至(8)中任一项所述的光接收元件,其中

372.所述第一半导体区的连接至阳极和阴极中的一个电极的第一接触部和所述第三半导体区的连接至另一电极的第二接触部被布置在不同的深度位置处。

373.(13)

374.根据以上(1)至(8)中任一项所述的光接收元件,还包括

375.所述第一导电类型的第四半导体区、以及具有与所述第四半导体区相同的导电类型的第五半导体区,并且所述第五半导体区在比所述第二半导体区更靠近所述光接收表面的位置处具有比所述第四半导体区更低的杂质浓度。

376.(14)

377.根据以上(1)至(8)中任一项所述的光接收元件,还包括

378.第四半导体区,具有与所述第二半导体区相同的导电类型和比所述第二半导体区更低的杂质浓度;以及第五半导体区,在比所述第二半导体区更靠近所述光接收表面的位

置处具有与所述第四半导体区不同的导电类型。

379.(15)

380.根据以上(1)至(14)中任一项所述的光接收元件,其中,

381.所述第一半导体区的平面形状是圆形。

382.(16)

383.根据以上(1)至(15)中任一项所述的光接收元件,其中,

384.所述第一半导体区的直径是2μm或更小。

385.(17)

386.根据以上(1)至(16)中任一项所述的光接收元件,其中,

387.所述第一半导体区和所述第二半导体区在深度方向上的相对距离是1000nm或更小。

388.(18)

389.根据以上(1)至(17)中任一项所述的光接收元件,其中

390.所述第一半导体区和所述第二半导体区中的每个的杂质浓度是1e+16/cm3或更大。

391.(19)

392.根据以上(1)至(18)中任一项所述的光接收元件,其中

393.堆叠有第一半导体基板和第二半导体基板的堆叠结构,

394.所述第一半导体区和所述第二半导体区形成在所述第一半导体基板中,以及

395.控制所述像素的信号读取的读取控制电路形成在所述第二半导体基板上。

396.(20)

397.一种测距系统,包括:

398.照明装置,发射照射光;以及

399.光接收元件,接收通过由被摄体反射所述照射光而获得的反射光,其中,

400.所述光接收元件包括:

401.像素,在所述像素中,在第一导电类型的第一半导体区和与所述第一半导体区相对的第二导电类型的第二半导体区接合的区域中形成倍增区,所述第二半导体区的平面区域形成得更大,并且形成在比所述第一半导体区更靠近光接收表面的位置处的所述第二半导体区的平面区域更大。

402.附图标记列表

403.10 像素

404.21 spad

405.22 恒流源

406.23 晶体管

407.24 反相器

408.31 半导体基板

409.41 n阱

410.42 n型半导体区

411.43 高浓度n型半导体区

412.44、44

’ꢀ

p型半导体区

413.45 空穴蓄积区

414.46 高浓度p型半导体区

415.47 雪崩倍增区

416.48 像素分离部

417.101 像素间沟槽部

418.102 绝缘层

419.121 固定充电膜

420.141 绝缘层

421.161 导电构件

422.162 绝缘膜

423.201 第一基板

424.202 第二基板

425.311 半导体基板

426.401 反相器

427.402 可变反相器

428.403 nor电路

429.404 反相器

430.405 mos晶体管

431.501 光接收元件

432.521 像素

433.611 测距系统

434.621 照明装置

435.622 成像装置

436.652 光接收元件

437.701 智能电话

438.702 测距模块

439.801 分离层

440.802 低浓度n型半导体区

441.803 高浓度p型半导体区

442.811 像素分离部

443.812 金属dti

444.813 氧化硅膜

445.816 片上透镜

446.841 气隙

447.842 氧化硅膜

448.921 支柱。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1