功率半导体器件的制作方法

本公开涉及功率半导体器件。更具体但不排他地,本公开涉及具有绝缘沟槽的沟槽栅极功率半导体器件。

背景技术:

1、功率半导体器件(例如,绝缘栅双极型晶体管(igbts))已广泛用作各种功率应用中的功率开关。igbt的重要工作参数通常包括集电极和发射极之间的导通状态压降(vce,sat)、开关损耗(esw)和安全工作区(soa)。vce,sat和esw表示igbt的效率,而soa表示igbt的可靠性。

2、一般来说,有两种常见的igbt结构。一种类型被称为平面栅极igbt,其中在晶圆的表面上提供栅极电极。另一种类型被称为沟槽栅极igbt,其中在晶圆中形成沟槽结构,并且在沟槽结构中掩埋栅极电极。沟槽栅极igbt具有垂直于晶圆表面的mos通道,并且垂直的mos通道有效地消除了平面栅极结构中的jfet效应。同时,由于mos通道的密度不受芯片表面积的限制,通道密度可以被大大提高。以此方式,与平面栅极igbt相比,沟槽栅极igbt可以提供增加的通道密度,并相应地减少导通状态压降vce,sat。然而,沟槽栅极igbt由于其高饱和集电极电流密度而具有较差的短路电流能力或较差的短路soa(scsoa)。因此,在最近的沟槽栅极技术中,采用了虚设区域来优化vce,sat和scsoa之间的折衷性能,而不牺牲反向阻断电压。

3、虚设区域(包括虚设沟槽以及虚设沟槽之间的虚设阱)引入了额外的寄生电容和更多的空间来存储自由电子-空穴载流子,以当器件截止或导通时,这些电子-空穴载流子需要移出或涌入。据报道,虚设沟槽可以电连接到沟槽栅极igbt的有源栅极电极,但是这种连接类型将由于增加的栅极-集电极电容(cgc)而导致大的开关损耗。还已知的是,虚设沟槽可以电连接到igbt的发射极电极,但是这种连接类型将提高导通切换速度(由集电极电流的变化速率di/dt表示),并通过改变栅极电阻器rg,on而导致不可控的di/dt。

4、因此,通常需要折衷igbt的一个工作参数以改进igbt的另一工作参数。其他类型的功率半导体器件也存在类似的问题。

5、通常希望提供一种具有改进的器件效率以及改进的可靠性的功率半导体器件。

技术实现思路

1、本公开的目的之一是提供一种改进的功率半导体器件,其解决了与已知结构相关的问题,无论是在本文中还是在其他方面。

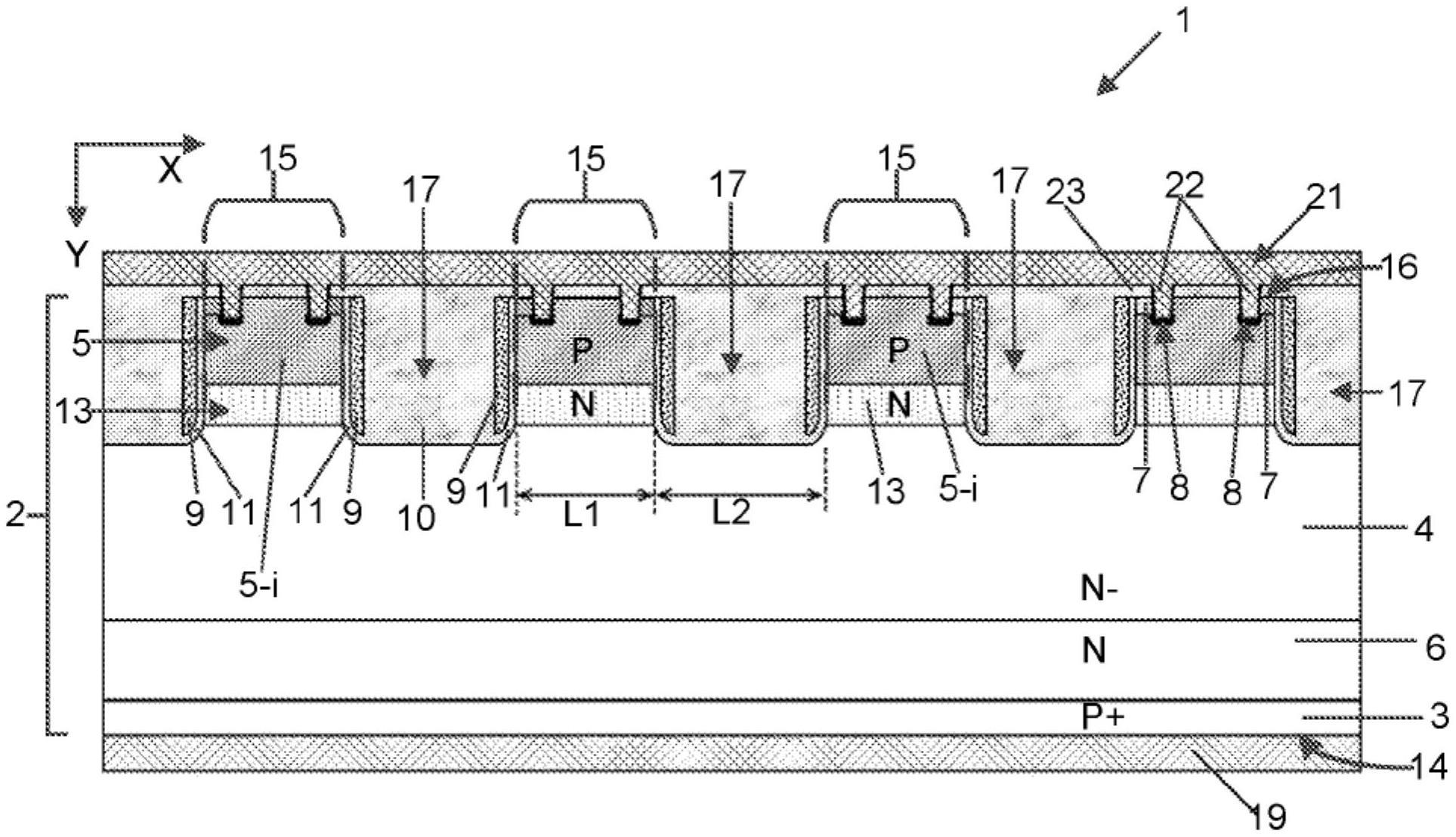

2、根据本公开的第一方面,提供了一种功率半导体器件,包括:

3、半导体衬底,其包括:

4、基极层,其选择性地设置在半导体衬底的第一侧,并且其中,基极层具有第一导电类型;

5、集电极层,其设置在半导体衬底的第二侧,其中,第二侧与第一侧相对,并且其中,集电极层具有第一导电类型;以及

6、漂移层,其具有与第一导电类型相反的第二导电类型,其中,漂移层布置在集电极层和基极层之间;

7、有源单元,其设置在半导体衬底中,其中,有源单元包括具有第二导电类型的发射极区和作为基极层的一部分的有源基极区;以及

8、绝缘沟槽,其设置在半导体衬底中并与有源单元相邻,其中:绝缘沟槽沿着第一方向从半导体衬底的第一侧的表面延伸到漂移层中;绝缘沟槽包括设置在其中的栅极电极和介电材料;以及栅极电极被配置为控制有源单元内的电流通道的导通/截止状态;

9、其中,有源单元沿着垂直于第一方向的第二方向具有第一长度l1,并且绝缘沟槽沿着第二方向具有第二长度l2,并且第一长度l1和第二长度l2还满足0.5≤l2/l1≤2的关系。

10、与相邻有源单元提供虚设半导体区的功率半导体器件(例如,igbt)的现有设计相比,使用第一方面的绝缘沟槽来代替至少一部分的虚设半导体区,在提供类似水平的电流密度时,对于改善soa和开关可控性以及降低功率半导体器件的开关损耗和emi噪声是有利的。有源单元的长度l1和绝缘沟槽的长度l2遵循设计规则0.5≤l2/l1≤2,这对于保持芯片正面的均匀电场分布(从而提高器件的可靠性)和保持过程均匀性和可控性是有用的。l2/l1是指第二长度l2与第一长度l1的比值。

11、应当理解,有源单元是指能够在整个功率半导体器件中传导电流的最小重复单元,并且有源单元被配置为在功率半导体器件的导通状态期间提供至少一个电流通道。由于栅极电极能够控制有源单元内的电流通道的导通/截止状态,因此栅极电极是有源栅极电极。应当理解,栅极电极被布置为与发射极区相邻,以便控制由有源单元提供的电流通道的导通/截止状态。

12、栅极电极可以沿着第一方向从半导体衬底的第一侧的表面延伸到半导体衬底中。

13、由有源单元提供的电流通道可以大致沿着第一方向。

14、介电材料的一部分可以充当发射极区和栅极电极之间的栅极绝缘层。

15、发射极区可以选择性地设置在半导体衬底的第一侧。优选地,第一长度l1和第二长度l2还可以满足l2/l1≤1.7的关系。更优选地,第一长度l1和第二长度l2还可以满足l2/l1≤1.5的关系。通过使l2/l1不大于2,优选地不大于1.7,最优选地不大于1.5,当器件反向偏置时,可以防止绝缘沟槽下的电场达到过高的水平,从而保护器件不损坏。

16、优选地,第一长度l1和第二长度l2还可以满足l2/l1≥1的关系。通过使l2/l1不低于0.5,更优选地不低于1,降低了器件承受高短路电流的风险,从而允许器件具有可接受的scsoa性能。

17、有源单元还可以包括设置在有源基极区和漂移层之间的第一注入区。第一注入区可以是第二导电类型,并且具有比漂移层更高的掺杂浓度。

18、有利地,第一注入区通过在导通状态期间增强漂移层中的载流子分布来改善功率半导体器件中的电导率调制,从而降低功率半导体器件的vce,sat。

19、功率半导体器件可以包括与有源单元相邻的另一绝缘沟槽。另一绝缘沟槽可以沿着第一方向从半导体衬底的表面延伸到漂移层中,并且可以包括设置在其中的栅极电极和介电材料。另一绝缘沟槽的栅极电极可以被配置为控制有源单元内的另一电流通道的导通/截止状态。

20、电流通道和另一电流通道可以布置在有源单元的相对侧。

21、栅极电极可以是第一栅极电极,并且绝缘沟槽可以包括第二栅极电极。第一栅极电极和第二栅极电极可以布置在绝缘沟槽的相对侧。

22、第二栅极电极可以是有源栅极电极或虚设栅极电极。

23、有源单元还可以包括虚设栅极沟槽,虚设栅极沟槽包括设置在其中的虚设栅极绝缘层和虚设栅极电极。

24、绝缘沟槽和虚设栅极沟槽可以沿着第一方向具有基本相同的深度。

25、有源单元可以包括多个虚设栅极沟槽。

26、有源单元的电流通道和另一电流通道可以设置在虚设栅极沟槽或多个虚设栅极沟槽的相对侧。

27、虚设栅极沟槽可以沿着第二方向布置在有源单元的中间。

28、功率半导体器件还可以包括发射极电极。发射极电极可以包括沿着第一方向延伸到基极层中的发射极接触沟槽。该发射极接触沟槽可以电连接到发射极区和虚设栅极电极。

29、发射极接触沟槽有利地简化了虚设栅极电极和发射极电极之间的电连接,并允许减小栅极电极和虚设栅极沟槽之间的最小距离,从而改善了功率半导体器件的电流密度和导通状态压降。发射极接触沟槽还有助于提高发射极电极的空穴收集能力,从而提高器件的soa性能。

30、在有源单元包括多个虚设栅极沟槽的情况下,发射极接触沟槽可以电连接到每个虚设栅极沟槽中的虚设栅极电极。

31、绝缘沟槽的栅极电极可以沿着第一方向具有比虚设栅极电极更大的长度。换言之,可以蚀刻虚设栅极沟槽以形成发射极接触沟槽。

32、发射极接触沟槽可以沿着第二方向具有比虚设栅极沟槽更大的长度。

33、在有源单元包括多个虚设栅极沟槽的情况下,发射极接触沟槽可以沿着第二方向具有比多个虚设栅极沟槽更大的长度。

34、发射极接触沟槽可以沿着第二方向布置在有源单元的中间。

35、功率半导体器件还可以包括在绝缘沟槽和漂移层之间的第二注入区,第二注入区具有第一导电类型。

36、特别地,第二注入区可以在绝缘沟槽的栅极电极和漂移层之间。

37、有利地,在功率半导体器件的导通状态期间,第二注入区保护栅极电极及其相关联的栅极绝缘层(由介电层提供)不受由集电极层注入的阻挡空穴的影响,并因此保护栅极电极和栅极绝缘层不受阻挡在集电极层上的空穴的俘获。结果,第二注入区提高了功率半导体器件的可靠性。此外,第二注入区为功率半导体器件提供更好的阻挡能力。

38、第二注入区可以电连接到发射极电极或浮置。

39、第二注入区也可以设置在虚设栅极沟槽和漂移层之间的有源单元内。

40、有利地,虚设栅极沟槽和漂移层之间的第二注入区为功率半导体器件提供更好的阻挡能力,并且可以电连接到发射极电极或浮置。

41、第二方向可以平行于半导体衬底的表面。

42、功率半导体器件还可以包括虚设单元。虚设单元可以包括虚设基极区,该虚设基极区是基极层的一部分。

43、应当理解,在功率半导体器件的导通状态期间,虚设单元不提供任何电流通道。

44、虚设单元可以不包括任何在虚设基极区内形成的发射极区。

45、虚设单元还可以包括虚设栅极沟槽,其包括设置在其中的虚设栅极绝缘层和虚设栅极电极。

46、虚设单元可以包括多个虚设栅极沟槽。

47、有源单元和虚设单元可以包括相同数量的虚设栅极沟槽。虚设单元沿着第二方向的长度可以等于第一长度l1。

48、第一注入区也可以设置在虚设基极区和漂移层之间的虚设单元内。

49、第二注入区也可以设置在虚设栅极沟槽和漂移层之间的虚设单元内。

50、有利地,虚设栅极沟槽和漂移层之间的第二注入区为功率半导体器件提供更好的阻挡能力,并且可以电连接到发射极电极。

51、功率半导体器件可以包括多个有源单元和多个绝缘沟槽,并且每个有源单元沿着第二方向紧挨着设置在两个绝缘沟槽之间。

52、“在之间紧挨着”表示两个绝缘沟槽之间没有其他结构。

53、功率半导体器件还可以包括多个虚设单元,并且其中至少一个虚设单元和至少两个绝缘沟槽沿着第二方向设置在相邻的有源单元之间。

54、绝缘沟槽可以沿着第二方向设置在虚设单元和有源单元之间,或者设置在两个虚设单元之间。

55、功率半导体器件还可以包括具有第二导电类型的缓冲层,其中缓冲层设置在漂移层和集电极层之间,并且具有比漂移层更高的掺杂浓度。

56、缓冲层对于减小功率半导体器件的导通状态压降vce,sat是有用的。

57、功率半导体器件可以包括绝缘栅极双极晶体管(igbt)。

58、根据本公开的第二方面,提供了一种制造功率半导体器件的方法,该方法包括:

59、提供半导体衬底,其包括:

60、基极层,其设置在半导体衬底的第一侧,其中,基极层具有第一导电类型;以及

61、漂移层,其具有与第一导电类型相反的第二导电类型;

62、选择性地蚀刻基极层和漂移层以在半导体衬底内形成绝缘沟槽;

63、在绝缘沟槽内形成栅极电极,并用介电材料填充绝缘沟槽;

64、在半导体衬底的第一侧的基极层内选择性地形成具有第二导电类型的发射极区,其中,发射极区和其中布置发射极区的基极层的一部分提供有源单元,并且其中,该绝缘沟槽与有源单元相邻,并且栅极电极被配置为控制有源单元内的电流通道的导通/截止状态;以及

65、在半导体衬底的第二侧形成集电极层,集电极层具有第一导电类型,其中,第二侧与第一侧相对,并且,漂移层布置在集电极层和基极层之间;

66、其中:

67、绝缘沟槽被配置为沿着第一方向从半导体衬底的第一侧的表面延伸到漂移层中;

68、有源单元沿着垂直于第一方向的第二方向具有第一长度l1,并且绝缘沟槽沿着第二方向具有第二长度l2;以及

69、第一长度l1和第二长度l2满足0.5≤l2/l1≤2的关系。

70、在适当的情况下,上文关于本公开的第一方面描述的任意可选特征可以应用于本公开的第二方面。

71、可以理解,上述l2/l1的各种范围允许范围端点的规定值具有一定程度的可变性,例如±10%。例如,2的规定极限可以是2*(1-10%)以及2*(1+10%)之间的任何数字。此外,以范围格式表示的值应以灵活的方式进行解释,以不仅包括明确列举为范围端点的数值,还包括包含在该范围内的所有单独数值或子范围,如同明确列举了每个数值和子范围一样。

- 还没有人留言评论。精彩留言会获得点赞!