等离子体沉积的膜中的氢管理的制作方法

等离子体沉积的膜中的氢管理

相关申请的交叉引用

1.本技术要求于2020年7月19日提交的题为“hydrogen management in plasma deposited films(等离子体沉积的膜中的氢管理)”的美国专利申请第16/932,793号的优先权,所述申请通过引用以其整体并入本文。

技术领域

2.本技术涉及用于半导体处理的方法和系统。更具体地,本技术涉及用于生产具有减少的氢含量的膜的系统和方法。

背景技术:

3.集成电路通过在基板表面上产生错综复杂的图案化材料层的处理来制成。在基板上产生图案化材料需要用于形成和移除材料的受控方法。随着器件尺寸持续减小,膜特征可导致对器件性能更大的影响。用于形成材料层的材料可影响所生产的器件的操作特征。随着材料厚度持续减小,膜的沉积特性可能对器件性能具有更大的影响。

4.因此,需要可用于产生高质量器件和结构的改进的系统和方法。这些和其他需求通过本技术来解决。

技术实现要素:

5.半导体处理的示例性方法可包括将含硅前驱物流动至半导体处理腔室的处理区域中。基板可容纳在处理区域内,且基板可维持在低于或约450℃的温度下。方法可包括冲击含硅前驱物的等离子体。方法可包括在半导体基板上形成非晶硅层。非晶硅层的特征可在于小于或约3%的氢掺入。

6.在一些实施例中,方法可包括将氢与含硅前驱物一起流动至半导体处理腔室的处理区域中。氢可以含硅前驱物的流率的至少两倍的流率流动。方法可包括将含硼前驱物或含磷前驱物与含硅前驱物一起流动至半导体处理腔室的处理区域中。在半导体处理方法期间,等离子体可以小于或约10khz的频率被脉冲,且等离子体脉冲的占空比可以是小于或约50%。方法可包括在非晶硅层上执行能量处理。能量处理可进一步减少氢掺入。能量处理可包括将非晶硅层暴露于uv、微波或原位等离子体。在半导体处理方法期间,能量处理可在不中断真空条件的情况下执行。

7.本技术的一些实施例可涵盖半导体处理方法。方法可包括将含硅前驱物流动至半导体处理腔室的处理区域中。基板可容纳在处理区域内,且基板可维持在低于或约450℃的温度下。方法可包括将催化剂前驱物流动至半导体处理腔室的处理区域中。方法可包括冲击含硅前驱物和催化剂前驱物的等离子体。方法可包括在半导体基板上形成非晶硅层。非晶硅层的特征可在于小于或约3%的氢掺入。

8.在一些实施例中,催化剂前驱物可包括含硼前驱物、含磷前驱物、或含硅和卤素的前驱物。卤素可以是或包括氟、氯或碘。在半导体处理方法期间,等离子体可以小于或约

10khz的频率被脉冲。等离子体脉冲的占空比可以是小于或约50%。方法可包括在非晶硅层上执行能量处理。能量处理可进一步减少氢掺入。能量处理可包括将非晶硅层暴露于uv、微波或原位等离子体。

9.本技术的一些实施例可涵盖半导体处理方法。方法可包括将含硅前驱物流动至半导体处理腔室的处理区域中。基板可容纳在处理区域内。基板可维持在低于或约450℃的温度下。方法可包括冲击含硅前驱物的等离子体。方法可包括在半导体基板上形成非晶硅层。非晶硅层的特征可在于第一量的氢掺入。方法可包括在非晶硅层上执行能量处理。能量处理可将来自非晶硅层中的氢的量减少至比第一量的氢掺入更少的第二量的氢掺入。

10.在一些实施例中,能量处理可包括将非晶硅层暴露于uv、微波或原位等离子体。第二量的氢掺入可以是小于或约2at.%。方法可包括将氢与含硅前驱物一起流动至半导体处理腔室的处理区域中。氢可以含硅前驱物的流率的至少两倍的流率流动。在半导体处理方法期间,等离子体可以小于或约10khz的频率被脉冲。等离子体脉冲的占空比可以是小于或约50%。

11.与传统系统和技术相比,此类技术可提供数个优点。例如,本技术的实施例可产生特征在于减少的氢含量的膜。此外,本技术可减少氢含量而不会从氢放气增加膜应力或孔隙率。结合以下描述和附图,更详细地描述了这些和其他实施例及其许多优点和特征。

附图说明

12.通过参考说明书的其余部分和附图,可进一步理解所公开的技术的本质和优点。

13.图1示出了根据本技术的一些实施例的示例性处理系统的俯视图。

14.图2示出了根据本技术的一些实施例的示例性等离子体沉积系统的示意性剖面视图。

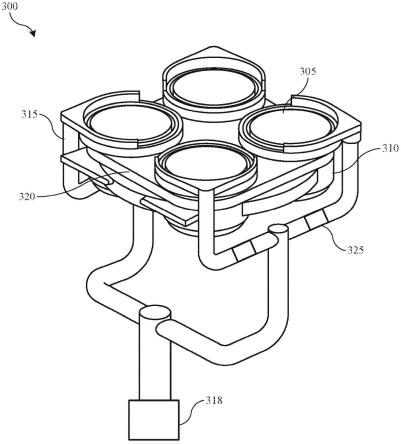

15.图3示出了根据本技术的一些实施例的半导体处理方法中的操作。

16.附图中的若干附图被包括作为示意图。应理解,附图是出于说明的目的,除非具体说明是按比例的,否则不应被视为按比例。此外,作为示意图,提供附图以帮助理解,且与真实表示相比,这些附图可能不包括所有方面或信息,且可包括用于说明目的的放大材料。

17.在所附附图中,类似的部件和/或特征可具有相同的附图标记。此外,相同类型的各种部件可通过在附图标记后面跟随在类似部件之间进行区别的字母来区分。如果在说明书中仅使用第一附图标记,则说明适用于具有相同第一附图标记的类似部件中的任何一者而不论字母如何。

具体实施方式

18.随着半导体器件尺寸持续减少,被包括在结构中的构成膜可影响器件性能,以及被包括在器件中的其他材料的制造。例如,形成含硅膜的处理可使用硅烷或其他含硅材料。这些前驱物可包括可掺入膜中的氢。将氢掺入膜中可在处理期间造成额外问题。例如,掺入膜中的氢可能热稳定性较差,且在后续处理期间,可发生放气。此外,氢可影响膜应力,膜应力可使膜变得越来越压缩,且还可造成膜分层。最终,在等离子体中的氢的体积可影响沉积工艺,且可使所形成的膜的晶粒尺寸和结晶度增加,这可挑战旨在形成非晶硅膜的沉积工艺。

19.为了减少或补偿氢掺入,传统技术可改变沉积参数,或可执行补救动作。例如,当在较高温度(诸如高于或约500℃,或高于或约600℃)下执行沉积时,在沉积期间可释放氢,这可改进膜质量和特性。此外,传统技术可在膜沉积之后执行退火。退火工艺可致密化膜,且允许从结构移除氢。尽管这些技术在一些制造操作期间可以是有效的,但其他处理可受限于热预算。

20.例如,在薄膜晶体管形成或任何数量的其他处理操作期间,非晶硅可在器件之上或之中形成。在这些器件中的一些中,下层材料或结构可能无法忍受与高温沉积或退火相关联的温度,且可能受限于小于或约550℃、小于或约500℃、小于或约450℃、小于或约400℃或更低的处理温度。传统技术可能受限于产生具有高达10at.%或更大的氢掺入的膜。对于薄膜晶体管形成,增加的氢掺入可影响晶体管的迁移率或性能。

21.本技术通过执行等离子体沉积工艺解决这些问题,其中所沉积的膜可特征在于减少的氢掺入。通过调整一个或多个处理操作或参数,本技术可产生特征在于减少的氢掺入的非晶硅膜,且所述膜可在降低的温度下产生。这可保护可能无法暴露于传统技术的温度的下层结构。

22.尽管其余公开内容将惯例地识别利用所公开的技术的特定沉积工艺,但将容易理解系统和方法同等地可应用于可在所述腔室或任何其他腔室中发生的其他沉积和蚀刻工艺。因此,本技术不应被视为仅限于与这些特定沉积工艺或腔室一起使用。本公开将在对根据所述的本技术的实施例的额外改变和调整之前,讨论可在根据本技术的一些实施例执行方法中使用的一个可能的系统和腔室。

23.图1示出了根据实施例的沉积、蚀刻、烘烤和固化腔室的处理系统100的一个实施例的俯视平面图。在附图中,一对前开式标准舱102供应通过机器臂104接收的各种尺寸的基板,并且将所述基板放置到低压保持区106中,然后将所述基板放置到定位于串联分区109a-c中的基板处理腔室108a-f中的一者中。第二机器臂110可用于将基板晶片从保持区106传送至基板处理腔室108a-f和返回。每个基板处理腔室108a-f可配备成执行数个基板处理操作,除了包括等离子体增强化学气相沉积、原子层沉积、物理气相沉积、蚀刻、预清洁、除气、定向和其他基板处理(包括退火、灰化等等)之外,还包括形成本文所述的半导体材料的堆叠。

24.基板处理腔室108a-f可包括一个或多个系统部件以用于在基板上沉积、退火、固化和/或蚀刻介电膜或其他膜。在一个配置中,两对处理腔室(例如,108c-d和108e-f)可用于在基板上沉积介电材料,且第三对处理腔室(例如,108a-b)可用于蚀刻所沉积的电介质。在另一配置中,所有三对腔室(例如,108a-f)可配置成在基板上沉积交替介电膜的堆叠。所述处理中的任何一者或多者可在与不同实施例中所示的制造系统分开的腔室中执行。应理解,系统100考虑到用于介电膜的沉积、蚀刻、退火和固化腔室的额外配置。

25.图2示出了根据本技术的一些实施例的示例性等离子体系统200的示意性剖面视图。等离子体系统200可示出一对处理腔室108,一对处理腔室108可设置在上述的串联分区109中的一者或多者中,且可包括专门配置用于执行根据本技术的实施例的处理的部件或组件。等离子体系统200大致可包括腔室主体202,腔室主体202具有限定一对处理区域220a和220b的侧壁212、底壁216和内部侧壁201。处理区域220a-220b中的每一者可以类似地配置,且可包括相同的部件。

26.例如,处理区域220b(其部件也可被包括在处理区域220a中)的部件可包括穿过在等离子体系统200中的底壁216中形成的通路222而设置在处理区域中的基座228。基座228可提供适配成在基座的暴露表面(诸如主体部分)上支撑基板229的加热器。基座228可包括加热元件232(例如电阻加热元件),加热元件232可在期望的处理温度下加热和控制基板温度。基座228还可由远程加热元件(诸如灯组件或任何其他加热装置)加热。

27.基座228的主体可通过凸缘233耦合至杆226。杆226可将基座228与功率输出或功率箱203电耦合。功率箱203可包括驱动系统,所述驱动系统控制在处理区域220b内基座228的抬升和运动。杆226还可包括电功率接口,以提供电功率至基座228。功率箱203还可包括用于电功率和温度指示器的接口,诸如热电偶接口。杆226可包括适配成与功率箱203可拆卸地耦合的底座组件238。圆周环235示出于功率箱203的上方。在一些实施例中,圆周环235可以是肩部,所述肩部适配成作为机械止动件或着陆部,配置成提供底座组件238与功率箱203的上表面之间的机械接口。

28.棒230可穿过在处理区域220b的底壁216中形成的通路224而被包括,且可用于定位穿过基座228的主体而设置的基板升降杆261。基板升降杆261可选择性地将基板229与基座间隔开,以促进用机器人交换基板229,所述机器人用于通过基板传送通口260将基板229传送进出处理区域220b。

29.腔室盖204可与腔室主体202的顶部部分耦合。盖204可容纳与盖204耦合的一个或多个前驱物分配系统208。前驱物分配系统208可包括前驱物入口通路240,前驱物入口通路240可穿过气体输送组件218将反应物和清洁前驱物输送至处理区域220b中。气体输送组件218可包括气体箱248,气体箱248具有设置在与面板246中间的挡板244。射频(“rf”)源265可与气体输送组件218耦合,射频(“rf”)源265可以为气体输送组件218供电,以促进在气体输送组件218的面板246与基座228之间生成等离子体区域(其可以是腔室的处理区域)。在一些实施例中,rf源可与腔室主体202的其他部分(诸如基座228)耦合,以促进等离子体生成。介电隔离器258可设置在盖204与气体输送组件218之间,以避免将rf功率传导至盖204。遮蔽环206可设置在与基座228接合的基座228的周边上。

30.可选的冷却通道247可形成于气体分配系统208的气体箱248中,以在操作期间冷却气体箱248。热传递流体(诸如水、乙二醇、气体等)可通过冷却通道247循环,使得气体箱248可维持在预定义温度下。衬垫组件227可设置在处理区域220b内,靠近腔室主体202的侧壁201、212,以避免将侧壁201、212暴露于处理区域220b内的处理环境。衬垫组件227可包括可耦合至泵系统264的圆周泵腔体225,泵系统264配置成从处理区域220b排出气体和副产物并且控制处理区域220b内的压力。多个排气口231可形成于衬垫组件227上。排气口231可配置成以促进系统200内的处理的方式允许气体从处理区域220b流动至圆周泵腔体225。

31.图3示出了根据本技术的一些实施例的在处理方法300中的示例性操作。方法可在各种处理腔室中执行,包括以上所述的等离子体系统200。方法300在所阐明的方法操作开始之前可包括一个或多个操作,包括前端处理、沉积、蚀刻、抛光、清洁或可在所描述的操作之前执行的任何其他操作。如图中所标记,方法可包括数个可选操作,这些可选操作可以或可以不具体地与根据本技术的方法相关联。例如,如以下将进一步讨论,描述了操作中的许多操作以便提供更广范围的半导体处理,但对技术并不是关键的,或者可通过替代方法执行。

32.方法300可涉及可选操作,以将半导体结构开发成特定制造操作。尽管在一些实施例中方法300可在底座结构上执行,但在一些实施例中,方法可在其他材料形成或移除之后执行。例如,可执行任何数量的沉积、掩模或移除操作,以在基板上产生任何晶体管、存储器或其他结构方面。在一些实施例中,在基板上形成的一个或多个结构可特征在于小于或约500℃、小于或约450℃、小于或约400℃或更少的热预算。因此,方法300和任何后续操作可在结构热预算下或以下的温度下执行。基板可设置在基板支撑件上,所述基板支撑件可定位在半导体处理腔室的处理区域内。产生下层结构的操作可在与可执行方法300的各方面相同的腔室中执行,且一个或多个操作还可在与可执行方法300的操作的腔室类似的平台上的一个或多个腔室中执行,或在其他平台上执行。

33.在一些实施例中,方法300可包括在基板上形成非晶硅层。在操作305处,方法可包括将含硅前驱物流动至其中容纳基板的处理区域中。含硅前驱物可以用载气输送,包括惰性前驱物,例如,诸如氩或氦。如将于以下进一步详细解释,在一些实施例中,在可选操作310处,额外前驱物可与含硅前驱物一起流动至处理区域中。在操作315处,等离子体可冲击流动至处理区域中的前驱物,且在操作320处,非晶硅层可沉积在基板上。所述形成或沉积可使用任何数量的前驱物(诸如硅烷或其他含硅材料)执行,且在一些实施例中,输送的含硅前驱物还可包括氢。因此,所沉积或形成的非晶硅层可特征在于第一量的氢掺入。尽管其余公开将讨论非晶硅膜,但应理解,硅膜可包括额外材料,所述材料可产生掺杂的非晶硅。例如,本技术的实施例可包含可与掺杂物(诸如磷、硼、硫、砷或其他材料)一起形成的硅膜。

34.如先前所述,本技术的一些实施例可包含形成于材料或结构之上的膜,其特征在于热预算是小于或约550℃、小于或约500℃、小于或约450℃、小于或约400℃、小于或约350℃、小于或约300℃或更少。因此,在一些实施例中,非晶硅层可在这些温度中的任一者下或以下形成,以容纳下层材料,且在一些实施例中,一个或多个操作(包括方法300的所有操作)可在这些温度中的任一者下或以下执行,且所处理的基板可在整个处理中被维持在低于或约为这些温度中的任一者。在一些实施例中,在形成期间的处理压力可以是大于或约1托,且可介于约2托和约20托之间。膜还可以由任何含硅材料形成,诸如硅烷或任何二元硅氢化合物,以及任何含硅和氢的前驱物。因此,所形成的层可特征在于第一量的氢掺入。因为更高温度沉积和退火可能不适合用于一些结构,在没有如以下将说明的任何其他相互作用的情况下,氢掺入可以是大于或约3at.%、大于或约5at.%、大于或约7at.%、大于或约10at.%或更多。这可造成先前所述的任何挑战,包括应力效应和后续放气。因此,在本技术的一些实施例中,可进行一个或多个修改以产生膜,其中所沉积的膜可特征在于小于或约3at.%或更少的氢掺入。

35.如可选操作310处所述,在一些实施例中,一个或多个额外前驱物可与含硅前驱物一起输送。例如,在一些实施例中,方法可进一步包括将氢与含硅前驱物一起流动至半导体处理腔室的处理区域中。尽管处理旨在减少在产生的硅膜中的氢掺入是违反直觉的,但令人惊讶的是,本技术可通过在处理气体中添加氢来产生这样的结果。

36.当前驱物在等离子体中分离时,许多硅氢键可断开,尽管一定量的硅和氢键合仍可发生在形成的膜内,从而造成最终膜的氢掺入。然而,当掺入额外量的氢时,等离子体将(诸如从氢气)额外分离氢,这可产生数个氢自由基和离子。因为这些粒子很小,它们可轻易穿透所沉积的膜。此外,这些粒子可特征在于相对高的能量,然后所述能量可被传送至膜中

以断开额外的硅和氢的键合。能量还可足以用从硅-氢键移除的氢形成氢键,这可产生氢气。这种新形成的氢气可在形成处理本身期间从膜流动,这可限制孔隙率或膜降解。

37.为了通过在等离子体前驱物中添加氢而在膜内产生减少氢的效应,氢的流动可大于含硅材料的流动。例如,在一些实施例中,氢的流率相较于含硅前驱物的流率可以是大于或约2:1,且可以是大于或约5:1、大于或约10:1、大于或约20:1、大于或约50:1、大于或约75:1、大于或约100:1、或更大。这可提供足够的氢自由基以渗透所沉积的膜,断开额外硅-氢键,且形成可从膜移除氢的氢键。

38.在一些实施例中,输送的额外前驱物可以是配置成与含硅前驱物产生催化反应的前驱物。含硼前驱物、含磷前驱物和一些含硅前驱物可提供此催化效应。例如,硼烷(可包括二硼烷)、磷化氢和硅卤化物可与硅烷或更高阶硅烷交互作用,以降低硅烷的分解温度,这可以降低断开硅-氢键的能量屏障。这可进一步限制所产生的膜中的氢掺入。硅卤化物可包括任何数量的卤素物质,包括氟、氯、溴和碘。

39.在一些实施例中,调整等离子体形成处理还可促进从所产生的膜移除氢。例如,本技术的一些实施例可包括在等离子体生成期间脉冲等离子体。等离子体可在等离子体生成频率下生成,诸如在一个非限制示例中所述等离子体生成频率为13.56mhz。等离子体功率还可在可以是小于或约10khz,且可以是小于或约9khz、小于或约8khz、小于或约7khz、小于或约6khz、小于或约5khz、小于或约4khz、小于或约3khz、小于或约2khz、小于或约1khz、或更小的脉冲频率脉冲。脉冲频率的占空比可提供一定量的“关闭”时间以用于等离子体生成。

40.在等离子体“关闭”时段期间,可能不发生沉积。尽管先前形成的离子可迅速熄灭,但自由基物质仍可接触加热的基板并将能量传送至所产生的非晶晶格中。这可继续激活并断开膜内的额外硅-氢键,然后可将额外硅-氢键从膜移除。在高占空比下,在沉积恢复之前,可能没有足够的时间来实现此效应。因此,在一些实施例中,占空比可维持在小于或约50%、且可维持在小于或约45%、小于或约40%、小于或约35%、小于或约30%、小于或约25%、小于或约20%、小于或约15%、小于或约10%、小于或约5%、或更少。这些技术中的任一者可以单独地或结合地减少在所沉积的膜中的氢掺入,以产生特征在于小于或约3at.%的氢掺入的非晶硅膜,且可将氢掺入减少至小于或约2.5at.%、小于或约2.4at.%、小于或约2.3at.%、小于或约2.2at.%、小于或约2.1at.%、小于或约2.0at.%、小于或约1.9at.%、小于或约1.8at.%、小于或约1.7at.%、小于或约1.6at.%、小于或约1.5at.%、小于或约1.4at.%、小于或约1.3at.%、小于或约1.2at.%、小于或约1.1at.%、小于或约1.0at.%、或更少。

41.在膜形成之后,在一些实施例中,在可选操作325处,在其上形成非晶硅层的基板可在后处理工艺中进一步处理,所述后处理工艺可以是额外能量处理。后处理可在与沉积相同的腔室中执行,或基板可从第一处理腔室传送至第二处理腔室。在一些实施例中,第二腔室可以在相同的工具(诸如先前所述的工具)上,且可在对基板维持真空条件的同时执行传送。后处理工艺可配置成通过将额外能量传送至沉积的膜中来进一步减少所产生的膜中的氢掺入,且断开额外的硅-氢键。这可将层内的氢掺入的量从沉积期间的第一量进一步减少至可以比第一量的氢掺入更少的第二量的氢掺入。第二量的氢掺入可以是小于或约2at.%,且可以是小于或约1.5at.%、小于或约1.0at.%、小于或约0.5at.%、或更少。

42.后处理可包括配置成提供额外能量传送,同时维持热预算的任何数量的处理。因此,在一些实施例中可能不执行热退火,且后处理工艺可在如先前所述的温度中的任一者下执行。后处理工艺可包括uv暴露、微波暴露或原位等离子体暴露。例如,可在维持温度低于或约450℃或更少的同时执行uv暴露,且可执行暴露达大于或约5分钟、大于或约10分钟、大于或约15分钟、大于或约20分钟、大于或约25分钟、大于或约30分钟、或更长。类似地,可在类似温度下执行微波退火达大于或约1分钟、大于或约2分钟、大于或约5分钟、大于或约10分钟、或更长。

43.在形成之后,可停止含硅前驱物的流动,且可以用氢或惰性气体(诸如氦或氩)执行后处理等离子体暴露。等离子体可以以低功率形成,以限制所产生的膜的溅射,且在一些实施例中,后处理等离子体可在小于或约2,500w形成,且可在小于或约2,000w、小于或约1,500w、小于或约1,000w、小于或约500w、或更小形成。为了限制在处理期间在膜内形成孔,可循环方法300以在膜形成期间在中间时段处结合所述处理。例如,在一些实施例中,膜可在至少两个操作中形成,其中每个操作可形成膜的总厚度的小于或约50%,且可形成小于或约30%、小于或约25%、小于或约20%、或更少。在形成循环之间,可执行后处理以从形成的膜的部分移除额外的氢。为了限制排队时间的减少,可在沉积腔室内执行等离子体处理,且可在与沉积腔室相同的工具上在腔室中执行其他能量处理。通过利用本技术的一个或多个方面,相较于传统技术可减少膜内的氢掺入。此外,所述的处理可在比许多传统技术更低的温度下执行,这可适应可能受到热预算限制的结构。

44.在前述说明中,为了解释的目的,已阐述了数个细节以便提供对本技术的各种实施例的理解。然而,对本领域技术人员将显而易见的是,某些实施例可在没有这些细节中的一些的情况下或在具有额外细节的情况下实践。

45.已公开数个实施例,本领域技术人员将认知可使用各种修改、替代构造和等效物而不背离实施例的精神。此外,并未说明数个公知的处理和元件,以便防止非必要地模糊本技术。因此,以上说明不应视为对本技术的范围的限制。

46.在提供值的范围的情况下,应理解,除非上下文另有明确规定,否则此范围的上限值和下限值之间的每个中间值,直到下限值单位的最小分数也被具体公开。在所阐明的范围中的任何阐明的值或未阐明的中间值之间的任何较窄范围以及在此阐明的范围中的任何其他阐明值或中间值被涵盖。这些较小范围的上限值和下限值可独立地包括在范围中或从范围排除,且在这两个限值中的任一者、这两个限值都不或这两个限值都被包括在较小范围中的每个范围也涵盖在本技术内,受限于所阐明的范围中任何具体排除的限值。在所阐明的范围包括限值中的一个或两个限值的情况下,排除那些限制中的任一者或两者的范围也被包括。

47.如本文和所附权利要求中所使用,除非上下文另有明确指示,否则单数形式的“一”、“一个”和“所述”包括复数引用。因此,例如,对“一前驱物”的引用包括多个此类前驱物,且对“所述层”的引用包括对一个或多个层和本领域技术人员已知的其等效物的引用,以此类推。

48.而且,当在本说明书中和在以下权利要求书中使用时,词语“包括(comprise(s))”、“包括有(comprising)”、“包含(contain(s))”、“包含有(containing)”、“包括(include(s))”以及“包括有(including)”旨在指定所阐明的特征、整数、部件或操作的存

在,但它们并不排除一个或多个其他特征、整数、部件、操作、动作或群组的存在或添加。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1