改进的功率器件的设计和制造的制作方法

背景技术:

1、硅基功率器件长期主导着电力电子器件应用和电力系统应用。另一方面,与硅(eg=1.1ev)相比,sic是一种具有更宽带隙(eg)(eg=3.3ev)的材料;因此,sic的阻断电压比si更高。与si(si的击穿电场为0.3×106v/cm)相比,sic的击穿电场(3×106v/cm至5×106v/cm)更高并且是更好的热导体(sic为3.7(w/cm-k),而si为1.6(w/cm-k))。sic已经成为功率mosfet的首选材料。然而,“即使成功地将sic功率mosfet投入商业市场,但是仍然有多个关键的可靠性问题尚未完全解决”[来源:sic功率mosfet的关键可靠性问题由美国陆军研究实验室的莱利斯、d.哈伯萨特、r.格林和e.穆罗公布于ecs交易,58(4)87-93(2013),doi:10.1149/05804.0087ecst]。

2、sic存在于被称为多型体的多晶型晶体结构中,例如3c-sic、4h-sic、6h-sic。图1a是b.j.巴利加在先进的高压功率器件概念(施普林格出版社,2011年)中报告的现有技术sic dmosfet结构。图1b图示了为图1a的现有技术sic dmosfet结构而模拟的电场等值线。5-kv屏蔽4h-sic反转模式功率mosfet结构的表面附近的电场分布如图1b所示,以能够对接面闸场效应晶体管(jfet)区域和闸极区域中的电场进行检查。在该现有技术器件中可以观察到p+屏蔽区的边缘处的电场的尖峰,其将产生闸极氧化层中的高电场,从而导致该mosfet器件的性能不良。图1c图示了屏蔽4h-sic反转模式mosfet中的电场分布。图中的模拟结果显示,对于图1a中的现有技术的sic dmosfet结构,闸极氧化层中的电场高达4mv/cm。

3、典型的sic mosfet器件结构(诸如图1a所示的结构)在p井区的拐角处产生高电场集中,这导致在闸极氧化层中产生高电场,尤其是在高汲极偏压(阻断模式)操作期间。4h-sic击穿的高临界电场(≈3mv/cm)会在闸极氧化层中产生非常高(>5mv/cm)的电场。在闸极氧化层中的此类高电场下观察到fowler-nordheim隧穿电流,这可能在闸极氧化层中产生陷井电荷,从而导致器件的可靠性差。

4、si的制程使用掺杂剂扩散等技术,但是这些常规制程无法用于制造sic器件,因为在1800℃以下的温度下,sic中的扩散系数可忽略不计。sic器件是通过离子注入源极区和p井区两者来制造,但是难以在sic中进行离子注入和深离子注入。因此,长期以来,人们一直认为需要对功率器件进行改良,以解决sic功率mosfet的可靠性问题。

5、此外,由于在最先进的sic平面dmosfet上可实现的mos通道迁移率有限(10cm2/vs至25cm2/vs),因此有必要形成具有亚微米通道长度的mos通道,以使功率mosfet的整体导通电阻不会显著降低。“如果使用不同的屏蔽形成p井区和n+源极区,则两个屏蔽的错位会导致单元每侧的通道长度不一致。为了避免阈值电压(vth)下降和击穿电压(vbr)下降,n+屏蔽相对于p井采用自对准方式。”[来源:1.2kv4h sic dmosfet的设计与制造,由r.huang等人公布于2016年第13届中国国际半导体照明论坛:第三代半导体国际会议(sslchina:ifws)]。dmosfet结构中的p井区和n+源极区之间的偏移形成dmosfet通道区。如果p井区和n+源极区是通过两个单独的屏蔽步骤形成,则这些层之间将不可避免地存在一定量的光刻未对准,从而导致单位单元的两侧上的mos通道长度不一致(或不对称)。采用通常用于大批量半导体制造中的投影光刻技术的两个屏蔽层之间的光刻未对准范围为+/-0.05μm至+/-0.2μm或更大,在没有明显不对称的情况下,这为实际可实现的mos通道长度设置了较低下限。对于0.5μm的目标通道长度,n+源极屏蔽步骤和p井屏蔽步骤之间的+/-0.2μm未对准可导致单位单元的一侧上的mos通道长度为0.3μm,而单位单元另一侧上的mos通道长度为0.7μm。虽然当mos通道长度较长时,mosfet的导通电阻增加,但低于最佳mos通道长度可能会导致不良效应,诸如闸极阈值电压(vth)退化以及其他短通道效应,诸如汲极诱导势垒降低(drain-inducedbarrier lowering,dibl)。

6、文献中已经提出了用于消除p井区和n+源极区之间的未对准的自对准技术。自对准mos通道形成就是此类技术中的一种,其中通道长度由侧壁间隔件沉积和蚀刻限定。图9是r.huang等人在“1.2kv 4h sic dmosfet的设计与制造”中报告的自对准注入技术的现有技术的制程,其中通道长度由侧壁间隔件沉积和蚀刻限定。

7、此外,“虽然sic功率mosfet与硅mosfet有诸多相似之处,但仍存在很多具有挑战性的差异。尤其,4h-sic(eg=3.26ev)的宽带隙性质既有优点也有缺点,实现了低本质载子浓度和高临界电场的同时对反型层迁移率和钝化介电层的可靠性提出了挑战。”[来源:sic功率mosfet设计面临的挑战,由美国纽约州尼斯卡尤纳市通用电气全球研究中心半导体技术实验室的kevin matocha公布于isdrs 2007,2007年12月12日至14日,美国马里兰州马里兰大学帕克分校]

8、在图1a所示的典型sic平面mosfet结构中,金属氧化物半导体(mos)通道形成在sic的水平或0001晶面上。与垂直侧壁或11-20晶面或10-10的晶面相比,sic的0001晶面上的通道迁移率或场效应迁移率通常比较低。sic的0001晶面上的通道迁移率或场效应迁移率在15cm2/v-sec至25cm2/v-sec的范围内,而相比之下,硅mosfet上的通道迁移率或场效应迁移率可超过350cm2/v-sec。当制作平面sic dmosfet时,导通电阻往往很大,并且mosfet受到场效应通道迁移率的限制。因此,长期以来,人们认为需要对功率器件进行改良,以解决sic mosfet中的低通道迁移率和高导通电阻的问题。

9、此外,“从应用角度看,功率mosfet的阈值电压是重要的设计参数。对于大多数系统应用,最低阈值电压必须保持在1伏以上,从而防止因噪声引起的电压尖峰而形成导通。同时,不期望高阈值电压,因为可用于在通道反型层中产生电荷的电压是由(vg-vt)确定的,其中vg是所施加的闸极偏压,而vt是阈值电压。”[来源:b.j.巴利加,碳化硅功率器件,施普林格出版社(2005),第234页]

10、图22[来源:b.j.巴利加,碳化硅功率器件,施普林格出版社(2005),第235页]图示了闸极氧化层厚度为0.1微米时4h-sic平面mosfet的阈值电压。图中还提供了具有相同闸极氧化层厚度的硅功率mosfet的所得结果,以供比较。

11、在竞相使具有高击穿电压额定值的平面闸极sic mosfet实现较低rds,on的情况下,通常采用的做法是使通道长度(lch)尽可能短,从而减少与通道相关的大部分传导损耗。这样做的代价是,随着通道长度变得越来越短,mosfet器件变得容易受到不良现象的影响,诸如dibl效应(汲极诱导势垒降低效应),这是导致器件性能不佳的原因,包括但不限于高汲极偏压下阈值电压(vth)滚降(roll-off)以及高汲极偏压下汲极泄漏(il)增加。缓解此问题的常规方法是均匀地提高通道区域中的掺杂浓度,但此方法存在高于最佳闸极阈值电压和导通电阻的问题,这可能会抵消缩短通道长度所实现的好处。

12、此外,尤其在电机控制和开关模式电源中,一直存在朝向更高工作频率发展的趋势。在电源中,由于被动组件(电感器和电容器)的尺寸和功率损耗降低,因此在高频率下运行具有吸引力,从而实现更高效、紧凑的系统设计。为了实现在更高频率下运行,使用具有经改良的开关性能的功率晶体管和整流器极其重要。在这方面,sic的电子参数优势将得到显著改善。

13、图27是mps二极管的现有技术的结构,该结构由并联连接的叉指状插脚二极管和肖特基二极管组成,如“t.木本和j.a.库珀的碳化硅技术基础,ieee出版社(2014),第296页”中所述。如图27中的现有技术所示的mps二极管在顶部具有金属层,该金属层与p+区域形成欧姆接触并且与n-区域形成肖特基接触,因此整个器件由并联连接的叉指肖特基二极管和pin二极管组成。p+阳极区域之间间隔足够远,这使得它们的耗尽区在零偏压或正向偏压下不会产生接触。这将在每个肖特基或非肖特基接触与n+基板之间留下穿过n-漂移区的导电路径。当施加正向偏压时,肖特基或非肖特基区域首先导通,因为在相同的正向电压下,肖特基势垒二极管的电流密度比pin二极管高几个数量级。因此,肖特基或非肖特基区域有效地限制了跨pin区域的压降,并且pin区域不导电。因此,几乎所有的正向电流都是因为电子从n-漂移区通过肖特基或非肖特基接触注入金属而形成。由于p+区域不向漂移区注入空穴,因此不存储少数载子电荷,并且关断瞬态很快,从而最大程度地降低了开关损耗。在不存在电导调制的情况下,漂移区的串联电阻由其厚度和掺杂决定。此类相对较高的电阻导致形成压降vdr,该压降在高电流下占总压降的绝大部分。在肖特基二极管中,在出现高浪涌电流的情况下,这会造成问题,因为纯肖特基二极管会进入热失控状态,造成严重后果。

14、此外,“[一种]碳化硅(sic)器件可包括设置在sic半导体层上方的闸极电极,其中所述sic半导体层包括:第一导电类型的漂移区;邻近所述漂移区设置的井区,其中所述井区为第二导电类型;以及邻近所述井区设置的所述第一导电类型的源极区,其中所述源极区包括源极接触区和夹止区,其中所述夹止区仅部分地设置在所述闸极电极下方,其中所述夹止区中的表面掺杂密度小于2.5×1014cm-2,其中所述夹止区被配置为在电流密度大于所述sic器件的标称电流密度的情况下耗尽,从而增加所述源极区的电阻。”[来源:碳化硅装置及其制造方法由彼得·阿尔芒·洛西、卢比萨·德拉戈柳布·斯特万诺维奇、格雷戈里·托马斯·邓恩、亚历山大·维克托洛维奇·博洛特尼科夫在2018年2月20日以us9899512b2的形式公布]。

15、us20190013312a1公开了分别编号为3、5的基极区,该基极区容纳从上表面2a延伸进入基极区3、5的内部的、编号为4、6的n型第一源极区和第二源极区,并且指出:“第一金属化层在第一表面上方延伸并且与注入结构以及jfet区域直接接触的同时形成jbs二极管。”[来源:具有集成二极管的碳化硅mosfet器件及其制程由马里奥·朱塞佩·萨吉奥、西蒙娜·拉斯村于2019年1月10日在美国专利商标局以us20190013312a1的形式公布]。

16、“一种n-mosfet器件(11),所述器件在基板(1)和闸极结构(7,8)之间具有n型通道(2),所述通道(2)由一层n掺杂的锗形成,所述锗层的厚度使得所述通道(2)完全耗尽而无需施加闸极电压,由此所述器件(11)在累积模式下工作。”[来源:锗n-mosfet器件和生产方法由达涅利·凯米、阿萨那西奥斯·迪穆拉斯、让·福佩林、奇亚拉·马尔基奥里、克里斯托夫·p.罗塞尔、玛丽莲·索萨、阿克塞尔m.塔彭尼尔、大卫·j.·韦伯于2011年2月3日以wo2011013042a1的形式公布]。

17、us9318597b2公开了一种包括垂直场效应晶体管(fet)和旁路二极管的半导体器件。它还指出,所述垂直fet器件包括基板、形成在所述基板上的漂移层、闸极接触点和位于与所述基板相对的所述漂移层的第一表面上的多个源极接触点、位于与所述漂移层相对的所述基板的表面上的汲极接触点、以及多个接面植入(junction implant),所述多个接面植入中的每一者在与所述基板相对的所述漂移层的表面上彼此横向分离并向下朝向所述基板延伸,并且通过在所述漂移层的所述第一表面上放置肖特基金属接触点来形成一个或多个旁路二极管中的每一者,使得每个肖特基金属接触点在所述多个接面植入中的两个接面植入之间运行。[来源:用于将肖特基接触集成到功率晶体管器件中的布局配置由帕拉夫人、爱德华·罗伯特·范布伦特、林成、约翰·威廉姆斯·帕尔穆尔于2016年4月19日在美国专利商标局以us9318597b2的形式公布]。

18、us9876104b2公开了一种多单元mosfet器件,所述器件包括具有集成肖特基二极管的mosfet单元,其中所述mosfet包括在p型井区中形成的n型源极区,所述p型井区形成在n型漂移层中,在所述mosfet的外围形成p型基极接触区,并且所述器件的源极金属化层与邻近所述器件的所述p型基极接触区的n型半导体区形成肖特基接触。[来源:高压半导体器件及其制造方法由凯文·马托查、基兰·查蒂、苏吉特班纳吉于2018年1月23日以us9876104b2的形式公布)。

19、us8436367b1公开了一种场效应型(mosfet、igbt等)sic功率半导体器件,所述器件具有“静音”通道传导、负通道迁移率温度系数、原位“镇流”源极电阻器和优化的单元热管理,以增加安全工作区。通过“主动”通道和“非主动”通道之间的分区以及通过调整感兴趣的温度范围的通道中的载子的迁移率来实现对与汲极电流相关的零温度交叉点(zerotemperature crossover point,ztcp)的位置的控制。”[来源:sic功率垂直dmos,增加了安全操作区域由杜米特鲁·斯杜拉、马克·范登伯格于2013年5月7日在美国专利商标局以us84367b1的形式公开]。

20、考虑到本领域技术人员的知识,长期以来,人们认为需要功率器件具有增加的第三象限交叉电流以克服性能和可靠性问题。

21、此外,图67a图示了垂直平面dmosfet和垂直沟槽umosfet形式的功率mosfet的两种实施方式。术语dmosfet源于相同名称的硅器件,其中n+源极区和p-基极区是由n型杂质和p型杂质通过同一屏蔽开口扩散形成(因此为“双扩散”mosfet)。在sic中,相同的结构通过双注入形成。术语umosfet源自于u形几何结构,但也使用术语沟槽mosfet。从历史上看,第一代sic功率mosfet是umosfet,但很快就加入了离子注入dmosfet。[来源:t.木本,j.a.库珀,《碳化硅技术基础》,ieee出版社(2014),第320-324页。]

22、由于它们的沟槽几何结构,相对于平面器件(诸如dmosfet),umosfet既存在机遇也带来挑战。可以在比dmosfet更小的表面区域中制造umosfet,因为mos通道被定向垂直于表面。由于通道长度由外延生长决定,因此也更容易形成短亚微米通道。然而,在晶体的蚀刻非极性面上形成mos通道,并且闸极氧化层的特性不同于(1000)平面上的特性。与垂直侧壁或11-20晶面或10-10晶面相比,0001晶面上的通道迁移率或场效应迁移率通常比较低。在1000平面上,通道迁移率可在15cm2/vs至25cm2/vs的范围内,而在sic的11-20晶面或10-10晶面上,通道迁移率可高达60cm2/vs至80cm2/vs。[来源:t.木本,j.a.库珀,《碳化硅技术基础》,ieee出版社(2014),第320-324页。]

23、图67b和图67c分别图示了垂直dmosfet和umosfet中的主要电阻,很明显,器件的几何结构有效地消除了存在于dmosfet中的jfet电阻。图67d图示了处于阻断状态的umosfet中的电场,沟槽拐角是出现显著的场拥挤的重要位置。因为氧化物场比半导体中的峰值场高约2.5倍(根据高斯静电定律),这是umosfet器件设计固有的严重问题。[来源:t.木本,j.a.库珀,《碳化硅技术基础》,ieee出版社(2014),第320-324页。]

24、因此,长期以来,人们认为需要将平面dmosfet和沟槽umosfet的所需特征组合到单个器件,可以有利地且灵活地将这样的器件设计为利用每个器件结构的特定优点,从而用于给定应用。此外,长期以来,人们认为需要将接面势垒肖特基(junction barrierschottky,jbs)或混合式pin肖特基(mps)整流元件整合到混合dmosfet/umosfet器件几何结构中。

技术实现思路

1、本文公开了本发明的一个或多个方面。

2、在一方面中,本文描述了一种器件。该器件包括位于sic基板上的单位单元。该单位单元包括闸极绝缘膜、井区中的沟槽、具有第二导电类型的第一下沉区和具有第二导电类型的第二下沉区。第一下沉区的深度等于或大于井区的深度。第一下沉区和第二下沉区中的每一者与具有第一导电类型的区域接触以形成p-n接面。

3、在一个实施例中,该器件包括半导体金属绝缘层半导体晶体管组件。

4、在又一个实施例中,井区紧邻绝缘层半导体界面;以及形成在井区内的第一导电类型的源极区。

5、在又一个实施例中,沟槽的深度大于或等于源极区的厚度。

6、在又一个实施例中,第一下沉区位于沟槽下方。

7、在又一个实施例中,第二下沉区的深度小于第一下沉区的深度。

8、在又一个实施例中,第二下沉区的深度大于井区的深度。

9、在又一个实施例中,该器件在闸极绝缘膜中具有小于4毫欧平方厘米的导通电阻、大于1.5伏的闸极阈值电压、大于500伏的击穿电压以及小于3.5兆伏/厘米的电场。

10、在另一方面中,描述了一种包括sic基板上的单位单元的器件。单位单元包括闸极绝缘膜、井区中的沟槽、第二导电类型的第一下沉区、第二导电类型的第二下沉区以及源极区。源极区与第二下沉区直接接触。

11、在一个实施例中,该器件包括半导体金属绝缘层晶体管组件。

12、在另一个实施例中,单位单元还包括第一导电类型的半导体基极,该半导体基极包括漂移区;紧邻绝缘层半导体界面的第二导电类型的井区;以及形成在井区内的第一导电类型的源极区。

13、在又一个实施例中,沟槽的深度大于或等于源极区的厚度。

14、在又一个实施例中,沟槽的深度大于源极区的深度。

15、在又一个实施例中,该器件具有大于10焦耳/平方厘米的崩溃能量,该崩溃能量通过将以焦耳为单位的崩溃能量除以以平方厘米为单位的总晶粒面积来计算。

16、在又一个实施例中,崩溃故障位于单位单元内。

17、在另一方面中,公开了一种包括位于sic基板上的单位单元的器件。单位单元包括闸极绝缘膜、井区中的沟槽、第二导电类型的第一下沉区、第二导电类型的第二下沉区以及源极区。第一下沉区的深度大于第二下沉区的深度。第二下沉层的宽度大于第一下沉层的宽度。

18、在另一个实施例中,第一下沉区位于沟槽下方。

19、在又一个实施例中,第二下沉区的深度小于第一下沉区的深度。

20、在又一个实施例中,第二下沉区的深度大于井区的深度。

21、在又一方面中,公开了一种包括碳化硅(sic)基板上的单位单元的器件。该单位单元包括第一导电类型第一源极区;第一导电类型第二源极区;第二导电类型井区;以及硅化物层。该器件包括垂直碳化硅(sic)双注入金属氧化物半导体场效应晶体管(dmosfet),该包括位于sic基板背面的汲极端子以及位于sic基板顶面的源极端子。第一导电类型第二源极区的厚度小于第一导电类型第一源极区的厚度。第一导电类型第二源极区散布在第二导电类型井区和硅化物层之间。第一导电类型第二源极区包括位于凹陷的sic沟槽区和第二导电类型井区之间的一片源极区。

22、在一个实施例中,该源极区片包括源极区薄片。

23、在另一个实施例中,第一导电类型第二源极区包括(a)目标厚度和(b)目标掺杂浓度中的至少一者。

24、在又一个实施例中,第一导电类型第二源极区的目标厚度的范围是1nm至1μm,并且目标掺杂浓度的范围是1015cm-3至1021cm-3。

25、在又一个实施例中,第一导电类型第二源极区包括位于硅化物层和第二导电类型井区之间的源极区片。

26、在又一个实施例中,该器件能够在负3伏的汲极电压下承载小于负500毫安的汲极电流。

27、在又一方面中,一种包括碳化硅(sic)基板上的单位单元的器件。该单位单元包括:第一导电类型源极区;第二导电类型井区;以及第二导电类型屏蔽区。第二导电类型屏蔽区被限定在第二导电类型井区内。

28、在一个实施例中,第二导电类型屏蔽区位于金属氧化物半导体场效应晶体管(mosfet)通道内。

29、在另一个实施例中,第二导电类型屏蔽区位于更靠近第二导电类型井区的边缘的位置。

30、在又一个实施例中,第二导电类型井区内的掺杂浓度在横向上是不均匀的。

31、在又一个实施例中,第二导电类型屏蔽区内的掺杂浓度高于第二导电类型井区内的掺杂浓度。

32、在又一个实施例中,第二导电类型屏蔽区延伸超出第二导电类型井区的垂直范围。

33、在又一个实施例中,该器件还包括在第二导电类型井区中的沟槽区。该沟槽区的深度大于或等于第一导电类型源极区的厚度。

34、在又一个实施例中,该器件包括与第二导电类型井区和第一导电类型源极区接触的闸极氧化层。该器件包括双注入金属氧化物半导体场效应晶体管(dmosfet)。

35、在又一个实施例中,该器件包括在金属氧化物半导体场效应晶体管(mosfet)通道内的多个第二导电类型屏蔽区。

36、在又一个实施例中,多个第二导电类型屏蔽区位于更靠近第二导电类型井区域的边缘的位置。

37、在又一个实施例中,多个第二导电类型屏蔽区延伸超出第二导电类型井区的垂直范围。

38、在又一个实施例中,第二导电类型屏蔽区埋入第二导电类型井区内。

39、在又一方面中,公开了一种包括碳化硅(sic)基板上的单位单元的器件。该器件包括第一导电类型源极区;第二导电类型井区;以及第二导电类型屏蔽区。第二导电类型屏蔽区被限定在第二导电类型井区内。第二导电类型屏蔽区将金属氧化物半导体场效应晶体管(mosfet)通道屏蔽以使其免受施加到汲极端子的高电势的影响。

40、在一个实施例中,该器件还包括第二导电类型井区中的沟槽区,该沟槽区的深度大于或等于第一导电类型源极区的厚度。

41、在另一个实施例中,该器件包括大于2.5伏的闸极阈值电压、在0伏的闸极至源极电压下大于3300伏的击穿电压、小于15毫欧平方厘米的导通电阻以及在1500伏的汲极电压下大于4微秒的短路耐受时间。

42、在又一个实施例中,该器件包括大于2伏的闸极阈值电压、在0伏的闸极至源极电压偏压下大于1200伏的击穿电压、小于4.5毫欧平方厘米的导通电阻以及在800伏的汲极电压下大于2.5微秒的短路耐受时间。

43、在又一个实施例中,该器件包括大于2.5伏的闸极阈值电压、在0伏的闸极至源极电压下大于6500伏的击穿电压、小于50毫欧平方厘米的导通电阻以及在3600伏的汲极电压下大于4微秒的短路耐受时间。

44、在又一个实施例中,该器件包括大于2.5伏的闸极阈值电压、在0伏的闸极至源极电压下大于10000伏的击穿电压、小于100毫欧平方厘米的导通电阻以及在5000伏的汲极电压下大于4微秒的短路耐受时间。

45、在又一个实施例中,该器件包括大于2.5伏的闸极阈值电压、在0伏的闸极至源极电压下大于13000伏的击穿电压、小于400毫欧平方厘米的导通电阻以及在10000伏的汲极电压下大于4微秒的短路耐受时间。

46、在又一个实施例中,第二导电类型屏蔽区在关断状态和阻断操作其中之一期间屏蔽金属氧化物半导体场效应晶体管(mosfet)通道,使其免受施加到汲极端子的高电势的影响。

47、在又一方面中,本文描述了一种方法。该方法包括形成碳化硅(sic)金属氧化物半导体场效应晶体管(mosfet);形成第二导电类型井区;在第二导电类型井区内形成第一导电类型源极区;以及形成第二导电类型屏蔽区。第二导电类型屏蔽区位于第一导电类型源极区之外。

48、在一个实施例中,第二导电类型屏蔽区位于第二导电类型井区内。

49、在另一个实施例中,第二导电类型屏蔽区延伸超出第二导电类型井区。

50、在又一个实施例中,在sic外延芯片上制造sic mosfet,该sic外延芯片的掺杂在1014cm-3至1018cm-3的范围内并且厚度在1微米(μm)至300微米(μm)的范围内。

51、在又一个实施例中,形成第二导电类型井区包括:沉积硬屏蔽,该硬屏蔽包括二氧化硅层、氮化硅层、多晶硅层、氮氧化硅层和金属层中的至少一者并且总厚度在50纳米至5微米的范围内;形成硬屏蔽图案;蚀刻硬屏蔽;以及使用第二导电类型离子进行离子注入和外延生长中的一者。执行离子注入的步骤包括以10kev至1000kev的能量以及1012cm-2至1015cm-2的注入剂量注入第二导电类型离子。该第二导电类型离子包括铝和硼中的一者。

52、在一个实施例中,形成第二导电类型屏蔽区包括形成更靠近第二导电类型井区的边缘的第二导电类型屏蔽区。

53、在另一个实施例中,形成第二导电类型屏蔽区包括形成限制在第二导电类型井区内的第二导电类型屏蔽区。

54、在又一个实施例中,该方法还包括形成金属氧化物半导体场效应晶体管(mosfet)通道。

55、在又一个实施例中,形成第二导电类型屏蔽区包括形成与金属氧化物半导体场效应晶体管(mosfet)通道接触的第二导电类型屏蔽区。

56、在又一个实施例中,形成第二导电类型屏蔽区包括形成与金属氧化物半导体场效应晶体管(mosfet)通道接触的多个第二导电类型屏蔽区。

57、在又一个实施例中,形成第一导电类型源极区包括使用氮离子和磷离子中的一者形成第一导电类型源极区。

58、在又一个实施例中,该方法还包括形成闸极氧化层;形成多晶硅闸极层;形成层间电介质(inter-layer dielectric,ild)层;形成硅化物区域;以及形成互连金属层。

59、在又一个实施例中,形成闸极氧化层包括对二氧化硅层、氮化硅层和氮氧化硅层中的一者的电介层执行热氧化和化学气相沉积(cvd)中的一者或堆栈组合。形成的闸极氧化层的厚度在10纳米至100纳米的范围内。

60、在又一个实施例中,形成多晶硅闸极层包括使用电浆增强化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)和低压化学气相沉积(low-pressurechemical vapor deposition,lpcvd)中的一者通过原位掺杂和后续推进掺杂中的一者来沉积多晶硅层。

61、在又一个实施例中,形成层间电介质(ild)层包括沉积二氧化硅层、氮化硅层和氮氧化硅层中的至少一者;以及二氧化硅层、氮化硅层和氮氧化硅层的堆栈组合。ild层的厚度大于或等于50纳米。

62、在又一个实施例中,形成硅化物区域包括在暴露的sic表面上形成硅化镍区域。

63、在又一个实施例中,形成第二导电类型屏蔽区包括形成延伸超出第二导电类型井区的垂直范围的第二导电类型屏蔽区。

64、在又一方面中,本文描述了一种方法。该方法包括形成碳化硅(sic)金属氧化物半导体场效应晶体管(mosfet);形成第二导电类型井区;在第二导电类型井区内形成第一导电类型源极区;以及形成第二导电类型屏蔽区。第二导电类型屏蔽区位于第一导电类型源极区之外。在金属氧化物半导体场效应晶体管(mosfet)通道内的第二导电类型井区中的掺杂浓度是不均匀的。第二导电类型屏蔽区的至少一部分位于第二导电类型井区内。

65、在一个实施例中,第二导电类型屏蔽区在不同位置处的掺杂浓度分布不同。

66、在另一个实施例中,第二导电类型屏蔽区在不同位置处的掺杂浓度分布没有什么不同。

67、在又一方面中,本文描述了一种半导体组件。该半导体组件包括第一导电类型的半导体基极,该半导体基极包括电压阻断层;以及在接触表面上的第二导电类型岛;以及电压阻断层上的金属层。金属层和电压阻断层包括肖特基接触和包括第一导电类型的第一导电类型层,并且该第一导电类型层不与肖特基接触接触,该肖特基接触散布在第二导电类型岛之间。

68、在一个实施例中,第一导电类型层的垂直范围低于第二导电类型岛的底部。

69、在另一个实施例中,第一导电类型层的垂直范围高于第二导电类型岛的底部。

70、在又一个实施例中,第一导电类型层内的掺杂浓度在垂直于肖特基接触的方向上是不均匀的。

71、在又一个实施例中,第一导电类型层的垂直范围高于或低于第二导电类型岛的底部。

72、在又一个实施例中,第一导电类型层的掺杂浓度沿接触表面的任何方向上不发生变化。

73、在又一个实施例中,第一导电类型层的第一掺杂浓度高于漂移区的第二掺杂浓度。

74、在又一个实施例中,第一导电类型层的第一掺杂浓度低于漂移区的第二掺杂浓度。

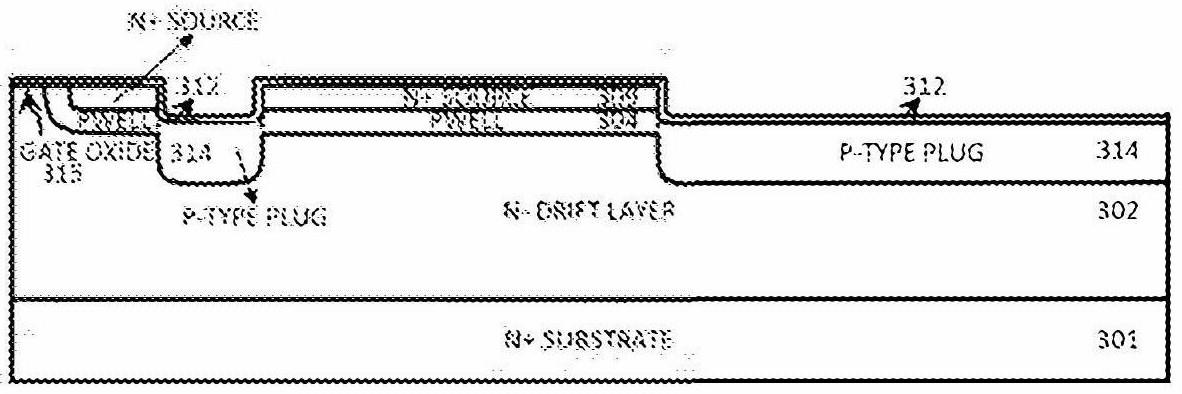

75、在又一个实施例中,肖特基接触包含包括al、ag、au、mo、ni、ti、w、tixwy、tixny或它们的组合的金属。

76、在又一方面中,一种包括散布在与肖特基层接触的n-区域和n+区域内的p+岛的二极管。

77、在一个实施例中,n+区域的垂直范围低于p+岛的底部。

78、在另一个实施例中,n+区域的垂直范围高于p+岛的底部。

79、在又一个实施例中,n+区域内的掺杂浓度在垂直于肖特基层的方向上是不均匀的。

80、在又一个实施例中,n+区域的垂直范围高于或低于p+岛的底部。

81、在又一方面中,一种包括散布在与肖特基层接触的p-区域和p+区域内的n+岛的二极管。

82、在一个实施例中,p+区域的垂直范围低于n+岛的底部。

83、在另一个实施例中,p+区域的垂直范围高于n+岛的底部。

84、在又一个实施例中,p+区域内的掺杂浓度在垂直于肖特基层的方向上是不均匀的。

85、在又一个实施例中,p+区域的垂直范围高于或低于n+岛的底部。

86、在一方面中,本文公开了一种金属绝缘层半导体场效应晶体管。该金属绝缘层半导体场效应晶体管包括位于sic基板上的单位单元。该单位单元包括在第二导电类型的井区、第一导电类型的源极区、第二导电类型的第一下沉区以及该第二导电类型的第二下沉区中的沟槽。第一下沉区的深度等于或大于井区的深度。第一下沉区和第二下沉区中的每一者与第一导电类型的区域接触,从而形成p-n接面。

87、在一个实施例中,第一下沉区的深度大于第二下沉区的深度。第二下沉层的宽度大于第一下沉层的宽度。

88、在另一方面中,本文公开了一种金属绝缘层半导体场效应晶体管。该金属绝缘层半导体场效应晶体管包括位于碳化硅(sic)基板上的单位单元。该单位单元包括:第一导电类型源极区;第二导电类型井区;以及第二导电类型屏蔽区。第二导电类型屏蔽区位于第一导电类型源极区之外。

89、在一个实施例中,第二导电类型屏蔽区延伸超出第二导电类型井区的垂直范围。

90、在另一个实施例中,该器件还包括位于第二导电类型井区中的沟槽区。该沟槽区的深度大于并等于第一导电类型源极区的厚度。

91、在又一个实施例中,该器件还包括位于沟槽区正下方的第一导电类型的下沉区。

92、在又一方面中,本文公开了一种半导体组件。该半导体组件包括第一导电类型的半导体基极,该半导体基极包括电压阻断层;以及在接触表面上的第二导电类型岛;以及电压阻断层上的金属层。金属层和电压阻断层包括肖特基接触和包括第一导电类型的第一导电类型层,并且该第一导电类型层不与肖特基接触接触,该肖特基接触散布在第二导电类型岛之间。

93、在一个实施例中,第一导电类型层的垂直范围低于第二导电类型岛的底部。

94、在另一个实施例中,第一导电类型层内的掺杂浓度在垂直于肖特基接触的方向上是不均匀的。

95、在又另一方面,本文公开了一种碳化硅二极管。该碳化硅二极管包括散布在第一导电类型的第二区域以及与金属层接触的第一导电类型的第一区域内的第一导电类型岛。

96、附图的简单说明

97、本发明或申请文件包括至少一幅彩色图式。在支付必要费用之后,智慧财产局将应要求提供附带彩色图纸的本发明或本发明之专利申请出版物的副本。

98、图1a图示了b.j.巴利加在先进的高压功率器件概念(施普林格出版社,2011)中报告的现有技术sic dmosfet结构。

99、图1b图示了为图1a中的现有技术sic dmosfet结构模拟的电场等值线。

100、图1c图示了图1a中的现有技术sic dmosfet结构的电场分布。

101、图2a图示了具有p+插塞区的sic dmosfet的实施例,该p+插塞区通过n+源极接触点将p井区接地。

102、图2b图示了图2a中的sic dmosfet结构的击穿模拟。

103、图3图示了sic dmosfet的实施例,其中图2a中的p+插塞区被深p型下沉#1区替代。

104、图4a至图4r为图示了用于制造图3中的sic dmosfet结构的制程步骤的横截面图。

105、图5a图示了sic dmosfet的实施例,其中除了深p型下沉#1区之外,还在n+源极区下方形成了p型下沉#2区。

106、图5b图示了根据图3和图5a所示的实施例设计的sic dmosfet结构的击穿模拟。

107、图6a至图6j为图示了用于制造图5a中的sic dmosfet结构的制程步骤的横截面图。

108、图7a图示了sic dmosfet的实施例,其中在注入p型下沉#1区之前,将沟槽蚀刻到n+源极区中。

109、图7b图示了图7a中的sic mosfet结构的击穿模拟。

110、图8a至图8bb为图示用于制造图7a中的sic dmosfet结构的制程步骤的横截面图。

111、图9图示了用于形成自对准mos通道的现有技术sic dmosfet制程。

112、图10图示了用于去除形成在外围的寄生n+源极区的sic dmosfet结构的实施例。

113、图11a至图11gg为图示了用于制造图10中的sic dmosfet结构的制程步骤的横截面图。

114、图12图示了具有专用制程步骤的sic dmosfet的实施例,该专用制程步骤用于掩蔽器件外围中的n+源极区的注入。

115、图13a至图13gg为图示了用于制造图12中的sic dmosfet结构的制程步骤的横截面图。

116、图14图示了具有专用制程步骤的sic dmosfet的实施例,该专用制程步骤用于掩蔽器件外围中的n+源极区以及主动区中的n+源极区的注入,以实现与p井区的欧姆接触

117、图15a至图15ff为图示了用于制造图14中的sic dmosfet结构的制程步骤的横截面图。

118、图16图示了sic dmosfet的实施例,其中多晶硅闸极金属化层在外围区域中被分段。

119、图17a至图17ff为图示了用于制造图16中的sic dmosfet结构的制程步骤的横截面图。

120、图18图示了sic dmosfet的实施例,其中mos通道的一部分位于(1000)晶面上并且第二部分位于(11-20)晶面或(11-00)晶面上。

121、图19a至图19u为图示了用于制造图18中的sic dmosfet结构的制程步骤的横截面图。

122、图20图示了sic dmosfet的实施例,其中mos通道的一部分位于(1000)晶面上,第二部分位于(11-20)晶面或(11-00)晶面上,p井沟槽更深,并且在n+源极区下方形成第二p井区。

123、图21a至图21v为图示了用于制造图20中的sic dmosfet结构的制程步骤的横截面图。

124、图22为现有技术并且图示了4h-sic平面mosfet的p-基掺杂浓度与阈值电压的关系图。

125、图23a到图23d图示了用于在p井区内的场屏蔽的sic dmosfet结构的实施例。

126、图24a至图24u为图示了用于制造图23a中的sic dmosfet结构的制程步骤的横截面图。

127、图25a到图25d图示了埋在p井结构内形成的用于场屏蔽的sic dmosfet结构的实施例。

128、图26a至图26u为图示了用于制造图25a中的sic dmosfet结构的制程步骤的横截面图。

129、图27为现有技术sic mps二极管的截面示意图。

130、图28a为具有埋置的n+区域的mps二极管结构的实施例。

131、图28b为图28a中描述的实施例的i-v特性。

132、图28c为图28a中的器件的横截面的比较。

133、图29a至图29l为图示了用于制造图28a所示的sic mps二极管的制程步骤的横截面图。

134、图30为mps二极管结构的实施例,其中n+区域的底部高于p+区域的底部。

135、图31a至图31l为图示了用于制造图30所示的sic mps二极管的制程步骤的横截面图。

136、图32a至图32f为具有多个n子区域、p子区域或两者的mps二极管结构的实施例。

137、图33aa至图33al为图示了用于制造图32a所示的sic mps二极管的制程步骤的横截面图。

138、图33ba至图33bl为图示了用于制造图32b所示的sic mps二极管的制程步骤的横截面图。

139、图33ea至图33el为图示了用于制造图32e所示的sic mps二极管的制程步骤的横截面图。

140、图33fa至图33fl为图示了用于制造图32f所示的sic mps二极管的制程步骤的横截面图。

141、图34为mps二极管结构的实施例,该二极管结构具有两种不同类型的p+井,取决于它们的深度与n+层的深度相比。

142、图35a至图35p为图示了用于制造图34所示的sic mps二极管的制程步骤的横截面图。

143、图36a为本发明的器件在w1/d1的变化比率下的阻断性能。

144、图36b为本发明的器件在w1/d1的变化比率下的阻断i-v曲线。

145、图36c为本发明的器件在w1/d1的变化比率下的正向i-v曲线。

146、图36d为本发明的器件在w1/d1的变化比率下的差分比导通电阻的性能。

147、图37a图示了根据一个实施例的dmosfet的器件结构。

148、图37b图示了根据一个实施例的接面型场效应晶体管(jfet)的器件结构。

149、图38图示了根据一个实施例的使用离子注入形成的n型层的示例。

150、图39a至图39c图示了根据各种实施例的jfet中的相对于p+闸极层的n层垂直范围。

151、图40a至图40c图示了根据各种实施例的dmosfet中的相对于p井层的n层垂直范围。

152、图41a至图41e为垂直jfet的横截面示意图,图示了用于图37b所示的器件的制程步骤。

153、图42a至图42d为功率mosfet结构的横截面示意图,图示了用于图37a所示的器件的制程步骤。

154、图43a和图43b图示了使用本发明的示教制造的1200v sic dmosfet的输出和击穿i-v特性。

155、图44a和图44b图示了使用本发明的示教制造的1200v sic mosfet的转移(id v/svgs)特性。

156、图45为对使用本发明的示教制造的1200v sic mosfet进行测量所得的单脉冲崩溃能量。

157、图46为图示了使用这些发明的示教制造并测试单脉冲崩溃能量测试的sicdmosfet的照片。

158、图47a和图47b为使用这些发明的示教制造的两个3.3kv sic mosfet的输出特性。

159、图47c为使用这些发明的示教制造的两个3.3kv sic mosfet的转移特性。

160、图47d为对使用本发明的示教制造的两个3.3kv sic mosfet进行测量的短路测试。

161、图48a图示了双注入金属氧化物半导体场效应晶体管(dmosfet)的单位单元的横截面结构的实施例,该dmosfet包括在第一导电类型第一源极区内的第一导电类型第二源极区。

162、图48b图示了dmosfet的一个或多个单位单元的横截面结构的实施例,包括集成肖特基二极管的一个或多个单位单元,每个dmosfet单位单元包括在第一导电类型第一源极区内的第一导电类型第二源极区。

163、图48c图示了沟槽闸极mosfet的一个或多个单位单元的横截面结构的实施例,包括集成肖特基二极管的一个或多个单位单元,每个mosfet单位单元包括在第一导电类型第一源极区内的第一导电类型第二源极区。

164、图49a至图49t图示了制造图48a中所示的dmosfet结构的制程的实施例。

165、图50a图示了具有常规p-n接面的sic dmosfet与具有去激活p-n接面的sicdmosfet(即,第一导电类型第二源极区)的电压-电流特性的实施例。

166、图50b为图示了与晶粒相关的dmosfet的侧面的实施例的透视图。

167、图50c和50d图示了分别通过mosfet以及通过h桥电路中的本质反并联二极管区的电流流动路径。

168、图51a图示了双注入金属氧化物半导体场效应晶体管(dmosfet)的单位单元的横截面结构的实施例,该dmosfet包括在第一导电类型第一源极区内的第一导电类型第二源极区。

169、图51b图示了dmosfet的一个或多个单位单元的横截面结构的实施例,包括集成肖特基二极管的一个或多个单位单元,每个dmosfet单位单元包括在第一导电类型第一源极区内的第一导电类型第二源极区。

170、图52a至图52t图示了制造图51a中所示的dmosfet结构的制程的实施例。

171、图53a图示了双注入金属氧化物半导体场效应晶体管(dmosfet)的单位单元的横截面结构的实施例,该dmosfet包括与第二导电类型井接触区直接接触的第一金属区。

172、图53b图示了dmosfet的一个或多个单位单元的横截面结构的实施例,包括集成肖特基二极管的一个或多个单位单元,每个dmosfet单位单元包括与相应的第二导电类型井接触区直接接触的第一金属区。

173、图53c图示了通过本质p-n接面二极管区与并联连接到dmosfet的肖特基二极管区的第三象限电流传导的实施例。

174、图53d图示了在将一个或多个肖特基二极管区与dmosfet的一个或多个基极二极管区串联连接后通过dmosfet的第三象限电流传导的实施例。

175、图54a至图54x图示了制造图53a中所示的dmosfet结构的制程的实施例。

176、图55a、图55b和图55c图示了双注入金属氧化物半导体场效应晶体管(dmosfet)的单位单元的横截面结构的实施例,该dmosfet包括分别在三个不同位置处弯曲的第二导电类型井接触区。

177、图55d、图55e和图55f图示了二极管集成dmosfet的一个或多个单位单元的横截面结构的实施例,每个dmosfet单位单元包括分别在三个不同位置处弯曲的第二导电类型井接触区。

178、图56a至图56t图示了制造图55a中所示的dmosfet结构的制程的实施例。

179、图57a至图57t图示了制造图55b中所示的dmosfet结构的制程的实施例。

180、图58a至图58t图示了制造图55c中所示的dmosfet结构的制程的实施例。

181、图59a、图59b和图59c图示了双注入金属氧化物半导体场效应晶体管(dmosfet)的单位单元的横截面结构的实施例,该dmosfet包括分别在三个不同位置处弯曲的第二导电类型井接触区,使第二导电类型井区能够仅通过第二导电类型井接触区与源极金属接触。

182、图59d、图59e和图59f图示了二极管集成dmosfet的一个或多个单位单元的横截面结构的实施例,每个dmosfet单位单元包括分别在三个不同位置处弯曲的第二导电类型井接触区,使第二导电类型井区能够仅通过第二导电类型井接触区与源极金属接触。

183、图59g图示了二极管集成沟槽闸极mosfet的一个或多个单位单元的横截面结构的实施例,包括集成肖特基二极管的一个或多个单位单元,每个mosfet单位单元包括在第一位置处的第二导电类型井接触区,使第二导电类型井区能够仅通过第二导电类型井接触区与源极金属接触。

184、图60a至图60t图示了制造图59a中所示的dmosfet结构的制程的实施例。

185、图61a至图61t图示了制造图59b中所示的dmosfet结构的制程的实施例。

186、图62a至图62t图示了制造图59c中所示的dmosfet结构的制程的实施例。

187、图63图示了功率mosfet的一个或多个单位单元的横截面结构的实施例,该一个或多个单位单元的第一单位单元包括位于半导体基板的水平表面和沟槽侧壁上的第一金属氧化物半导体(mos)界面,并且该一个或多个单位单元的第二单位单元包括仅形成在该沟槽侧壁上的第二金属氧化物半导体(mos)界面。

188、图64a至图64ab为图示了制造图63中所示的mosfet结构的制程的实施例的横截面图。

189、图65图示了功率mosfet的一个或多个单位单元的横截面结构的实施例,该一个或多个单位单元的第一单位单元包括在半导体基板的水平表面和沟槽侧壁上的第一金属氧化物半导体(mos)界面,并且该一个或多个单位单元的第二单位单元包括与mosfet的第一导电类型漂移层相邻形成的金属区。

190、图66a至图66aa为图示了制造图65中所示的mosfet结构的制程的实施例的横截面图。

191、图67a图示了垂直平面dmosfet和垂直沟槽umosfet形式的功率mosfet的两种实施方式。

192、图67b和图67c分别图示了垂直dmosfet和umosfet中的主要电阻,很明显,器件的几何结构有效地消除了存在于dmosfet中的jfet电阻。

193、图67d图示了处于阻断状态的umosfet中的电场,沟槽拐角是显著场拥挤的重要位置。

194、根据附图和下面的详细说明,本实施例的其他特征将会显而易见。

195、具体描述

196、定义与一般技术

197、除非本文另有限定,否则与本发明相关的科学和技术术语应具有本领域普通技术人员通常理解的含义。此外,除非上下文另有要求,单数术语应包括复数,并且复数术语应包括单数。一般而言,本文所述的与半导体处理相关的命名法以及半导体处理技术是本领域中公知且常用的命名法和技术。

198、除非另有说明,否则通常按本领域公知的常规方法执行本发明的方法和技术,并且如在本说明书通篇引用和讨论的各种通用且更具体的参考文献中所述。本文所述的与半导体器件技术、半导体处理和其他相关领域相关的命名法以及流程和技术是本领域中公知且常用的命名法以及流程和技术。

199、为了使图示简单明了,附图图示了构造的一般方式,并且可能省略了众所周知的特征和技术的描述和细节,以避免造成本公开被不必要地模糊化。此外,附图中的元素不一定按比例绘制。例如,相对于其他元素,图中的一些元素的尺寸可能被放大,从而有助于提高对本公开的实施例的理解。不同图中的相同参考编号代表相同的元素。

200、说明书和请求项书中的术语“第一”、“第二”、“第三”、“第四”等(如果有)用于区分类似元素,而不一定是用于描述特定的次序或时间顺序。应当理解,如此使用的术语在适当的情况下是可互换的,例如,使得本文所述的实施例能够以除了本文所示或以其他方式描述的顺序之外的顺序进行操作。此外,术语“包括”和“具有”及它们的任何变体意在涵盖非排他性包含,使得包括一系列元素的制程、方法、系统、物品、器件或装置不一定限于这些元素,但可包括未明确列出的或该制程、方法、系统、物品、器件或装置所固有的其他元素。

201、说明书和请求项书中的术语“左”、“右”、“前”、“后”、“顶部”、“底部”、“上”、“下”等(如果有)用于说明性目的,不一定用于说明永久的相对位置。应当理解,如此使用的术语在适当的情况下是可互换的,例如,使得本文所述的装置、方法和/或制品的实施例能够在除了本文所示或以其他方式描述的方向以外的方向上进行操作。

202、除非明确说明,否则不应将本文所使用的任何元素、行为或指令解释为关键或必要的。此外,如本文所使用的,冠词“一个”和“一”意在包括各项目,并且可以与“一个或多个”互换使用此外,如本文所使用的,术语“组”意在包括各项目(例如,相关项目、无关项目、相关项目和无关项目的组合等),并且可以与“一个或多个”互换使用。如果仅使用一个项目,则使用术语“一”或类似语言。此外,如本文所使用的,术语“具有”、“拥有”、“有”等意在作为开放式术语。此外,除非另有明确说明,否则短语“基于”意指“至少部分基于”。

203、除非另有说明,否则以下术语和短语应理解为具有以下含义。

204、如本文所用,术语“单位单元”是指半导体中重复出现的半导体中的图案片段。

205、如本文所用,术语“sic”是指作为化合物半导体的碳化硅,是化学式为sic的硅和碳的混合物。硅与碳共价键合。在4h sic中,ramsdell分类方案中包含4h,此处数字表示层数,字母表示bravais晶格。这意味着4h-sic结构具有四个六边形sic层。sic存在于一种称为多型体的多晶型晶体结构中,例如3c-sic、4h-sic、6h-sic。目前,4h-sic被用于功率器件制造。[来源:4h sic mosfet在纳米尺度上的完整分析电势解决方案由m k亚达夫、k p普拉丹和pk萨胡于2016年5.月24日公开·2016越南科技翰林院]

206、如本文所用,术语“基板”是指在其上或其中制造或附接集成电路的组件的支撑材料。

207、如本文所用,术语“jfet”是指接面闸场效应晶体管,它是一种可用作电子控制开关、放大器或电压控制电阻器的三端半导体器件。fet(场效应晶体管)是一种单极晶体管,其中电流载子注入源极端子并且通过半导体材料通道传递到汲极端子,其导电性在很大程度上取决于从控制电极施加到半导体的电场。主要有两种类型的fet,即接面fet和绝缘闸极fet。在接面fet中,闸极通过pn接面与通道隔离。在绝缘闸极fet中,闸极通过绝缘层与通道隔离,使得闸极和通道形成电容器,其中绝缘层作为电容器电介质。

208、如本文所用,术语“mosfet”是指金属氧化物半导体场效应晶体管,它是一种具有源极(s)、闸极(g)、汲极(d)和基极(b)端子的四端器件。mosfet的基极经常连接到源极端子,使其成为类似场效应晶体管的三端器件。

209、如本文所用,术语“dmosfet”是指双注入金属氧化物半导体场效应晶体管。sicmosfet的常见物理结构是4h-sic中的平面双注入mosfet(sic-dmosfet)。

210、如本文所用,术语“掺杂剂”是指通过扩散、涂覆或注入基板(例如改变其性质)从外部来源添加到材料中的杂质。在半导体技术中,可向半导体中添加杂质以改变其电特性,或向材料中添加杂质以产生具有所需电特性的半导体。n型(负)掺杂剂(例如,用于iv族半导体的磷)通常来自元素周期表的v族。当添加到半导体中时,n型掺杂剂会产生一种含有传导电子的材料。p型(正)掺杂剂(例如,用于iv族半导体的硼)通常来自iii族并形成传导电洞(conduction hole,即电子壳中的空位)。

211、如本文所用,术语“汲极”是指接收从源极电极通过晶体管通道的电荷载子的场效应晶体管的电极。

212、如本文所用,术语“源极”是指场效应晶体管中电荷载子的来源连接到的主动区/电极。

213、如本文所用,术语“闸极”是指对与其直接相关联的半导体区域施加影响从而以临时方式改变半导体区域的导电特性(通常产生开/关式开关动作)的控制电极或控制区域。场效应晶体管的控制电极或控制区域位于源极和汲极及它们的区域之间。

214、如本文所用,术语“杂质”是指存在于半导体晶体中的异物(诸如硅中的硼或砷),它被添加到半导体中以产生p型或n型半导体材料,或以其他方式形成其电特性取决于杂质掺杂剂原子的材料。

215、如本文所用,术语“pn接面”是指p型半导体和n型半导体之间的过渡界面和过渡区。

216、如本文所用,术语“多晶硅”是指硅的多晶形式。

217、如本文所用,术语“p型”是指其中的空穴密度超过传导电子密度的非本质半导体。

218、如本文所用,术语“带隙”是指束缚在其原子核上的电子的能级(价电子)与允许电子自由迁移的能级(传导电子)之间的差异。带隙取决于所涉及的特定半导体。

219、如本文所用,术语“击穿”是指反向偏压半导体器件(例如,p型半导体材料和n型半导体材料之间的反向偏压接面)中从高动态电阻到极低动态电阻的突然变化,其中对于反向施加的电压的小幅增加,反向电流会快速增加,并且器件的行为就好像是它有负电阻一样。

220、如本文所用,术语“通道”是指用于在场效应晶体管的源极和汲极之间传导电流的路径。

221、如本文所用,术语“芯片”是指其上形成一个或多个主动或被动固态电子器件的半导体材料单晶基板。芯片可包含集成电路。在封装并配备外部连接器之前,芯片通常无法使用。

222、如本文所用,术语“接触点”是指与另一电导体或电气组件接触以向该导体或电气组件输送电流或从其输送电流的导体的点或部分。

223、如本文所用,术语“晶粒”是指与半导体切片分离的其上形成一个或多个主动电子元件的一小块半导体材料。有时被称为芯片。n+基板。

224、如本文所用,术语“下沉层”是指dmosfet结构内的关键位置处的深注入区域

225、如本文所用,术语“插塞”是指用于将井和源极接触点接地的结构。

226、如本文所用,术语“漂移层”是指用于支持功率mosfet中的高电压的轻掺杂区域

227、如本文所用,术语“井”是指金属氧化物半导体(mos)晶体管中的某些区域。总是在“井”区域中创造mos晶体管。pmos(正通道mos)晶体管制造在被称为“n井”区域的n掺杂区域。类似地,nmos晶体管(负通道mos)制造在被称为“p井”的“p型”区域。这确保了由于存在晶体管区域和井区之间的反向偏压,两个晶体管之间的通过底面的泄漏较低。

228、如本文所用,术语“源极互连金属化层”是指使用细线金属图案互连数千个mosfet的互连金属化层。

229、如本文所用,术语“自对准”是指半导体器件制造中的处理步骤。通常需要在集成电路制造的不同光刻阶段所制造的结构之间实现精确对准。如果结构是“自对准”的(这意味着在光刻定义的一系列位置中,一个结构被强制进入相对于另一个结构的特定位置),则可以放宽对光刻对准公差的严格要求。

230、如本文所用,术语“器件”是指在物理上独立的基极中实现客观存在的单个电气元件,在不破坏其所述功能的情况下,该电气元件无法被进一步分割。

231、如本文所用,术语“表面”是指物体的外部或外部边界。

232、如本文所用,术语“沟槽”是指通过使用基板表面上的凹槽或其他凹口对单片集成电路中的电子元件进行电隔离,这些凹槽或凹口可以填充或不填充电绝缘(即电介质)材料。

233、如本文所用,术语“电介质”是指非导电体,也称为绝缘体。

234、如本文所用,术语“迁移率”是指当受到外加电场时载子移动通过半导体的能力。在同一半导体中,电子和空穴通常具有不同的迁移率。

235、如本文所用,术语“rie”是指反应离子蚀刻(reactive ion etching),rie是用于微加工的蚀刻技术。rie是一种干法蚀刻,其特性与湿法蚀刻不同。rie使用化学反应电浆去除沉积在晶圆上的材料。电浆由电磁场在低压(真空)下产生。来自电浆的高能离子攻击晶圆表面并与之发生反应。

236、如本文所用,术语“ild”是指层间电介质,一种电介质材料,用于在高级集成电路中将布置在多个层级(多级金属化层)中的紧密间隔的互连线电分离。

237、如本文所用,术语“cvd”是指化学气相沉积,它是一种通常在真空下生产高质量、高性能固体材料的方法。在半导体工业中,该制程通常用于生产薄膜。在典型的cvd中,晶圆(基板)暴露于一个或多个挥发性前体,该前体在基板表面上反应和/或分解从而产生所需的沉积物。通常,也会产生挥发性副产物,该副产物通过流经反应室的气流去除。

238、如本文所用,术语“pecvd”是指用于在基板上从气态(气相)到固态沉积薄膜的电浆增强化学气相沉积制程。该制程涉及化学反应,该化学反应在产生反应气体的电浆之后发生。

239、如本文所用,术语“lpcvd”是指低压化学气相沉积技术,该技术利用热量引发前体气体在固体基板上的反应。在表面上发生这种反应形成了固相材料。

240、如本文所用,术语“dibl”是指汲极诱导势垒降低(drain inducedbarrierlowering),其为mosfet中的短通道效应,最初指的是在较高汲极电压下晶体管阈值电压的降低。在具有长通道的经典平面场效应晶体管中,通道形成的瓶颈发生在离汲极接触点足够远的位置处,通过基板和闸极的组合对其进行静电屏蔽以使其免受汲极电势的影响,因此传统上阈值电压与汲极电压无关。在短通道器件中,这一点已不再适用:汲极电势会对通道进行门控,因此高汲极电压可打开瓶颈,并且提前导通电晶体。

241、如本文所用,术语“icp”是指电感耦合电浆蚀刻技术(inductivelycoupledplasma etching),该技术通常用于器件制造的专用半导体市场。这项技术可结合化学反应和离子诱导蚀刻两者。对离子通量进行独立控制可实现高度的制程灵活性。icp蚀刻基于使用电感耦合电浆来源。由于rf天线和电浆之间的感应耦合,icp来源产生高密度电浆。位于电浆生成区的天线产生交变rf磁场,并诱导rf电场,从而激发在低压下参与气体分子和原子电离的电子。由于在反应器壁附近不存在电场,因此实际上没有对壁造成离子轰击或腐蚀。

242、如本文所用,术语“p-屏蔽”是指精心设计的p型掺杂区域,其被策略性地置于mosfet通道区域附近或内部,目的是在关断状态和阻断操作期间屏蔽mosfet通道,使其免受施加到汲极端子的高电势的影响。

243、如本文所用,术语“第一导电类型区域”和“第二导电类型区域”分别用于描述n型器件的n型区和p型区。对于p型器件,“第一导电类型区域”和“第二导电类型区域”分别用于描述p型区和n型区。

244、如本文所用,术语“i-v特性曲线”是指电气器件或组件的电流-电压特性曲线或简称为i-v曲线,它是指用于定义其在电路中的操作的一组图形曲线。

245、如本文所用,术语“mv/cm”是指兆伏/厘米,指的是电场的单位。

246、如本文所用,术语“崩溃故障”是指在绝缘材料和半导体材料两者中都可能发生的现象。它是电流倍增的一种形式,可以在原本是良好绝缘体的材料中产生非常大的电流。这是一种电子崩溃。当过渡区中的载子被电场加速到足以通过与束缚电子碰撞产生可移动或自由电子-空穴对的能量时,就会发生崩溃过程。发生击穿时的电压被称为击穿电压。崩溃故障可导致半导体器件结构损坏。

247、如本文所用,术语“崩溃能量”定义为当mosfet被设置为崩溃模式或超过其击穿电压时,mosfet能够承受的能量的量。

248、如本文所用,术语“顶面”是指dmosfet的外侧/顶部。垂直sic dmosfet的顶面可包括源极端子。

249、如本文所用,术语“底面”是指dmosfet的底侧/基座。垂直sic dmosfet的底面可包括汲极端子。

250、如本文所用,术语“正面”是指在前面可见的dmosfet的侧面。

251、如本文所用,术语“背面”是指dmosfet的背侧。垂直sic dmosfet的背面可包括汲极端子。

252、如本文所用,术语“加”是指金属氧化物半导体(mos)晶体管中掺杂浓度过高的特定区域。

253、如本文所用,术语“主动区”是指发生电流传导的dmosfet区域。

254、如本文所用,术语“耗尽区”是指带电载子的流动在给定时间内减少的区域。

255、如本文所用,术语“热预算”是指在给定的高温操作期间转移到晶圆的热能总量。

256、如本文所用,术语“功函数”是指将电子从给定金属的表面移至无穷远处所需的最小能量。

257、如本文所定义,如果两个或更多个元件由相同的材料组成,则它们是“一体的”。如本文所定义,如果两个或更多个元件由不同的材料组成,则它们是“非一体的”。

258、如本文所用,术语“沟槽侧壁”是指形成沟槽区的侧面的壁。

259、如本文所用,术语“底部”是指沟槽区的基部。

260、如本文所用,术语“晶面”是指其中存在大量原子的半导体基板的晶体内部的假想平面。

261、如本文所用,术语“mos界面”是指电互连两个区域的区域/路径。

262、如本文所用,术语“水平表面”是指半导体基板的顶面上的未蚀刻表面。

263、如本文所用,术语“rf”是指射频(radio frequency)。射频是交流电流或电压或磁场、电场或电磁场或机械系统的振荡率。

264、实施例涉及sic dmosfet功率器件,其中p井区有效地屏蔽敏感闸极氧化层,使其免受存在于sic中的高电场的影响,尤其是在高汲极偏压或阻断模式操作期间。

265、一个实施例涉及使用p+插塞通过n+源极接触点将p井区接地。

266、一个实施例涉及使p井区之间的横向间隔足够窄以抑制闸极氧化层中的电场,同时确保导通电阻不高。

267、一个实施例涉及用深p型下沉#1区替换dmosfet的p+插塞区。

268、实施例涉及在mosfet器件结构内的特定位置形成一个或多个深注入下沉区,诸如位于mosfet单位单元的中心处的第一p型下沉区,其深度可等于或大于p井区的深度。

269、实施例涉及在n+源极区下形成第二p型下沉区,其深度可等于或大于p井区,但小于或等于第一p型下沉区的深度。

270、实施例涉及硼注入,可有利地将硼注入用于形成深下沉区,因为硼具有比铝更大的注入范围,可产生更深的注入轮廓

271、实施例涉及形成具有所需形状的第一沟槽,可在形成第一p型下沉区之前,在n+源极区中蚀刻该沟槽,其可用于增加第一p型下沉区的深度。第一沟槽的深度可在0.01μm至2μm的范围内。所得的第一下沉区的深度可能比p井区的深度大0%到100%。第一p型下沉区的深度可以与整个外延层一样大。

272、涉及在n+源极区中形成第一沟槽的实施例可降低或消除用于形成第一p型下沉区的昂贵的超高能注入步骤的需求。

273、涉及第一沟槽的实施例可有利地用于从第一p型下沉区去除n+源极注入,这对于防止通过n+源极注入对第一p型下沉区进行补偿可能是合乎需要的。如果n+源极区与p井区自对准,则这尤其有用。

274、实施例涉及逐渐降低的注入浓度,其可用于形成第一p型下沉区和第二p型下沉区以代替盒形注入轮廓,因为这有利于在高汲极偏压下适当地形成电场。p型下沉区中的掺杂可从接近sic表面的最大值线性变化到等于或略高于p型下沉区的另一端处的漂移层掺杂浓度的值。

275、第一下沉区和第二下沉区的设计的实施例可简化p井区的设计,p井区可设计为支持金属氧化物半导体(mos)通道的形成,并且可有利地设计为实现低导通电阻,而不会影响其他性能指标,诸如反向漏电流和闸极氧化层中的电场。

276、功率电子器件中的sic器件的特点是具有快速开关时间、高阻断电压能力以及在高温下工作的能力。这些特性以及制程的最新进展表明,作为传统硅基(si)器件的接替者,sic有可能彻底改变功率电子器件。与si(si带隙为1.1ev,si的击穿电场为0.3×106v/cm)相比,sic是一种宽带隙材料(3.3ev)并且它的击穿电场(3×106v/cm至5×106v/cm)更高。sic是一种更好的热导体(sic为3.7(w/cm-k)而si为1.6(w/cm-k)),这使得sic器件能够在极高的功率水平下工作,并且仍能耗散所产生的大量多余热量。sic的这些材料特性为在功率器件上使用sic而不是si提供了多种优势。对具有相同结构和尺寸的sic半导体晶粒和si半导体晶粒进行对比时,sic晶粒呈现比si晶粒更低的特定导通电阻和更高的击穿电压。

277、本文公开的实施例提供了针对sic dmosfet设计和制造的新型技术,用于在器件结构上形成电场并降低奇点处的电场集中。本文中的实施例将闸极氧化层区中的电场降低至小于3.5mv/cm并提高器件可靠性。

278、si的制程使用掺杂剂扩散等技术,但这些常规制程无法用于制造sic器件,因为sic的扩散系数在1800℃以下的温度下可忽略不计。sic器件是通过源极区和p井区的离子注入来制造的,但是在sic中进行离子注入,特别是深离子注入是一个难点。在本文实施例中,采用新技术实现了源极区和p井区的深离子注入。

279、与硅器件相比,本文实施例的sic器件的可靠性更高、工作温度更高、效率更高且电压能力更高,这使得它们非常适合电动载具和可再生能源行业。电动载具中的牵引逆变器承受高热(>150℃),负载循环和可再生能源转换器承受极端环境条件。例如,本文中描述的针对sic器件的实施例将功率转换效率最大化至>98%,同时提供高可靠性,从而使其成为电动载具的理想候选,以最小化对电动载具的操作员而言是昂贵的维护时间和停机时间。

280、所公开的实施例改变了sic功率dmosfet器件能够有效屏蔽敏感闸极氧化层以使其免受存在于4h sic中的高电场的影响的方式,特别是在高汲极偏压(阻断模式操作)期间。

281、在本文实施例中,sic功率dmosfet器件克服了实现低导通电阻以及实现稳健阻断性能之间的权衡,这意味着在靠近闸极氧化层的结构中具有低电场。

282、本文实施例包括包含垂直mosfet的sic功率dmosfet的单位单元。sic功率dmosfet器件的特定区域是由注入、n+源极区、n-漂移层和n+基板形成的p井区。在本文实施例中,在导通状态期间,当闸极电压被施加到该器件(通过n+源极区流入并通过源极金属化层流出)时,电流从汲极垂直流过形成在p井层的顶部处的反型层。在关断状态或阻断状态下,在本文实施例中,在p井和n漂移层接面之间支持电压。在p井和n漂移层之间形成pn接面。在反向偏压中通过该pn接面支撑施加在结构上的电压。

283、在本文实施例中,功率mosfet具有多个物理尺寸,包括:单位单元的节距,其是mosfet的重复单元;通道长度,即形成反型通道的p井部分;两个连续p井之间的距离,称为接面闸场效应晶体管(jfet)区域或jfet间隙;闸极氧化层的厚度;以及层间电介质(ild)层,用于将源极互连金属化层与多晶硅闸极隔离。

284、在本文实施例中,使用sic优于si的优点是,对于类似的芯片尺寸,sic可支持更高的功率密度。sic可支持的电压量可以是si的10倍,sic芯片通过mosfet可承载的电流可以是si的10倍到50倍。sic mosfet形成一种方便的开关,因为可以实现更高的功率密度。性能优势与电压和电流之间的权衡有关。相比之下,sic的电压阻断和电流传导能力大约是si的200倍。

285、在本文实施例中,在sic dmosfet单位单元的中心处的p+插塞被替换为ps#1区。在本实施例中,ps#1区延伸至p井区下方。在阻断条件下,电场或击穿可能发生的主要区域位于sic dmosfet的单位单元的中心处,基本上在ps#1区和n漂移层之间。sic结构倾向于在p井和n漂移层之间击穿,特别是在p井区的弯曲处。在本文实施例中,结构将在ps#1区和n漂移层之间击穿。此处,击穿的位置已经移动朝向单位单元的中心,这导致更靠近闸极氧化区的电场较低。在本实施例中,由于ps#1区,靠近闸极氧化层区的电场降低,这应该使器件更加稳健。

286、本文实施例与现有技术的sic器件在结构上存在差异、制造方法上存在差异、器件功能上存在差异以及器件产生的结果上存在差异。本文实施例的模拟数据显示了结构的性能和结果的差异。除了ps#1区之外,本文实施例的器件还具有位于n+源极区的下方的ps#2区域。这以如下方式改进了实施例中的电场分布:在阻断操作模式期间,在单位单元的更大区域上切断电压,这实现甚至更稳健的操作。在本文实施例中,ps#2区可以比p井区更深并且可以比ps#1区更浅。在本文实施例中,sic dmosfet结构中的所有p型区中,其中最深的是ps#1区,中间的是ps#2区,较浅的是p井区。本文实施例展示了更合适的这些ps#1结构和ps#2结构中的电场形成方式。

287、在本文实施例中,包括ps#2区的另一优势是ps#2用作次级p井区。p井区的设计需要满足多个不同的约束条件。p井区中的电剂量可以足够大,从而实现所需的击穿电压,同时,在形成mos通道的闸极氧化层区附近的p井区的掺杂可以足够低,从而实现合理的低阈值电压。

288、在本实施例中,p井区现在可以满足相互矛盾的要求。通过将ps#2置于n+源极区的下方,放宽了p-井区的设计,p-井区目前仅用于通道限定和通道形成。在本文实施例中,不必将p井设计为用于支持击穿电压。本文实施例为设计者提供了更大的灵活性,以设计仅适合于mos通道形成的p井区。

289、在本文实施例中,在将沟槽蚀刻到位于sic dmosfet的单位单元中间的n+源极区之后,形成ps#1。这种沟槽的优势是,它使电场位置进一步远离闸极氧化层界面,到达sicdmosfet的单位单元中间。在本实施例中,将凹沟槽蚀刻到n+源极区中有效地创建了更深的ps#1区。电场进一步远离闸极氧化层区,这将有助于实现更强大的阻断能力。在本文实施例中,做沟槽的原因之一是因为难以在sic中进行离子注入,尤其是深离子注入。由于存在源极沟槽,因此可以形成深ps#1下沉区。在本文实施例中,蚀刻沟槽然后进行离子注入,允许形成更深的ps#1区,这是有效的并实现了功能性。

290、在本文实施例中,由于沟槽有助于形成更深的ps#1,因此允许通过减少氧化物来形成更薄的氧化层区。sic dmosfet需要更厚的氧化层,以防止它们在电介质场中击穿。在本文实施例中,通过引入p型下沉区,可以使用较薄的氧化层。

291、在本文实施例中,使用一系列屏蔽步骤,然后进行离子注入或蚀刻以及沉积步骤来制造sic dmosfet器件。在本文实施例中,使用用于屏蔽晶圆的特定部分或器件的特定部分的光刻技术,并执行特定步骤,然后移除该屏蔽,并执行其他步骤来制作一系列结构的情况下生产单位单元。最小化步骤的数量对于实现成本效益非常重要。也就是说,如果能够以某种方式减少步骤的数量,结构成本就会更低。此外,制造sic的特定步骤是昂贵的,而本文实施例使这些昂贵的步骤的数量最小化。例如,在sic中,离子注入是相对昂贵的步骤。使用离子注入制成p井、p插塞和n+源极区。离子注入是昂贵的步骤,尤其是更深度的离子注入更为昂贵。因此,尽量减少深离子注入具有重要意义。此外,p型注入的成本是n型注入的5倍到10倍,因为p型注入需要在更高的温度(400-1000℃)下进行,而相比之下,n型注入可以在室温下进行。因此,减少p型注入也至关重要。

292、在实施例中,本文中晶圆首先经历一系列离子注入步骤,通常称为制程的前端,然后进行高温退火,用于退火去除注入损伤并电激活注入。该制程的后端通常包括形成闸极氧化层、ild和其他金属化步骤。

293、在本文实施例中,为了制造sic dmosfet结构,将使用光刻技术来屏蔽晶圆的特定部分以创建p井区,随后,可使用下一屏蔽步骤来实现n+源极区,随后将使用另一屏蔽步骤来实现p+插塞区。需要对晶圆进行退火以激活注入区。在此之后,可以通过热氧化物或使用沉积的氧化物来生长闸极氧化层或闸极电介质。可使用多晶硅或其他难熔金属形成闸极金属化层。然后选择性地对闸极金属化层进行图案化和蚀刻以进入n+源极区,随后沉积ild,然后对其进行图案化以实现用于为n+源极区创建这些欧姆接触的窗口。对于汲极区域,可以在晶圆的背面(即汲极)上实现欧姆接触。在制程结束时,使用源极互连金属化层来连接各种单位单元。

294、通常在几个屏蔽步骤中产生sic mosfet。这些屏蔽步骤中的一些屏蔽步骤可用于形成注入区,而其他屏蔽步骤用于形成诸如闸极氧化层、ild等结构。本文实施例均在11个屏蔽步骤中完成,而不增加用于任何附加特征(如实施例中的ps#1、ps#2、源极沟槽形成或其他结构)的屏蔽步骤。

295、在sic中,离子注入是一种引入掺杂剂的方法,因为扩散效果不佳。因此,要实现使ps#1区比p井区更深,需要更高的注入能量。在本文实施例中,通常使用铝或硼来实现sic中的p型区。因此,为了实现ps#1区和深ps#1区,在本文实施例中,使用硼注入来替代铝注入,因为对于给定能量,硼注入可产生比铝注入更深的区域。实现深ps#1区的另一种方式是使用更高的能量,并且仍然使用铝作为p型掺杂。

296、在本文实施例中,形成p井区,随后形成n+源极区。在形成n+源极区的同时,执行离子注入以实现ps#2区。相同的屏蔽步骤用于形成n+源极区和ps#2区。在本文实施例中,这使得能够在n+源极区的正下方实现ps#2区。

297、在本文实施例中,使n+源极注入与p井注入自对准,以减少或甚至消除如果在不同屏蔽步骤中实现两个区域可能发生的未对准。

298、在本文实施例中,为了实现亚0.5微米通道长度或亚1微米通道长度,使用传统注入屏蔽步骤形成第一p井区。沉积足够厚度的电介质层,然后使用光刻技术可以有选择地对该层进行图案化,然后进行离子注入,从而实现p井区。一旦完成此步骤,第二电介质层沉积在该图案化的第一电介质层的顶部,然后进行无图案蚀刻。这产生了电介质间隔区域,该区域随后限定了经受n+源极注入的区域。因此,通过选择适当的第二电介质层的厚度,可以限定mos通道长度。

299、在这里的实施例中,为了实现0.5微米宽的通道,首先使用传统的光刻技术创建一个p井区,例如可以沉积和图案化二氧化硅层,然后可以沉积第二个厚度等于0.5微米的二氧化硅层。把这层蚀刻下来时,就会发现有一个间隔物,也是0.5微米。当人们进行n+源极植入时,实际上会有一个0.5微米的mos通道长度。

300、在实施例中,通道的长度不是由光刻技术的限制形成的,而是由沉积电介质层的能力形成的,例如二氧化硅可以更好地控制。人们可以以比光刻技术更高的分辨率来沉积电介质或二氧化硅层。

301、在一种称为减法的方法中,该制程首先制造一个n+源极,然后沉积一个电介质层,再通过多晶硅的变化形成p+层。这里的实施例采用加法,第一个做p井区,然后沉积有一定厚度的电介质,这将确定通道长度,然后放入n+源极。因此,与现有技术的sic dmosfet的形成方式相比,本实施例中的n+和p井区的顺序是相反的。

302、这里的实施例避免了在闸极区植入n+源极区。在sic mosfet结构中,存在一个寄生的npn晶体管,它不是在正常工作期间被触发,而是在你以极高的速度将该器件从关到开或从开到关时被触发。

303、在这里的实施例中,进入n+源极区的沟槽是在植入ps#1区之前形成的,导致ps#1区更深。但这样做的另一个好处是,可以从不希望植入n+源极区的部分移除n+源极区。因此,这就是在n+源极区蚀刻沟槽的次要好处。同样的遮蔽步骤用于进行sic干蚀,然后植入ps#1区域。这只需通过一个遮蔽步骤即可实现。在一个实施例中,ps#2区域与n+源极区域一起以相同的遮蔽步骤形成。sic沟槽和ps#1区域再次使用相同的遮蔽步骤形成。在这个实施例中,使用两个遮蔽步骤制作四个特征。

304、在这里的实施例中,ps#1下沉区的成本降低了,因为不必采用深层离子植入法。深度离子植入,属高剂量,价格昂贵。而在外围,有一个深的p+也是有益的,以防止可能形成的击穿区。在这里的实施例中,避免了外围的击穿区,因为使用单一的步骤来创建ps#1和沟槽。当以自对准的方式形成mos通道时,在有p井区域的地方都会形成n+源极区,甚至延伸到器件的外围。在这里的实施例中,避免了由于沟槽和ps#1的形成而在外围的击穿。

305、图2a所示的一个实施例是一个sic dmosfet的横截面结构的单元格。该器件的关键区域是p井区203,是通过离子植入或p型种(如铝或硼)的外延再生长形成。有一个n+源极区204,n-漂移层202,和一个n+基板201。在导通状态下,当闸极电压被施加到多晶硅闸极206上时,电流从汲极201垂直流过在p井层203顶部形成的反转层,通过n+源极区204,并通过源极金属化层208流出。在关断状态或阻断状态下,一个电压被支持在p井区203、n-漂移层202接面上,并且在p井区和n-漂移层之间形成一个pn接面。施加到结构上的电压在反向偏压下被支持在这个pn接面上。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井区中形成反转通道的部分,两个连续的p井区之间的距离,称为jfet区域或jfet间隙,以及闸极氧化物205的厚度。另一个特征是ild层207,用于将源极互连金属化层208与多晶硅闸极206绝缘。在单元格的最中心,有一个p+插塞209,它与n+源极金属化层接地。sic dmosfet中p+插塞的目的是通过n+源极接触点将p井区接地。通常情况下,如图2a所示,p+插塞的植入深度要比p井区域浅一些。dmosfet器件结构可导致p井区203的角部出现高电场集中,从而导致闸极氧化层205中出现高电场,特别是在高汲极偏压(阻断模式)操作期间。4h-sic中击穿的高临界电场(≈3mv/cm)导致闸极氧化物中出现非常高的(>5mv/cm)电场。在闸极氧化物中如此高的电场下,可以观察到fowler-nordheim隧道电流,这可能会导致闸极氧化物中出现被困电荷,从而导致器件可靠性差。在这里的实施例中,p井区(jfet区域)之间的横向间距被做得足够窄,以抑制闸极氧化物中的电场,同时确保mosfet的导通电阻足够低。

306、图2b是图2a中所示的sic mosfet的击穿模拟。模拟结果显示,电场峰值位于p井区的角落,这导致闸极氧化层中存在一定的高电场。电场强烈地集中在p井区的角落,因为那是最大曲率的区域。(本实施例有局限性)

307、图3所示的一个实施例是一个sic dmosfet的横截面单元格。该器件的关键区域是p井区303,是通过离子植入或p型种(如铝或硼)的外延再生长形成。有一个n+源极区304,n-漂移层302,和一个n+基板301。在导通状态下,当闸极电压被施加到多晶硅闸极306上时,电流从汲极301垂直流过在p井层303顶部形成的反转层,通过n+源极区304,并通过源极金属化层308流出。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井区中形成反转通道的部分,两个连续的p井区之间的距离,称为jfet区域或jfet间隙,以及闸极氧化物305的厚度。另一个特征是ild层307,用于将源极互连金属化层308与多晶硅闸极306绝缘。这里,图2a的sic dmosfet的p+插塞区域209被一个深p型下沉#1(p-type sinker#1,ps#1)区域309取代。ps#1区域的深度大于p井区的深度。在关断状态或阻断状态下,图2a所示的结构将在p井区203和n-漂移层202之间击穿,特别是在p井区的曲率处。但是随着图3中ps#1区域309的引入,电场或将发生击穿的主要区域,现在是在图的最中心,基本上是在ps#1区域309和n-漂移层302之间。更深的ps#1区域的存在导致电场峰值位置从p井区303的角落移动到ps#1区域309。在高汲极偏压操作期间,4h-sic的电场峰值位置已经远离了闸极氧化物305。现在闸极氧化物305中的电场比图2a器件的电场要低。

308、图4a至图4r描述了图3所示结构的制造过程。sic dmosfet的制造过程是在sic基板401上,首先使用4h-sic si-面磊晶圆,其掺杂度(1014-1018cm-3)和厚度(1μm至300μm)适合图4a所示的外延层402。在图4b中沉积了一个空白的硬屏蔽403(包括cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层,如镍,厚度从50nm到5μm不等),然后使用光刻技术进行图案化,然后进行干蚀刻(例如使用反应性离子蚀刻),如图4c所示。在图4d中进行p型植入404(由硼或铝组成,能量范围为10kev至800kev,植入剂量范围为1012cm-2至1015cm-2),以创建图4e中的p井区405。移除屏蔽403,并沉积另一个硬屏蔽层406(包括cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层,如镍,厚度从50nm到5μm不等),并在图4f中图案化,以定义n+源极区。请注意,单元格的中心被掩盖了,用于源极(src)的植入。如图4g所示,src(n+源极区)407是通过植入n型(n+)杂质408(包括氮或磷,能量范围从10kev到500kev,植入剂量范围从1013cm-2到1016cm-2)形成的。去除硬屏蔽406后,另一个硬屏蔽层409被沉积并在图4h中图案化。图4h中的ps#1区411是通过植入p型杂质410形成的。深层ps#1区域可以使用铝或硼的离子植入法形成,这些是4h-sic中常用的p型掺杂物。硼可以有利地用于形成这种深p型下沉区,因为与铝相比,它的植入范围明显更高,而且使用硼的深植入可以用较低的离子植入能量形成。在一个例子中,与p井区相比,ps#1区域可以用硼植入法形成,深度高出20-50%。硼植入物可包括能量范围从10kev到800kev,植入剂量范围从1012cm-2至1015cm-2。在本发明的一个相关实施例中,ps#1区域的掺杂曲线可以通过逐渐降低的掺杂浓度形成,在sic表面有一个高峰值。ps#1区域的这种梯度掺杂曲线可以防止在三维景观中形成尖角,并有利于在高汲极偏压操作期间将峰值电场扩散到更大的区域,从而导致更高的击穿电压。在一个例子中,ps#1区域可以在靠近sic表面,通过在1019cm-3至1020cm-3范围内的峰值掺杂形成,该掺杂随着进入碳化硅的深度而线性减少,达到背景n漂移层掺杂(在1014-1016cm-3范围内)。ps#1区的线性梯度掺杂曲线导致足够部分的汲极电势被支持在ps#1区,而不仅仅是在n-漂移区。这导致了一个伪电荷平衡的结构,促进了更大的sic区域的击穿,导致了击穿时的临界电场较低,从而使闸极绝缘体中的电场较低。随后是图4i中硬屏蔽409的去除(使用本领域人士通常采用的干法或湿法蚀刻技术)。然后,在图4j中,作为闸极氧化物的氧化层412被热生长或使用化学气相沉积(cvd)沉积。闸极氧化物的厚度可以从10纳米到100纳米。干式或湿式热氧化都可用于使氧化物增加。电浆增强cvd(pecvd)或低压cvd(lpcvd)可用于闸极氧化物沉积。然后在图4k的顶部413上沉积多晶硅闸极层。多晶硅层可以使用pecvd或lpcvd进行沉积。多晶硅层可以使用硼或磷进行简并掺杂,可以在原位或在随后的步骤中进行。原位掺杂可以通过在多晶硅沉积化学过程中加入ph3前体来进行。多晶硅的沉积后掺杂可以通过沉积一层pocl3,然后在700-900℃的温度下进行驱动步骤。如图4l所示,在上面沉积一个硬屏蔽414,并进行图案化。多晶硅闸极层413是通过使用图4m中的图案化屏蔽层414进行蚀刻。然后从图4n中的顶部移除屏蔽层414。在晶圆上沉积层间电介质(ild)层415(包括50纳米到-1000纳米厚的二氧化硅、氮化硅、氧氮化硅层或其叠加组合);在上面沉积和图案化硬屏蔽416,以定义ild开口;如图4o所示,使用硬屏蔽416对ild层进行图案化。此外,使用图4p中相同的屏蔽416对闸极氧化物进行蚀刻。然后去除屏蔽416,在图4q中暴露的sic表面上形成一个硅化镍区域417。互连金属层418(al或ag或au)在图4r中的芯片顶部和底部被沉积和图案化。

309、本发明的作者认识到,图1a中的现有技术装置的主要问题是,p井区不能有效地屏蔽敏感的闸极氧化物,不受在4h-sic中存在的高电场的影响,特别是在高汲极偏压(阻断模式操作)时。更深的ps#1区域的存在导致电场峰值位置从p井区的角落移动到ps#1区域。在高汲极偏压操作期间,4h-sic的电场峰值位置已经远离了闸极氧化物。

310、这个实施例的优点是,击穿位置从p井区域的角落移到了新形成的ps#1区域的底部,既远离了闸极氧化界面,又深入了半导体。现在,包含ps#1区域的器件结构的闸极氧化物中的电场明显低于现有技术的器件,这可见于图5b中使用silvacoatlas的器件模拟。

311、图5a所示的一个实施例是一个纵向功率dmosfet的横截面单元格。该器件的关键区域是p井区503,是通过离子植入或p型种如铝或硼的外延再生长形成。有一个n+源极区504,n-漂移层502,和一个n+基板501。在导通状态下,当闸极电压被施加到多晶硅闸极506上时,电流从汲极501垂直流过在p井层503顶部形成的反转层,通过n+源极区504,并通过源极金属化层508流出。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井区中形成反转通道的部分,两个连续的p井区之间的距离,称为jfet区域或jfet间隙,以及闸极氧化物505的厚度。另一个特征是ild层507,用于将源极互连金属化层508与多晶硅闸极506绝缘。在这里,除了在图3所示的一个实施例中已经描述过的ps#1区域509之外,还在n+源极区域504下形成了第二个p型下沉#2(ps#2)区域510。ps#2区域的形成比p井区503更深,但比ps#1区域509更浅。例如,ps#2区域510可以比p井区域503深20%,而ps#1区域509可以比ps#2区域510深20%。

312、ps#2区域的存在导致ps#1和ps#2区域在高汲极偏压操作下共享峰值电场。ps#2区域的存在缓解了高汲极偏压条件下器件结构中电场峰值的局部最大值。在图1a所示的现有技术sic mosfet中,p井区的设计需要满足相互冲突的要求。在n+源极区下的p井区的电剂量必须足够高,以防止在非状态(高汲极偏压)操作下的触穿击穿。但是,与此同时,p井区的表面掺杂必须足够低,以保持合理的较低的闸极阈值电压和器件导通电阻。在这种情况下,本实施例中引入的ps#2区域可以被认为是一个二级p井区域,其设计的主要目的是防止触穿击穿,并在高汲极偏压操作下适当地塑造电场曲线。ps#2区域的存在释放了主要p井区设计中的约束,可用于与导通状态相关的器件指标,如闸极阈值电压和导通电阻。由于引入了ps#2区域,p井区的设计不必以支持击穿电压为目标,这给设计者提供了更大的灵活性,能够适当地设计p井区以单单形成mos通道。

313、根据图3和图5a中描述的两个实施例设计的sic dmosfet的击穿模拟图5b显示,电场峰值位置已经从p井区域的角落移到了单元格的中心,导致闸极氧化层的电场更低。

314、图6a至图6j描述了图5a所示结构的制造过程。sic dmosfet的制造过程是在sic基板601上,首先使用4h-sic si-面磊晶圆,其具有适合图6a所示的外延层602的掺杂度(1014-1018cm-3)和厚度(1μm至300μm)。在图6b中沉积了一个空白的硬屏蔽603(包括cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层,如镍,厚度从50nm到5μm不等),然后使用光刻技术进行图案化,然后进行干蚀刻(例如使用反应性离子蚀刻),如图6c所示。在图6d中进行p型植入604(由硼或铝组成,能量范围为10kev至800kev,植入剂量范围为1012cm-2至1015cm-2),以创建图6e中的p井区605。移除屏蔽603,并沉积另一个硬屏蔽层606(包括cvd沉积的二气化硅、氮化硅、氧氮化硅或金属层,如镍,厚度从50nm到5μm不等),并在图6f中图案化,以定义n+源极区。请注意,单元格的中心被掩盖了,用于源极(src)的植入。如图6g所示,src(n+源极区)607是通过植入n型(n+)杂质608(包括氮或磷,能量范围从10kev到500kev,植入剂量范围从1013cm-2到1016cm-2)形成的。图6h中的ps#2区609是通过植入p型杂质610形成的。深层ps#2区域可以使用铝或硼的离子植入法形成,这些是4h-sic中常用的p型掺杂物。硼可以有利地用于形成这种深p型下沉区,因为与铝相比,它的植入范围明显更高,而且使用硼的深植入可以用较低的离子植入能量形成。若使用铝,ps#2区域可包括能量范围从100kev到1mev,植入剂量范围从1013cm-2至1016cm-2。若使用硼,ps#2区域可包括能量范围从50kev到800kev,植入剂量范围从1013cm-2至1016cm-2。用于形成n+源极区的硬屏蔽606也用于定义离子植入的ps#2区。在这种情况下,ps#2区域是在n+源极区域下自我对齐的。去除硬屏蔽606后,另一个硬屏蔽层612被沉积并在图6i中图案化。ps#1区611是通过植入p型杂质613形成的,该杂质可包括铝或硼。硼可以有利地用于形成ps#1区域,因为与铝相比,它的植入范围明显更高,而且使用硼的深植入可以用较低的离子植入能量形成。若使用铝,ps#1区域可包括能量范围从100kev到1mev,植入剂量范围从1013cm-2至1016cm-2。若使用硼,ps#1区域可包括能量范围从50kev到800kev,植入剂量范围从1013cm-2至1016cm-2。ps#2区域可以高于p井区的深度,但低于ps#1区域的深度形成。作为该实施例的第二个例子,ps#2区域可以比p井区深20%,而ps#1区域可以比ps#2区域深20%。在本发明的一个相关实施例中,ps#1区域和ps#2区域的掺杂曲线可以通过逐渐降低的掺杂浓度形成,在sic表面有一个高峰值。ps#1区域和ps#2区域的这种梯度掺杂曲线可以防止在三维景观中形成尖角,并有利于在高汲极偏压操作期间将峰值电场扩散到更大的区域,从而导致更高的击穿电压。作为例子,ps#1和ps#2区域可以分别借在靠近sic表面和靠近n+源极区,且范围在在1019cm-3至1020cm-3的峰值掺杂形成。在ps#1和ps#2区域的掺杂浓度可能会随着进入碳化硅的深度而线性下降到背景n-漂移层的掺杂(在1014-1016cm-3范围内)。ps#1/ps#2区的线性梯度掺杂曲线导致有足够部分的汲极电势被支持在ps#1/ps#2区,而不仅仅是在n-漂移区。这导致了一个伪电荷平衡的结构,促进了更大的sic区域的击穿,导致了击穿时的临界电场较低,从而使闸极绝缘体中的电场较低。在图6j中,去除硬屏蔽612(干法或湿法蚀刻)是在ps#1区域的形成之后进行的。建立图5a所示结构的过程中的其余步骤完全遵循图4j至图4r所示的相同步骤。

315、这种具有一定深度的ps#1和ps#2区域的"阶梯式"排列,在高汲极偏压操作下,可以使闸极氧化物中的电场更低。然而,ps#2区域的另一个好处是p井区可以做得更浅,植入剂量更低,这可以降低器件的导通电阻,同时提高闸极阈值电压,从应用角度看,这两点都是可取的。因此,通过本发明的教导,可以更好地权衡关闭状态和开启状态的性能。

316、图7a所示的一个实施例是一个sic dmosfet的横截面单元格。该器件的关键区域是p井区703,是通过离子植入或p型种如铝或硼的外延再生长形成。有一个n+源极区704,n-漂移层702,和一个n+基板701。在导通状态下,当闸极电压被施加到多晶硅闸极706上时,电流从汲极701垂直流过在p井层703顶部形成的反转层,通过n+源极区704,并通过源极金属化层708流出。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井区中形成反转通道的部分,两个连续的p井区之间的距离,称为jfet区域或jfet间隙,以及闸极氧化物705的厚度。另一个特征是ild层707,用于将源极互连金属化层708与多晶硅闸极706绝缘。在这里,在植入ps#1区709之前,在n+源极区704中蚀刻了一个沟槽711。这里在n+源极区域704下的ps#2区域710是在ps#1区域709之外形成的。ps#2区域的形成比p井区703更深,但比ps#1区域709更浅。最好是将电场位置尽量远离闸极氧化界面,以获得器件运行的强大阻断能力,从而提高器件的可靠性。将击穿位置移到离闸极氧化层705最远的单元格中间是一个实施例,通过在n+源极区704中蚀刻凹槽711,已经有效地创造了一个比图3和图5a中更深的ps#1区域,并将电场移到离闸极氧化区域更远的地方。

317、在p型下沉区域中,ps#1区域的设计深度最大。虽然硼植入是在sic技术中创造这种深p型区域的一种技术,但当你考虑到现有的商用离子植入器的最大范围时,就会发现sic中的离子植入不是一个简单的过程,深层离子植入尤其困难。n+源极区也被称为源极沟(source trench),它的作用是可以用较低的离子植入能量实现ps#1区,从而降低这一植入步骤的成本和时间,而不会影响植入深度。在这里的实施例中,在植入n+源极区之后,但在植入ps#1区之前,可以在sic上干法蚀刻沟槽。用于ps#1植入的同一硬屏蔽层可用于蚀刻sic中的源极沟。在这个实施例中,首先对硬屏蔽层进行图案化,然后将沟槽干蚀刻在sic中,紧接着对ps#1区域进行离子植入。源极沟的形成自然地延长了ps#1区域的深度。因此,ps#1区域可以用较低的离子植入能量来实现,这就降低了这一植入步骤的成本/时间,而不会影响到植入深度。源极沟的形成也消除了n+源极区,使p井区与n+源极欧姆接触直接连接,从而使p井接地,p井区与n+源极区短路。

318、根据图7a中描述的实施例设计的sic dmosfet的击穿模拟,即图7b,显示电场峰值位置已经从p井区域的角落移到了单元格的中心,导致闸极氧化层的电场更低。

319、图8a至图8bb描述了图7a所示sic dmosfet结构的制造过程。sic dmosfet的制造过程是在sic基板801上,首先使用4h-sic si-面磊晶圆,其适合的掺杂度(1014-1018cm-3)和厚度(1μm至300μm),供图8a所示的外延层802。在图8b中沉积了一个空白的硬屏蔽803(包括cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层,如镍,厚度从50nm到5μm不等),然后使用光刻技术进行图案化,然后进行干蚀刻(例如使用反应性离子蚀刻),如图8c所示。在图8d中进行p型植入804(由硼或铝组成,能量范围为10kev至800kev,植入剂量范围为1012cm-2至1015cm-2),以创建图8e中的p井区805。移除屏蔽803,并沉积另一个硬屏蔽层806(包括cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层,如镍,厚度从50nm到5μm不等),并在图8f中图案化,以定义n+源极区。如图8g所示,n+源极区807是通过植入n型(n+)杂质808(包括氮或磷,能量范围从10kev到500kev,植入剂量范围从1013cm-2到1016cm-2)形成的。图8h中的ps#2区809是通过植入p型杂质810形成的。深层ps#2区域可以使用铝或硼的离子植入法形成,这些是4h-sic中常用的p型掺杂物。硼可以有利地用于形成这种深p型下沉区,因为与铝相比,它的植入范围明显更高,而且使用硼的深植入可以用较低的离子植入能量形成。从图8i的顶部移除图案化硬屏蔽806。另一个硬屏蔽层811在图8j中的顶部形成,并在图8k中图案化。图8l中,图案化的屏蔽811被用来在基板上蚀刻812,以创造一个凹陷区域。作为凹陷区域813的源极沟是通过穿透图8m中的源极区在基板中形成的。图8n中的p型植入814是为了创建ps#1区域而进行的。若使用铝,ps#1区域可包括能量范围从100kev到1mev,植入剂量范围从1013cm-2至1016cm-2。若使用硼,ps#1区域可包括能量范围从50kev到800kev,植入剂量范围从1013cm-2至1016cm-2。图8o中的ps#1区815是通过自动对位植入p型杂质形成的。正如在上述实施例中更完整地描述的那样,ps#1/ps#2区域的线性梯度掺杂曲线可能更适合用来代替均匀(突然)的掺杂曲线,这导致有足够部分的汲极电势被支持在ps#1/ps#2区域,而不仅仅在n-漂移区域。这导致了一个伪电荷平衡的结构,促进了更大的sic区域的击穿,导致了击穿时的临界电场较低,从而使闸极绝缘体中的电场较低。

320、在p型下沉区域中,ps#1区域通过使用硼植入技术被设计成具有最大的深度,沟槽的形成自然地延长了ps#1区域的深度。用于蚀刻源极沟槽811的相同硬屏蔽被用来定义ps#1区域。对于本发明领域的人来说,sic沟槽可以用干式蚀刻技术形成,包括反应性离子蚀刻、电感耦合电浆(icp)-rie等。虽然图7a中显示该沟槽区域的侧壁坡度为90°,但形成侧壁角度较小(60-90°)的沟槽区域是有利的,因为这将减少ps#1区域的曲率,从而提高器件的阻断性能。

321、从图8p的顶部移除图案化硬屏蔽811。在图8q中,形成了一个用于闸极氧化的氧化层816。在图8r的顶部817上沉积多晶硅闸极层。多晶硅层可以使用pecvd或lpcvd进行沉积。多晶硅层可以使用硼或磷进行简并掺杂,可以在原位或在随后的步骤中进行。原位掺杂可以通过在多晶硅沉积化学过程中加入ph3前体来进行。多晶硅的沉积后掺杂可以通过沉积一层pocl3,然后在700-900℃的温度下进行驱动步骤。如图8s所示,在上面沉积一个硬屏蔽818,并进行图案化。多晶硅闸极层817是通过使用图8t中的图案化屏蔽层818进行蚀刻。然后从图8u中的顶部移除屏蔽层818。在图8v的晶圆上沉积了一层间介电层(ild)819(包括50nm-1000nm厚的二氧化硅、氮化硅、氧氮化硅层或其叠加组合)。在图8w中,沉积一个硬屏蔽820并进行图案化,以确定ild的开口。如图8x所示,ild层使用硬屏蔽820进行图案化。此外,使用图8y中相同的屏蔽820对闸极氧化物816进行蚀刻。然后在图8z中移除屏蔽820。在图8aa中,暴露的sic表面上形成了一个硅化镍区域821。互连金属层822(铝(al)或银(ag)或金(au))在图8bb中的芯片顶部和底部被沉积和图案化。

322、此处实施例的优点是,通过蚀刻源极沟区,在植入ps#1区之前,击穿位置已被进一步移入半导体,并远离闸极氧化层。由于碳化硅的固有硬度,离子植入掺杂物的观察范围(深度)明显低于在硅内的时候。例如,在碳化硅中形成深层(>0.3μm)的离子植入层需要极高的植入能量(>300kev),这需要双重或三重电离的植入种类,这大大降低了这些离子植入步骤的通量并增加了成本。如本实施例所述形成源极沟,就不需要双重/三重电离植入步骤,可以利用低成本、高通量的单电离植入来实现ps#1区域。

323、本实施例涉及sic dmosfet功率器件,可用于制造自对准功率mosfet。

324、一个实施例涉及到提高mos通道密度。

325、一个实施例涉及到提高有效场效应迁移率。

326、一个实施例涉及到改进设备的可靠性。

327、一个实施例涉及到在给定的芯片尺寸下降低导通电阻。

328、一个实施例涉及到自对准功率器件的设计和制造。

329、一个实施例涉及到设计和制造具有亚微米通道长度的mos通道。

330、一个实施例涉及到去除无意中在器件外围形成的寄生n+源极区。

331、一个实施例涉及到器件主动区中的p井区与源欧姆接触的适当接地。

332、一个实施例涉及到去除形成在自对准功率器件的主动区和外围区的寄生npn晶体管。

333、一个实施例涉及到适当位置的源极沟与离子植入的p+插塞区域的组合,以使主主动mosfet区中的p井区适当接地,并去除形成在mosfet外围的寄生n+源极区域。

334、一个实施例涉及到在mosfet外围形成高掺杂的p+插塞区域,特别是在闸极垫(gate pad)和闸极总线(gate bus)区域下。

335、一个实施例涉及到在快速开关转换期间,由于基极偏压效应导致阈值电压降低,在脆弱的位置抑制mosfet的假导通。

336、一个实施例涉及改进mosfet的最大额定dv/dt。

337、一个实施例涉及改进mosfet的最大崩溃式能量等级。

338、一个实施例涉及到利用一个专门的制程步骤来掩盖器件外围的n+源极区植入。在本实施例中,p+插塞区域首先形成,而源极沟则是在后来的ild蚀刻步骤中创建的。

339、一个实施例涉及到在侧壁隔板形成后和n+源极植入前应用的专用硬屏蔽。该层防止在器件外围形成n+源极区,因此避免了器件外围的寄生npn结构。

340、一个实施例涉及到一个放置在n+源极区下面并与主p井区电连接的p井区(p井#2)。p井#2在n+源极的植入下提供额外的电剂量,以防止伸入式击穿,特别是在源极沟形成后。

341、一个实施例涉及到一个专门的制程步骤,用于掩盖器件外围的n+源极区以及主动区单元格中间的n+源极区的植入,以实现与p井区的欧姆接触。

342、一个实施例涉及在器件外围形成分段式多晶硅闸极金属化层,而不是连续的闸极总线,这将减少mosfet的闸极基极电容。

343、一个实施例涉及mosfet闸极电容的降低。

344、一个实施例涉及改进mosfet的开关转换速度。

345、本文所述的实施例显示了设计和制造自对准sic dmosfet功率器件的新颖技术。由于sic平面dmosfet可实现的迁移率有限,有必要形成亚微米长度的n井通道,以便mosfet的整体功率和导通电阻不会下降。

346、在mosfet中,由于p井和n+源极区之间的偏移,形成了通道区。如果p井和n+源极区是由两个独立的掩蔽步骤形成的,就会出现光刻错位,这将导致单元格两边的mosfet通道长度不对称。在本文所述的实施例中,为了尽量减少mos通道长度的这种不对称性,p井和n+源极植入是以自对准的方式进行的。文献中提出了几种实现自对准mosfet的技术,其中包括使用氧化物间隔物的方法形成自对准的p井和n+源极区,而n+源极植入在p井植入之下。

347、本文的实施例描述了自对准通道形成过程中的几种创新技术,这些技术不仅可以消除sic mosfet制造过程中的错位误差,而且还可以减少通道长度。通道的长度可以用狭窄的间隔物做得更小。虽然自对准过程确实提供了制作任意短的通道长度以及消除错位的好处,但它确实在单元格外的器件结构方面产生了一些其他问题,因为n+区域与p井区是重合的。

348、在传统的mosfet中,p井和n+源极区不是自对准的,有一个专门的掩蔽步骤,将用于形成n+源极植入。在本文所述的实施例中,在自对准制程中,没有专门的掩蔽步骤进行n+源极植入。有一个专门的掩蔽步骤,执行p井植入,然后沉积间隔物,再蚀刻间隔物,接着植入以实现n+源极区。凡是有p井区的地方,也会有n+源极植入。在装置的外围植入n+源极是不可取的。重要的是,只用p型植入物来终止该器件。这里描述的各种实施例介绍了一些技术,可以摆脱器件外围的n+源极植入,并以一些其他区域取代它。

349、mosfet的主动区是发生电流传导的地方,而mosfet的外围区是提供器件边缘终止以阻断任何电压的地方。为了描述本文件中的创新,闸极垫和闸极总线区域也被视为mosfet外围区域的一部分。在本文所述的一个实施例中,涉及到适当位置的源极沟与离子植入的p+插塞区域的组合,以使主主动mosfet区中的p井区适当接地,并去除形成在mosfet外围的寄生n+源极区域

350、在没有自对准的传统mosfet中,可以把源极植入到任何需要的地方,然后创建一个区域用于将p井接地。在自对准的dmosfet中,由于源极植入物与p井自对准,因此不仅p井会一直延伸到外围,而且n+源极区也会一直延伸到外围。

351、一个寄生的npn晶体管存在于mosfet单元格的主动区,由n+源极区,其作用类似于n+发射器,p井区,用于形成p基,和n+源极欧姆接触形成。在器件的外围和闸极垫金属化层下,没有n+源极的欧姆接触,因此,寄生npn晶体管的发射器和基极区域在这个区域没有被短路。在mosfet的正常直流或开关操作下,寄生npn晶体管不会被激活,但在极端条件下操作该器件会导致寄生npn晶体管的触发。

352、在主动区,通过创建源极沟槽,已经将这个寄生npn晶体管的发射器和基极短路,并确保在器件的主动区,这个寄生晶体管将不会导通。在没主动沟槽的器件外围,寄生的npn晶体管存在,即使它在主动区被短路了。寄生的npn晶体管有可能在外围区域导通,这是不可取的。

353、在这里的实施例中,通过在器件的外围创建一个源极沟,并提供一个p型植入的插塞区域,可以确保寄生npn晶体管完全去除。由于该晶体管的发射器已被完全移除,因此没有机会出现任何种类的寄生bjt结构。通常情况下,进行单独的掩蔽步骤,以掩蔽n+源极区在这些位置的形成,但在这里的实施例中,源极沟可以有利地用于去除寄生的n+源极区,并用p+插塞区取代它们,该p+插塞区与源极沟自对准,并与p井区电连接。

354、要放在器件外围的p+插塞区域的掺杂浓度可以有利地做到非常高。这样做,可以避免这里描述的另一个寄生器件效应。在典型的功率mosfet器件结构中,如上所述,在器件外围存在适度掺杂的p井区,可以带有或没有寄生的n+源极区。如果n+源极区与器件外围的p井区重合(即n+源极区没有刻意从外围区域掩盖),这将导致p井区的p型电剂量得到部分补偿。在这两种情况下,从电学角度看,器件外围的p井区可能电阻非常高。在功率mosfet从关断状态切换到导通状态或反之亦然的过程中,汲极电压(或dv/dt)的极高变化率会导致电容性电流流过这个电阻性高的外围p井区,它们只被mosfet主动区的源极欧姆接触收集。换句话说,在器件开关期间,由高dv/dt引起的电容性电流必须从器件外围穿越很长的距离到主动区的源极欧姆接触。在现有技术的mosfet中,p井区的高电阻率会导致显著的基极偏压效应,其结果是降低了这些区域的器件阈值电压。因此,器件的这些部分可能表现出错误的开启,可能导致器件故障/破坏。本实施例中的高掺杂p+插塞区域可以通过减少在mosfet外围区域形成的基极偏压量来缓解上述影响,使得本实施例中描述的mosfet更能抵抗dv/dt引起的故障。换句话说,本实施例中描述的mosfet结构将比现有技术的mosfet具有更高的dv/dt等级。这减少了开关损耗,提高了电路效率。

355、在本文的一个实施例中,利用一个专门的制程步骤来掩蔽器件外围的n+源极区植入。在本实施例中,p+插塞区域首先形成,而源极沟则是在后来的ild蚀刻步骤中创建的。

356、在本文的实施例中,在器件的主动区有一个源极沟,但在器件的外围没主动沟。在p井区植入后和n+源极植入前形成的侧壁间隔物之间穿插了一个专门的掩蔽步骤,以从mosfet的外围区域掩蔽n+源极的植入。屏蔽层保护器件的外围不受源极植入区域的影响。第二个更深的p井区(p井#2)是使用用于n+源极植入的相同掩蔽步骤形成的。在稍后的步骤中,在器件的主动区以及器件外围都形成了p+插塞区。随后,在主动区的不连续位置蚀刻出一条穿过n+源极区的沟槽,以接触p+插塞区,后者通过欧姆或硅化物金属化层与n+源极区形成短路。

357、在本文的一个实施例中,源极区植入从器件的外围被掩蔽。使用一个专门的制程步骤,用于掩蔽器件外围的n+源极区以及主动区单元格中间的n+源极区的植入,以实现与p井区的欧姆接触。

358、在这里的一个实施例中,多晶硅金属化层在器件的外围被分段,而不是像通常看到的那样是一个连续的层。在形成侧壁间隔物之间,在p井区植入之后和实施n+源极植入之前,有一个专门的掩蔽步骤,以将n+源极区从器件的外围区域以及主动区中的选定区域掩蔽。

359、在这里的一个实施例中,将多晶硅金属化层分段,可以减少寄生的闸极到基极电容或闸极到源极电容,这些都是寄生电容。多晶硅岛不是断开的,而是在与图平面正交的位置连接的。减少寄生电容将使器件的开关速度更快,这将通过减少开关损耗提高电路效率。

360、图10所示的一个实施例是sic dmosfet的横截面结构的单元格和器件外围。该器件的关键区域是p井区203,是通过离子植入或p型种如铝或硼的外延再生长形成。有一个n+源极区204,n-漂移层202,和一个n+基板201。在导通状态下,当闸极电压被施加到多晶硅闸极208上时,电流从汲极201垂直流过在p井层203顶部形成的反转层,通过n+源极区204,并通过源极金属化层211流出。在关断状态或阻断状态下,一个电压被支持在p井区203、n-漂移层202接面上,并且在p井区和n-漂移层之间形成一个pn接面。施加到结构上的电压在反向偏压下被支持在这个pn接面上。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井区中形成反转通道的部分,两个连续的p井区之间的距离,即接面型场效应管(jfet)区域或间隙,以及闸极氧化物207的厚度。另一个特征是ild层209,用于将源极互连金属化层211与多晶硅闸极208绝缘。

361、源极沟区205是通过在器件的选定位置干法蚀刻穿过n+源极层来实现的,然后通过p型离子植入步骤来实现源极沟下的p+插塞区206。在单元格的最中心,有一个p+插塞206,它与n+源极金属化层接地。sic dmosfet中p+插塞的目的是通过n+源极接触点将p井区接地。

362、源极沟205器件结构的形成使主主动mosfet区域的p井区能够适当接地,并去除在mosfet外围形成的寄生n+源极区域204。当n+源极区以自对准方式与p井区形成时,在n+源极区形成后,源极沟的形成将寄生的n+源极区从芯片的器件外围和闸极垫区的下方移除。

363、在这里的实施例中,源极沟和离子植入的p+插塞区的结合提供了三个重要的功能。首先,它提供了p井区与器件主动区的源极欧姆接触的适当接地,其次,它有助于消除无意中在器件外围形成的寄生n+源极区。第三,高掺杂的p+插塞区域增加了mosfet的dv/dt等级。在这里的实施例中,上述两点都能确保去除寄生npn晶体管,否则它会在这些区域形成。

364、虽然mosfet单元格内也存在一个寄生的npn晶体管,但n+发射器(由n+源极区形成)和p基(由p井区形成)被n+源极欧姆接触短路。在器件的外围和闸极垫金属化层下,没有n+源极的欧姆接触,因此,寄生npn晶体管的发射器和基极区域在这个区域没有被短路。虽然这个寄生npn晶体管在mosfet的正常直流或开关操作下不会被激活,但该器件在短路或崩溃模式等极端条件下的操作会导致同时出现极高的接面温度、高dv/dt和高电流密度,这可能导致寄生npn晶体管的触发。通常,执行单独的掩蔽步骤以掩蔽在这些位置形成的n+源极区。但在本文的实施例中,源极沟可有利地用于移除寄生n+源极区并将其替换为p+插塞区,该p+插塞区与源极沟自对准并电连接到p井区。

365、图11a至图11ff描述了图10所示结构的制造过程。sic dmosfet的制造过程是在sic基板301上,首先使用4h-sic si-面磊晶圆,其具有适合图11a所示的外延层302的掺杂度(1014-1018cm-3)和厚度(1μm至300μm)。在图11b中的沉积包含二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的化学气相沉积(cvd)沉积层(厚度在50nm到5μm之间)的毯状硬屏蔽303,然后使用光刻术形成图案,随后使用反应离子蚀刻(rie)进行干蚀刻,如图11c所示。然后以铝或硼为p型杂质,通过离子注入或外延生长形成p井区。在图11d中以1012cm-2至1015cm-2的注入剂量在10kev到800kev的能量范围内执行包含硼或铝的p型注入304,以创建图11e中的p井305。

366、第二硬屏蔽层306由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积在图案化的第一硬屏蔽层303的顶部,其厚度在图11f中为50nm到5μm之间。随后是图11g中的非等向蚀刻(anisotropic etching)307,以形成如图11h所示的侧壁垫片306。

367、在图11i中完成n型植入物308以在图11j中创建n+源极区309。n+源极区由离子注入或由n型杂质(例如氮或磷)外延再生长形成。因此,源极区309以与p井区304自对准的方式形成。在图11k中分别移除第一和第二硬屏蔽层303和306。虽然上述步骤序列是构成自对准p井和n+源极区的一种方法,但可采用其他方法来实现相同的结果。例如,n+源极区309可先在第一硬屏蔽层的沉积和图案化之后形成,随后进一步蚀刻第一硬屏蔽层以再形成p井区304。

368、另一个由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积出的屏蔽层310,其在图11l顶部厚度范围是从50nm到5μm之间。屏蔽层310在图11m中被图案化。图案化屏蔽310在干蚀刻方法中被用于蚀刻在图11n中的基板311中,以在sic内创建凹陷区域。源极沟312是通过穿透图11o中的源极区域而在基板中形成的凹陷区域。在这些选定的位置中,整个n+源极区以干法蚀刻被去除。使用相同的硬屏蔽310,通过在图11p中注入受控剂量的p型杂质313,例如铝或硼,在图11q中形成p+插塞层。在特定实施方式中,p+插塞层314的深度可优选地超过n+源极注入的深度,甚至可超过p-井区域的深度。在图11d中以1013cm-2到1017cm-2的注入剂量在10kev到800kev的能量范围内执行包含硼或铝的p型注入以创建p+塞区域。p+插塞区域314在源极沟312下实现,源极沟312电连接到p井区域304。在图11r中移除屏蔽层。晶圆退火以激活注入的杂质。

369、作为闸极氧化物的氧化物层315通过热氧化或使用如图11s中的二氧化硅、氮化硅、氮氧化硅等的介电层的cvd形成。闸极氧化层的厚度可以在5nm到100nm之间。干热氧化或湿热氧化均可用于氧化物生长。闸极氧化物沉积可采用电浆增强化学气相沉积(pecvd)或低压化学气相沉积(lpcvd)。然后在图11t中沉积多晶硅闸极层316。可使用pecvd或lpcvd沉积多晶硅层。多晶硅层可使用硼或磷在原位或后续步骤中简并掺杂。可通过向多晶硅沉积化学中添加ph3前体来执行原位掺杂。多晶硅的沉积后掺杂可通过沉积一层pocl3,然后在600-900℃的温度范围内进行驱动步骤来执行。硬屏蔽317由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,厚度在50nm到5μm之间,从上到上,并如图11u所示形成图案。通过使用图11v中的图案化屏蔽层317来蚀刻多晶硅层316。然后在图11w中移除屏蔽层317。在图11x中的晶圆上沉积包含50nm-1000nm厚的二氧化硅、氮化硅、氮氧化硅层或其堆栈组合的ild层318。

370、硬屏蔽319由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其顶部的厚度在50nm到5μm之间,并且在顶部形成图案以限定图11y中的ild开口。如图11z所示,使用硬屏蔽319蚀刻ild层318。此外,使用图11aa中的相同屏蔽319蚀刻闸极氧化物315。然后在图11bb中移除屏蔽319。在图11cc中,在暴露的sic表面上形成硅化镍区域320。屏蔽层321由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层形成,顶部厚度在50nm到5μm之间,并在图11dd中形成图案。使用图11ee中的屏蔽321蚀刻ild层318。在图11ff中移除屏蔽层321。将铝或银或金的互连金属层322沉积并在基板的顶部和底部形成图案。图11gg。

371、在本文的实施例中,可以使用稍微不同的方法替代地实现用于形成源极沟区域和p+插塞区域的相同最终结构。在上述方法中,p井区和n+源极区使用自对准制程实现。然而,在本文的实施例中,可以首先使用深硼或铝注入作为埋层来形成p-塞层,该埋层放置在n+源极区之下。用于n+源极沟实现的干蚀刻可在该过程的稍后执行。在一个实施例中,可以优选地在高温退火过程之后实现n+源极沟。

372、图12中所示的实施例是sic dmosfet的横截面结构的单元和器件外围。该器件的关键区域是p井区403,其由p型物种(例如铝或硼)的离子注入或外延再生长形成。存在n+源极区404、n-漂移层402和n+基板401。当闸极电压被施加到多晶硅闸极407时,在导通状态下,电流从汲极401垂直流动,通过形成在p井层403顶部的反转层,通过n+源极区域404,并通过源极金属化层412流出。在关断状态或阻断状态下,在p井403、n漂移层402接面之间支持电压,并且在p井和n漂移层之间形成pn接面。施加在该结构上的电压在反向偏压中通过该pn接面得到支撑。功率mosfet有几个关键特性,包括单元节距(mosfet的重复单元)、通道长度(形成反转通道的p井部分)、两个连续p井之间的距离,其被称为jfet区域或jfet间隙和闸极氧化物407的厚度。另一特征是ild层409,其用于将源极互连金属化层412与多晶硅闸极隔离

373、在p井植入物之后和n+源极注入物之前的侧壁间隔物的形成之间穿插有专用的掩蔽步骤,以从mosfet的外围区域掩蔽n+源极注入物。使用用于n+源极注入的相同掩蔽步骤形成第二更深的p井区域(p井#2)405。在随后的步骤中,在器件的主动区以及器件外围形成p+插塞区406。p+插塞406通过n+源极金属化层接地。sic dmosfet中的p+插件的目的是用n+源极接触点将p井区域接地。

374、沟槽410随后在主动区中离散位置处蚀刻穿过n+源极区以接触p+插塞区,p+插塞区通过欧姆硅化物411金属化层与n+源极区形成短路。使用用于对层间介电层(ild)进行图案化的相同硬屏蔽,在选定区域将源极沟410蚀刻到sic中。在本文的实施例中,源极沟槽410具有两个功能。首先,源极沟露出先前埋在n+源极区下的p+塞层的表面,用于随后与欧姆硅化物金属接触,第二,源极沟露出n+源极区的侧壁,用于随后与欧姆硅化物金属接触。

375、在本文的实施例中,在形成侧壁间隔物之后并且在n+源极注入之前应用专用硬屏蔽或光致抗蚀剂层。该层防止在器件外围中形成n+源极区,并避免器件外围中的寄生npn结构

376、在本文的实施例中,第二p井区(p井#2)405置于n+源极区404之下,并电连接到主p井区,在n+源极注入下提供额外的电剂量,以防止穿透击穿,特别是在源极沟形成之后。源极沟的蚀刻可能无意中蚀刻n+源极区下的主p井区的一部分,从而局部降低该区域中的p井剂量,导致这些位置处的不良穿透击穿。

377、图13a至图13gg描述了制造图12所示结构的过程。sic dmosfet的制程在sic基板501上,并从使用4h sic si面外延芯片开始,该4h sic si面外延芯片具有图13a所示外延层502的适当掺杂(1014-1018cm-3)和厚度(1μm至300μm)在图13b中沉积包含二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层(厚度在50nm到5μm之间)的覆盖硬屏蔽503,然后使用光刻术进行图案化,随后使用rie(例如,如图13c所示)进行干蚀刻。然后以铝或硼为p型杂质,通过离子注入或外延生长形成p井区。执行包含硼或铝的p型注入504,能量范围为10kev至800kev,注入剂量范围为1012cm-2至1015cm-2,如图13d所示,以创建图13e中的p井505。

378、第二硬屏蔽层506由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积在图案化的第一硬屏蔽层503的顶部,其厚度在图13f中为50nm到5μm之间。随后是图13g中的非等向蚀刻507,以形成如图13h所示的侧壁垫片506。图案化屏蔽层508由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其厚度在图案化屏蔽层顶部的50nm到5μm之间,并具有图13i中的侧壁垫片。硬屏蔽层508图案化在器件的外围区域上。

379、在图13j中完成n型植入物509以在图13j中创建n+源极区510。n+源极区由离子注入或由n型杂质(例如氮或磷)外延再生长形成。n+源极区510以与p井区504自对准的方式形成。源极区以与p井区自对准的方式形成,同时源极区与器件的外围区屏蔽。深第二p井区(p井#2)511可与图13k中的n+源极区同时形成。埋入的p井#2区域可使用铝或硼形成,并放置在器件主动区的n+源极区下方。p井#2区域可优选使用p型物种硼形成,与sic中的铝相比,p型物种硼具有更高的离子注入范围。可能不需要将p井区域#2与器件的外围区域屏蔽。

380、在图13l中分别移除第一和第二硬屏蔽层503和506。另一屏蔽层512由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其厚度在图13m顶部从50nm到5μm之间。屏蔽层512在图13n中被图案化。通过在图13o中以受控剂量注入诸如铝或硼的p型杂质513,在图13p中实现埋在n+源极区510下的p+塞区514p+塞区域514电连接到p井区域504和p井#2区域511。p+塞区域的形成可能比p井和p井#2区域更深。然后在图13q中移除屏蔽层512,并且通过高温退火激活植入物。

381、作为闸极氧化物的氧化物层515通过热氧化或使用介电层的cvd例如二氧化硅、氮化硅、氮氧化硅等形成,如图13r。闸极氧化层的厚度可以在10nm到100nm之间。干热氧化或湿热氧化均可用于氧化物生长。pecvd或lpcvd可用于闸极氧化层沉积。多晶硅闸极层516随后沉积在图13s中多晶硅层可使用pecvd或lpcvd来沉积。多晶硅层可使用硼或磷在原位或后续步骤中简并掺杂。可通过向多晶硅沉积化学中添加ph3前体来执行原位掺杂。多晶硅的沉积后掺杂可通过沉积一层pocl3,然后在700-900℃的温度范围内进行驱动步骤来执行。由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积出硬屏蔽517,顶部厚度在50nm到5μm之间,并促成如图13t。通过使用图13u中的图案化屏蔽层517来蚀刻多晶硅层516。然后在图13v中移除屏蔽层517。ild层518包含50nm-1000nm厚的二氧化硅、氮化硅、氮氧化硅层或其堆栈组合由此在图13w中的晶圆上沉积。硬屏蔽519由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积出,其顶部的厚度在50nm到5μm之间,并且在顶部形成图案以限定图13x中的ild开口。如图13y所示,使用硬屏蔽蚀刻ild层518。此外,使用图13z中的相同屏蔽519蚀刻闸极氧化物515。在图13aa中,用于图案化ild层519的硬屏蔽用于通过完全蚀刻穿过n+源极层并进入p+塞层来实现源极沟区域520。然后在图13bb中移除屏蔽519。在图13cc中,在暴露的sic表面上形成硅化镍区域521。屏蔽层522由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层形成,其顶部厚度在50nm到5μm之间,然后在图13dd中图案化。在图13ee中蚀刻ild层518。在图13ff中移除屏蔽层522。图13gg,属铝或银或金的互连金属层523沉积并在基板的顶部和底部形成图案。与传统mosfet中的n+源极区域的水平表面相反,在本实施例中,通过源极沟槽区域的蚀刻侧壁与n+源极区域进行欧姆接触。

382、图14所示的实施例是sic dmosfet的横截面结构的单元和器件外围。该器件的关键区域是p井区域603,其由p型物种(例如铝或硼)的离子注入或外延再生长形成。存在n+源极区604、n-漂移层602和n+基板601。在导通状态下,当闸极电压被施加到多晶硅闸极607时,电流从汲极601垂直流动,通过形成在p井层603顶部的反转层,通过n+源极区域604,并通过源极金属化层610流出。在关断状态或阻断状态下,在p井603、n漂移层602接面之间支持电压,并且在p井和n漂移层之间形成pn接面。施加在该结构上的电压在反向偏压中通过该pn接面得到支撑。功率mosfet有几个关键特性,包括单元节距(mosfet的重复单元)、通道长度(形成反转通道的p井部分)、两个连续p井之间的距离,其被称为jfet区域或jfet间隙和闸极氧化物606的厚度。另一特征是ild层608,其用于将源极互连金属化层610与多晶硅闸极607隔离。在单元电池的最中心,有一个p+插塞层605,该层通过n+源极金属化层接地。sic dmosfet中的p+插塞的目的是用n+源极接触点将p井区域接地。

383、在本文的一个实施例中,在p井植入物之后和n+源极注入物之前形成侧壁间隔物之间穿插专用掩蔽步骤,以从mosfet的外围区域掩蔽n+源极注入物。这还屏蔽了来自器件主动区中选定区域的n+源极注入,从而实现与p井或p+塞区域的欧姆接触。该实施例消除了对先前实施例中存在的源极沟的需要。

384、在本文的实施例中,在形成侧壁间隔物之后和n+源极注入之前应用专用硬屏蔽或光致抗蚀剂层,以防止在器件外围中形成n+源极区域,并避免器件外围中的寄生npn结构。在主动区中的选定区域中避免注入n+源极区,并且这使得能够在没有中间n+源极区的情况下与p井或p+塞区进行欧姆接触。

385、图15a至图15ff描述了制造图14所示结构的过程。sic dmosfet的制程在sic基板701上,并且首先使用4h sic si面外延芯片,该芯片具有图15a所示外延层702的适当掺杂(1014-1018cm-3)和厚度(1μm至300μm)。在图15b中沉积包含二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层(厚度在50nm到5μm之间)的毯状硬屏蔽703,然后使用光刻术进行图案化,随后例如使用rie进行干蚀刻,如图15c所示。然后以铝或硼为p型杂质,通过离子注入或外延生长形成p井区。在图15d中以1012cm-2到1015cm-2的注入剂量在10kev到800kev的能量范围内执行包含硼或铝的p型注入704,以创建图15e中的p井705。

386、第二硬屏蔽层706由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积在图案化的第一硬屏蔽层703的顶部,其厚度在图15f中为50nm到5μm之间。这之后是图15g中的非等向蚀刻707,以形成如图15h所示的侧壁垫片706。硬屏蔽层708由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其厚度范围为50nm至5μm,并在图15i中图案化。图案化屏蔽层与侧壁垫片706一起在图案化屏蔽层旁边的顶部形成。在图15j中完成n型植入物709以在图15k中创建n+源极区710。n+源极区由离子注入或由n型杂质(例如氮或磷)外延再生长形成。因此,源极区710以与p井区705自对准的方式形成,同时其被器件的外围区域以及器件的主动区的选定区域屏蔽,以使得能够与源欧姆金属化层接触。在图15l中分别移除第一和第二硬屏蔽层703和708。另一屏蔽层711由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其顶部厚度从50nm到5μm不等,在图15m。屏蔽层711在图15n中被图案化。

387、使用硬屏蔽711,通过在图15o中注入受控剂量的p型杂质712,例如铝或硼,在图15p中实现p+塞区域。在特定实施方式中,p+插塞层713的深度可优选地超过n+源极注入的深度,甚至可超过p井区域的深度。在图15q中移除屏蔽层711。晶圆退火以激活注入的杂质。

388、作为闸极氧化物的氧化物层714通过热氧化或如图15r中的使用介电层如二氧化硅、氮化硅、氮氧化硅等的cvd形成。闸极氧化层的厚度可以在10nm到100nm之间。干热氧化或湿热氧化均可用于氧化物生长。pecvd或lpcvd可用于闸极氧化层沉积。然后在图15s中沉积多晶硅闸极层715。多晶硅层可使用pecvd或lpcvd来沉积。多晶硅层可使用硼或磷在原位或后续步骤中简并掺杂。可通过向多晶硅沉积化学中添加ph3前体来执行原位掺杂。多晶硅的沉积后掺杂可通过沉积一层pocl3,然后在700-900℃的温度范围内进行驱动步骤来执行。由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积出硬屏蔽716,顶部厚度在50nm到5μm之间,并促成如图15t。通过使用图15u中的图案化屏蔽层716来蚀刻多晶硅层715。然后在图15v中移除屏蔽层716。在图15w中的晶圆上沉积包含50nm-1000nm厚的二氧化硅、氮化硅、氮氧化硅层或其堆栈组合的ild层717。

389、硬屏蔽718由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其顶部的厚度在50nm到5μm之间,并且在顶部形成图案以限定图15x中的ild开口。如图15y所示,使用硬屏蔽蚀刻ild层717。此外,使用图15z中的相同屏蔽718蚀刻闸极氧化物714。然后在图15aa中移除屏蔽718。在图15bb中,在暴露的sic表面上形成硅化镍区域719。屏蔽层720由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层形成,其顶部的厚度在50nm到5μm之间,然后在图15cc中图案化。在图15dd中蚀刻ild层717。在图15ee中移除屏蔽层720。在图15ff中,在基板的顶部和底部沉积铝或银或金的互连金属层721并形成图案。

390、图8所示的实施例是sic dmosfet的横截面结构的单元和器件外围。该器件的关键区域是p井区域803,其由p型物种(例如铝或硼)的离子注入或外延再生长形成。存在n+源极区804、n-漂移层802和n+基板801。在导通状态下,当闸极电压被施加到多晶硅闸极807时,电流垂直地从汲极801流过形成在p井层803顶部的反型层,流过n+源极区域804,并通过源极金属化层810流出。在关断状态或阻断状态下,在p并803、n-漂移层802接面之间支持电压,并且在p井和n-漂移层之间形成pn接面。施加在该结构上的电压在反向偏压中通过该pn接面得到支撑。功率mosfet有几个关键特性,包括单元节距(mosfet的重复单元)、通道长度(形成反转通道的p井部分)、两个连续p井之间的距离,其被称为jfet区域或jfet间隙和闸极氧化物806的厚度。另一特征是ild层808,其用于将源极互连金属化层810与多晶硅闸极807隔离。在单元电池的最中心,有一个p+插塞805,该层通过n+源极金属化层接地。sicdmosfet中的p+塞的目的是用n+源极接触点将p井区域接地。

391、在本文的一个实施例中,在p井植入物之后和n+源极注入物之前形成侧壁间隔物之间穿插专用掩蔽步骤,以从mosfet的外围区域掩蔽n+源极注入物。这还屏蔽了来自器件主动区中选定区域的n+源极注入,从而实现与p井或p+塞区域的欧姆接触。该实施例消除了在一些早期实施例中存在的源极沟的需要。

392、在本文的实施例中,在形成侧壁间隔物之后和n+源极注入之前应用专用硬屏蔽或光致抗蚀剂层,以防止在器件外围中形成n+源极区域,并避免器件外围中的寄生npn结构。在主动区中的选定区域中避免注入n+源极区,并且这使得能够在没有中间n+源极区的情况下与p井或p+塞区进行欧姆接触。

393、在本文的实施例中,器件807的外围区域中的多晶硅金属化层是分段的,而不是连续层。在本文的实施例中,在器件外围形成分段闸极金属化层而不是连续闸极总线可显著降低mosfet的闸极基极电容。这可能导致mosfet的开关速度显著提高。

394、图17a至图17ff描述了制造图8所示结构的过程。sic dmosfet的制程在sic基板901上,并且首先使用4h-sic si面外延芯片,该芯片具有图17a所示外延层902的适当掺杂(1014-1018cm-3)和厚度(1μm至300μm)。在图17b中沉积包含二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层(厚度在50nm到5μm之间)的毯状硬屏蔽903,然后使用光刻术进行图案化,随后例如使用rie进行干蚀刻,如图17c所示。然后以铝或硼为p型杂质,通过离子注入或外延生长形成p井区。在图17d中以1012cm-2到1015cm-2的注入剂量在10kev到800kev的能量范围内执行包含硼或铝的p型注入904,以创建图17e中的p井905。

395、第二硬屏蔽层906由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积在图案化的第一硬屏蔽层903的顶部,其厚度在图17f中为50nm到5μm之间。这之后是图17g中的非等向蚀刻907,以形成如图17h所示的侧壁垫片906。硬屏蔽层908由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其厚度范围为50nm至5μm,并在图17i中图案化。图案化屏蔽层908与侧壁间隔物一起在图案化屏蔽层旁边的顶部形成。在图17j中完成n型注入909以在图17k中创建n+源极区910。n+源极区由离子注入或由n型杂质(例如氮或磷)外延再生长形成。因此,源极区910以与p井区905以自对准的方式形成,同时其被器件的外围区域以及器件的主动区的选定区域屏蔽,以使得能够与源极欧姆金属化层接触。在图17l中分别移除第一和第二硬屏蔽层903和908。另一屏蔽层911由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,在图17m顶部的厚度范围为50nm至5μm。屏蔽层911在图17n中形成图案。

396、使用硬屏蔽911并通过在图17o中注入受控剂量的p型杂质912(如铝或硼),在图17p中实现p+插塞区域913。在图17q中移除屏蔽层911。晶圆退火以激活注入的杂质。

397、作为闸极氧化物的氧化物层914通过热氧化或使用如图17r中的二氧化硅、氮化硅、氮氧化硅等的介电层的cvd形成。闸极氧化层的厚度可以在10nm到100nm之间。干热氧化或湿热氧化均可用于氧化物生长。pecvd或lpcvd可用于闸极氧化层沉积。然后在图17s中沉积多晶硅闸极层915。多晶硅层可使用pecvd或lpcvd来沉积。多晶硅层可使用硼或磷在原位或后续步骤中简并掺杂。可通过向多晶硅沉积化学中添加ph3前体来执行原位掺杂。多晶硅的沉积后掺杂可通过沉积一层pocl3,然后在700-900℃的温度范围内进行驱动步骤来执行。由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积出硬屏蔽916,顶部厚度在50nm到5μm之间,并促成如图17t。通过使用图17u中的图案化屏蔽层916来蚀刻多晶硅层915。在本文描述的实施例中,用于对多晶硅闸极金属进行图形化的掩蔽步骤产生部分分段的多晶硅图形。虽然在横截面示意图中不明显,但断开的门指应在与图纸平面正交的位置连接。使用图案化屏蔽916在图17v中蚀刻闸极绝缘体914。然后在图17w中移除屏蔽层916。在图17x中的晶圆上沉积包含50nm-1000nm厚的二氧化硅、氮化硅、氮氧化硅层或其堆栈组合的ild层917。

398、硬屏蔽918由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层沉积,其顶部的厚度在50nm到5μm之间,并且在顶部形成图案以限定图17y中的ild开口。如图17z所示,使用硬屏蔽蚀刻ild层917。然后在图17aa中移除屏蔽918。在图17bb中,在暴露的sic表面上形成硅化镍区域919。屏蔽层920由二氧化硅、氮化硅、氮氧化硅或金属层(例如镍)的cvd沉积层形成,其顶部的厚度在50nm到5pm之间,然后在图17cc中图案化。在图17dd中蚀刻ild层917。在图17ee中移除屏蔽层920。将铝或银或金的互连金属层921沉积并在基板的顶部和底部形成图案。图17ff。

399、实施例涉及sic dmosfet功率器件,其中p井区域有效地屏蔽敏感闸极氧化物,使其免受sic中存在的高电场的影响,尤其是在高汲极偏压或阻断模式操作期间。

400、一个实施例涉及使用p+塞将具有n+源极接触点的p井区域接地。

401、一个实施例涉及一种设备在源极区形成之前,通过对p井注入区进行干法蚀刻形成p井通道,从而在(0001)面或水平面上形成一部分mos通道,在(11-20/10-10)面上形成另一部分mos通道或者sic的垂直晶面,这有利于增加mos通道迁移率。

402、一个实施例涉及一种设备一种更深的垂直mos通道,通过蚀刻穿过p井区域形成。随后,在n+源极区形成后,第二个p井区(pw#2)被离子注入n+源极区下方和周围,以抑制到达穿透击穿。

403、一个实施例涉及一种设备p井通道的形成为器件设计者提供了灵活性,既可以增加给定导通电阻目标的有效通道长度,也可以降低给定芯片尺寸的导通电阻。

404、电力电子中的sic器件具有快速开关时间、高阻断电压能力和在高温下工作的能力。这些特性以及制程的最新进展表明,sic作为传统硅基(si)器件的继任者,有可能彻底改变电力电子技术。sic是一种宽带隙材料(3.3ev),与si(si带隙为1.1ev,si的击穿电场为0.3x106v/cm)相比,sic具有更高的击穿电场(3x106v/cm至5x106v/cm)。sic是一种更好的热导体(sic为3.7(w/cm-k)而si为1.6(w/cm-k)),它使sic器件能够在极高的功率水平下运行,并且仍能耗散产生的大量多余热量。sic的这些材料特性为在功率器件上使用sic代替si提供了多种优势。在具有相同结构和尺寸的sic和硅半导体体芯片的比较中,sic芯片显绘示比硅芯片更低的导通电阻和更高的击穿电压

405、本文公开的实施例提供了用于sic dmosfet设计和制造的具有更高通道密度的新技术,其可有利于降低器件的导通电阻。

406、在典型的sic平面mosfet结构(也称为dmosfet)中,mos通道形成在sic的水平或0001晶面上。与垂直侧壁或11-20或10-10晶面相比,sic 0001晶面上的通道迁移率或场效应迁移率往往较低。当制作平面sic dmosfet时,导通电阻往往很大,并且dmosfet受到场效应通道迁移率的限制。

407、与硅mosfet相比,sic 0001晶面上的通道迁移率或场效应迁移率在15到25cm2/v-sec的范围内,硅mosfet的通道迁移率或场效应迁移率可以超过350cm2/v-sec。设计低电阻sic mosfet的一种方法是找到可以创建非常小的通道长度的方法,以便这种反型层迁移率仅在该器件电流传导路径的较小区域内有效,但这可能导致短通道效应问题。因此,仅减少通道并不能解决0001晶面中的低通道迁移率问题,因为它引入了短通道效应,这导致该器件的可靠性差和鲁棒性差。在本文的实施例中,解决该问题的一种方法是通过在sic中引入沟槽mosfet。在沟槽mosfet中,取代在水平或0001晶面上形成mos通道,通道现在形成在垂直侧壁上或所谓的a平面或m平面上,或也称为10-10或11-20平面上。与水平面相比,这两个平面具有显著更高的通道迁移率,接近水平面的五倍,导致垂直通道的迁移率为110至120cm2/v-sec。

408、与平面mosfet相比,沟槽mosfet可以提供更高的通道密度,因此可以增加封装密度。由于通道移动性更高,它使器件具有较小的导通电阻。尽管传统沟槽mosfet比dmosfet具有优势,但sic中传统沟槽mosfet结构的问题在于,沟槽底部存在高电场,并且沟槽中的一部分闸极氧化物在阻塞操作模式下受到高电场的影响。这将成为典型沟槽mosfet结构的故障点,为了克服此问题,有必要在沟槽底部屏蔽闸极氧化物。用于屏蔽闸极氧化层的p型植入和类似w-沟mosfet的方法用于屏蔽闸极氧化层。

409、但是,创建这些屏蔽区域会增加导通电阻。与dmosfet相比,通道mosfet具有更高的通道迁移率,因此降低了导通电阻,但它在通道拐角处产生了高电场。为了解决这个问题,引入了屏蔽区,但这会增加导通电阻。通过降低沟槽mosfet的导通电阻而获得的一些好处现在由于屏蔽而丧失,屏蔽是设计传统沟槽mosfet时的一种折衷。

410、在本文的实施例中,该器件既不是纯dmosfet,也不是纯沟槽mosfet。在该器件中,mos通道形成在0001平面以及垂直侧壁或11-20(或10-10)平面上,因此它是dmosfet和沟槽mosfet之间的混合体。

411、在本文的实施例中,与纯dmosfet相比,该器件具有更短的总通道长度,但具有相同的有效通道迁移率。通过以这种方式增加通道长度,您可以克服与制作短通道dmosfet相关的一些健壮性和可靠性问题。在本文的实施例中,该器件具有完全包围或包围在p型注入区中的沟槽。这为高电场提供了自然屏蔽。由于沟槽完全在p井内形成,因此沟槽不存在暴露于n-型外延层的区域,n-型外延层可缓解沟槽角落处的高电场问题。

412、在本文的实施例中,该器件的结构通过蚀刻到p井区域中的沟槽来区分,并且该沟槽被称为p井沟槽。在第一实施例中,形成p井区域,然后将沟槽蚀刻到p井区域中,因此该沟槽的所有侧面都包含在该p井区域中。该沟槽也紧随n+源极区的形成。通过如本实施例中所述的该过程,该器件具有在0001相位上形成的mos通道的一部分以及在11-20或10-10平面上形成的通道的另一部分。

413、形成本实施例中所述器件的主要步骤是通过离子注入或外延生长,以铝或硼作为p型杂质,形成p井区。然后,通过使用反应离子蚀刻(rie)或具有用于形成该沟槽的适当硬屏蔽层的高功率电感耦合电浆(icp)源,通过控制蚀刻到p井区域来形成p井沟槽。

414、在本文的实施例中,该沟槽可以形成在70°和90°之间的侧壁角度。这是形成沟槽的近似角度。例如,该沟槽的深度可在0.1μm至0.5μm之间。p井沟的深度可以调整为小于p井区的深度,p井沟的底部完全封闭在p井区内。

415、在本文的实施例中,在形成p井通道之后,通过离子注入或通过使用杂质(例如氮或磷)外延再生长来形成n+源极区。n+源极完全包含在p井区域内,n+源极不延伸到p井区域之外。在本文的实施例中,一个选项是,p井沟槽区域可使用与可用于形成n+源极区域相同的掩蔽步骤形成,即使不需要。接下来,通过注入铝或硼来形成用于接地p井的p+塞层。p+塞层的深度可能超过源极注入层的深度,这样它既可以使源极注入与放置在顶部的欧姆层短接,也可以为p井区域提供接地。该制程的其余部分包括晶圆的热处理,用于电激活、电形成、闸极金属形成、层间电介质(ild)、图案化ild、欧姆金属化层、以及设置厚焊盘金属化层。

416、在本文的实施例中,为了形成闸极绝缘体,使用诸如二氧化硅、氮化硅或氮氧化合物的介电层的热氧化或化学气相沉积(cvd)。在sic中,0001平面的氧化速率与11-20或10-10平面不同,这意味着水平侧壁和垂直侧壁的氧化速率不同。这会导致垂直侧壁上的闸极氧化层比水平侧壁上的闸极氧化层更厚。在本文的实施例中,可以沉积cvd二氧化硅,并确保水平侧和垂直侧的厚度相同。

417、在具有本文所述sic dmosfet的实施例p井沟槽在源极区形成之前和p井区形成之后形成。器件中的mos通道的一部分现在平行于0001平面形成,另一部分平行于11-20平面形成。与用于相同横向封装的平面器件相比,根据本实施例制造的mosfet将具有更高的通道密度,因此能够实现更紧密的封装。除了几何地增加通道密度之外,本文的实施例还可以利用垂直侧壁的更高通道移动性。

418、在本文的实施例中,器件具有更高的通道密度、更高的通道迁移率和更低的导通电阻。对于给定的导通电阻目标,可以增加有效通道长度。当将实施例中描述的器件与典型平面dmosfet进行比较时,对于相同的导通电阻目标,可以使实施例中的器件具有更高的通道长度。短信道效应会降低系统的可靠性和鲁棒性,而较长的信道长度可以缓解短信道效应。在本实施例中使用该器件的另一种方法是,对于与平面dmosfet中相同的通道长度,您可以实现更小的芯片,这意味着更低的成本器件。

419、本实施例中的器件可以具有与平面dmosfet相同的通道长度,但是由于11-20和10-10方向的更高通道迁移率,因此可以在垂直侧壁中提供更长的通道,并且仍然具有更短的水平通道。由于更高的信道移动性,本实施例中的设备将具有更低的导通电阻。然后,它允许您为相同的导通电阻设计更小的芯片尺寸,并设计一个与本实施例相同的器件,该器件在垂直方向上具有更长的通道,在水平方向上具有更短的通道,从而允许制造更低的导通电阻mosfet。

420、本文描述的实施例可与tega等人在美国专利申请中从hitachi公开的现有技术区分:美国2018/0331174a1,于2018年11月出版。来自hitachi的tega等人在美国专利中描述的现有技术结构描述了一种sic mosfet结构,其中mos通道形成在水平和垂直p井表面上,而在垂直和水平侧壁上形成该mos通道的p井通道不是连续形成的。p井沟仅在3d景观中的正交位置形成。如果它是连续形成的,则装置中任何位置的横截面将显示相同的结构。但是,在现有技术的情况下,通过这些类型的沟槽的横截面在每个位置显示不同的横截面,因为设备中有许多区域没有p井沟槽。然而,本文实施例中描述的器件中的p井沟槽在性质上是连续的,因此不同于来自hitachi的tega等人描述的现有技术结构。

421、第二个区别是,当与这里的实施例中所描述的相比时,由来自hitachi的tega等人描述的现有技术结构中的mos通道的构造是完全不同的。现有技术中的mos通道形成在n+源极区和单独的n+累积区之间。在本文描述的实施例中的器件中,首先形成p井区域,然后形成进入p井区域的沟槽,然后形成源极注入。然而,在由tega等人从hitachi描述的现有技术结构中,形成p井区域,随后形成源极注入、聚集区域、热处理,然后形成p井沟槽。区别在于mos通道是如何以及何时在该过程中形成的。

422、第三个区别是,用于在垂直sic晶面上实现mos通道的沟槽创建过程是在现有技术中完成所有注入步骤后进行的,该技术由来自hitachi的tega等人描述。结果,与在垂直侧壁上形成的mos通道相比,n+源极区升高。在本文实施例中描述的器件中,在p井注入之后和在n+源极注入之前立即蚀刻p井沟槽,n+源极注入形成在通过p井沟槽的蚀刻产生的凹陷区域上。

423、在tega等人提出的结构中,除了p+塞区、n+源极区和p井区外,还有n+聚集区和p+屏蔽区。

424、本文描述的实施例使您能够在垂直侧壁上形成极长的通道。p井沟可以形成得更深,因此p井沟的底部可以延伸到p井区域之外。

425、在本文的一个实施例中,形成p井区域,随后形成深p井沟槽和源极注入。在源极注入之后,形成第二个p井区。第二个p井区延伸至源极区下方,并在拐角处有一个盖子,以防止任何锋利边缘的可靠性问题。

426、在本文的实施例中,倾斜注入用于将p井区域延伸到p井区域的横向范围之外,并保护闸极氧化物免受任何汲极感应电场的影响。本实施例中的结构通过将第二p井区延伸到源极区之外,提供了从通道区屏蔽汲极电势的自然方式。

427、形成实施例中描述的器件的过程包括通过使用铝或硼的离子注入或外延生长形成p井区。随后是通过rie或基于icp的蚀刻控制p井区域的蚀刻形成的p井沟槽。p井沟槽的侧壁角度可在75°和90°之间。p井沟槽区域的深度可在0.1μm至2μm的范围内。然后通过离子注入或由氮或磷等n型杂质外延再生长形成n+源极区。在本文的实施例中,由于p井沟槽的底部可能不完全封闭在p井区域内,因此形成第二p井区域。第二个p井在n+源极区下方形成足够的深度,同时确保p井区的横向范围现在大于原始p井区。

428、如这里的实施例中所述,存在两种形成第二p井的方法。在一种情况下,可沉积专用硬屏蔽层并以略大于原始p井区域的范围形成图案,然后可执行pw#2的离子注入。在第二种情况下,倾斜离子注入可有利地用于实现pw#2。在这里描述的一个实施例中,相同的硬屏蔽可用于创建p井沟槽、n+源极区和随后的pw#2区,其横向范围比使用p型杂质的倾斜离子注入的原始pw区更大。该制程的剩余部分包括晶圆的热处理,以电激活注入的杂质、闸极绝缘体形成、闸极电极形成、层间电介质形成、源极/汲极欧姆金属化层,以及最终形成与芯片探测和封装兼容的焊盘或互连金属。闸极绝缘体通过碳化硅的热氧化或通过诸如二氧化硅、氮化硅、氮化硅等介电层的cvd形成。

429、本实施例中描述的器件允许在导通电阻与稳健性之间进行更自由的权衡,这在sic功率mosfet的情况下经常遇到。虽然较长的通道允许您具有良好的短路性能,并且由于通道迁移率较低,导通电阻较高,这是sic的固有特性。

430、图18所示的实施例是sic dmosfet的横截面结构的单元。该器件的关键区域是p井区域203,其由p型物种(例如铝或硼)的离子注入或外延再生长形成。存在n+源极区域204,n-飘移层202和n+基板201。当闸极电压被施加到多晶硅闸极206时,在导通状态下,电流从汲极201垂直流动,通过形成在p井层203顶部的反转层,通过n+源极区域204,并通过源极金属化层208流出。在关断状态或阻断状态下,跨p井203、n-漂移层202接面支撑电压,并且在p井和n-漂移层之间形成pn接面。施加在该结构上的电压在反向偏压中通过该pn接面得到支撑。功率mosfet有几个关键特性,包括单元节距(mosfet的重复单元)、通道长度(形成反转通道的p井部分)、两个连续p井之间的距离,其被称为jfet区域或jfet间隙和闸极氧化物205的厚度。另一特征是ild层207,其用于将源极互连金属化层208与多晶硅闸极206绝缘。在单元电池的最中心,有一个p+塞层209,该层通过n+源极金属化层接地。sic dmosfet中的p+塞的目的是用n+源极接触点将p井区域接地。

431、p井区203首先通过使用铝或硼作为p型杂质的离子注入或外延生长形成。然后,通过使用适当图案化的硬屏蔽层通过rie或icp蚀刻,且控制蚀刻到p井区域203中,来形成p井沟槽210。p井井槽的侧壁角度可在70°和90°之间。p井沟槽区域210的深度可在0.1μm至0.5μm范围内。p井沟槽的深度可以调整为比p井区域的深度浅。p井沟的底部可封闭在p井区域内。然后通过离子注入或由氮或磷等n-型杂质外延再生长形成n+源极区。优选地,可以使用用于执行形成n+源极区204所需的离子注入的相同掩蔽步骤来形成p井沟槽区。可通过注入受控剂量的p型杂质(例如铝或硼)来形成p+塞层209。在特定实施中,p+塞层的深度可以超过n+源极注入的深度,甚至可以超过p井区域的深度。该制程的剩余部分包括晶圆的热处理,以电激活注入的杂质、闸极绝缘体形成、闸极电极形成、层间电介质形成、源极/汲极欧姆金属化层,以及最终形成与芯片探测和封装兼容的焊盘或互连金属。闸极绝缘体205通过热氧化或使用诸如二氧化硅、氮化硅、氮氧化硅等介电层的cvd形成。

432、在本文的实施例中,沟槽形成在形成n+源极区之前的p井区中。mos通道的一部分平行于(0001)晶面形成,而mos通道的另一部分平行于sic的(11-20)或(1-100)晶面形成。根据本实施例制造的dmosfet将具有更高的通道密度,这有利于降低器件的导通电阻。本发明领域的技术人员众所周知,与在平坦(0001)晶面上形成的mos通道相比,平行于4h-sic(11-20)或(10-10)晶面的垂直侧壁上形成的mos通道可以实现更高的场效应迁移率。在这里描述的一个实施例中,除了增加通道密度外,根据本实施例制造的dmosfet的有效通道迁移率预计将高于使用其mos通道始终平行于4h sic的(0001)晶面制造的dmosfet的有效通道迁移率。可利用该期望特征来增加给定导通电阻目标的有效通道长度或减小给定芯片尺寸的导通电阻,以器件设计者感兴趣的为准。

433、本技术中描述的实施例可与tega等人在美国专利申请中公开的装置区分:us2018/0331174a1[以下简称为参考文献1],尽管该申请描述了在垂直和水平p井表面上形成mos通道的sic mosfet结构:

434、(1)在参考文献1中,垂直sic晶面上的mos通道不是连续形成的,而是仅在主动区的离散正交位置形成的。因此,通过参考1mosfet的横截面在垂直sic侧壁上不包含任何mos通道形成。

435、(2)参考文献1中的mos通道结构与本文实施例中描述的完全不同。在参考文献1中,mos通道形成于n+源极区和单独的n+累积区之间,该区域将mos通道连接至jfet区。

436、(3)在参考文献1中,用于在垂直sic晶面上实现mos通道的沟槽创建过程在所有注入步骤完成后进行。结果,与在垂直侧壁上形成的mos通道相比,n+源极区升高。在本文描述的实施例中,在p井注入之后和在n+源极注入之前立即蚀刻p井沟槽,n+源极注入形成在通过p井沟槽的蚀刻创建的凹陷区域上。

437、图19a至图19u描述了图18中所示结构的制造过程。sic dmosfet的制造过程是在sic基板301上进行的,首先是使用4h-sic si面外延晶圆,其掺杂度(1014-1018cm-3)和厚度(1μm至300μm)适合图19a所示的外延层302。在图19b中沉积了一个由cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层(例如镍)组成的空白硬屏蔽303,其厚度为50纳米至5微米,然后使用光刻技术进行图案化,接着使用rie进行干蚀刻,例如图19c所示。然后通过离子植入或外延生长,使用铝或硼作为p型杂质,首先形成p井区。在图19d中进行由硼或铝组成的p型植入304,能量范围为10kev至800kev,植入剂量范围为1012cm-2至1015cm-2,以形成图19e中的p井305。移除屏蔽303,并通过cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层如镍,厚度为50纳米至5微米的另一硬屏蔽层306,然后如图19f所示进行图案制作。通过rie或icp蚀刻,使用图19g中适当图案的硬屏蔽层306,通过控制蚀刻制程307在p井区形成p井沟308。p井沟308的侧壁角度在70°和90°之间。p井沟区域的深度从0.1μm0.5μm。p井沟的深度可以调整为比p井区305的深度浅。p井沟槽308的底部可以被封闭在p井区305内。在图19h中,为创建n+源极区310做了一个n型植入309。n+源极区是通过离子植入或通过n型杂质(例如氮或磷)的外延再生长形成。用于蚀刻p井沟槽的同一硬屏蔽层306可以有利地用于n+源极植入物的图案化,以便源极植入物在p井沟槽下完全对齐。在图19i中,屏蔽层306被移除。在图19j中沉积了另一个硬屏蔽层311。在图19k中,硬屏蔽层311进行图案化。可以通过植入控制剂量的p型杂质312,如图19l中的铝或硼,形成p+插塞。p+插塞313的深度最好可以超过n+源极植入物的深度,甚至可以超过p井区的深度,在图19m的一个特定实施案例中。随后,使用图19n中本领域人士普遍采用的干法或湿法蚀刻技术去除硬屏蔽311。然后通过热氧化或使用如图19o中的二氧化硅、氮化硅、氧氮化硅等电介质层的cvd方式形成作为闸极氧化物的氧化层314。闸极氧化物的厚度可以从10纳米到100纳米。干式或湿式热氧化都可用于氧化物的生长。电浆增强化学的气相沉积法(pecvd)或低压化学气相沉积(lpcvd)可用于闸极氧化物沉积。然后在图19p中沉积一个多晶硅闸极层315。多晶硅层可以使用pecvd或lpcvd进行沉积。多晶硅层可以使用硼或磷进行退火掺杂,可以在原位或在随后的步骤中进行。原位掺杂可以通过在多晶硅沉积化学过程中加入ph3前体来进行。多晶硅的沉积后掺杂可以通过沉积一层pocl3,然后在700-900℃的温度下进行驱动步骤。如图19q所示,在上面沉积硬屏蔽316并进行图案化。多晶硅闸极层315是通过使用图案化屏蔽层316进行蚀刻。在图19r中,屏蔽层316接着被移除。在晶圆上沉积由50nm-1000nm厚的二氧化硅、氮化硅、氧氮化硅层或其叠加组合组成的ild层317;在上面沉积和图案化一个硬屏蔽,以确定ild开口;如图19s所示,使用硬屏蔽对ild层317进行图案化。接着闸极氧化物314是使用相同的屏蔽蚀刻的。然后去除屏蔽,在图19t中暴露的sic表面上形成一个硅化镍区域318。图19u中,铝或银或金的互连金属层319被沉积在芯片的顶部和底部,并进行图案化。

438、图20所示的一个实施例是sic dmosfet的一个横截面结构的单元格。该器件的关键区域是p井区403,它是通过离子植入或p型物种(例如铝或硼)的外延再生长而形成。有一个n+源极区404,n-漂移层402,和一个n+基板401。在导通状态下,当对多晶硅闸极406施加闸极电压时,电流从汲极401垂直流过p井区403顶部形成的反转层,通过n+源极区404,并通过源极金属化层408流出。在关断状态或阻断状态下,一个电压被支持在p井403、n-漂移层402接面上,并且有一个pn接面在p井和n-漂移层之间形成。施加到结构上的电压在反向偏压下被支持在这个pn接面上。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井中形成反转通道的部分,两个连续的p井之间的距离,称为jfet区域或jfet间隙,以及闸极氧化物405的厚度。另一个特点是ild层407,用于将源极互连金属化层408与多晶硅闸极406绝缘。在单元格的最中心,有一个p+插塞409,其通过n+源极金属化层接地。sic dmosfet中p+插塞的目的是通过n+源极接触点将p井区接地。

439、通过干法蚀刻在紧接源极区404形成之前的p井植入区中形成p井沟槽410,导致mos通道的一部分形成在(0001)或水平面上,mos通道的另一部分形成在sic的(11-20/10-10)或垂直晶体面上。然而,在图20所示的实施例中,通过对p井区的全部蚀刻,形成了一个更深的垂直mos通道。随后,在形成n+源极区之后,在n+源极区的下方和周围离子注入了第二个p井区,表示为pw#2411,以抑制穿透性击穿。

440、通过离子植入或外延生长,使用铝或硼作为p型杂质,首先形成p井区403。然后,通过使用适当图案的硬屏蔽层,通过rie或icp蚀刻对p井区进行控制性蚀刻,形成p井沟410。p井沟410的侧壁角度可以在75°和90°之间。p井沟区域的深度可以从0.5μm 2μm。与图18所示的器件相比,图20中的器件的p井沟的深度可以调整为与p井区的深度相同或甚至略深。在图20所示的实施例中,p井沟的底部可能不会完全封闭在p井区内。n+源极区是通过离子植入或通过n型杂质(如氮或磷)的外延再生长形成。然后在n+源极区下形成一个足够深度的第二p井区(pw#2)411,使pw#2区的横向范围大于原p井区。形成pw#2411区域的两种方法被确定。(1)可沉积专用的硬屏蔽层,并以比原p井区稍大的范围进行图案化,然后进行pw#2的离子植入。(2)倾斜离子植入法可有利地用于实现pw#2。在这里的实施例中,同一硬屏蔽可用于创建沟槽,n+源极区,然后是pw#2区,其横向范围使用倾斜离子植入的p型杂质,使得比原来的p井区403更大。该制程的其余部分包括对晶圆进行热处理,以便对植入的杂质进行电活化,形成闸极绝缘体,形成闸极电极,形成层间电介质,形成源极/汲极欧姆金属化层,最后形成与芯片探测和封装兼容的焊盘或互连金属。闸极绝缘体405是通过碳化硅的热氧化或通过电介质层如二氧化硅、氮化硅、氧氮化硅等的cvd形成的。

441、图20中的这个实施例所描述的器件是对图18中的实施例所描述的器件的增强,并具有几个额外的功能和优势。图20中的实施例的mos通道的垂直部分可以做得比图18所示的器件大得多,这是因为图20中的mosfet有更深的p井沟410。与水平表面相比,更大比例的mos通道可以在具有较高通道移动能力的垂直侧壁上实现。例如,对于1微米的总通道长度,0.25微米的mos通道可以在水平表面实现,0.75微米的mos通道可以在垂直侧壁实现。因此,在相同的mos通道长度下,图20所示实施例中描述的器件的有效通道移动性可以比图18所示实施例中描述的器件大。因此,对于相同的有效通道移动性,与使用图18中的实施例制造的mosfet相比,使用图20中的实施例可以制造出更长的通道mos。长通道mosfet具有更高的器件稳健性,包括更低的汲极饱和电流、更高的短路稳健性、更低的随汲极电压变化的vth滚降、对汲极端引入的势垒降低(dibl)效应的免疫。

442、在图20的实施例中,与原来的p井403相比,pw#2411需要的范围更大,这对减少mos通道水平部分的通道长度是必要的和有益的。通过形成一个横向范围大于原始p井的pw#2,在高压阻断条件下的汲极电势被pw#2区域有效地屏蔽了原始p井区。这使得延伸到p井沟外的原始p井区的横向范围(电剂量)大大减少,而没有穿透性击穿的风险。p井沟以外的p井区的横向范围减少,导致在水平表面上形成的mosfet通道的部分更小。

443、图21a至图21v描述了图20中所示结构的制造过程。sic dmosfet的制造过程是在sic基板501上进行的,首先是使用4h-sicsi面外延晶圆,其掺杂度(1014-1018cm-3)和厚度(1μm至300μm)适合图21a所示的外延层502。在图21b中沉积了一个由cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层(例如镍)组成的空白硬屏蔽503,其厚度为50纳米至5微米,然后使用光刻技术进行图案化,接着使用rie进行干蚀刻,例如图21c所示。然后通过离子植入或外延生长,使用铝或硼作为p型杂质,首先形成p井区。在图21d中进行由硼或铝组成的p型植入504,能量范围为10kev至800kev,植入剂量范围为1012cm-2至1015cm-2,以形成图21e中的p井505。移除屏蔽503,并通过cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层如镍,厚度为50纳米至5微米的另一硬屏蔽层506,然后如图21f所示进行图案制作。通过rie或icp蚀刻,使用图21g中适当图案化的硬屏蔽层506,通过控制蚀刻制程507在p井区形成深p井沟508。p井沟508的侧壁角度可以在75°和90°之间。例:p井沟区域的深度可以从0.5微米到2微米不等。p井沟508的深度可以调整为与p井区的深度相同或甚至略深。p井沟的底部可能没有完全封闭在p井区内。

444、在图21h中,为创建n+源极区510做了一个n型植入509。n+源极区是通过离子植入或通过n型杂质(例如氮或磷)的外延再生长形成。然后在n+源极区下形成一个足够深度的第二p井区(pw#2)511,使pw#2区的横向范围大于图21i中的原p井区。形成pw#2区域511的两种方法被确定。(1)可沉积专用的硬屏蔽层,并以比原p井区稍大的范围进行图案化,然后进行pw#2的离子植入。(2)倾斜离子植入法可有利地用于实现pw#2。在这里的实施例中,同一硬屏蔽506可用于创建p井区508,n+源极区510,然后是pw#2区511,其横向范围使用倾斜离子植入的p型杂质,使得比原来的p井区更大。

445、在图21j中,屏蔽层506被移除。在图21k中沉积了另一个硬屏蔽层512。在图21l中,硬屏蔽层512进行图案化。可以通过植入控制剂量的p型杂质513,如图21m中的铝或硼,形成p+插塞。p+插塞514的深度最好可以超过n+源极植入物的深度,甚至可以超过p井区的深度,在图21n的一个特定实施案例中。随后,使用图21o中本领域人士普遍采用的干法或湿法蚀刻技术去除硬屏蔽512。然后通过热氧化或使用如图21p中的二氧化硅、氮化硅、氧氮化硅等电介质层的cvd方式形成作为闸极氧化物的氧化层515。闸极氧化物的厚度可以从10纳米到100纳米。干式或湿式热氧化都可用于氧化物的生长。pecvd或lpcvd可用于闸极氧化物的沉积。然后在图21q中沉积一个多晶硅闸极层516。多晶硅层可以使用pecvd或lpcvd进行沉积。多晶硅层可以使用硼或磷进行退火掺杂,可以在原位或在随后的步骤中进行。原位掺杂可以通过在多晶硅沉积化学过程中加入ph3前体来进行。多晶硅的沉积后掺杂可以通过沉积一层pocl3,然后在700-900℃的温度下进行驱动步骤。如图21r所示,在上面沉积硬屏蔽517并进行图案化。多晶硅闸极层516是通过使用图案化屏蔽层517进行蚀刻。在图21s中,屏蔽层517接着被移除。在晶圆上沉积由50nm-1000nm厚的二氧化硅、氮化硅、氧氮化硅层或其叠加组合组成的ild层518;在上面沉积和图案化一个硬屏蔽,以确定ild开口;如图21t所示,使用硬屏蔽对ild层518进行图案化。接着闸极氧化物515是使用相同的屏蔽蚀刻的。然后去除屏蔽,在图21u中暴露的sic表面上形成一个硅化镍区域519。图21v中,铝或银或金的互连金属层520被沉积在芯片的顶部和底部,并进行图案化。

446、本文所述的一个实施例涉及到短通道sic mosfet的设计和制造。

447、本文所述的一个实施例涉及到将高电压、短通道sic mosfet的dibl效应降至最低。

448、本文所述的一个实施例涉及到设计和制造具有亚微米级通道长度的mos通道。

449、本文所述的实施例实现了一个既具有足够低的导通电阻,又具有足够高的短路耐受时间的器件。

450、本文所述的实施例涉及到在通道的某些区域局部增加通道的掺杂浓度。sicmosfet的非均匀掺杂通道在导通电阻、阈值电压和短路耐受时间之间提供了更好的权衡。

451、在本文所述的实施例中,涉及到在通道局部增加掺杂浓度,使其不会过多地增加阈值电压,但同时减少dibl效应,以实现更好的权衡。

452、在本文所述的一个实施例中,在p井区内形成了称为p型屏蔽层的p型屏蔽。p-屏蔽总是起源于p井区,但它可以延伸到p井区的垂直范围之外。

453、在本文所述的一个实施例中,p-屏蔽区的底部可以延伸到p井区的下方。

454、在本文所述的一个实施例中,可以有多个p-屏蔽区。不同p-屏蔽区的掺杂浓度可以彼此不同。

455、本文所述的实施例涉及一种器件,其中p-屏蔽区被形成埋在p井结构内。p-屏蔽总是起源于p井区,但它可以延伸到p井区的垂直范围之外。

456、在本文的一个实施例中,器件结构可以有多个p-屏蔽区。在这些情况下,不同的p-屏蔽区的它们的掺杂浓度分布不一定要相同,可以彼此不同。

457、在平面闸极sic mosfet中实现较低的导通级电阻的竞赛中,特别是在高额定击穿电压的情况下,通常的做法是使通道长度尽可能短,因为这可以减少与sic通道有关的很大一部分传导损耗。与硅mosfets中的mos迁移率相比,sic mos结构中的mos迁移率要小得多,因此为了达到足够低的导通电阻,人们需要使通道长度相当短,有时甚至是亚微米范围。

458、随着通道长度变短,短通道效应在sic功率mosfet中成为一个问题,导致汲极端引入的势垒降低效应,也称为dibl效应,这是造成sic mosfet中许多可靠性问题的原因。

459、一个相关的问题是在高汲极偏压下阈值电压的滚落,而所设计的器件只有在非常低的汲极偏压下才能达到某种期望的阈值电压。但是,当汲极偏压接近它的阻断值时,阈值电压会大幅降低,这是不可取的,因为通道可能无意中打开。

460、此外,遭受dibl效应的器件在高汲极偏压下具有极大的饱和电流。这导致在短路负载条件下的过度功率耗散。这导致了较低的短路耐受时间。虽然sic mosfets有限的mos通道移动性可以用短通道长度来克服,但它与dibl效应带来的问题有关。

461、缓解这一问题的一种方法是增加通道区的掺杂浓度,这将均匀地增加器件的阈值电压。虽然这种方法可以减少饱和汲极电流,但这也增加了器件的导通电阻。

462、本文所述的实施例可以实现一个既具有足够低的导通电阻,又具有足够高的短路耐受时间的器件。虽然传统的方法只是均匀地增加通道区域的掺杂浓度,但本文所述的实施例并没有均匀地增加其他通道的掺杂浓度,而是在通道的某些区域局部增加。sicmosfet的非均匀掺杂通道在导通电阻、阈值电压和短路耐受时间之间提供了更好的权衡。

463、在这里的实施例中,掺杂浓度的增加使得它们不会过多地增加阈值电压,但同时减少dibl效应,从而实现更好的权衡。

464、在本文所述的一个实施例中,在p井区内形成了称为p型屏蔽层的p型屏蔽。p-屏蔽是起源于p-井区,但在本实施例的某些例子中,它可以延伸到p-井区的垂直范围之外。

465、在这里的一个实施例中,p-屏蔽区的底部可以进一步向下延伸,可以达到p井区的下方。在本文所述的一个实施例中,可以有多个p-屏蔽区。不同p-屏蔽区的掺杂浓度可以彼此不同。

466、在本文所述的一个实施例中,在p井区内形成了称为p型屏蔽层的p型屏蔽。p-屏蔽是起源于p-井区,但在本实施例的某些例子中,它可以延伸到p-井区的垂直范围之外。

467、在这里的一个实施例中,p-屏蔽区的底部可以进一步向下延伸,可以达到p井区的下方。在这里的一个实施例中,可以有多个p-屏蔽区埋在p井区中。不同p-屏蔽区的掺杂浓度可以彼此不同。

468、埋在p井结构内的p屏蔽区重新加强了"p井区的局部掺杂,并在表面为mosfet通道提供了更好的屏蔽,同时将dibl效应降至最低。在本文所述的实施例中,由于p-屏蔽没有直接连接到通道上,p-屏蔽不会改变vth。

469、图23a所示的一个实施例是sic dmosfet的一个横截面结构的半单元格。该器件的关键区域是p井区203,它是通过离子植入或p型物种(例如铝或硼)的外延再生长而形成。有一个n+源极区205,n-漂移层202,和一个n+基板201。在导通状态下,当对多晶硅闸极207施加闸极电压时,电流从汲极201垂直流过p井区203顶部形成的反转层,通过n+源极区205,并通过源极金属化层210流出。在关断状态或阻断状态下,一个电压被支持在p井203、n-漂移层202接面上,并且有一个pn接面在p井和n-漂移层之间形成。施加到结构上的电压在反向偏压下被支持在这个pn接面上。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井中形成反转通道的部分,两个连续的p井之间的距离,称为接面型场效应管(jfet)区域或jfet间隙,以及闸极氧化物206的厚度。另一个特点是ild层208,用于将源极互连金属化层210与多晶硅闸极207绝缘。

470、在本文所述的一个实施例中,在p井区内形成了称为p型屏蔽层的p型屏蔽204a。p-屏蔽可以位于p井区内部,使其与p井区的平均背景掺杂浓度相比,掺杂浓度最高的点的横向位置位于p井区的边界内。p-屏蔽区域总是起源于p井区内。a点和b点是用来描述植入的p-屏蔽区的掺杂情况的参考点。

471、图23b所示的实施例与图23a的实施例相似,只是p-屏蔽区的底部进一步向下延伸到p井中,并能到达p井区之外。

472、在图23c和图23d所示的一个实施例中,器件与图23a类似。图23c和图23d中的器件举例说明了有多个p-屏蔽区的情况。在这些情况下,不同的p-屏蔽区的它们的掺杂浓度分布不一定要相同,可以彼此不同。

473、在用高电压偏压汲极的情况下,在通道中间形成的p-屏蔽可以帮助缓解汲极偏压引起的耗竭区的扩展,从而消除dibl效应。除了减轻dibl效应外,p-屏蔽区还为控制mosfet的vth提供了一种简单的方法,从而能够改善短路时间(tsc)。p-屏蔽使器件结构中关键位置的p井的掺杂浓度局部增加,而不是p井掺杂浓度的均匀增加。通过本发明所述的方法,在较低的vth、导通电阻和对短通道效应更好的免疫力方面,可以获得更好的权衡。在这种情况下,如果p-屏蔽区的深度大于p井区,即p-屏蔽区在垂直方向上延伸到p井区之外,p-屏蔽区还可以为通道区提供更好的电场屏蔽,从而进一步减轻通道中的dibl效应。具有多个p-屏蔽区的器件结构可以在不同的p-屏蔽区设计不同的掺杂浓度。在本文所述的一个实施例中,可将较高的掺杂浓度应用于靠近p井边缘(点a)的p屏蔽区/s,而靠近点b的p屏蔽区则可采用较低的掺杂浓度。这种结构的好处是,在给定的通道长度下,具有较低的闸极阈值电压以及对短通道效应的出色免疫力。

474、图24a至图24u描述了图23a中所示结构的制造过程。sic dmosfet的制造过程是在sic基板301上进行的,首先是使用4h-sic si面外延晶圆,其掺杂度(1014-1018cm-3)和厚度(1μm至300μm)适合图24a所示的外延层302。在图24b中沉积了一个由cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层(例如镍)组成的空白硬屏蔽303,其厚度为50纳米至5微米,然后使用光刻技术进行图案化,接着使用反应离子刻蚀(rie)进行干蚀刻,例如图24c所示。然后通过离子植入或外延生长,使用铝或硼作为p型杂质,首先形成p井区。在图24d中进行由硼或铝组成的p型植入304,能量范围为10kev至1000kev,植入剂量范围为1012cm-2至1015cm-2,以形成图24d中的p井305。在图24e中,图案化屏蔽层303被移除。

475、图24f中,硬屏蔽层306是由二氧化硅、氮化硅、氧氮化硅或金属层(例如镍),厚度从50纳米到5微米不等的cvd沉积层沉积。屏蔽层306是用光刻法制作的,然后用rie进行干蚀刻,例如在图24g中。

476、如图24h所示,做了一个p型植入物307,在p井内创造一个p型区域,称为p型屏蔽308。p-屏蔽区308可以用铝或硼作为p型杂质形成。p-屏蔽区的掺杂浓度可以在1e16cm-3到1e21cm-3之间。在图24i中,图案化屏蔽层306被移除。

477、在图24j中沉积了一个由cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层(例如镍)组成的空白硬屏蔽309,其厚度为50纳米至5微米,然后使用光刻技术进行图案化,接着使用rie进行干蚀刻,例如图24k所示。

478、图24l中的n+源极区311是通过离子植入或通过n型杂质如氮或磷310的外延再生长形成的。在图24m中,图案化屏蔽层309被移除。

479、通过热氧化或使用如图24n中的二氧化硅、氮化硅、氧氮化硅等电介质层的cvd方式形成作为闸极氧化物的氧化层312。闸极氧化物的厚度可以从10纳米到100纳米。干式或湿式热氧化都可用于氧化物的生长。电浆增强化学的气相沉积法(pecvd)或低压化学气相沉积(lpcvd)可用于闸极氧化物沉积。然后在图24o中沉积一个多晶硅闸极层313。多晶硅层可以使用pecvd或lpcvd进行沉积。多晶硅层可以使用硼或磷进行退火掺杂,可以在原位或在随后的步骤中进行。原位掺杂可以通过在多晶硅沉积化学过程中加入ph3前体来进行。多晶硅的沉积后掺杂可以通过沉积一层pocl3,然后在700-900℃的温度下进行驱动步骤来进行。在图24p中,多晶硅层313进行图案化。图24q中的晶圆上沉积了由50nm-1000nm厚的二氧化硅、氮化硅、氧氮化硅层或其叠加组合组成的ild层314。在图24r中,ild层314进行图案化。在图24s中,闸极氧化物312进行图案化。

480、在图24t中,在暴露的sic表面上形成了镍硅化物区域315。图24u中,铝或银或金的互连金属层316被沉积在基板的顶部和底部,并进行图案化。

481、图25a所示的一个实施例是sic dmosfet的一个横截面结构的半单元格。该器件的关键区域是p井区403,它是通过离子植入或p型物种(如铝或硼)的外延再生长而形成。有一个n+源极区405,n-漂移层402,和一个n+基板401。在导通状态下,当对多晶硅闸极407施加闸极电压时,电流从汲极401垂直流过p井区403顶部形成的反转层,通过n+源极区405,并通过源极金属化层410流出。在关断状态或阻断状态下,一个电压被支持在p井403、n-漂移层402接面上,并且有一个pn接面在p井和n-漂移层之间形成。施加到结构上的电压在反向偏压下被支持在这个pn接面上。在功率mosfet中,有几个关键特征,其中包括单元格的间距,即mosfet的重复单位,通道长度,即p井中形成反转通道的部分,两个连续的p井之间的距离,称为接面型场效应管(jfet区域)或jfet间隙,以及闸极氧化物406的厚度。另一个特点是ild层408,用于将源极互连金属化层410与多晶硅闸极407绝缘。

482、在p井结构内形成一个p型屏蔽区404a。换句话说,p-屏蔽是在sic表面下形成的,mosfet通道就位于那里。如图25a所示,p-屏蔽区总是起源于p井区,但在本实施例的某些例子中,可以延伸到p井区的垂直范围之外,如图25b所示。

483、图25b所示的实施例与图25a的实施例相似,只是p-屏蔽区的底部进一步向下延伸到p井中,并能到达p井区之外。

484、图25c和图25d所示的器件结构也与图25a中的器件相似,但它们举例说明了有多个p-屏蔽区的情况。在这些情况下,不同的p-屏蔽区的它们的掺杂浓度分布不一定要相同,可以彼此不同。上述各图中的a点和b点是用来描述植入的p-屏蔽区的掺杂情况的参考点。

485、图25a至图25d中的p-屏蔽层"重新加强"了p井区的局部掺杂,在表面为mosfet通道提供了更好的屏蔽,同时将dibl效应降至最低。由于p-屏蔽没有直接连接到通道上,在这种情况下,p-屏蔽不会改变阈值电压。图25a所示的器件为缓解dibl提供了同样的场屏蔽,但不需要改变阈值电压值,而这对图23a的器件来说是不可避免的。

486、图26a至图26u描述了图25a中所示结构的制造过程。sic dmosfet的制造过程是在sic基板501上进行的,首先是使用4h-sic si面外延晶圆,其掺杂度(1014-1018cm-3)和厚度(1μm至300μm)适合图26a所示的外延层502。在图26b中沉积了一个由cvd沉积的二氧化硅、氮化硅、氧氮化硅或金属层(例如镍)组成的空白硬屏蔽503,其厚度为50纳米至5微米,然后使用光刻技术进行图案化,接着使用反应离子刻蚀(rie)进行干蚀刻,例如图26c所示。然后通过离子植入或外延生长,使用铝或硼作为p型杂质,首先形成p井区。在图26d中进行由硼或铝组成的p型植入504,能量范围为10kev至1000kev,植入剂量范围为1012cm-2至1015cm-2,以形成图24d中的p井505。在图26e中,图案化屏蔽层503被移除。

487、图26f中,硬屏蔽层506是由二氧化硅、氮化硅、氧氮化硅或金属层(例如镍),厚度从50纳米到5微米不等的cvd沉积层沉积。屏蔽层506是用光刻法制作的,然后用rie进行干蚀刻,例如在图26g中。

488、如图26h所示,做了一个p型植入物507,在p井内创造一个p型区域,称为p型屏蔽508。p-屏蔽区508可以用铝或硼作为p型杂质形成。在p井结构内形成一个p型屏蔽区。换句话说,p-屏蔽是在sic表面下形成的,mosfet通道就位于那里。p-屏蔽区域总是起源于p井区内。p-屏蔽区的位置,是通过仔细调整用于实现p-屏蔽区的植入能量来控制的。

489、p型屏蔽区可以通过p型离子植入步骤创建,该步骤包括硼或铝,能量范围为25kev至800kev,植入剂量范围为1012cm-2至1015cm-2。在图26i中,图案化屏蔽层506被移除。

490、一种橡皮布硬屏蔽509,其包括二氧化硅、氮化硅、氮氧化硅或诸如镍的金属层的化学气相沉积(cvd)沉积层,如图26k所示,在图26j中沉积厚度在50纳米到5微米之间的薄膜,然后使用光刻术进行图案化,随后使用rie进行干蚀刻。

491、图26l中的n+源极区511是通过离子植入或通过n型杂质如氮或磷510的外延再生长形成的。在图26m中,图案化屏蔽层509被移除。

492、通过热氧化或使用如图26n中的二氧化硅、氮化硅、氧氮化硅等电介质层的cvd方式形成作为闸极氧化物的氧化层512。闸极氧化物的厚度可以从10纳米到100纳米。干式或湿式热氧化都可用于氧化物的生长。电浆增强化学的气相沉积法(pecvd)或低压化学气相沉积(lpcvd)可用于闸极氧化物沉积。然后在图26o中沉积一个多晶硅闸极层513。多晶硅层可以使用pecvd或lpcvd进行沉积。多晶硅层可以使用硼或磷进行退火掺杂,可以在原位或在随后的步骤中进行。原位掺杂可以通过在多晶硅沉积化学过程中加入ph3前体来进行。多晶硅的沉积后掺杂可以通过沉积一层pocl3,然后在700-900℃的温度下进行驱入步骤来进行。图26p中对多晶硅层513进行了图案化。图26q中的晶圆上沉积了由50nm-1000nm厚的二氧化硅、氮化硅、氧氮化硅层或其叠加组合组成的ild层514。在图26r中,ild层514进行图案化。在图26s中,闸极氧化物512进行图案化。

493、在图26t中,在暴露的sic表面上形成了镍硅化物区域515。图26u中,铝或银或金的互连金属层516被沉积在基板的顶部和底部,并进行图案化。

494、本文所述的实施例涉及到sic晶体管

495、这里的一个实施例中描述的器件有一个埋藏的n+区域,它位于该p+岛之间。埋藏的n+区域的形成方式是,它与晶圆表面物理分离,因为它不接触肖特基层。有一部分n-漂移层与肖特基表面接触。n+区域与晶圆表面的物理分离是本实施例的一个关键特征,因为肖特基金属的sic器件具有n-掺杂浓度,而不是n+掺杂浓度。与肖特基金属接触的碳化硅表面具有n-掺杂浓度,这对于降低肖特基金属界面与碳化硅的电场强度至关重要。在本文所述的一个实施例中,埋藏的n+区域的垂直范围低于p+区域的底部,并覆盖p+区域的底部。与现有技术的mps二极管相比,p+岛之间的间距更窄,p+岛的深度更深。n+区的存在使p+岛之间的间距更窄。p+岛屏蔽了肖特基界面在高电压运行期间形成的电场。在这里的实施例中,穿插在n+区域中的p+区域被设计成在p+岛和n+区域之间实现一定程度的电荷平衡,这提供了进一步降低该器件的导通电阻的好处,也保持了低电场。

496、在本文的一个实施例中,n+区的底部高于p+区的底部。p+区域的底部与n-漂移层接触,这是一种权衡,因为这将使漏电流降低,但导通电阻升高。在位于p+岛之间的n+区域被埋藏的器件的实施例中,可以实现更好的导通电阻,而在n+区域不完全包围p+岛底部的器件的实施例中,可以实现更低的漏电流。在本文所述的一个实施例中,位于p+岛之间的埋藏的n+区域和不完全包围p+岛底部的n+区域都可以存在于同一个器件上。

497、在本文所述的一个实施例中,n+区是由几个子n区形成的,而p+区是由许多子p区形成的,因此这些不同的层或片中的掺杂浓度可能不同。在一个实施例中,要么n+区域的最后一片在p+岛的下方,完全覆盖在p+岛的周围,要么n+片的底部高于p+区域的底部。离碳化硅表面更远的n+型子区域的掺杂浓度可以逐渐提高,这可能有降低传导损失的好处。在另一个实施例中,离sic表面较远的p型子区域的掺杂浓度可以逐渐降低,这可能会使阻断特性更好。这里的实施例中所描述的不同的掺杂浓度允许自由地将器件设计适当地调整为较低的泄漏电流、更好的传导损失、较低的电阻等。相对于只有一个p+层和一个n+层,分层和不同掺杂的n+和p+区域可以实现更好的权衡,这可以通过使用多个离子植入步骤或多个外延生长来实现。

498、在这里的一个实施例中,穿插在一组多个p+井之间的n+区域是以这样的方式形成的,它与晶圆表面物理分离,并一直延伸到n-漂移区域。在这里的实施例中,n+区域与sic晶圆表面的物理分离使其与其他类似的发明不同。

499、在本文的实施例中,与肖特基金属(金属1)接触且为n型半导体的sic芯片的一部分具有相同的n-漂移掺杂浓度,因为与肖特基金属(金属1)直接接触的n型sic半导体的掺杂浓度在sic mps二极管的高压阻断模式操作期间,对于降低芯片表面的电场强度至关重要。

500、图28a所示的实施例的器件是sic mps二极管的横截面示意图。该器件的关键区域是位于底部的n+基板201,它为晶圆提供机械支持,厚度约为350微米。一个n-漂移区202,通常是一个外延层,位于n+基板的顶部。有多个p+井204,形成线性条纹或更复杂的圆形或六角形图案。该器件有一个第一金属层205,表示为金属1,它是n型sic半导体区域的肖特基金属,并与它下面的n型区域形成肖特基接触。该器件在晶圆的正面有一个第二金属层206,表示为金属2,与金属1接触。金属2通常被称为"动力金属",通常是铝制的。在n+基板的底部有一个硅化物层207。在晶圆的背面下面有一个第三金属层208,表示为金属3,它与硅化层接触。

501、图28a所示的装器件有一个n+区域203,它穿插在一组多个p+井204之间。n+区203是以这样的方式形成的,它与晶圆表面物理分离,并一直延伸到n-漂移区202。n+区与sic晶圆表面的物理分离是本文所述实施例的一个关键特征,并将其与其他类似发明区分开来。与肖特基金属205接触的sic晶圆的一部分,表示为金属1,是一个n型半导体,具有与n-漂移区202相同的掺杂浓度。在本文所述的实施例中,在sic mps二极管的高压阻断工作模式中,与标记为金属1的肖特基金属205直接接触的n型sic半导体的掺杂浓度对于降低晶圆表面的电场强度至关重要。n+区域203的垂直范围低于p+区域204的底部。埋藏的n+区完全围绕着p+区,这为肖特基注入的多数载子提供了一个更有导电性的行进路径,并减少了总的正向传导损耗。