具有沟槽底部屏蔽结构的沟槽半导体装置的制作方法

本发明涉及功率半导体装置,更具体而言,涉及具有栅极沟槽的功率半导体装置以及制造这种装置的方法。

背景技术:

1、金属绝缘半导体场效应晶体管(“misfet”)是可以被用作开关装置的众所周知的类型的半导体晶体管。misfet是三端装置,其具有栅极、漏极和源极端子以及半导体主体。源极区域和漏极区域形成在半导体主体中,由沟道区域隔开,并且栅极电极(其可以充当栅极端子或电连接到栅极端子)部署成与沟道区域相邻。misfet可以通过向栅极电极施加偏置电压而被接通或关断。当misfet接通时(即,它处于其“导通状态”),电流通过misfet的源极区域和漏极区域之间的沟道区域传导。当偏置电压从栅极电极移除(或降低到阈值电平以下)时,电流停止通过沟道区域传导。举例来说,n型misfet具有n型源极和漏极区域以及p型沟道。因此,n型misfet具有“n-p-n”设计。当向栅极电极施加足以在p型沟道区域中产生导电n型反型层的栅极偏置电压时,n型misfet接通,所述导电n型反型层电连接n型源极区域和漏极区域,从而允许其间的多数载流子传导。功率misfet的栅极电极通常通过薄栅极介电层与沟道区域隔开。

2、在一些应用中,misfet可能需要承载大电流和/或能够阻断高电压。这种misfet通常被称为“功率”misfet。本领域已知各种各样的其它功率半导体装置,包括例如双极结晶体管(“bjt”)、绝缘栅双极晶体管(“igbt”)、结势垒肖特基二极管、栅极关断晶体管(“gto”),mos控制的晶闸管和其它各种装置。这些功率半导体装置通常由宽带隙半导体材料制成,诸如基于碳化硅(“sic”)或氮化镓(“gan”)的半导体材料。在本文中,宽带隙半导体材料是指带隙大于1.40ev的半导体材料。

3、功率半导体装置可以具有横向结构或垂直结构。在具有横向结构的装置中,装置的端子(例如,功率mosfet装置的漏极、栅极和源极端子)位于半导体层结构的同一主表面(即顶部或底部)上。作为对照,在具有垂直结构的装置中,在半导体层结构的每个主表面上提供至少一个端子(例如,在垂直mosfet装置中,源极可以在半导体层结构的顶表面上并且漏极可以在半导体层结构的底表面上)。半导体层结构可以包括或可以不包括下面的衬底。在本文中,术语“半导体层结构”是指包括诸如半导体衬底和/或半导体外延层之类的一个或多个半导体层的结构。

4、常规的功率半导体装置通常具有半导体衬底,诸如具有第一导电类型的碳化硅衬底(例如,n型衬底),其上形成具有第一导电类型(例如,n型)的外延层结构。该外延层结构的一部分(其可以包括一个或多个单独的层)用作功率半导体装置的漂移区域。该装置通常包括“有源区域”,其包括一个或多个具有诸如p-n结的结的功率半导体装置。有源区域可以形成在漂移区域上和/或漂移区域中。有源区域充当主结,用于在反向偏置方向上阻断电压并在正向偏置方向上提供电流。功率半导体装置还可以在与有源区域相邻的终端区域中具有边缘终端。一个或多个功率半导体装置可以形成在衬底上,并且每个功率半导体装置通常将具有其自己的边缘终端。在衬底被完全处理之后,所得结构可以被切割以分离单独的边缘端接的功率半导体装置。功率半导体装置可以具有单位单元(unit cell)结构,其中每个功率半导体装置的有源区域包括多个单独的“单位单元”装置,这些装置彼此平行部署并且一起用作单个功率半导体装置。

5、功率半导体装置被设计用于阻断(在正向或反向阻断状态下)或通过(在正向操作状态下)大电压和/或电流。例如,在阻断状态下,功率半导体装置可以被设计为承受数百或数千伏特的电势。但是,随着所施加的电压接近或超过装置被设计为阻断的电压水平,非少量水平的电流可能开始流过功率半导体装置。这种通常被称为“泄漏电流”的电流会是非常不希望的。如果电压增加到超过装置的设计电压阻断能力,泄漏电流可能开始流动,该设计电压阻断能力可能随着漂移区域的掺杂和厚度等等而变化。泄漏电流也可能由于其它原因而出现,诸如装置的边缘终端和/或主要结的故障。如果施加到装置的电压增加到超过击穿电压达到临界水平,那么增加的电场可能导致半导体装置内电荷载流子的不可控且非期望的失控生成,从而导致被称为雪崩击穿的情况。

6、功率半导体装置也可能在低于装置的设计击穿电压的电压水平下开始允许非少量泄漏电流流动。特别地,泄漏电流可能开始在有源区域的边缘处流动,在有源区域的边缘处可能由于电场拥挤效应出现高电场。为了减少这种电场拥挤(以及由此产生的增加的泄漏电流),可以提供包围功率半导体装置的有源区域的部分或全部的上述边缘终端。这些边缘终端可以将电场扩散到更大的区域,从而减少电场拥挤。

7、包括mosfet晶体管的垂直功率半导体装置可以具有标准栅极电极设计,其中晶体管的栅极电极形成在半导体层结构的顶部上,或者,替代地,可以将栅极电极埋在半导体层结构内的沟槽中。具有掩埋栅极电极的mosfet通常被称为栅极沟槽mosfet。在标准栅极电极设计的情况下,每个单位单元晶体管的沟道区域被水平部署在栅极电极下方。作为对照,在栅极沟槽mosfet设计中,沟道是垂直部署的。栅极沟槽mosfet可以提供增强的性能,但通常需要更复杂的制造过程。

技术实现思路

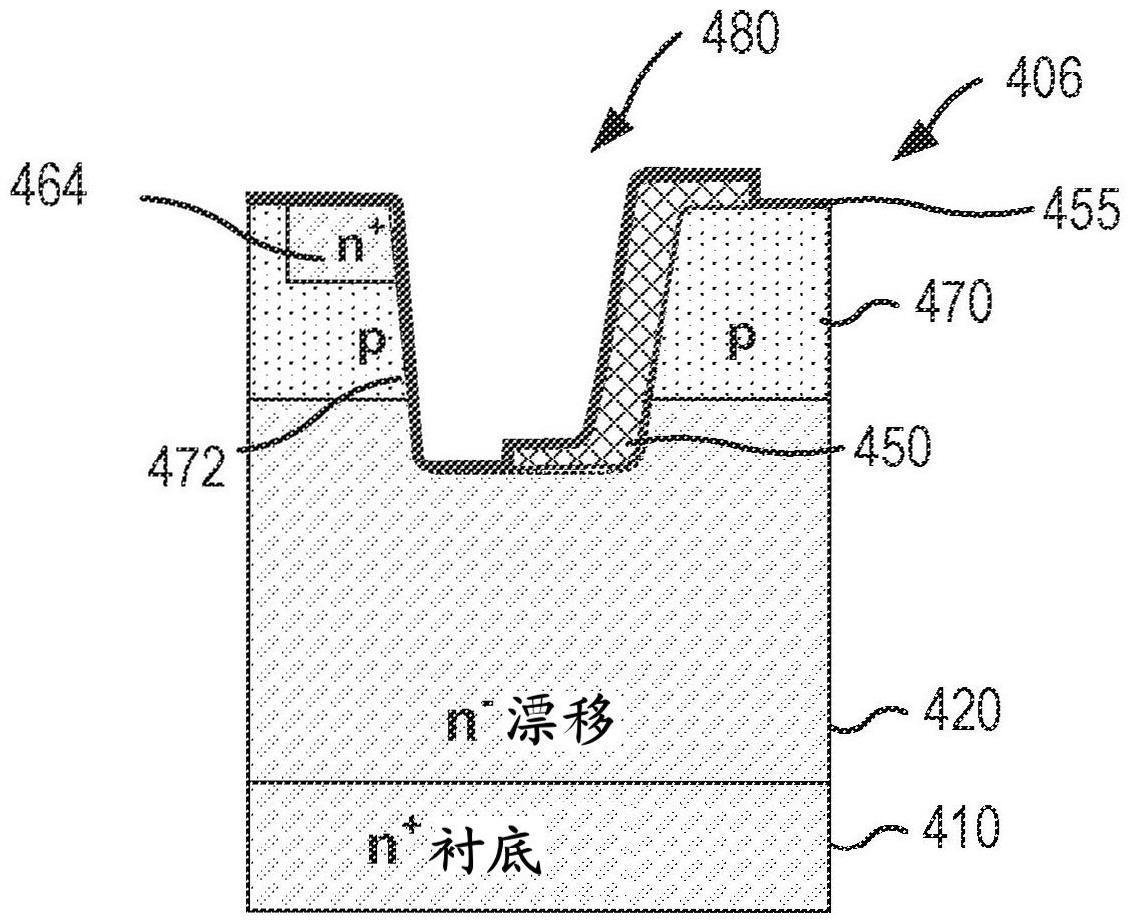

1、根据本发明构思的一些实施例,可以提供一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;位于半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口;以及多个多晶硅层,每个多晶硅层位于相应栅极沟槽的第二侧壁上。

2、在一些实施例中,该装置可以包括在每个多晶硅层上的氧化物层。在一些实施例中,该装置可以包括在相应栅极沟槽内的栅极结构,并且每个栅极结构包括栅极氧化物。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个多晶硅层延伸相应栅极沟槽的长度。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个栅极沟槽包括包含相应多晶硅层的第一长度部分和没有相应多晶硅层的第二长度部分。

3、在一些实施例中,该装置可以包括在栅极沟槽的第一侧壁中和在栅极沟槽的第二长度部分的第二侧壁中的沟道区域。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域在阱区域中。在一些实施例中,每个栅极沟槽包括第三长度部分,该第三长度部分包括在其第一侧壁上的多晶硅层。在一些实施例中,该装置可以包括在栅极沟槽的第一侧壁中的沟道区域。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域在阱区域中。在一些实施例中,宽带隙半导体包括碳化硅。在一些实施例中,该装置可以包括在每个栅极沟槽的底表面、第一侧壁和第二侧壁上的下氧化物层,并且多晶硅层可以在下氧化物层上。在一些实施例中,该装置可以包括在多晶硅层上的上氧化物层。

4、根据本发明构思的一些实施例,可以提供一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;位于半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口;以及多个多晶硅层,每个多晶硅层位于多个栅极沟槽中的相应栅极沟槽下方。

5、在一些实施例中,多个栅极沟槽包括:第一栅极沟槽,各自具有在其底表面下方的相应的多晶硅层;以及第二栅极沟槽,在其底表面下方没有多晶硅层。在一些实施例中,该装置可以包括在每个第二栅极沟槽中的栅极结构。在一些实施例中,装置的每个栅极沟槽可以包括多个多晶硅层中的相应多晶硅层。在一些实施例中,该装置可以包括在每个栅极沟槽中的栅极结构。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个多晶硅层延伸相应栅极沟槽的长度。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个栅极沟槽包括包含相应多晶硅层的第一长度部分和没有相应多晶硅层的第二长度部分。在一些实施例中,该装置可以包括在栅极沟槽的第一侧壁中和在栅极沟槽的第二长度部分的第二侧壁中的沟道区域。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域在阱区域中。在一些实施例中,该装置可以包括在每个多晶硅层上的氧化物层。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。在一些实施例中,该装置可以包括在每个栅极沟槽的第一侧壁中的沟道区域。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域在阱区域中。在一些实施例中,宽带隙半导体包括碳化硅。

6、根据本发明构思的一些实施例,可以提供一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口,每个栅极沟槽包括沿着栅极沟槽的长度交替的多个第一长度部分和多个第二长度部分;以及多个多晶硅层,每个多晶硅层位于第一长度部分中的相应栅极沟槽的第二侧壁上。每个栅极沟槽的第二长度部分可以没有多晶硅层。

7、在一些实施例中,该装置可以包括在每个栅极沟槽内的氧化物层。在一些实施例中,氧化物层包括在每个栅极沟槽的第一长度部分中的第一横截面和在每个栅极沟槽的第二长度部分中的第二横截面。在一些实施例中,该装置可以包括在相应栅极沟槽内的栅极结构,其中栅极结构包括栅极电极。在一些实施例中,栅极电极包括在每个栅极沟槽的第一长度部分中的第一横截面和在每个栅极沟槽的第二长度部分中的第二横截面。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。在一些实施例中,宽带隙半导体包括碳化硅。

8、根据本发明构思的一些实施例,可以提供一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口,并且多个栅极沟槽包括第一栅极沟槽和第二栅极沟槽;多个多晶硅层,每个多晶硅层位于多个栅极沟槽中的相应第一栅极沟槽下方;多个栅极电极,每个栅极电极布置在多个栅极沟槽中的相应第二栅极沟槽内。每个栅极沟槽的第二长度部分可以没有多晶硅层。

9、在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个多晶硅层延伸相应第一栅极沟槽的长度。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸。在一些实施例中,该装置可以包括在第二栅极沟槽的第一侧壁中的沟道区域。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域可以在阱区域中。在一些实施例中,宽带隙半导体包括碳化硅。

10、根据本发明构思的一些实施例,提供了一种形成半导体装置的方法。该方法可以包括:在衬底上形成宽带隙半导体层结构,该半导体层结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中形成多个栅极沟槽,栅极沟槽彼此间隔开,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口;以及沿着各栅极沟槽的第二侧壁形成多晶硅层。

11、在一些实施例中,该方法可以包括在多晶硅层上形成氧化物层。在一些实施例中,该方法可以包括在每个栅极沟槽的底表面、第一侧壁和第二侧壁上形成下氧化物层,其中形成多晶硅层包括在下氧化物层上形成多晶硅层。在一些实施例中,该方法可以包括在多晶硅层上形成上氧化物层。在一些实施例中,该方法可以包括在相应栅极沟槽内形成栅极结构,其中每个栅极结构包括栅极电极。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该方法可以包括在半导体层结构的第一主表面上形成第一源极/漏极接触并且在半导体层结构的与第一主表面相对的第二主表面上形成第二源极/漏极接触。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个多晶硅层延伸相应栅极沟槽的长度。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个栅极沟槽包括包含相应多晶硅层的第一长度部分和没有相应多晶硅层的第二长度部分。在一些实施例中,沟道区域形成在栅极沟槽的第一侧壁中和栅极沟槽的第二长度部分的第二侧壁中。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域可以在阱区域中。在一些实施例中,沟道区域形成在栅极沟槽的第一侧壁中。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域可以在阱区域中。在一些实施例中,宽带隙半导体包括碳化硅。

12、根据本公开的一些实施例,可以提供一种形成半导体装置的方法。该方法可以包括在衬底上形成宽带隙半导体层结构,该半导体层结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中形成多个栅极沟槽,栅极沟槽彼此间隔开,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口;以及在至少一些栅极沟槽的底部处形成多晶硅层。

13、在一些实施例中,多个栅极沟槽包括:第一栅极沟槽,每个第一栅极沟槽在其底表面上具有相应多晶硅层;以及第二栅极沟槽,在其底表面上没有多晶硅层。在一些实施例中,该方法还可以包括在每个第二栅极沟槽中形成栅极结构。在一些实施例中,在半导体装置的每个栅极沟槽中形成多晶硅层。在一些实施例中,该方法可以包括在每个栅极沟槽中形成栅极结构。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个多晶硅层延伸相应栅极沟槽的长度。在一些实施例中,每个栅极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个栅极沟槽包括包含相应多晶硅层的第一长度部分和没有相应多晶硅层的第二长度部分。在一些实施例中,该方法可以包括在每个多晶硅层上形成氧化物层。在一些实施例中,该方法可以包括在半导体层结构的第一主表面上形成第一源极/漏极接触并且在半导体层结构的与第一主表面相对的第二主表面上形成第二源极/漏极接触。在一些实施例中,宽带隙半导体包括碳化硅。

14、根据本公开的一些实施例,可以提供一种形成半导体装置的方法。该方法可以包括:在衬底上形成宽带隙半导体层结构,该半导体层结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中形成多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口,每个栅极沟槽包括沿着栅极沟槽的长度交替的多个第一长度部分和多个第二长度部分;以及形成多个多晶硅层,每个多晶硅层位于第一长度部分中的相应栅极沟槽的第二侧壁上。每个栅极沟槽的第二长度部分可以没有多晶硅层。

15、在一些实施例中,该方法可以包括在每个栅极沟槽内形成氧化物层。在一些实施例中,氧化物层包括在每个栅极沟槽的第一长度部分中的第一横截面和在每个栅极沟槽的第二长度部分中的第二横截面。在一些实施例中,该方法可以包括在相应栅极沟槽内形成栅极结构,其中栅极结构包括栅极电极。在一些实施例中,栅极电极包括在每个栅极沟槽的第一长度部分中的第一横截面和在每个栅极沟槽的第二长度部分中的第二横截面。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该方法可以包括在半导体层结构的第一主表面上形成第一源极/漏极接触并且在半导体层结构的与第一主表面相对的第二主表面上形成第二源极/漏极接触。在一些实施例中,宽带隙半导体包括碳化硅。

16、根据本公开的一些实施例,提供了一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;位于半导体层结构的上部中的多个源极沟槽,每个源极沟槽具有底表面、第一侧壁、第二侧壁和上开口;位于半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口;以及多个多晶硅层,每个多晶硅层位于多个源极沟槽中的相应源极沟槽下方。

17、在一些实施例中,多个源极沟槽包括第一源极沟槽,每个第一源极沟槽在其底表面下方具有相应的多晶硅层,并且其中每个栅极沟槽在其底表面下方没有多晶硅层。在一些实施例中,该装置可以包括在每个栅极沟槽中的栅极结构。在一些实施例中,每个栅极沟槽和每个源极沟槽在与半导体层结构的上表面平行的方向上在长度上延伸,并且每个多晶硅层延伸相应的源极沟槽的长度。在一些实施例中,该装置可以包括在每个栅极沟槽的第一和第二侧壁中的沟道区域。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域,并且沟道区域在阱区域中。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。

18、根据本公开的一些实施例,提供了一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口,每个栅极沟槽包括多个第一长度部分、多个第二长度部分和多个第三长度部分;多个第一多晶硅层,每一第一多晶硅层位于第一长度部分中的相应栅极沟槽的第一侧壁上;以及多个第二多晶硅层,每个第二多晶硅层位于第二长度部分中的相应栅极沟槽的第二侧壁上。第三长度部分中的每个栅极沟槽的第一和第二侧壁可以没有第一和第二多晶硅层。

19、在一些实施例中,该装置可以包括在每个栅极沟槽内的氧化物层。氧化物层可以在每个栅极沟槽的第一长度部分中具有第一横截面、在每个栅极沟槽的第二长度部分中具有第二横截面,并且在每个栅极沟槽的第三长度部分中具有第三横截面。在一些实施例中,该装置可以包括在相应栅极沟槽内的栅极结构,其中栅极结构包括栅极电极。栅极电极可以在每个栅极沟槽的第一长度部分中具有第一横截面、在每个栅极沟槽的第二长度部分中具有第二横截面,并且在每个栅极沟槽的第三长度部分中具有第三横截面。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。在一些实施例中,宽带隙半导体包括碳化硅。

20、根据本公开的一些实施例,提供了一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;在半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口,每个栅极沟槽包括多个第一长度部分和多个第二长度部分;以及多个多晶硅层,每个第一多晶硅层在第一长度部分中的相应栅极沟槽的第一和第二侧壁上。在第二长度部分中的每个栅极沟槽的第一和第二侧壁可以没有多晶硅层。

21、在一些实施例中,该装置可以包括在每个栅极沟槽内的氧化物层。氧化物层可以在每个栅极沟槽的第一长度部分中具有第一横截面并且在每个栅极沟槽的第二长度部分中具有第二横截面。在一些实施例中,该装置可以包括在相应栅极沟槽内的栅极结构,其中栅极结构包括栅极电极。栅极电极可以在每个栅极沟槽的第一长度部分中具有第一横截面,并且在每个栅极沟槽的第二长度部分中具有第二横截面。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。在一些实施例中,宽带隙半导体包括碳化硅。

22、根据本公开的一些实施例,提供了一种装置。该装置可以包括:宽带隙半导体层结构,该结构包括具有第一导电类型的漂移区域;位于半导体层结构的上部中的多个栅极沟槽,每个栅极沟槽具有底表面、第一侧壁、第二侧壁和上开口,并且每个栅极沟槽暴露漂移区域的侧表面;以及多个多晶硅层,每个多晶硅层位于相应栅极沟槽的第一和第二侧壁的至少部分上。

23、在一些实施例中,该装置可以包括在每个栅极沟槽内的氧化物层。在一些实施例中,该装置可以包括在相应栅极沟槽内的栅极结构,其中栅极结构包括栅极电极。在一些实施例中,半导体层结构包括具有与第一导电类型不同的第二导电类型的阱区域。在一些实施例中,该装置可以包括在半导体层结构的第一主表面上的第一源极/漏极接触和在半导体层结构的与第一主表面相对的第二主表面上的第二源极/漏极接触。在一些实施例中,宽带隙半导体包括碳化硅。

- 还没有人留言评论。精彩留言会获得点赞!